# **Class 0 & Reliability ESD Case Studies**

**No Product Sales!**

**Client Locations**

Ted Dangelmayer www.dangelmayer.com

# **Examples of Customer Base**

# Outline

- Preliminaries

- Manufacturing Quality Case Studies

- Reliability Case Studies

- System Reliability Case Studies

- Class 0 Case Studies

# **ESD Acronyms**

- EPM:

- ESD Program Management: A Total EPM Quality System

- EPM Yield Risk Benchmarking<sup>TM</sup>

- Relative Compliance to Best Practices

- Quantifies Yield Improvement Opportunity

- HBM Human Body Model

- CDM Charged Device Model

- CBE Charged Board Event

- CDE Cable Discharge Event

- EOS Electrical Overstress

- IC Damage due to Electrical Over Voltage or Current

## "Class 0" Terms Used in this Tutorial

- Class 0

- Blanket term used to refer to devices with thresholds less than 250 volts HBM or CDM (i.e., Class OA or OB)

- Class 0B

- Withstand Voltage greater than/equal to 125 volts and less than 250 volts HBM or CDM

- Class 0A

- Withstand Voltages Less than 125 volts HBM or CDM

- Class "000"

- Withstand voltage Less than 50 volts

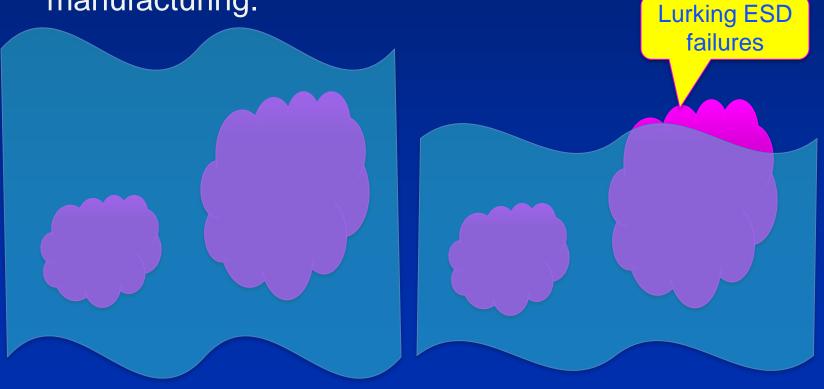

# **Class 0 Exposes Issues**

- Lower water level exposes boulders in a stream.

- Class 000 exposes CDM issues in sensitive device manufacturing.

# ESD Damage A Quality & Reliability Issue

- Catastrophic

- Device failure that is both sudden and complete. It involves complete loss of the required function

- Cumulative

- Device failure resulting from multiple sub-threshold exposures to ESD

- Latent

- Device failure over time due to prior ESD damage

## **Class 0 Risk Technologies**

#### • ICs

- Nanoscale CMOS

- RF

- GaAs

- Optoelectronics

- Lasers

- LEDs

- Detectors (PIN, APD)

- MEMS

- MR Heads

Sylvania Application Notes

## ESDA Technology Roadmap Device Thresholds Are Declining

|       | Average Device Thresholds |       |       |       |       |       |       |       |      |

|-------|---------------------------|-------|-------|-------|-------|-------|-------|-------|------|

| Model | 1975                      | 1982  | 1985  | 1992  | 1998  | 2003  | 2007  | 2013  | 2014 |

| HBM   | 900V                      | 1400V | 2800V | 3800V | 3000V | 2200V | 1500V | 1000V | 750V |

| CDM   | 275V                      | 285V  | 750V  | 800V  | 700V  | 675V  | 625V  | 325V  | 240V |

#### IC Design Target Levels

| Model | 2009  | 2010  |

|-------|-------|-------|

| HBM   | 2000V | 1000V |

| CDM   | 500V  | 250V  |

## **Manufacturing Quality Case Studies**

## Aerospace Manufacturing Case Study CDM Device Failures

#### Background

- No Prior History of ESD Failures

- Multiple CDM Failures Detected

- Triggered Extensive Investigation

- All Manufacturing Locations

- Factory Programs Based on HBM

- Identification and Resolution of Root Cause Major Concern

## Aerospace Manufacturing Case Study CDM Device Failures

Root Cause of Factory Failures Screwdriver Discharge Current Test – 6.7 Amps

- Military ESD Requirements 40 Years Out Dated

- Minimal CDM Controls In Place

- Compliance Verification

Inadequate

- Charged Screwdriver

- Used At Multiple Manufacturing Sites

- Generated Discharge

Currents up to 6.7 Amps!!!

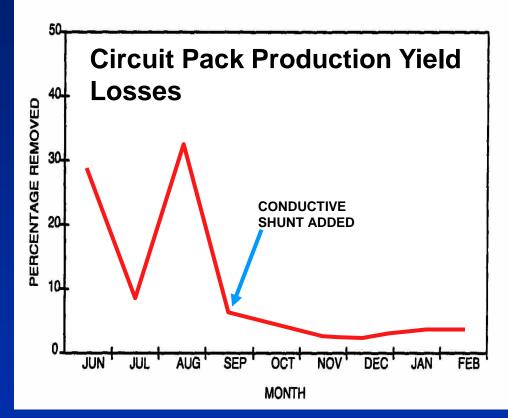

# **Customized Solutions Are Essential** Circuit Board - Class 000 Case Study:

- Design Transfer

- No ESD Data

- 15 Volt CDM Threshold

- 100% Failure Rate: Some Lots

- \$1.2B Sales Jeopardy

- \$1K Invested in Shunt

- \$6.2M/yr Savings Documented

Book: ESD PROGRAM MANAGEMENT Ted Dangelmayer

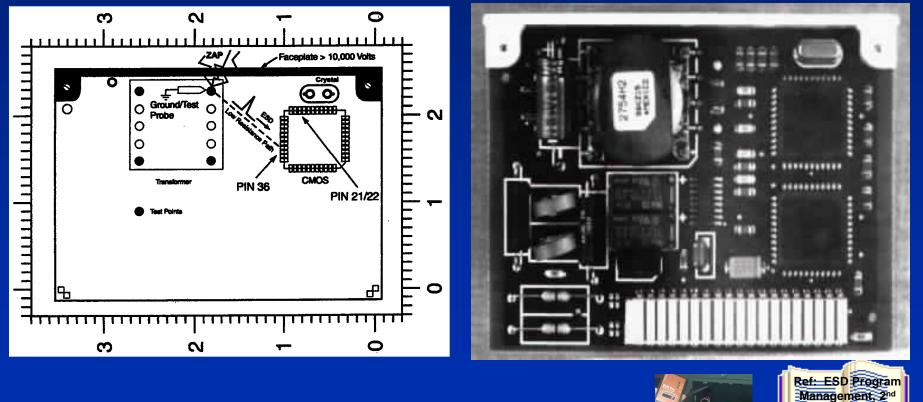

# **Faceplate Field- Induced CBE Failure**

**Established Code - New Faceplate Supplier**

40% Failure Rate - 1.5KV CDM Threshold

Copyright © 2014 Dangelmayer Associates

edition, pp59-61

## Defense Manufacturing: EOS (CBE/CDE) Case Study

- Background Subsystem Assembly Operation

- 12% Circuit Board EOS Failure Rates

- FA Determination by IC Supplier was EOS

- Ungrounded Conveyor System

- Static Generating Carts

- Strong & Persistent ESD Discharge Events

- During Assembly Operations

- Installing Coax Cables

- ESD CBE & CDE Countermeasures Reduced Failures by 80%

## **Strong ESD Events During Assembly** *Charged Product and Cables*

### Class 000 – Wafer Saw Example Unexpected Results!

- CDM Threshold 35 Volts

- 92.2% Defective at Wafer Saw

- Failure Analysis

- CDM Damage

# **Reliability Case Studies**

# ESD Latent Damage A Quality & Reliability Issue

- Bipolar Junction

- 450 Volt HBM Withstand Voltage

- 3 of 15 Failed QA Tests

- 5 of 24 Circuit Boards

Failed after Five Days

- Customer Failures: 17 of 31 Circuit Boards Failed after two Weeks

#### **Latent Failure**

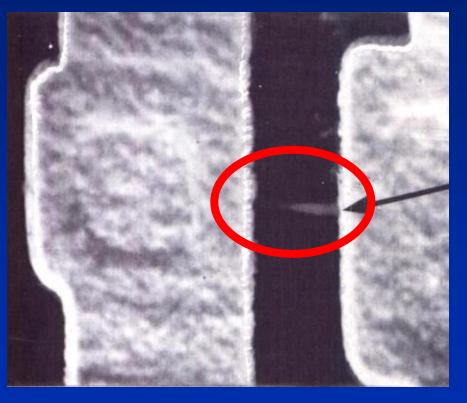

## Defense Manufacturing Case Study Device Classification Error

Background

- MOSFET Device Reclassified as Class 0 HBM

- Triggered Extensive Investigation

- All Manufacturing Locations

- Latency Major Concern

- Analysis Indicated Latency Risk Not Significant

For HBM

### HBM Voltage Distribution with Basic S20.20 Controls in Place

Copyright © 2014 Dangelmayer Associates

p25

# **System Reliability**

# **System Level ESD Upsets**

#### ESD Generates <u>Radio Waves</u> That Affect Microprocessors

- Scrambled Program Instructions and Data

- Microprocessor Lockup

- Confusing Error Messages

- "Software Errors"

## Product Design Reliability Case Study: Lightwave Transmission System

- Multi-million Dollar Lightwave System

- No Design Transfer Verification Of ESD/EMI Protection

- Three Years Apparently Successful Deployment

- Then:

- Major Alarms

- Customer Complaints

- Major Alarms W/O Direct Equipment Contact

- Forced To Remove Bays

- 1 \$B Lost Sales

#### Medical Reliability – System Level Case Study: Tinnitus Treatment Device

#### Background

- Failures In The Field And Lab

- **Production Stopped!**

- Test Methods

- Electrostatic Tribocharging

- ESD When Plugging Headphones Into Charged Unit

- Measuring Current When Plugging In Headphones

- EMI Susceptibility Using ESD Gun

- Failure Level Increase With Ferrite Core

- ESD/EMI Susceptibility With Power Cord

- ESD Gun To Metal On Headphones

- Staticide Treatment Of Plastics

Medical Reliability – System Level Case Study: Tinnitus Treatment Device

## Summary of problems found

- ESD: severe tribocharging of plastic body combined with metal contact when plugging in headphones results in critically severe ESD event that upsets unit

- ESD: Spark to metallic part of headphones upsets unit

- EMI Susceptibility: headphones act as an antenna that picks up radiation from nearby spark and upsets internal circuitry

- Processor is susceptible to ESD/EMI upset 100% of the time, because it is never really turned off. This is highly undesirable from an ESD/EMI susceptibility point of view

p32

ESD testing degraded performance of protection devices

Copyright © 2014 Dangelmayer Associates

#### Medical Reliability – System Level Case Study: Tinnitus Treatment Device

## Solutions

- Product Design Changes

- Reduce tribocharging of unit to safe level

- Prevent ESD spark from occurring between headphone and metal ring of jack

- Static dissipative material on jack or headphone plug

- Add impedance between headphone and VLSI IC

- Ferrite core, series resistance or inductance

- Shunt ESD current from headphone to ground plane of PCB

- Diode, etc

- Improve ESD robustness of VLSI input pins

- Current Reconstruction Scanning Most Definitive

Analysis

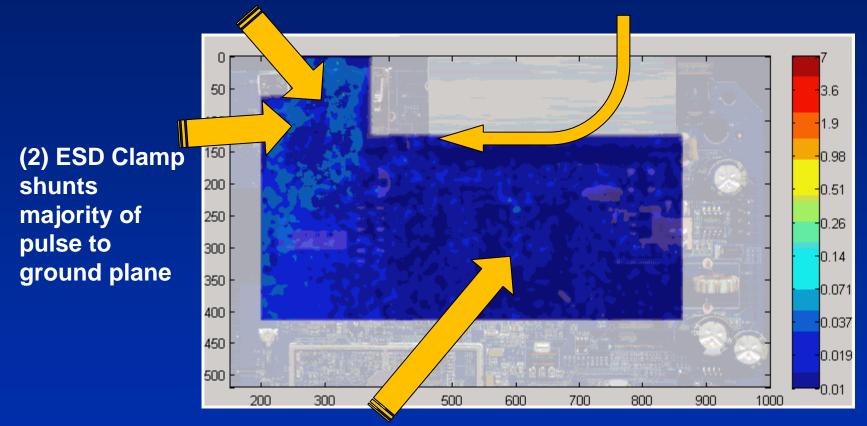

#### Example of USB strike causing Ethernet soft error...

#### (1) ESD pulse is injected into USB port (Units in A/m)

(4) Some energy coupled into nearby nodes (Ethernet port) causing upset

(3) Residual Current shunted by clamps inside ASIC

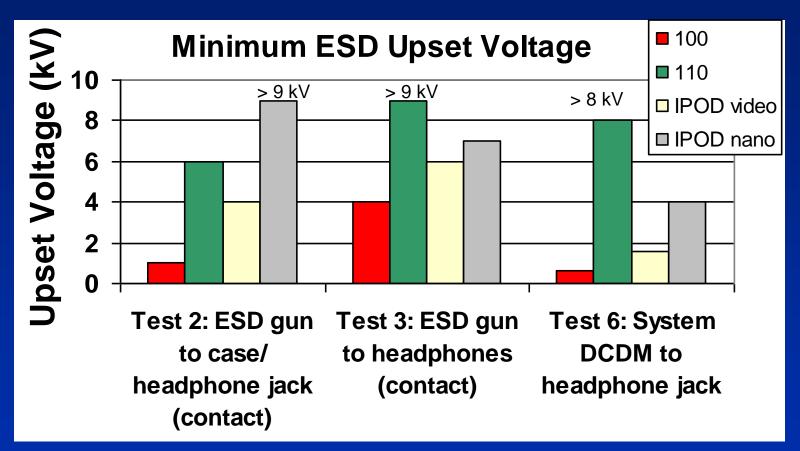

# **Tinnitus Unit vs. IPOD Comparison**

- Significant improvements in 110 processor

- Passes Level 2 (>4kV failure level)

#### **MR Head Class 0 Case Study**

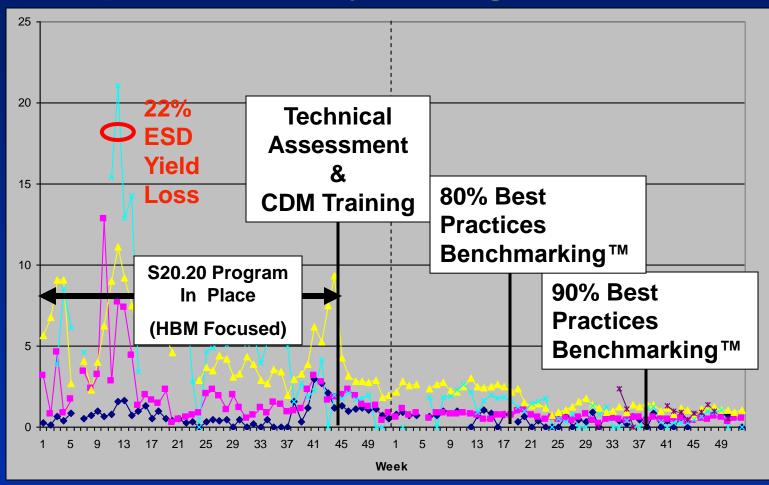

## S20.20 Class 0 Limitations and Yield Improvements by Adding CDM & CDE

Note: Courtesy Herald Datanetics Itd. - 1<sup>st</sup> Class 0 Certified Manufacturing Operation http://www.dangelmayer.com/class-0-certification.php Each data point is confirmed ESD damage during production (typically 65 volt CDM/HBM ESD sensitivity) and different colors represent different products.

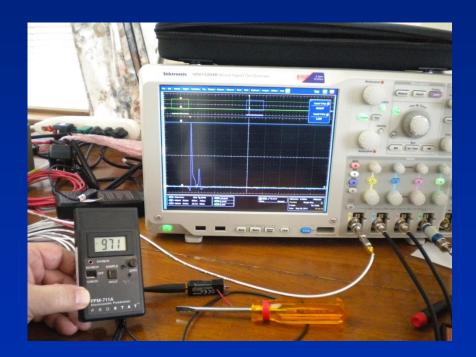

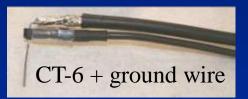

# **Test Equipment Review**

Measuring Current Transients

Current Probe: Tektronix CT-6 (2ghz Bandwidth)

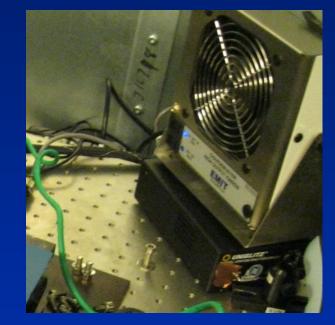

# Measuring EMI From Sparks Credence EM Aware With Data Acquisition System

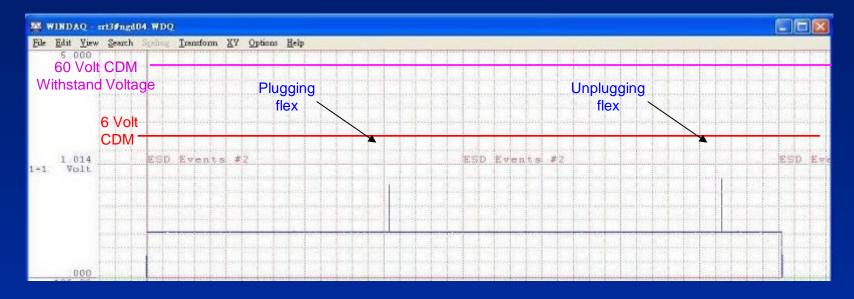

# Example: Setting Maximum Acceptable V, I for Class 0A

### CDM ESD Sensitivity

- 60 Volts

- 100 Ma

#### Manufacturing Specification(1/10th Failure Level)

- Current Transients: ≤ 10 Ma

- EMI: No Event Over 6 Volts CDM

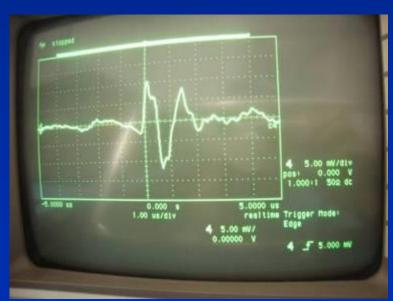

## SRT Test Set Current Probe Measurement

#### Connector

#### **Continuous Contact**

Maximum current: 2mA Horizontal: 1us/div Vertical: 5mV/div Trigger: 5mV

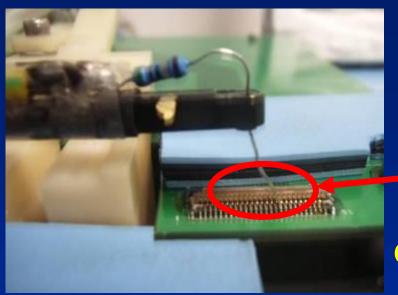

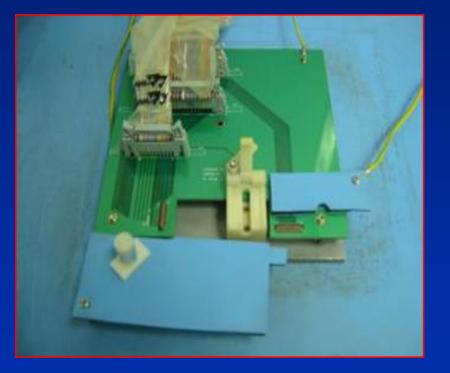

## Class 0A – Customized Solution Special Operating Procedure (SOP)

#### **MR Head Test Fixture**

#### SOP

- Dissipative Touch Pad For Flex Connector

- At Same Elevation As Test Socket

- Ground Flex Connector

To Touch Pad For

4 Sec. Prior To Test

# SRT Current Probe Test Result Before/After New SOP\*

| Equipment | Transient Current (mA)<br>at connector pin |         |  |  |  |

|-----------|--------------------------------------------|---------|--|--|--|

|           | Before                                     | After   |  |  |  |

| SRT #3    | 60-200                                     | 2.0-2.5 |  |  |  |

| SRT #4    | 50-180                                     | 2.0-2.3 |  |  |  |

| SRT #5    | 50-180                                     | 1.0-1.5 |  |  |  |

#### \*Special Operating Procedure

# MR Head Process Improvement Correlated ESD/EMI Test Result

# Class 0A ESD Engineering Requirements (1/10<sup>th</sup> of Thresholds) Satisfied With Margin to Spare

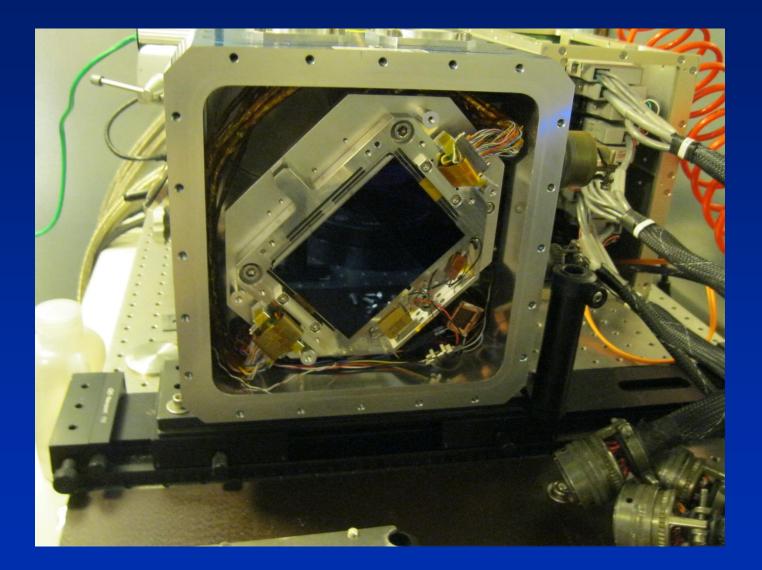

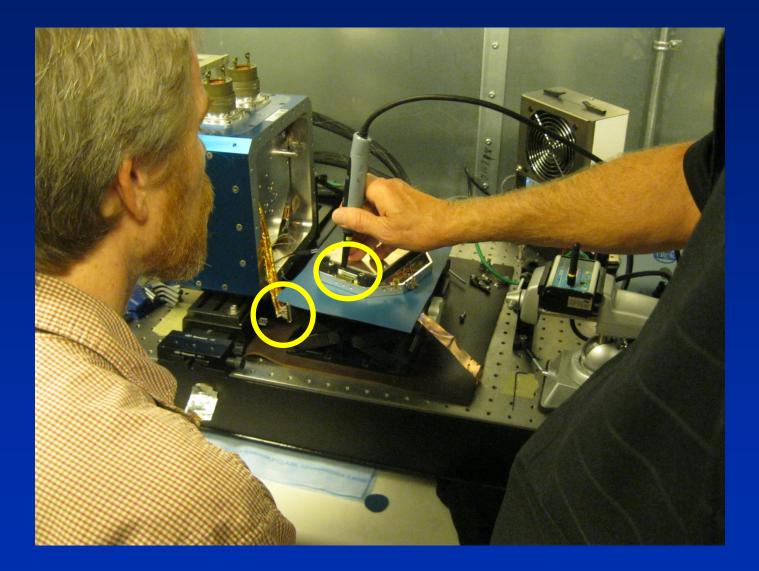

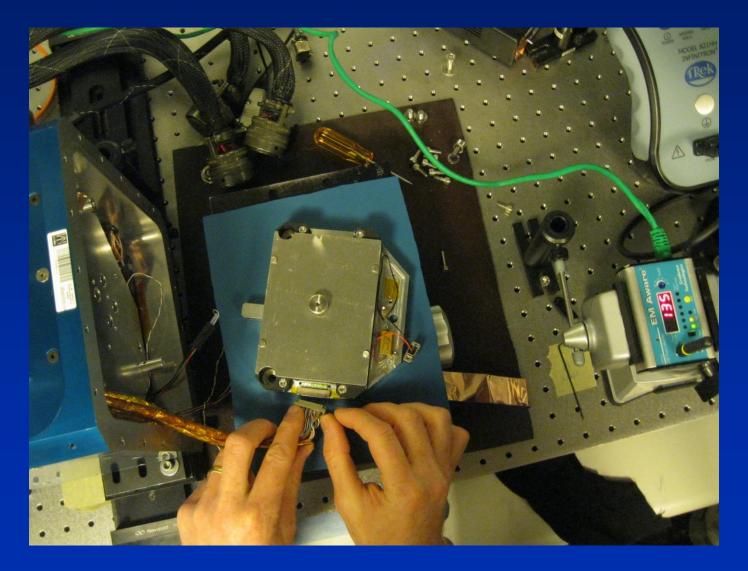

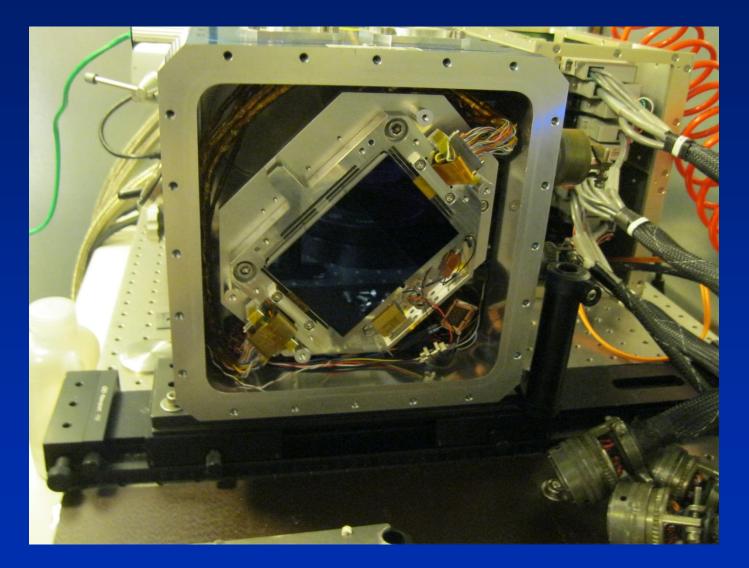

### Gemini Telescope Class 0 Case Study Background

- Objective: Replace 3 CCD Arrays

- \$175,000 Each Array

- First Two Damaged with ESD

- Obtained Expert Advice and Guidance

- To Prevent Further ESD Damage

### **Gemini Dewer**

#### **Contact Voltmeter Measurements** *Objective: Every Pin Prior to Contact - Less that One Volt*

### Class 000: Ionization Gun Essential Tool DC Ionizing DC Bench Gun Ionizer

Essential for Lowering Pin Voltages below 1 Volt

1 Second Decay Rates Insufficient for Pin Voltage Reduction

### **Event Free Insertion**

**Every Pin Prior to Contact - Less that One Volt**

### **Successfully Installed CCDs** ESD Event Free – No ESD Damage!

# Questions

Contact information: Ted Dangelmayer Terry Welsher 978 282 8888 ted@dangelmayer.com

# **Automation Case Studies**

# Far More Complex!

### 200 Volts on Device Evaluate Risk With Event Detection

# 200 Volts: No ESD Events Above 10 Volts

### **30 Volts on Device** Evaluate Risk With Event Detection

#### **30 Volts on Device** ESD Events Detected – Must Determine Source!

# **Automation Video Class Exercise**

### **Test Handler – Multiple ESD Events** Including Double Jeopardy & Class 0A Devices

### **SMT ESD Events Common Issue** *Must Locate & Eliminate Risk for Class 0*

### ESD Events in Glove Box Common Issue High Risk For Class 0A

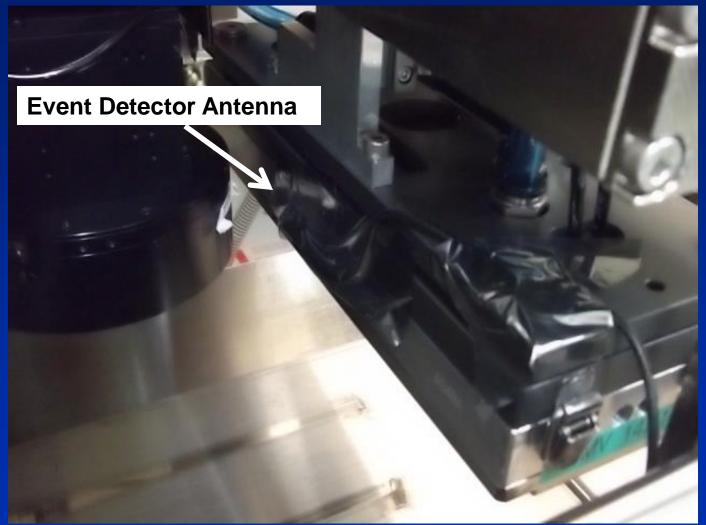

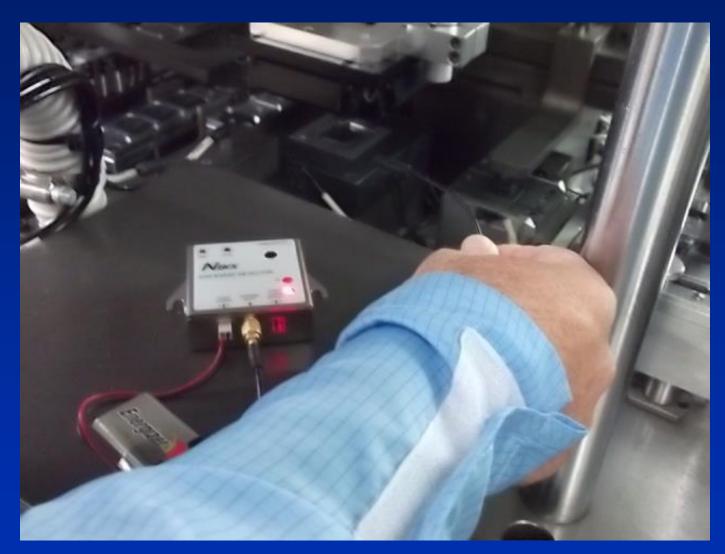

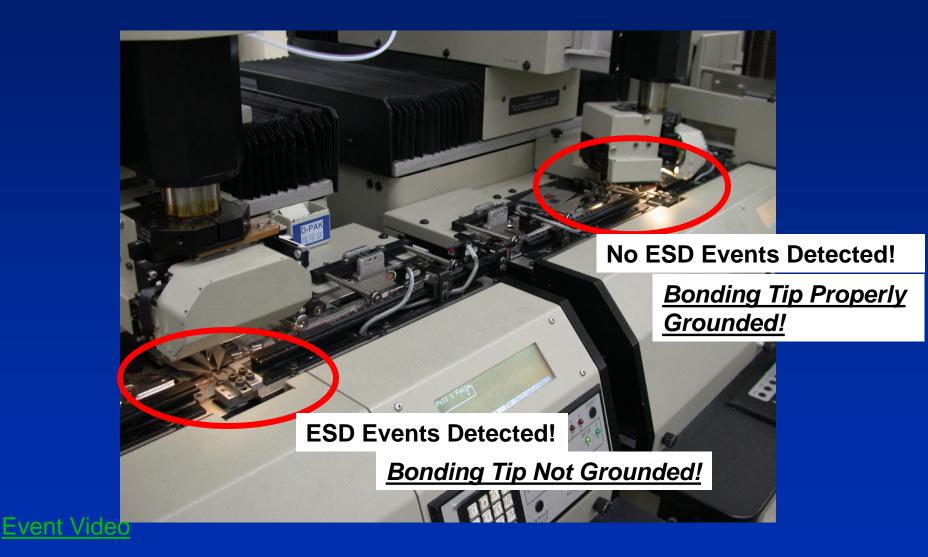

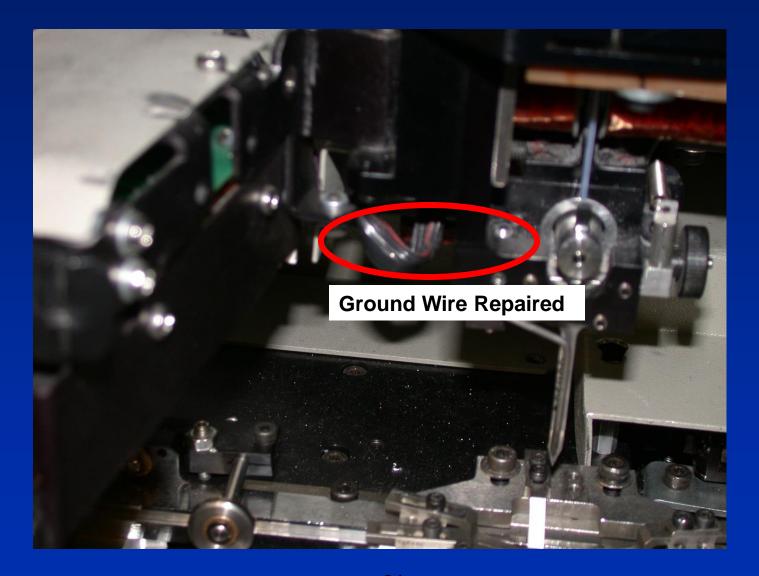

### Proper Grounding Essential ESD Event Detection Good Analytical Tool

#### **Event Corrective Action — Repaired Grounding**

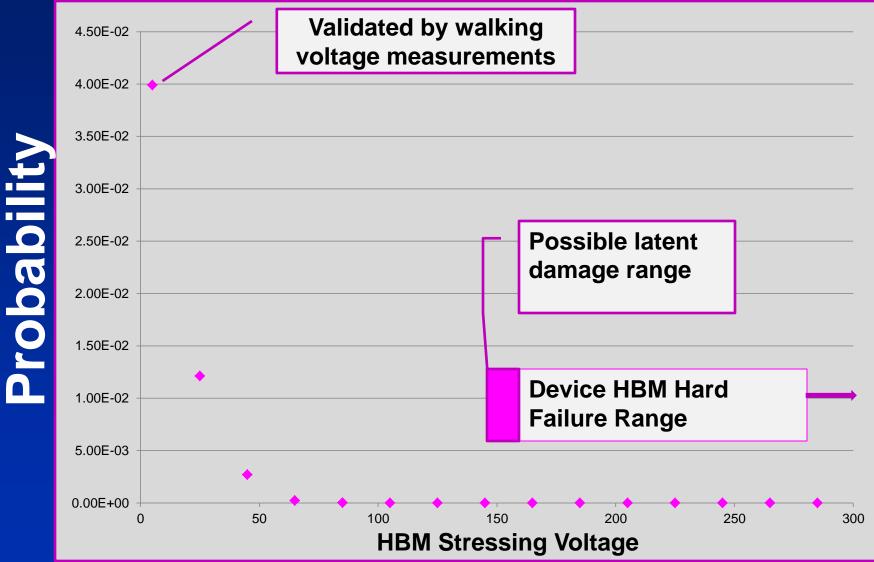

#### An Example: <u>HBM</u> Latency Risk for MOSFETS:

#### Generic MOSFETs do display latent effects of sub-threshold events.

- Literature studies show significant damage only when pulses are within about 5-10% of the threshold (See Tunnicliffe et al J. Electrostatics 1993)

- Even then multiple pulses are typically required to produce the latent damage sites

- Normal HBM ESD precautions typically keep voltages well under 5 volts

- Excursions from normal are *highly unlikely* to produce damage in the latency region without also causing catastrophic damage to some parts.

- Thus, latency risk should track HBM ESD dropout risk

- If no HBM ESD failures have been observed it is highly likely that no latent damage has occurred as well

- If HBM failures have been observed, the risk of latency is the about the same regardless of which handling method is used.

### Steps Taken To Resolve Yield Losses Cost of Implementation = \$335,000 (That Did Not Work!)

- Enhance ESD Training

- ESD Flooring & Footwear

- ESD Chairs, Garments, Carts

- Room Ionization & Bench Top Ionizers

- Constant Wrist Strap Monitors

- Daily SPC to Ensure Compliance to Procedure

- Dissipative Handling Materials & Containers

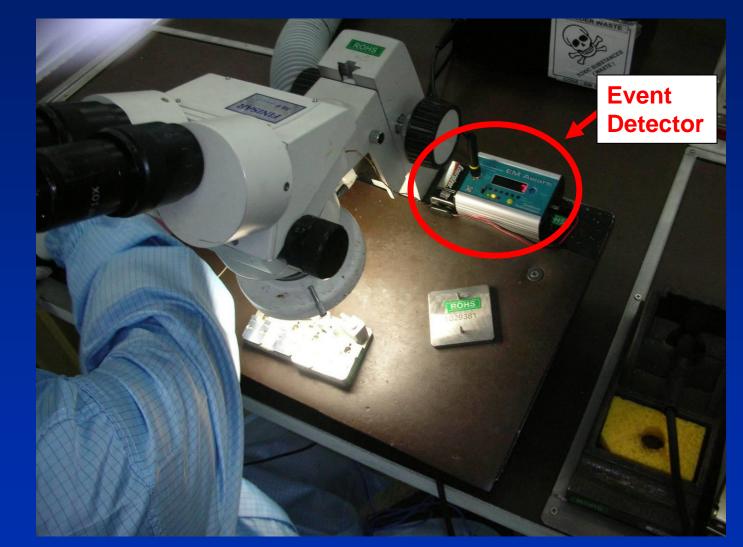

#### **Event Detectors Useful for Workstation Analysis**

Photo Courtesy Dangelmayer Associates Copyright © 2014 Dangelmayer Associates

Video

### **Grounded Springs Added to Conveyor** *to Ground ESD Product Trays*

### **ESD Events Due to High Charging Carts**