# Intellectual Property Key Ingredients.....

W. Tonti IEEE Sr. Director IEEE Future Directions *w.r.tonti@ieee.org*

1

#### A TUTORIAL WALK THROUGH A PATENT

US 5,798,553 Issue Date: 8/25/1998 TRENCH ISOLATED FET DEVICES, AND METHOD FOR THEIR MANUFACTURE

### A TUTORIAL WALK THROUGH A PATENT

### OUTLINE OF PRESENTATION:

- POTENTIAL PATENTS

- REQUIREMENTS FOR OBTAINING A PATENT

- EXEMPLARY PATENT US 5,798,553

- OVERVIEW OF PROBLEM TO BE SOLVED

- THE SOLUTION

- COMMENTS ON PATENT

- MY PERSPECTIVE OF FACTORS CONDUCIVE TO SUCCESSFUL INVENTING

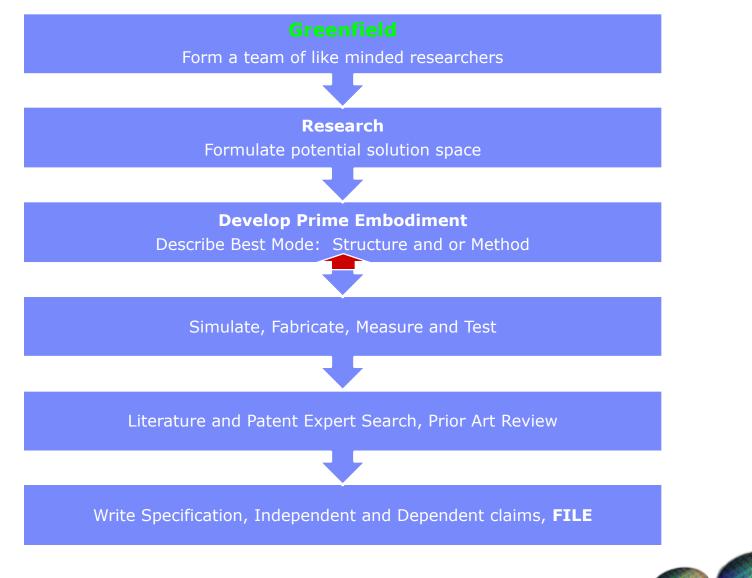

## The Process of Inventing: New Space, Base Tech – Think Tank

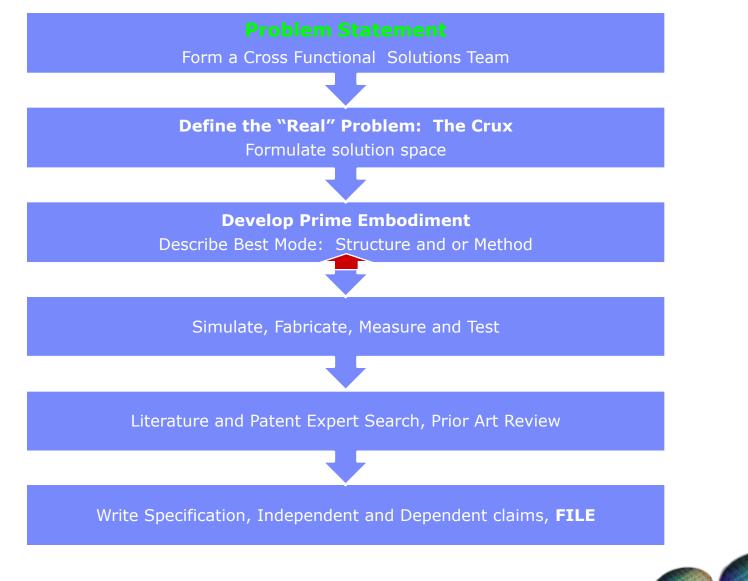

## The Process of Inventing: Solving a Problem, Cross Functional Team

- PROGRESS IN TECHNOLOGY DEVELOPMENT IS IMPEDED BY <u>PROBLEMS</u> ENCOUNTERED ALONG THE WAY

- UNANTICIPATED APRIORI

- <u>SOLUTIONS</u> ARE REQUIRED TO ACHIEVE THE GOALS OF A PROJECT

- → FERTILE GROUND FOR INVENTING

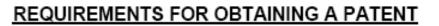

TO OBTAIN A PATENT, AN INVENTION MUST BE:

- NEW

- USEFUL

- NON OBVIOUS

## **The Patent Process**

- Solution of an existing problem

- Identifying elements for a future roadmap

- Leverage your strengths

- Form a team

- Everyone is a contributor, no idea is bad

- ✤ Write it down.....

- For me ideas come at night. Have a pad nearby.

- A picture really is worth 1000 words

## Where do you search for Prior Art?

- ✤Two main sources of IP

- IEEE Xplore

- US patent database

- ♦ Why bother searching?

- It is required.

- Your claims will be modified based on what you uncover.

- More often than not prior art will sharpen your own submission.

## Transistor

Four Terminal Switch, A Field Effect Device Minority Carrier Current flows from (Source to Drain) Requires a potential to invert the surface (Gate) Common Substrate Connection

Fundamental design criterion: Built in potential  $\phi_B = [kT/q] Ln(N/N_s)$

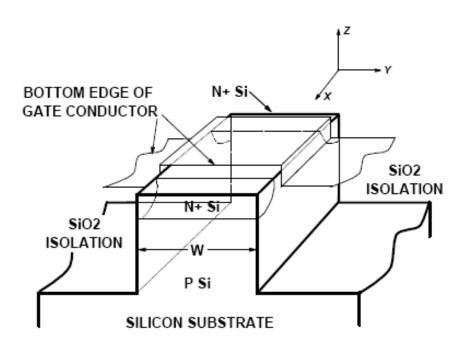

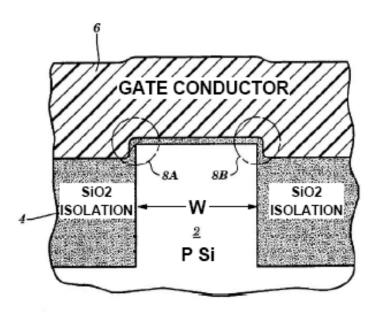

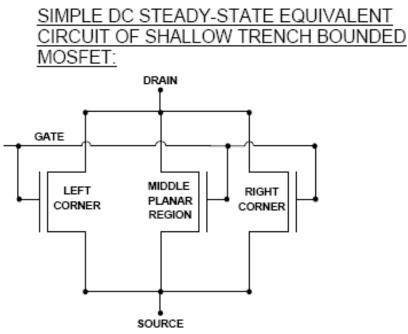

#### OVERVIEW OF PROBLEM TO BE SOLVED US 5,798,553

#### PROBLEM STATEMENT:

HOW CAN THE CHANNEL CURRENT CONTRIBUTED BY THE SILICON CORNER OF MOSFETS BOUNDED BY SHALLOW TRENCH ISOLATION (STI) BE MINIMIZED?

CHANNEL CURRENT IS IN THE "x" DIRECTION

#### OVERVIEW OF PROBLEM TO BE SOLVED US 5,798,553

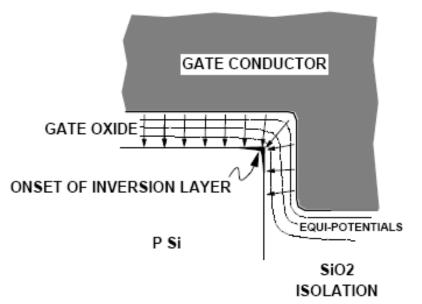

CROSS-SECTION NORMAL TO CHANNEL CURRENT:

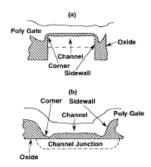

FIG. 1

FOR EQUAL DOPING CONCENTRATION, THE THRESHOLD VOLTAGE (Vt) AT THE SILICON CORNERS (8A, 8B) IS LOWER THAN AT THE MIDDLE PLANAR REGION

- WHY?

Figure 11. Cross section through the width of a MOSFET isolated by shallow trench dielectric.

#### OVERVIEW OF PROBLEM TO BE SOLVED US 5,798,553

#### ELECTRIC POTENTIALS AND FIELDS IN THE VICINITY OF THE SILICON CORNER:

- ELECTRIC FIELD IS STRONGEST AT THE SILICON CORNER

- DUE TO SMALL RADIUS OF CURVATURE

- HIGHER CORNER FIELD

→ STRONGER INFLUENCE OF GATE

VOLTAGE ON SI SURFACE POTENTIAL

→ CORNER INVERTS FIRST

→ Vt corner < Vt planar</p>

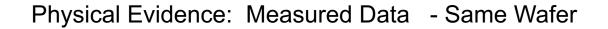

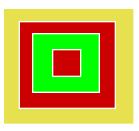

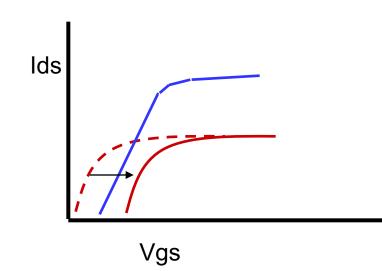

♦ MOS Characteristic of device specifically designed without a corner

(Note, this is NOT a solution!) This design is an annular device ring. Large, leaky, not optimized...

MOS Characteristic standard device design

Figure 2. IV characteristics of SC-PFET. Increased arsenic dose separates corner and channel contribution with a different subthreshold slope. Device geometry W<sub>eff</sub>/L<sub>eff</sub> = 20μm/3μm; bias conditions are V<sub>ds</sub> = -3.6V, V<sub>nw</sub> = 0.0V.

#### OVERVIEW OF PROBLEM TO BE SOLVED

US 5,798,553

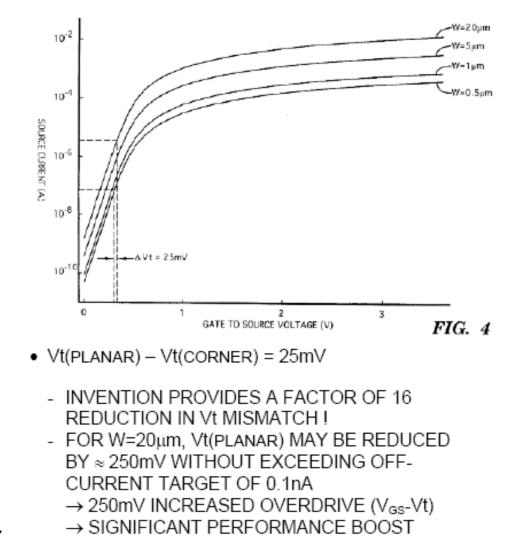

- Vt (CORNER MOSFETs) < Vt (MIDDLE MOSFET) → OFF-CURRENT DOMINATED BY CORNERS

- BUT, EQUIVALENT (ELECTRICAL) CHANNEL WIDTH OF CORNER MOSFETs IS TYPICALLY << PHYSICAL CHANNEL WIDTH OF MIDDLE MOSFET (W)

#### $\rightarrow$ ON-CURRENT DOMINATED BY MIDDLE

- ON-CURRENT ∝ W

- CORNERS CONTRIBUTE NEGLIGIBLY TO ON-CURRENT

OVERVIEW OF PROBLEM TO BE SOLVED US 5,798,553

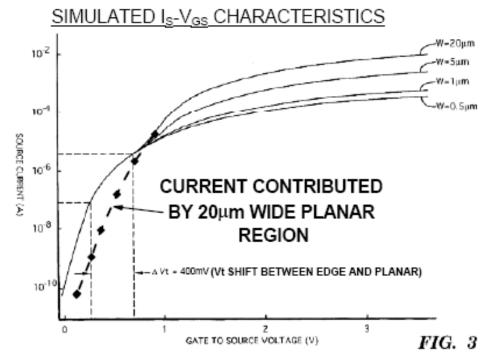

CORNERS DOMINATE OFF-CURRENT (V<sub>gs</sub>=0)

- PLANAR REGION DOMINATES ON-CURRENT (V<sub>gs</sub> > Vt(PLANAR)  $\approx 0.70$ V) FOR TYPICALLY EMPLOYED CHANNEL WIDTHS (W  $\gtrsim 0.5 \mu m$ ) FOR HIGH PERFORMANCE APPLICATIONS

- $Vt(PLANAR) Vt(CORNER) \approx 400 mV$

- PROMINENT KINK IN CHARACTERISTIC

OVERVIEW OF PROBLEM TO BE SOLVED US 5,798,553

- NEED HIGHEST ON-CURRENT FOR HIGHEST PERFORMANCE

- $dV/dt = I_{ON}/C_{LOAD}$

- NEED LOWEST OFF-CURRENT FOR LOWEST STANDBY POWER

- LOW POWER (BATTERY) APPLICATIONS

- → MUST MINIMIZE CORNER CURRENT

- CORNER CURRENT INCREASES STANDBY POWER WITHOUT CONTRIBUTING TO PERFORMANCE

#### <u>OR</u>

- HIGHER OVERALL Vt's REQUIRED TO MEET STANDBY POWER TARGET DEGRADES PERFORMANCE

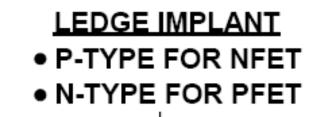

- INVENTION SEEKS TO SUPPRESS CORNER

CURRENT WITHOUT DEGRADING CURRENT

FROM MIDDLE PLANAR REGION

- MAKE Vt (CORNER) ≥ Vt (PLANAR REGION)

- SELECTIVELY INCREASE CHANNEL DOPING CONCENTRATION AT THE CORNERS BUT NOT AT THE MIDDLE PLANAR REGION

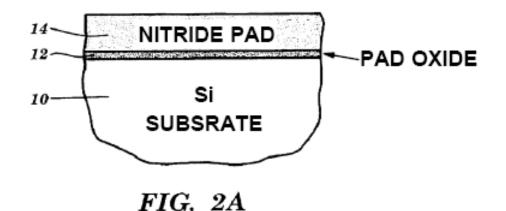

THE SOLUTION US 5,798,553

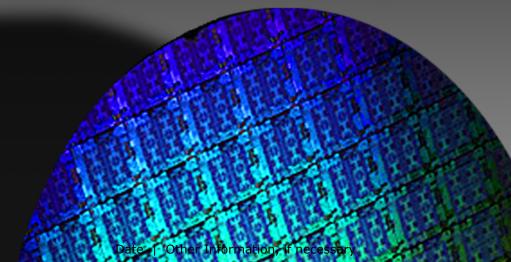

- STARTING WITH A STANDARD MONOCRYSTALLINE SILICON SUBSTRATE (WAFER)

- THERMALLY GROW A THIN (PAD) OXIDE

- DEPOSIT A SILICON <u>NITRIDE PAD</u> LAYER BY CHEMICAL VAPOR DEPOSITION (CVD)

- USING A PHOTORESIST MASK (NOT SHOWN), ETCH A SLOT THROUGH THE NITRIDE PAD

- USE OF AN ANISOTROPIC (DIRECTIONAL) REACTIVE ION ETCH (RIE) FOR SIN SELECTIVE TO SIO2

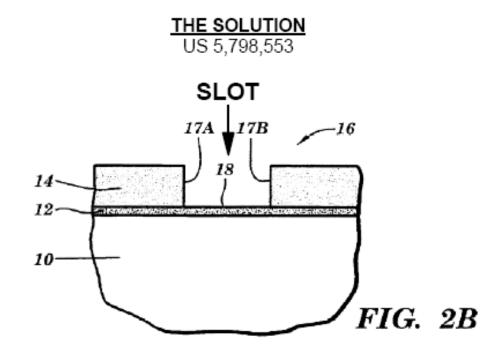

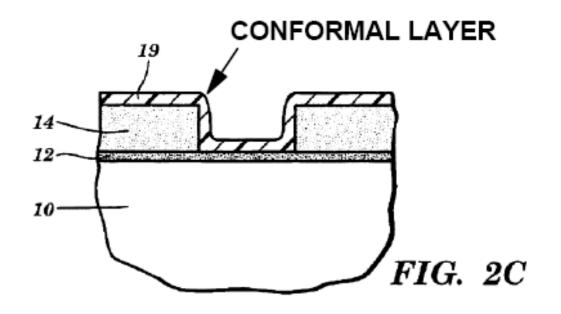

THE SOLUTION US 5,798,553

- DEPOSIT A CONFORMAL LAYER

- e.g. CVD SiO2, OR A POLYMER

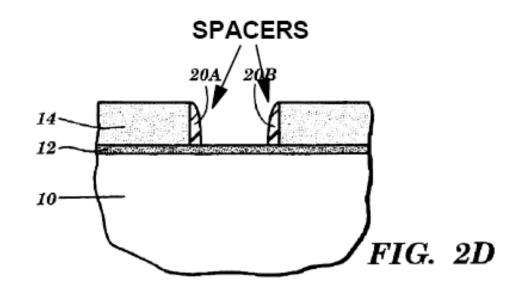

THE SOLUTION US 5,798,553

- USE A REACTIVE ION ETCH (RIE) TO DIRECTIONALLY ETCH THE CONFORMAL LAYER

- ETCHES HORIZONTAL SURFACES MUCH FASTER THAN VERTICAL SURFACES

- → FORMS SIDEWALL <u>SPACERS</u> IN SLOT

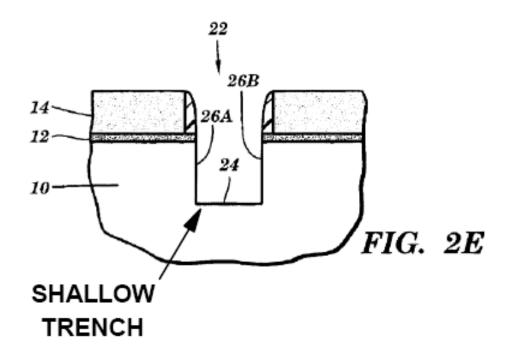

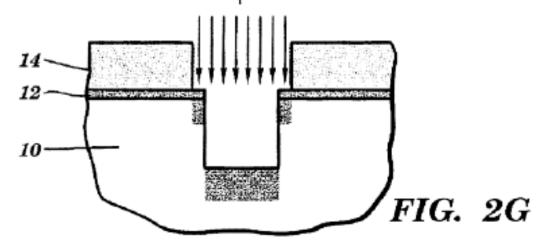

## THE SOLUTION

US 5,798,553

- USE A REACTIVE ION ETCH (RIE) TO DIRECTIONALLY ETCH THROUGH THE REMAINING PAD OXIDE LAYER (12)

- USE A SILICON RIE (CHANGE ETCH CHEMISTRY) TO DIRECTIONALLY ETCH SHALLOW TRENCHES (24) INTO SILICON

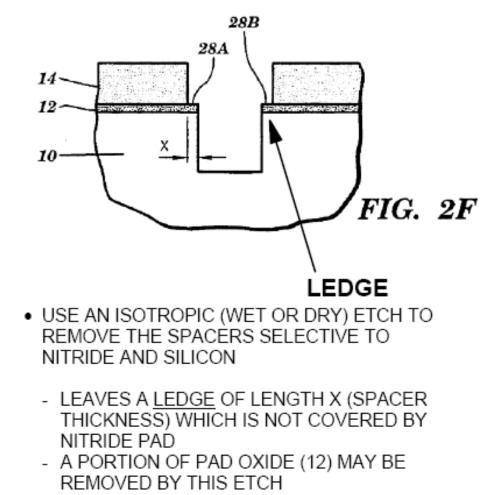

THE SOLUTION US 5,798,553

## SPACER REMOVAL

- ION IMPLANT THE LEDGE

- SELECTIVELY DOPES EDGE HIGHER THAN MIDDLE PLANAR REGION

- RAISES Vt (CORNER) ≥ Vt (PLANAR)

## THE SOLUTION

US 5,798,553

#### SIMULATED IS-VGS CHARACTERISTICS

### COMMENTS ON PATENT US 5,798,553

#### WHAT IS NEW?

WHAT IS USEFUL?

WHAT IS NON OBVIOUS?

#### Impact of Shallow Trench Isolation on Reliability of Buried- and Surface-Channel sub-µm PFET

William Tonti<sup>\*</sup>, Ronald Bolam IBM Microelectronics Division Essex Junction, Vermont 05452 \* (802) 769-6561 (Fax 6567) wtonti@btvlabvm.vnet.ibm.com

> Wilfried Hänsch SIEMENS Components Incorporated c/o IBM Microelectronics Essex Junction, Vermont 05452

#### Abstract

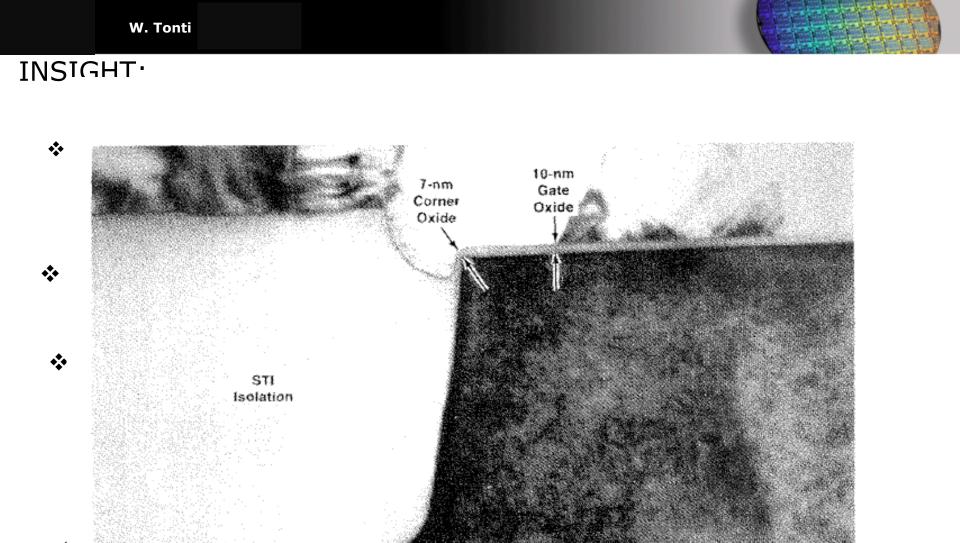

Shallow trench isolation exhibits all the required isolationtechnology properties for ULSI [1]. Its high degree of scaleability relies on the fact that its lateral (isolation width) and vertical (isolation depth) dimensions are decoupled due to an almost-ideal box-shape profile of the isolation (Figure 1). A consequence of the abrupt device edge is that a parasitic drain-to-source leakage path can exist at the corner and along the trench sidewall. This paper describes degradation mechanisms of surface-channel (SC) and buried-channel (BC) PFET devices that are directly related with a corner and sidewall parasitic leakage. Both parasitic regions show a characteristic degradation behavior that can limit device reliability for PFETs in the sub-µm regime. The necessary processing conditions that overcome this limitation are also given.

#### Introduction

The effects of hot carrier degradation on P-channel device characteristics become more important as MOSFET dimensions continue to shrink [2,3,4]. Electron charge trapping and interface state generation are the main contributors to the degradation [5]. This results in a positive threshold shift and an increased source-to-drain drive current.

To improve circuit performance, scaling the device active area and isolation is essential. Reducing channel length and oxide thickness increases drive current capability. The reduced oxide thickness improves the subthreshold slope which, in turn, reduces the device off current ( $I_{\rm th}$  at  $V_{\rm gs}$ =0.0V). This scaling trend is essential for today's low-power MOSFET operation requirements.

Shallow trench isolation (STI) provides additional leverage by reducing the isolation feature size; however, a reliability mechanism related to the isolation properties can increase the device off current. A localized hot carrier degradation at the STI-drain-gate region reduces the expected scaling improvement. Figure 1 depicts a two-dimensional cross section, where the drain of the MOSFET would be located in the third dimension. Traditional hot carrier degradation could occur in this dimension and device damage would result [4]. The damaged region would be located along the third dimension bordering the drain, corner and polysilicon gate intersection. The hot carrier mechanism adversely affects drain leakage currents along the boundary; the consequence of hot carrier degradation in subthreshold operation for SC and BC PFET devices are discussed in this paper.

Figure 1. (a) A cross section through the width of a shallow trench bounded MOSFET. The dashed line is the location of the BC-PFET channel junction. The poly recess at the device edges is the gate wraparound. (b) is the equivalent planar structure of (a).

#### Experiment

To investigate edge hot carrier degradation in STI isolation, we used buried-channel and surface-channel PFETs with a gate oxide thickness of 10.0nm and optimized design lengths of 0.4µm and 0.3µm, respectively [6]. Both devices shared the same N-well in an N substrate and followed the same process sequence: formation of shallow trench isolation, well implants, gate oxide, N+ polysilicon gate electrode, and source-drain diffusions [7]. The substrate doping concentration was ≈1.0×1016 cm13. An N-well mask was used to implant the field tailor and anti-punch through doping through a screening oxide into the channel and isolation regions. A second threshold voltage compensation mask was used to independently adjust the surface concentration in the respective channel regions of these devices. The device threshold characteristics were set by using the compensation mask to vary an arsenic threshold-tailor implant for the SC-PFET and a boron implant for the BC-PFET. The resulting buried-layer junction depth for the BC-PFET was

### Can you Publish?

### File Date: 9/16/1997 Issue Date: 8/25/1998

21

- COLLABORATIVE EFFORT

- NOT FOR LONERS

- TEAM WITH COMPLEMENTARY SKILLS

- SYNERGISM→SPARKS NEW IDEAS

- BROAD PERSPECTIVE OF THE ART

- IMPROVES WITH EXPERIENCE

- THE RIGHT OPPORTUNITIES

- CHALLENGING PROJECTS

- BLESSINGS OF MANAGEMENT

- A PASSION FOR SEEKING SOLUTIONS

- PERSISTENCE

- DOGGED DETERMINATION

- WILLINGNESS TO PURSUE OUTRAGEOUS IDEAS

- PARADIGM SHIFTS

|       | W. Tonti    |  |

|-------|-------------|--|

| Ackno | wledgements |  |

I would like to acknowledge my co inventor and long time friend Dr. Jack Mandelman who has prepared many of the visuals contained in this package.

# **Questions ?? Ask The....**

William Tonti w.r.tonti@ieee.org 802 238 5401

Date Other Information, if necessary