### **Application of X2Y Capacitors in Power Delivery Networks**

### Steve Weir IPBLOX, LLC Presented to IEEE RTP Chapter April 1, 2008

GROUP AFFILIATE

Page I

© 2008, IPBLOX LLC, All Rights Reserved

## **Property Rights Disclosure**

#### "PROPERTY OF IPBLOX LLC"

Information contained in this document is not to be reproduced in any form without permission of IPBLOX LLC. Any information in this document is proprietary and may not be used or disclosed without the express permission of IPBLOX LLC.

#### **"CONFIDENTIAL PROPERTY OF IPBLOX LLC"**

This document includes valuable trade secrets. Unauthorized disclosure of use of this document may violate the Uniform Trade Secrets Act.

#### Getting a Handle on PCB Power Delivery

- PCB Power delivery is dominated by:

- Inductance

- Limits useful frequency range of each PDN element

- Resonance

- Sets worst case noise

#### Getting a Handle on PCB Power Delivery

- Inductance

- Limits performance of *every* PDN component

- Compensated by capacitive component w/ *less* inductance

- Examples:

- -VRM ⇒ Bulk Caps

- Bulk caps ⇒ Ceramic caps

- Ceramic caps ⇒ Power cavity

#### Getting a Handle on PCB Power Delivery

- Resonance

- Occurs wherever a large phase transition ( >135° ) occurs in the PDN transfer function

- Typical: Inductive Z<sub>MAG</sub> crosses capacitive Z<sub>MAG</sub>

- Magnitude depends on Z<sub>CHAR</sub>, and Q- both increase w/ inductance

- Modal occurs at locations and frequencies where reflections from the structure boundaries strongly reinforce

#### **Getting a Handle On Bypass Networks**

- Bypass networks are a source of much confusion:

- Confusion results primarily from misconceptions of spatial behavior of the planes

### **PDN Impedance**

- At least two impedances:

- Impedance seen by any particular load

- Plane cavity spreading inductance limits

between IC power via attach and bypass cap attach

- Distributed impedance presented to composite loads

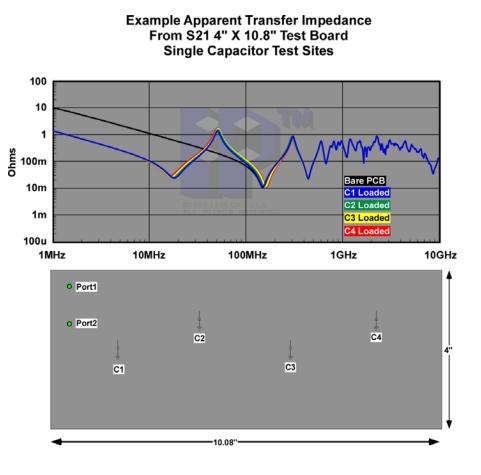

#### Plane Impedance from S21 One Cap at a Time

- Receive port S21 represents port to port insertion loss

- Varies w/ position of ports

- Distorted by series loss:

- Plane L/R looks like lower shunt Z

- Cap position doesn't seem to matter

- This is a fallacy

Page 8

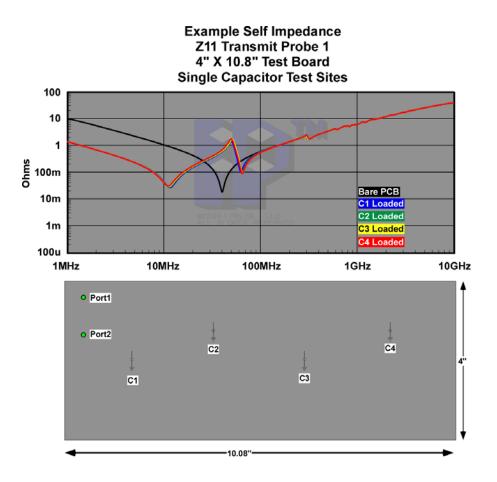

## Plane Impedance from Z11?

- Single Port

- Plane spreading inductance dominates

- Probing awkward

- Can be derived from S21 w/ probes on either side of PCB

- Tells the truth ( sort of )

- About attachment the size of the probe ports only

- Spreading inductance varies little from small probe radius to distant caps

© 2008, IPBLOX LLC, All Rights Reserved

### **Power Plane Paradoxes**

- Power cavities are low inductance capacitors:

- Parallel plates, inductance set by cavity height and aspect ratio between ports

- Resonate w/ discrete caps

- $F_{\text{RES}} \approx 1/(2\pi (\text{ESL}_{\text{BYPASS}} * C_{\text{CAVITY}})^{0.5})$

- Power cavity spreading inductance limits HF performance

- Power cavity spreading inductance isolates bypass caps from IC power connections

- Spreading inductance increases logarithmically w/ radius

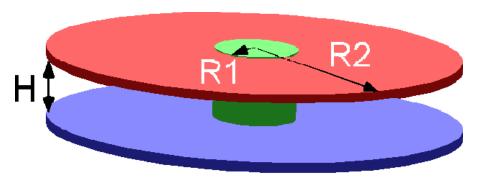

### **Plane Inductive Behavior**

- Incremental impedance from any point decreases linearly with: circumference, radius, time

- Conversely impedance increases linearly w/ frequency, IE inductive transfer function

- Hence planes appear inductive @ HF

Inductance = 5.08nH \* H(inches) \* In(R2/R1) 0.20nH \* H(mm) \* In(R2/R1)

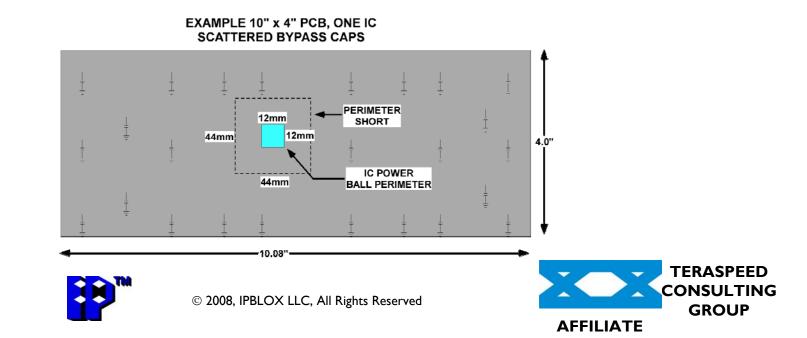

### **IC Point of View**

- IC's typically have multiple power pins spread over some area of PCB

- Much lower spreading L than colinear VNA ports

- Significant sensitivity to capacitor proximity

- Evaluate interconnect w/ perimeter short model

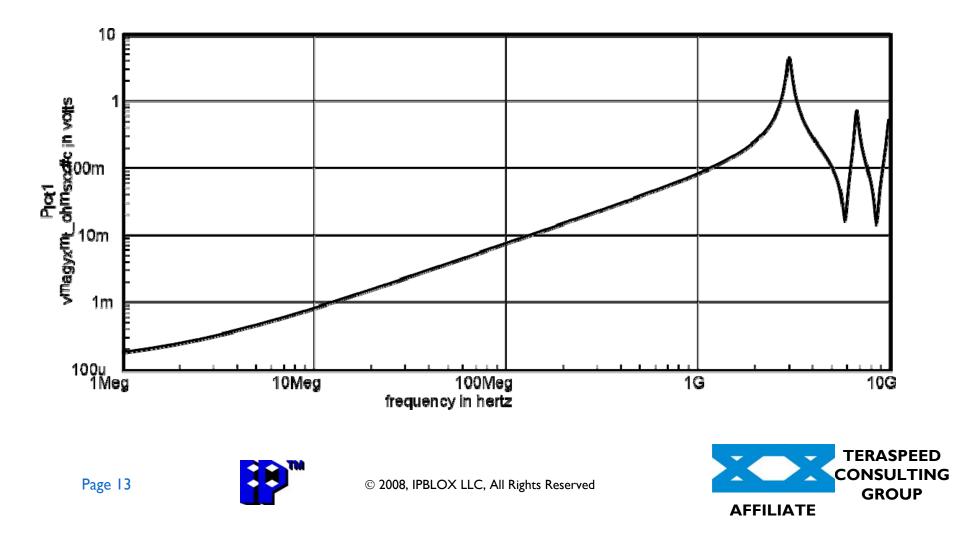

### **Shorted Perimeter Around IC**

• Response very different than single VNA port

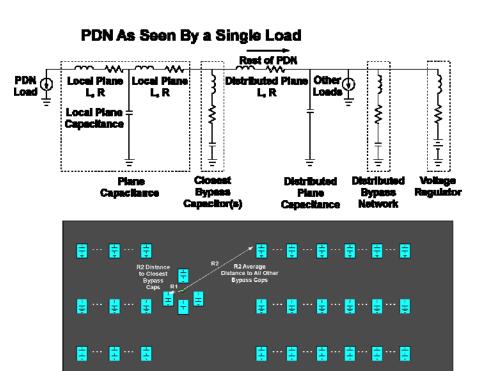

## Simplified PDN Model, Single Load

- To a single load, plane L/R fundamentally limits Z<sub>MIN</sub>

- Current divides between closest bypass caps and rest of PDN through planes

- Closest caps are most important

- Other caps appear through plane spreading inductance / delay

- Spreading inductance beyond closest caps *usually* small

- Depends on dielectric thickness

- Other loads filter through spreading inductance and local caps

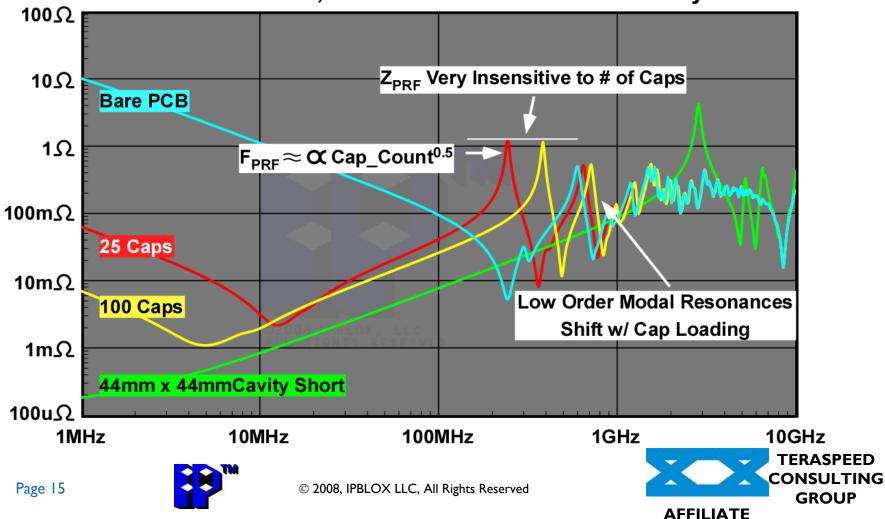

### **Bypass / Cavity PRF**

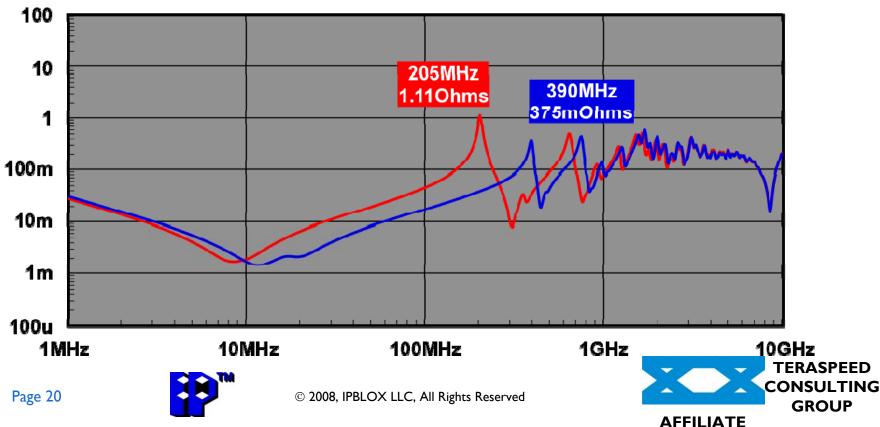

Example ZPRF Insensitivity to # of Bypass Caps 4"x10" PCB, 12mm x 12mm Power Ball Array

# Key Bypass Issues

- Position of bypass capacitors relative to loads does matter

- The distributed inductance of the *bypass network* w/the plane cavity set F<sub>PRF</sub>

- The inductance and ESR of **Each** bypass cap largely sets the  $Z_{\text{PRF}}$  **Independent** of  $F_{\text{PRF}}$

# **Distributed Inductance and F<sub>PRF</sub>**

- Parallel resonance occurs where:

- jwL<sub>BYPASS\_NETWORK</sub> = 1/jwC<sub>POWER\_CAVITY</sub>

- Move resonance by manipulating the bypass network inductance

- The number of caps needed is:

- N<sub>CAPS</sub> = ESL<sub>MOUNTED\_CAP</sub> / L<sub>BYPASS\_TARGET</sub>

- F<sub>PRF</sub> is relatively insensitive to capacitor positions for any practical design

- Assumes capacitors distributed

- F<sub>PRF</sub> only moves as square root of capacitor count

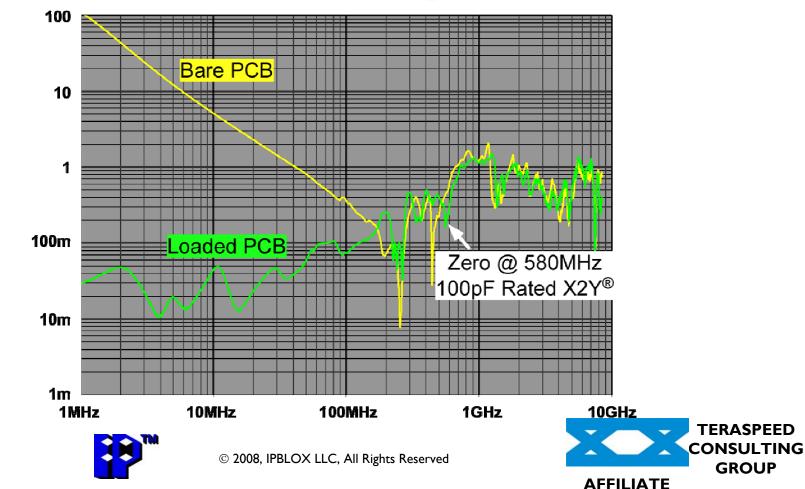

- Loading a PCB w/ bypass caps shifts the lower modal resonances

- First order approximation of undamped PDN peak impedance, Z<sub>PRF</sub>:

- Is independent of the number of capacitors: N

- In practice drops slowly as N drives  $F_{\text{PRF}}$  up due to cavity skin, dielectric losses & capacitor ESR changes

- Is proportional to  $ESL_{MOUNTED\_CAP}/ESR_{CAP}$

- Lower mounted inductance / better caps improve

- Damping can greatly improve

- Combination of lower Q caps and damping very effective

# $Z_{DRF}$ Insensitivity to # Caps

- For high Q networks:

- $-Z_{PRF}$

- Q

- $-Z_{PRF}$

- R<sub>NFTWORK</sub>

- $-Z_{PRF}$

- ≈ Z<sub>CHAR</sub>\*Q •  $Z_{CHAR}$  =  $L_{NETWORK}^{0.5*}C_{CAVITY}^{-0.5}$ • Q =  $jw_{PRF}L_{NFTWORK}$  /  $R_{NETWORK}$  $- jw_{PRF} \approx 1/(2\pi^*(L_{NETWORK}^*C_{CAVITY})^{0.5})$ =  $L_{NETWORK}^{0.5*}C_{CAVITY}^{-0.5}$  /  $R_{NETWORK}$

- =  $L_{\text{NETWORK}} / (C_{\text{CAVITY}} * R_{\text{NETWORK}})$

- $L_{\text{NETWORK}} = \text{ESL}_{\text{MOUNTED CAP}}/N$

- $= ESR_{CAP}/N$

- =  $ESL_{MOUNTED CAP} / (C_{CAVITY} * ESR_{CAP})$

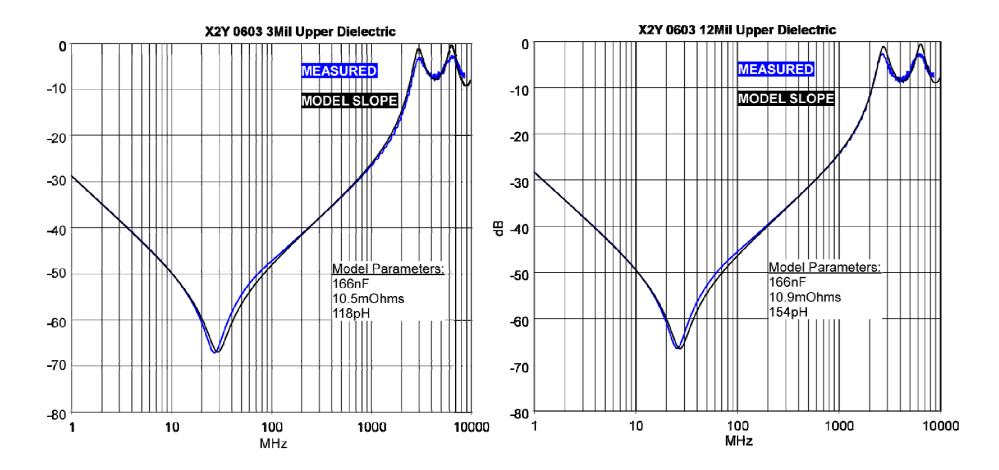

#### Move F<sub>PRF</sub>, Reduce Z<sub>PRF</sub> w/ Lower Q Caps

### **X2Y<sup>®</sup> Low MOUNTED L Caps**

Page 21

© 2008, IPBLOX LLC, All Rights Reserved

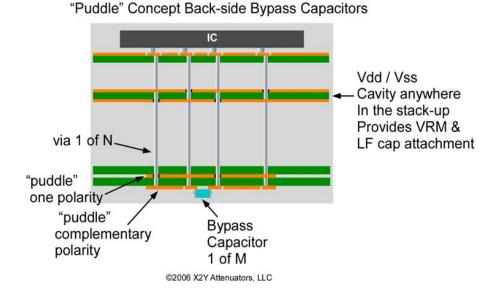

## **Puddle Concept**

- Shares bypass capacitors and vias

- When used for backside caps improves cap utilization and reduces Q

- Backside caps attach-

- To an etch puddle as shown, OR

- An etch ring

- Puddle avoids spreading L

- Locate bypass caps on surface closest to puddle/ring

- Vdd DC distribution on internal layers

Page 22

© 2008, IPBLOX LLC, All Rights Reserved

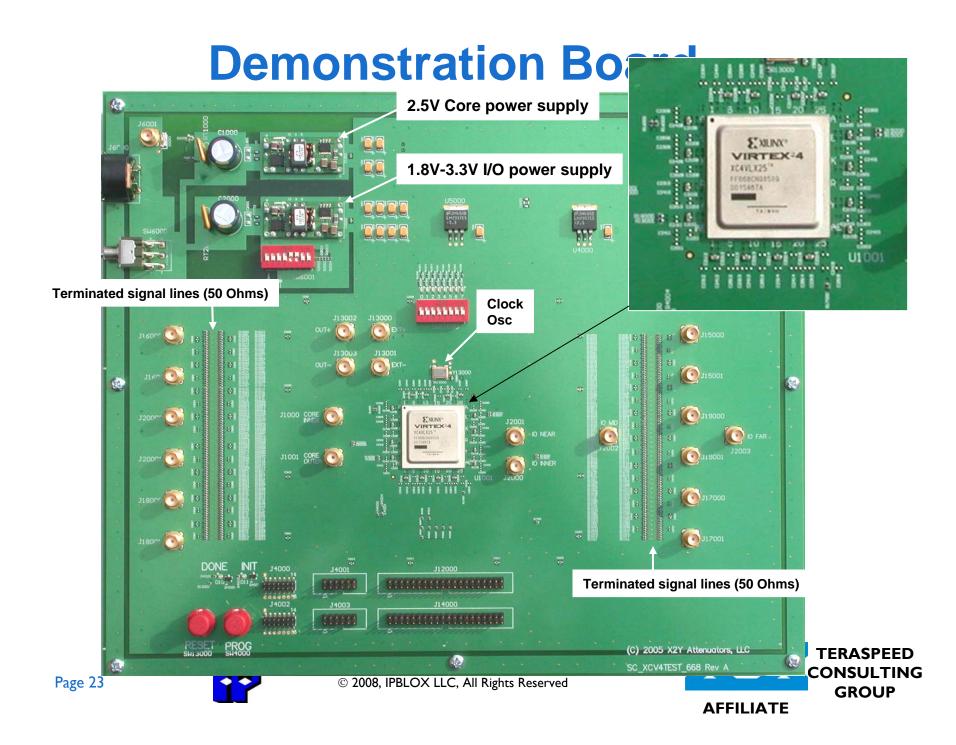

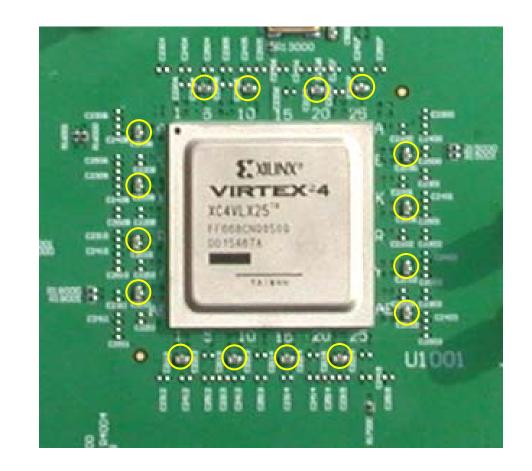

# **FPGA Bypass Design**

- Two bypass capacitor options:

- 16 X2Y 0603 100nF capacitors (shown circled)

- Up to 64 conventional 0402 capacitors (unpopulated positions at right)

- 16 of the 64 conventional on same radius as X2Y capacitors

AFFILIATE TERASPEED CONSULTING GROUP

Page 24

$\ensuremath{\textcircled{}}$  2008, IPBLOX LLC, All Rights Reserved

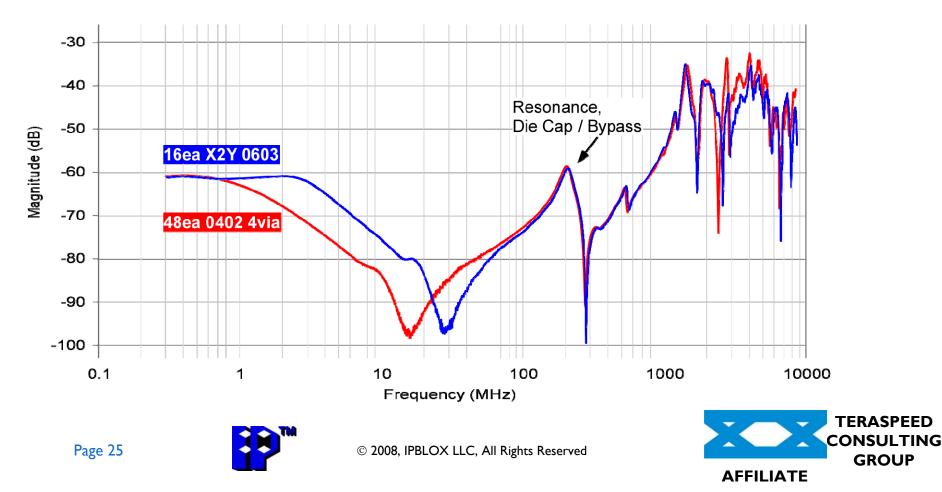

#### **Test PCB VNA Measurments**

• 16 X2Y® using 96 vias total same inductive response as 48 0402s using 192 vias total

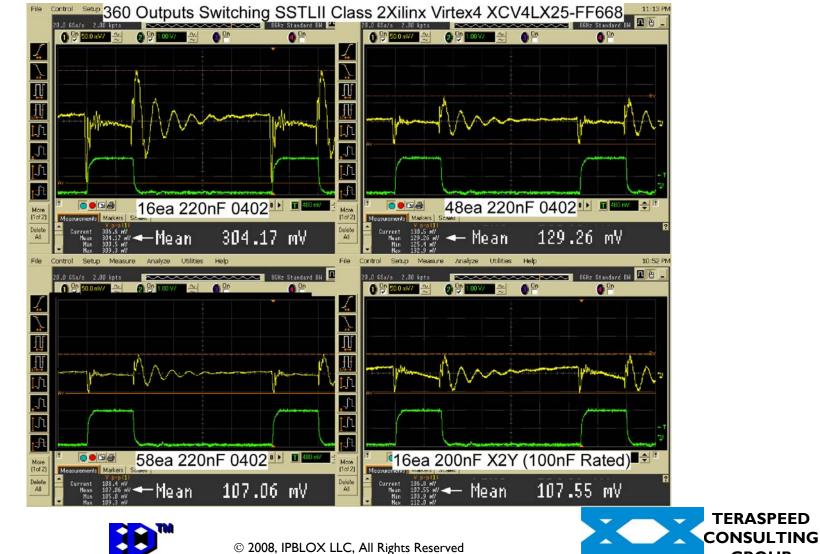

### **Test Board Noise Measurements**

GROUP

**AFFILIATE**

Page 26

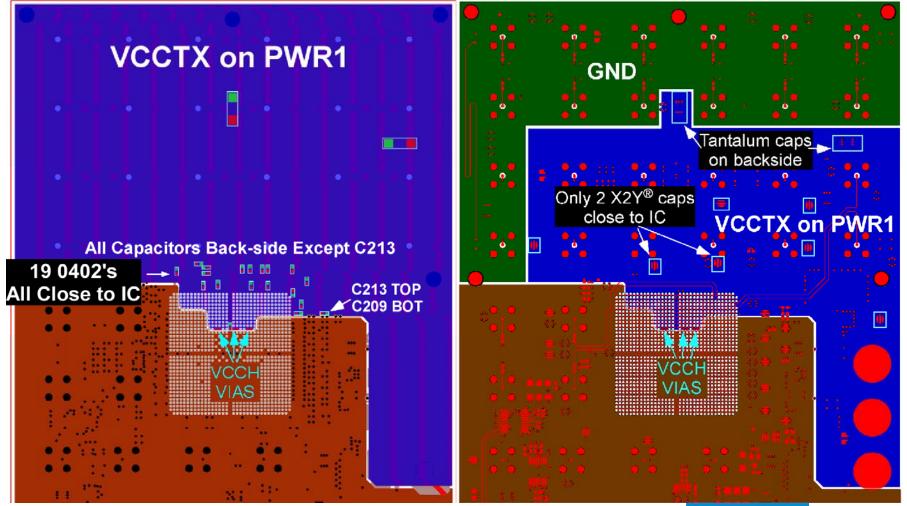

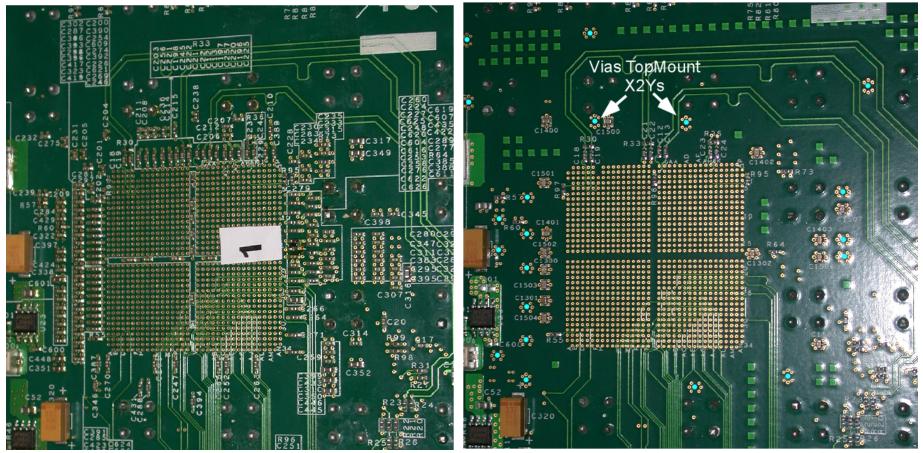

#### **Example Altera StratixII GX Eval Bd**

- PCB Demonstrates SerDes Performance of Altera StratixII GX FPGAs

- Comparison of original conventional MLCC based bypass and X2Y<sup>®</sup> based bypass

## **Transmit Analog: VCCH**

- Original Design

- 2 x 330uF tantalum caps + 20 MLCCs

- 1D < 80mOhms equivalent resistive to 250MHz</p>

- Ignores spatial effects and IC parasitics

- Spatial effects dominate above 10MHz

- Most caps on back

- Typical as caps congest precious PCB component side

- Aggravates # of caps needed

- Raises Q of bypass network to plane resonance

© 2008, IPBLOX LLC, All Rights Reserved

Page 28

### **Transmit Analog: VCCH**

- X2Y<sup>®</sup> Design

- Preserve 1D performance of orig.

- 2 x 330uF tantalum caps + 2 MLCCs + 7 X2Y®

- 1/3 caps & much lower inductance:

- Capacitor + mount L much smaller w/ X2Y for like mounts

- X2Y's mounted on top surface closer to planes

- X2Y caps fit on top because so few needed

- Smaller plane area used

- More realistic to actual designs

- Raises F<sub>PRF</sub>

- Also rasise Z<sub>PRF</sub>

© 2008, IPBLOX LLC, All Rights Reserved

4/2/2008

Page 29

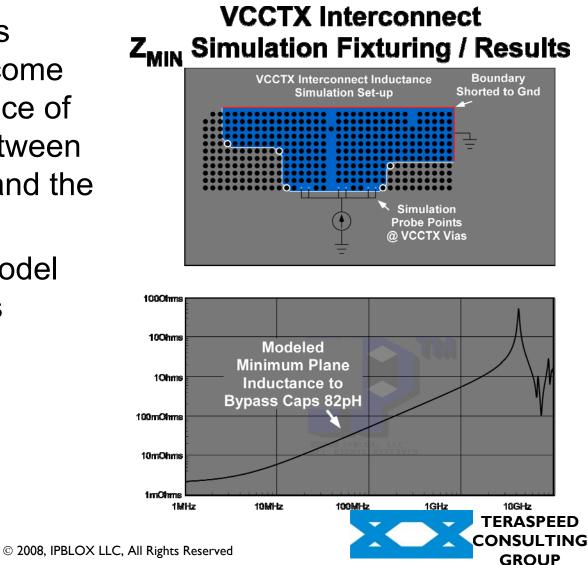

### Determining PDN Interconnect Limits

- No amount of bypass capacitors can overcome the intrinsic impedance of the interconnects between the nearest bypass and the power pins

- Shorted boundary model identifies those limits

AFFILIATE

### **Example Design StratixII GX**

Page 31

© 2008, IPBLOX LLC, All Rights Reserved

TERASPEED CONSULTING GROUP

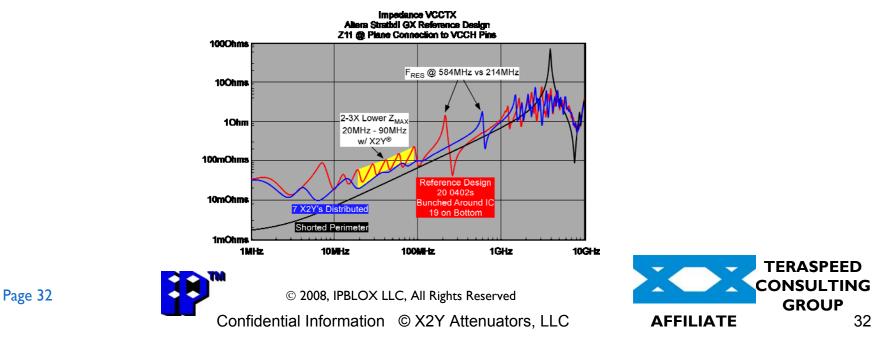

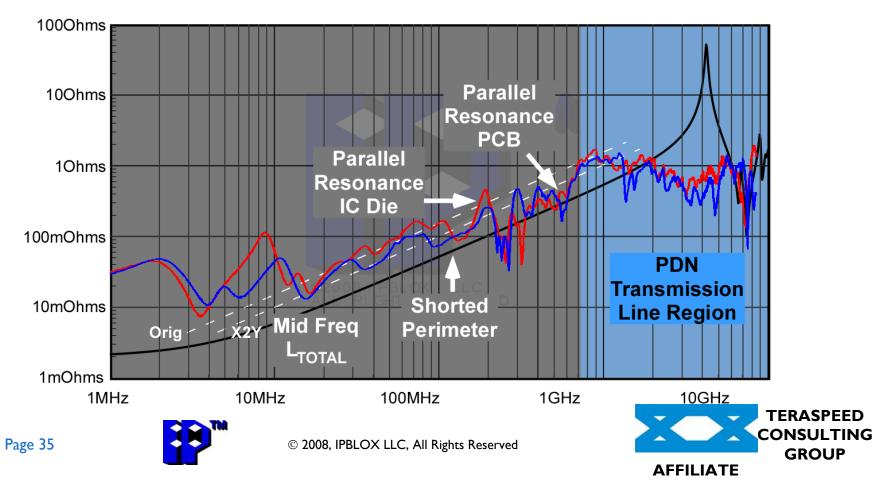

### StratixII GX VCCH Supply Simulation No IC

Radically lower mounted L / cap w/ X2Y<sup>®</sup> top-side solution flattens impedance modulation.

- Remains much closer to limit of shorted planes

Higher F<sub>RES</sub> w/lower Q stabilizes power system much faster after each transient.

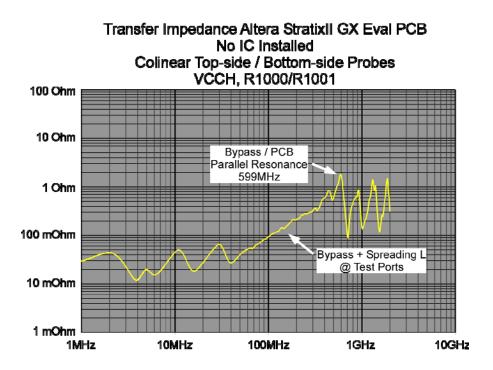

### **Measured X2Y® Network**

- Bypass network measured through PCB

@ 2 0805 one top-side

/ one bottom side, straight through vias

- Measured bypass to plane PRF closely matches simulation

- Detune resonance by changing one cap ( next slide )

© 2008, IPBLOX LLC, All Rights Reserved

#### **PCB w/ PRF Compensated**

#### StratixII GX VCCH Measured @ IC VIAS

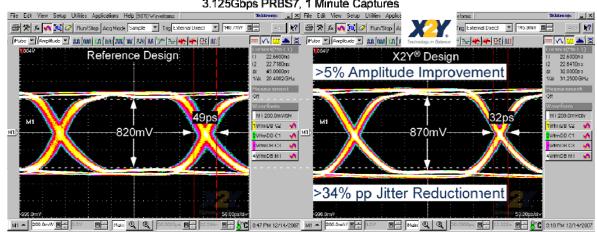

#### **Example StratixII GX**

### Measured VCCTX Networks vs Simulated Shorted Perimeter

### **Example Design StratixII GX**

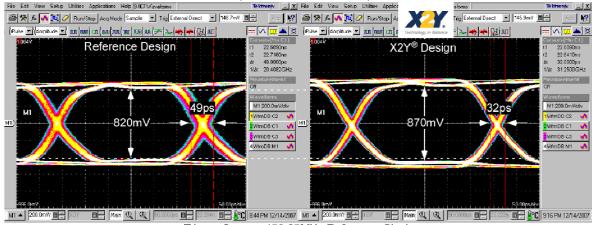

#### Original Design

#### X2Y<sup>®</sup> Design

Page 36

$\odot$  2008, IPBLOX LLC, All Rights Reserved

#### **Measured Performance**

3.125Gbps PRBS7, 1 Minute Captures

Trigger Source: 156.25MHz Reference Clock

3.125Gbps PRBS23, 1 Minute Captures

Trigger Source: 156.25MHz Reference Clock

© 2008, IPBLOX LLC, All Rights Reserved

#### **PowerPoser**<sup>TM</sup>

@ 2008, IPBLOX LLC, All Rights Reserved

Page 38

## Conclusions

- Understanding spatial behavior of PDNs is critical to proper analysis and design

- Inductance and resonance are the main problems to overcome

- Capacitor mounted inductance determines the number of capacitors needed to meet basic HF impedance requirements

- Detuning resonance provides substantial performance gains, lower L more feasible

- X2Y<sup>®</sup> capacitors excel at low mounted inductance

### **How To Contact Us?**

IPBLOX, LLC 150 N. Center St. #211 Reno, NV 89501 v (866) 675-4630 f (707) 780-1951 www.ipblox.com eng@ipblox.com steve@teraspeed.com

Power Delivery Solutions

Teraspeed Consulting Group, LLC 121 North River Drive Narragansett, RI 02882 v (401) 284-1827 f (401) 284-1840 <u>www.teraspeed.com</u> scott@teraspeed.com 3D E/M Modeling Teraspeed Labs 13610 SW Harness Lane Beaverton, OR 93007 v (503) 430-1065 <u>www.teraspeed.com</u> tom@teraspeed.com IBIS Model Development

© 2008, IPBLOX LLC, All Rights Reserved