# 2D to 3D MOS Technology Evolution for Circuit Designers

Alvin Loke<sup>1</sup>, Ray Stephany<sup>1</sup>, Andy Wei<sup>2</sup>, Bich-Yen Nguyen<sup>3</sup>, Tin Tin Wee<sup>1</sup>, John Faricelli<sup>1</sup>, Jung-Suk Goo<sup>2</sup>, and Shawn Searles<sup>1</sup>

> <sup>1</sup>Advanced Micro Devices <sup>2</sup>GlobalFoundries <sup>3</sup>Soitec

> > AUTHORIZATION

All copyrights to the material contained in this document are retained by us and our employers.

IEEE Solid-State Circuits Society – Fort Collins Chapter DL Seminar 14-Dec-2012

#### **My Teachers**

Phil Fisher

Avago

Ying-Keung Leung

GlobalFoundries

**Bob Barnes** Avago

Larry Bair AMD

John Bravman Bucknell

Tom Cynkar Avago

Dick Dowell Avago

Bruce Doyle AMD

Emerson Fang Apple

John Faricelli AMD

**Dennis Fischette** AMD

Mike Gilsdorf Avago

Jung-Suk Goo GlobalFoundries

Bob Havemann Rick Hernandez Novellus PMC-Sierra

Mark Horowitz Ron Kennedv Stanford Avago

Takamaro Kikkawa Greg Kovacs Hiroshima Univ. Stanford

LSI

Steve Kuehne

Tom Lee Stanford

Justin Leung Intel

Tom Lii TL

Joe McPherson TL

Soitec

**Bich-Yen Nguyen**

Michael Oshima Chintamani Palsule AMD Sionyx

Jim Pfiester

Avago

Jim Plummer Stanford

Dave Pulfrey

Gary Ray Intel

Changsup Ryu

Krishna Saraswat Shawn Searles Stanford AMD

Ray Stephany AMD

Matt Angyal IBM Qi-Zhong Hong TI Wei-Yung Hsu

Charles Moore

Avago

Gerry Talbot AMD

LSI

Ram Venkatraman Jeff Wetzel SVTC

Martin Wedepohl Tin Tin Wee UBC AMD

Simon Wong Stanford

Applied Materials Andy Wei

GlobalFoundries

Patrick Yue HKUST

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

Samsung

Carl-Mikael Zetterling KTH

#### The 10000-Foot View... A Switch

## Outline

#### Part 1

- Motivation

- MOSFET & Short-Channel Fundamentals

- Lithography

- Getting to 130nm

- More MOSFET Fundamentals

#### • Part 2

- Strain Engineering (90nm & Beyond)

- High-K / Metal-Gate (45nm & Beyond)

- Migrating to Fully-Depleted (22nm & Beyond)

- Tri-Gate FinFETs

- Conclusions

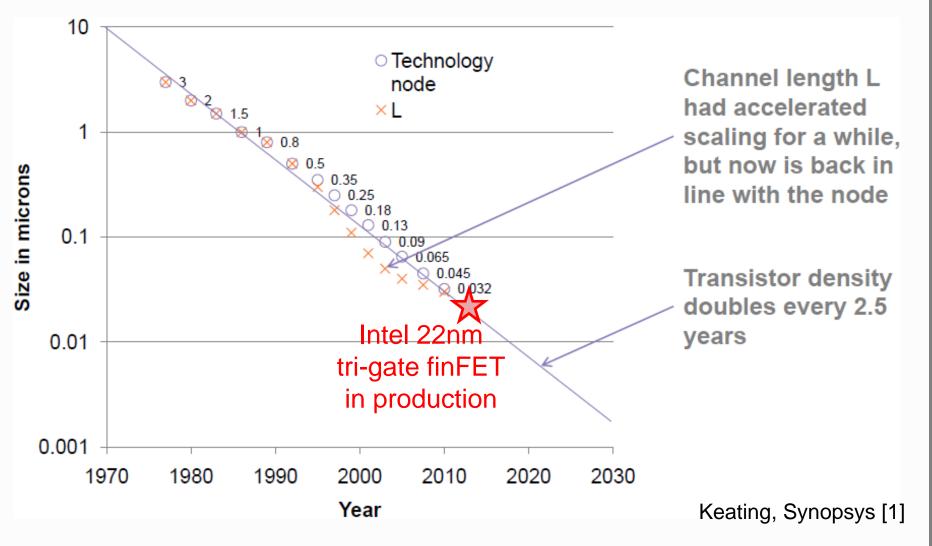

#### **CMOS Scaling Still Alive...**

• Leading foundries frantically after manufacturable tri-gate

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

## ...But Slowing Down

- MOS performance improves with scaling

- BUT \$\$\$ (as always) is THE main reason to scale

- Each new CMOS node shrinks dimensions by  $\sqrt{2}$

- Same functionality in half the area

- Cost-per-functionality

if area reduction exceeds

increased cost-per-area for more complex manufacturing

- Enables more functionality on a single die

- Fewer dies  $\rightarrow$  fewer packages  $\rightarrow$  lower cost

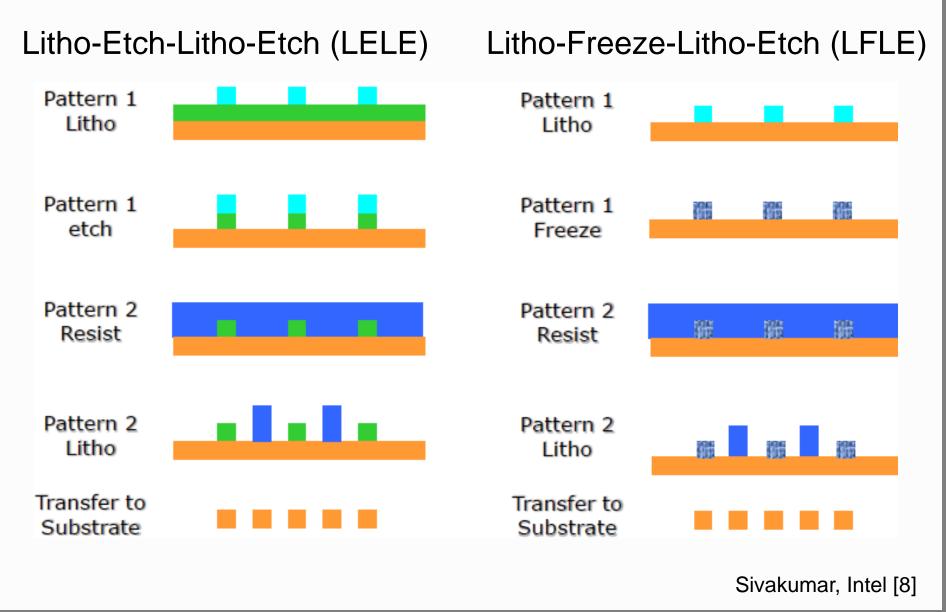

- Moving to planar 20nm CMOS is not so obvious for many

- Wafer cost is getting prohibitive, e.g., double patterning

- Fully-depleted option (e.g., tri-gate fins) is compelling to enable low-power operation, especially with high demand for portable ICs

- 28nm likely to be around for a while

## **Our Objective**

- Understand how MOSFET structure has evolved

- Learn about enabling technologies

- Understand why it has evolved this way

#### **Words of Wisdom**

# People get lost because they cannot be found.

#### Theodorus Loke

## Outline

#### Part 1

Motivation

#### – MOSFET & Short-Channel Fundamentals

- Lithography

- Getting to 130nm

- More MOSFET Fundamentals

- Part 2

- Strain Engineering (90nm & Beyond)

- High-K / Metal-Gate (45nm & Beyond)

- Migrating to Fully-Depleted (22nm & Beyond)

- Tri-Gate FinFETs

- Conclusions

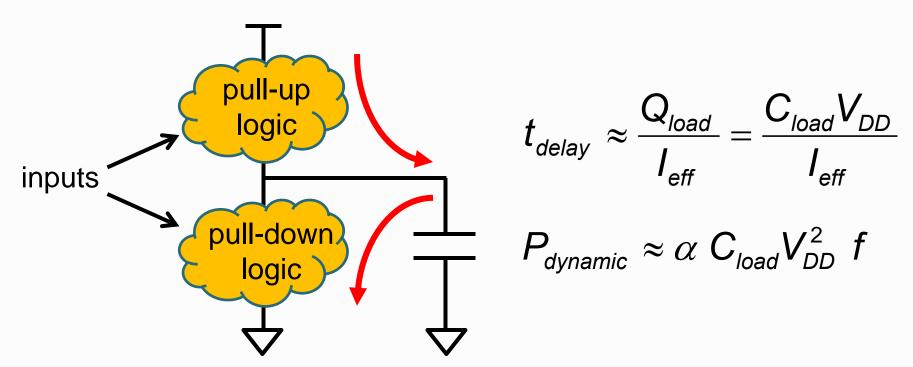

#### The Basis of All CMOS Digital ICs

- Charging and discharging a capacitor... very quickly!

- For shorter delay and lower power

- $C_{load} \downarrow \rightarrow$  reduce parasitics (wires, gates, junctions, ...)

- $V_{DD} \downarrow \rightarrow$  reduce logic swing

- $I_{eff} \uparrow \rightarrow$  move charge quicker

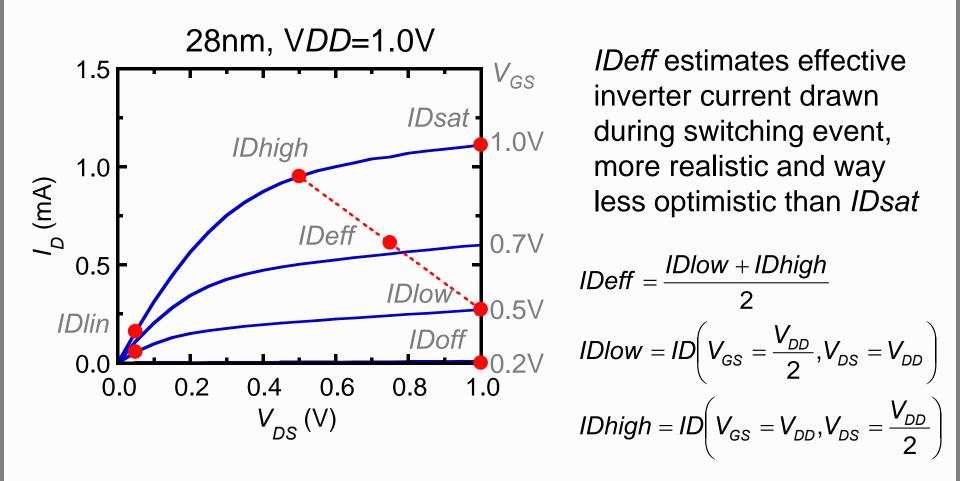

#### **Effective Inverter Drive Current**

Na et al., IBM [3]

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

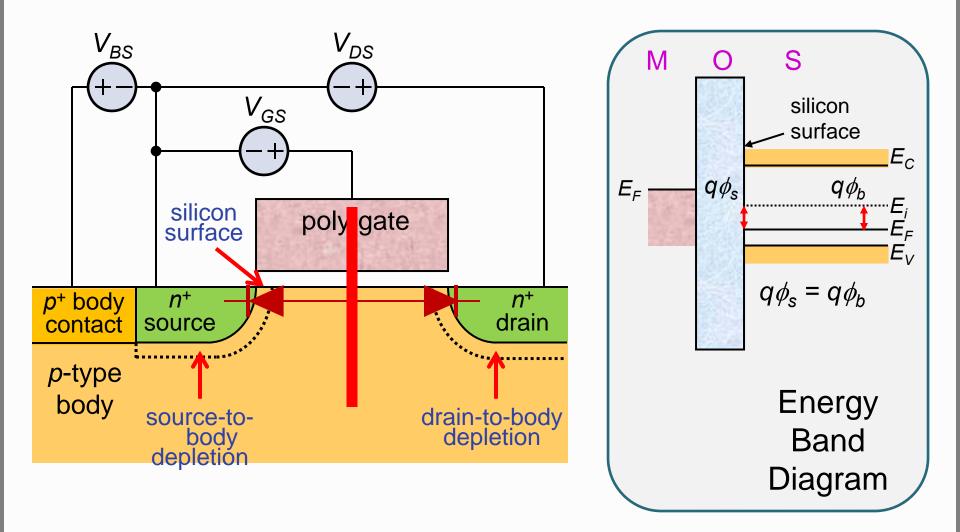

#### Flatband Condition ( $V_{GS} = V_{FB}$ )

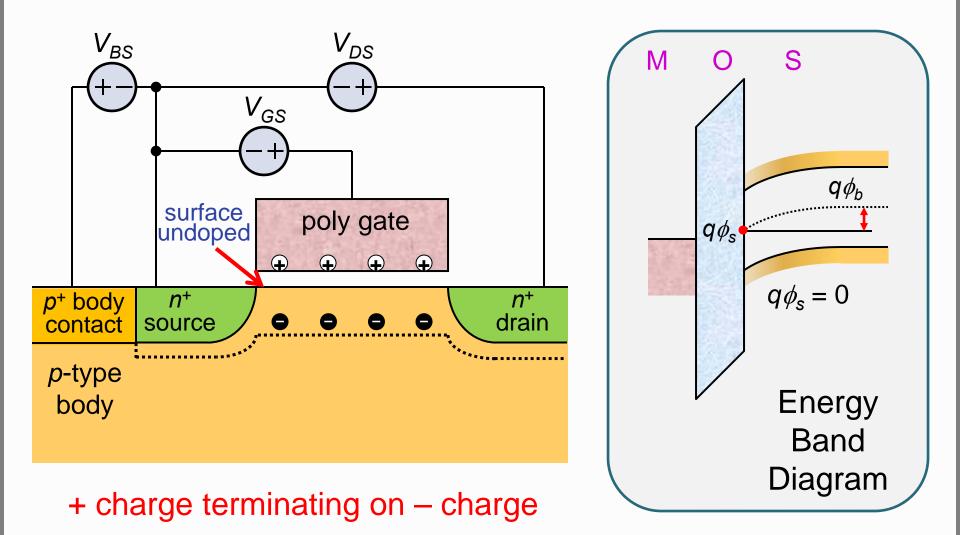

#### **Onset of Surface Inversion (** $\phi_s$ **=0)**

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

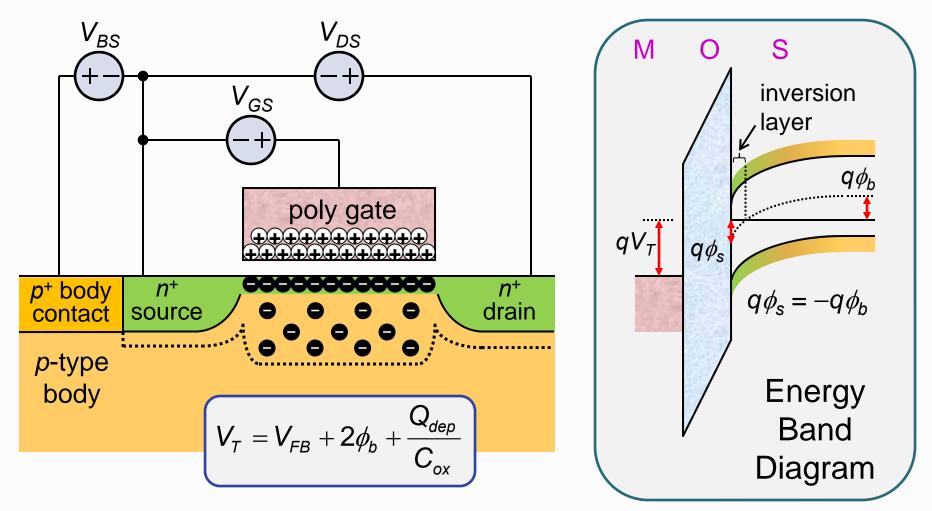

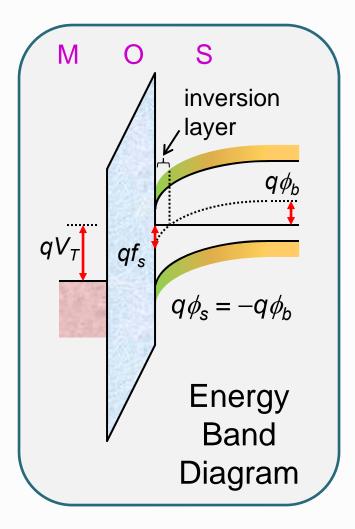

# Onset of Strong Surface Inversion $(V_{GS}=V_T)$

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

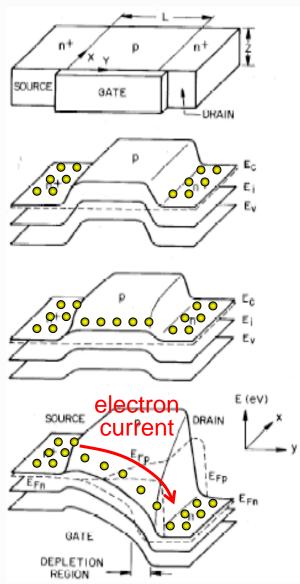

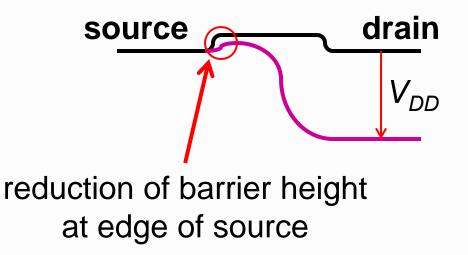

#### **Lower the Surface Barrier**

$V_{GS} = 0$  $V_{DS} = 0$  (no current) Large source barrier (back-to-back diodes)

$V_{GS} \approx V_T$  $V_{DS} = 0$  (no net current) Source barrier lowered Surface is inverted

$V_{GS} > V_T$   $V_{DS} > 0$  (net source-to-drain current flow)

Carriers easily overcome source barrier

Surface is strongly inverted

Sze [4]

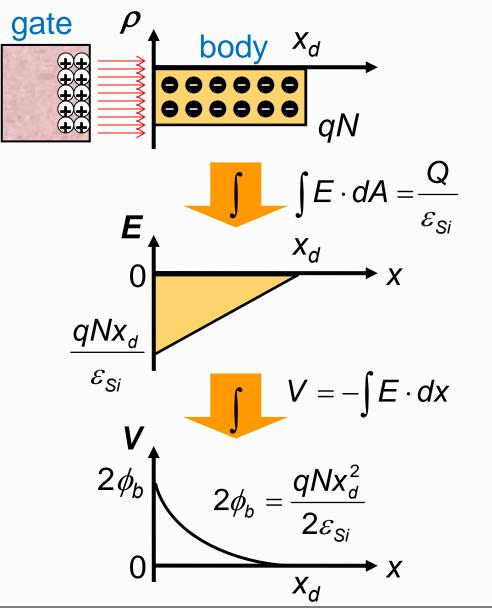

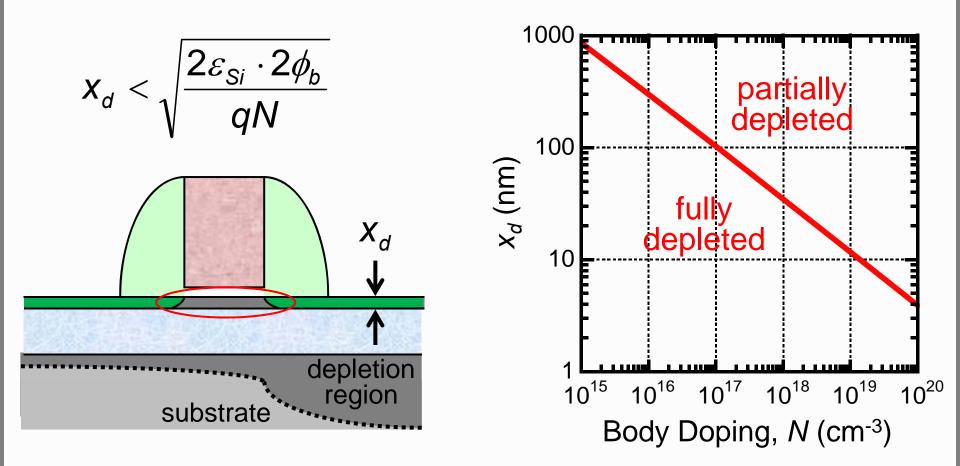

## Quantifying Charge to Move $\phi_s$ by $2\phi_b$

- Assume *uniformly doped* p-type body

- How much body must be depleted to reach strong inversion?

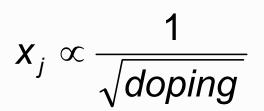

$$X_d = \sqrt{\frac{2\varepsilon_{Si} \cdot 2\phi_b}{qN}} \propto \frac{1}{\sqrt{N}}$$

$Q_{dep} = qNx_d$

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

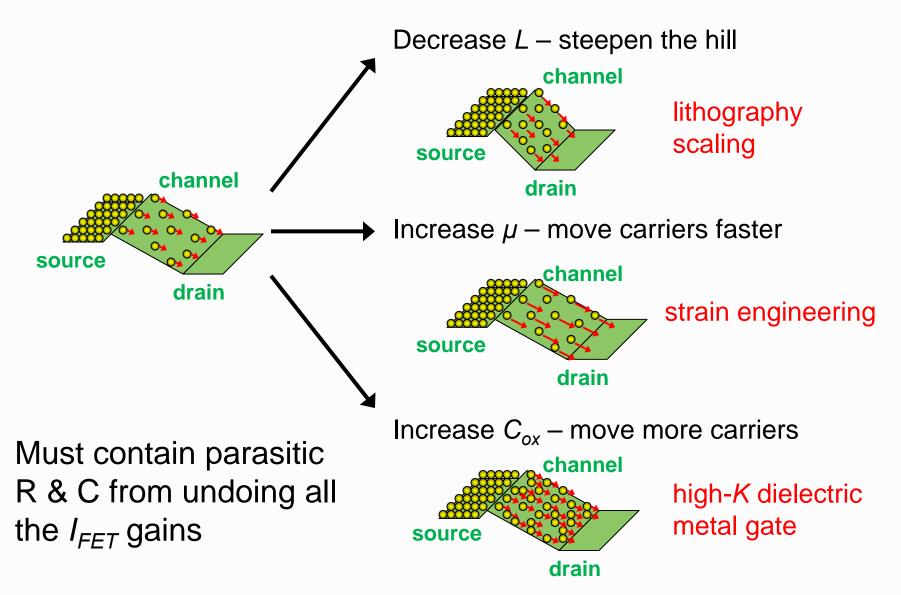

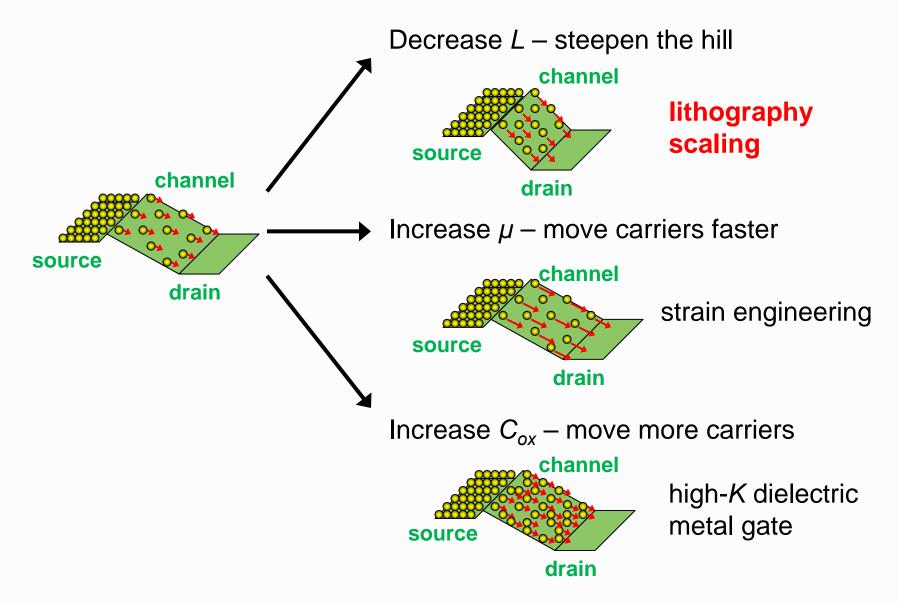

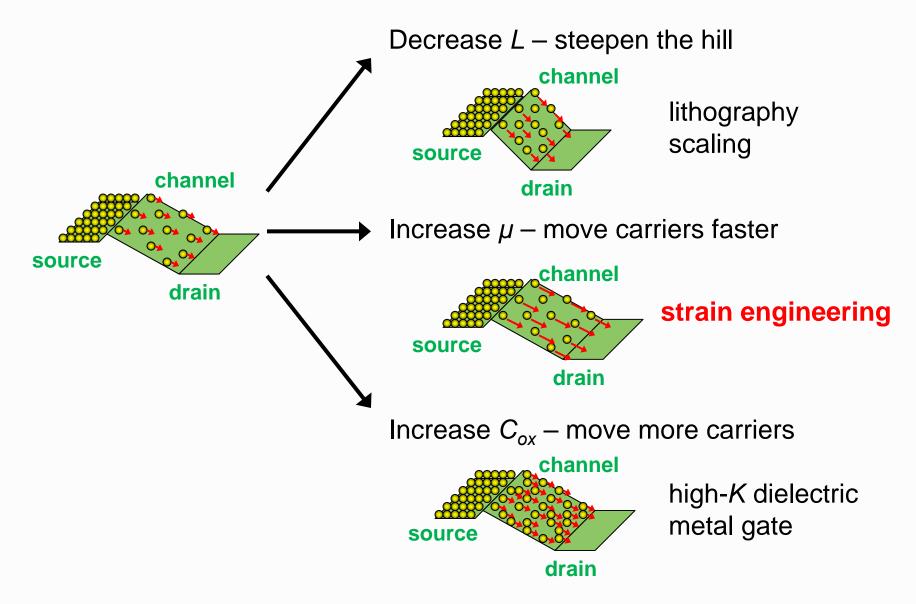

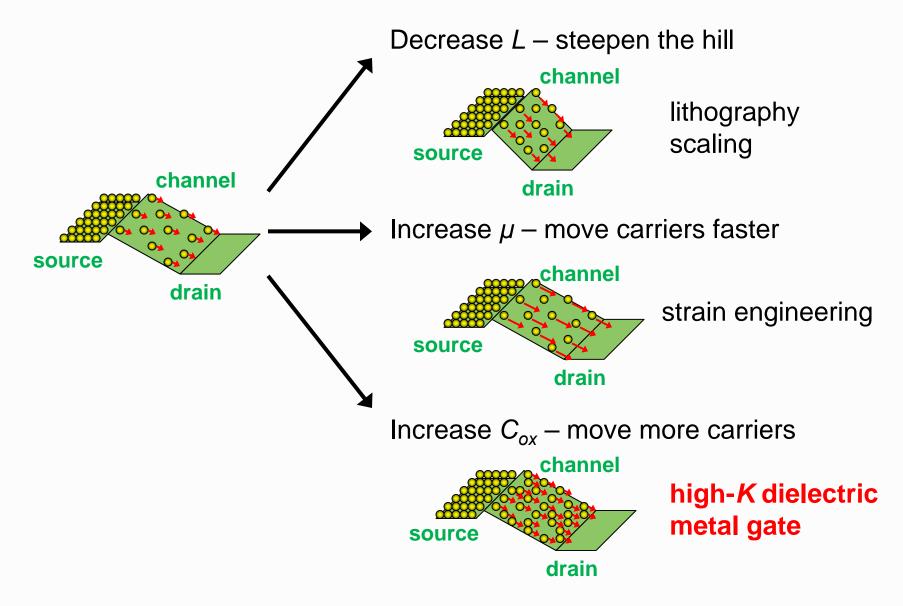

#### **The Roads to Higher Performance**

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

- $\rightarrow$  Higher channel electric fields

- Velocity saturation

- Mobility degradation

## **Overcoming Short-Channel Effects**

Improve gate electrostatic control of channel charge

- Higher body doping but higher  $V_T$

- Shallower source/drain but higher R<sub>s</sub>

- Thinner  $t_{ox}$  but higher gate leakage

- High-K dielectric to reduce tunneling

- Metal gate to overcome poly depletion

- Fully-depleted structures (e.g., fins)

Stressors for mobility enhancement

#### **Profound Revelation**

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

## Outline

#### Part 1

- Motivation

- MOSFET & Short-Channel Fundamentals

#### Lithography

- Getting to 130nm

- More MOSFET Fundamentals

- Part 2

- Strain Engineering (90nm & Beyond)

- High-K / Metal-Gate (45nm & Beyond)

- Migrating to Fully-Depleted (22nm & Beyond)

- Tri-Gate FinFETs

- Conclusions

#### **The Roads to Higher Performance**

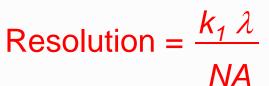

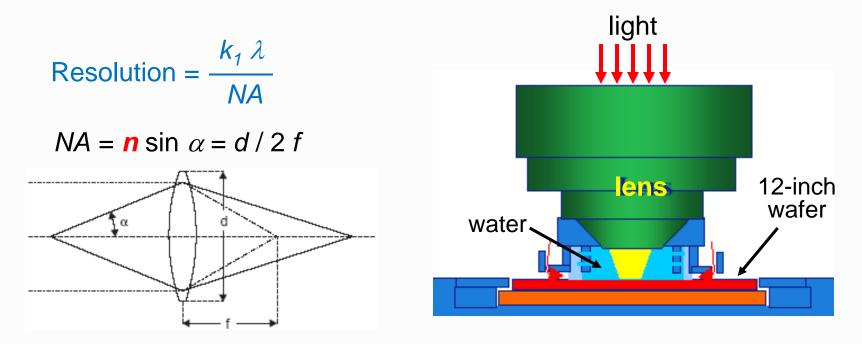

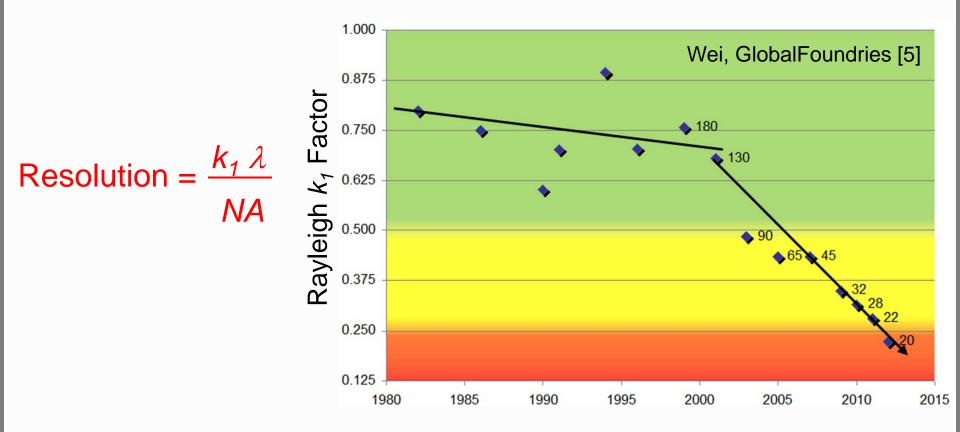

## Let There Be Light

- Tooling has traditionally driven resolution scaling

- Shorter  $\lambda$  : 436nm  $\rightarrow$  365nm  $\rightarrow$  248nm  $\rightarrow$  193nm

- Higher NA lenses  $\rightarrow$  capping at 1.35

- Both *λ* and NA have hit a wall

- No new litho tool for 22/20nm nodes

- (EUV not primetime yet)

- Single patterning limited to ~80nm pitch

Wei, GlobalFoundries [5]

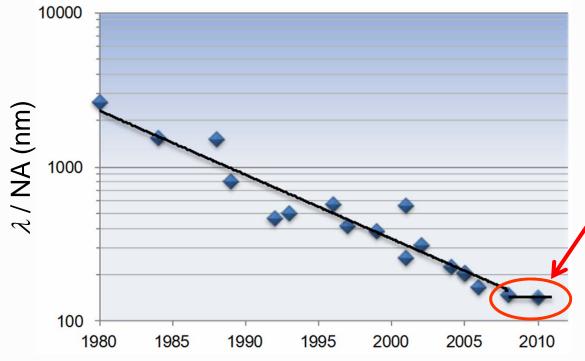

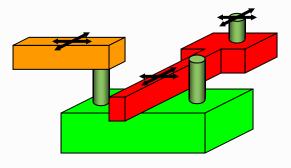

# **Step-and-Scan Projection Lithography**

- Slide both reticle & wafer across narrow slit of light

- Only need high-NA optics orthogonal to scan but now high-precision constantspeed stages to move mask & wafer

- Cheaper than high-NA 2-D optics

- 6" x 6" physical reticle size (4× reduction)

- 25 x 33mm or 26 x 32mm field size

- Weak intensity of deep-UV source requires sensitive *chemically-amplified* resists for better throughput

- Enables dose mapping (adjust light dose during scan to compensate for loading)

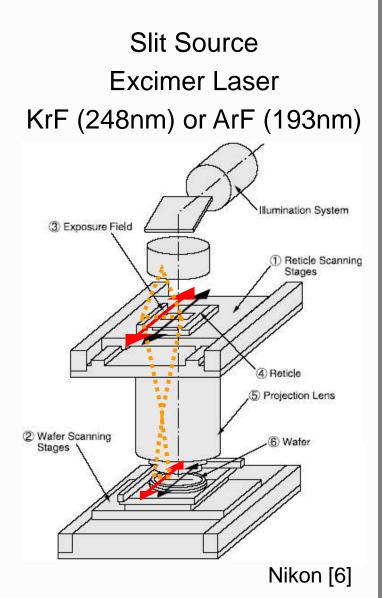

# **Immersion Lithography**

- Remember oil immersion microscopy in biology class?

- Extend resolution of refractive optics by squirting water puddle on wafer surface prior to exposure

- *n<sub>water</sub>* ~1.45 vs. *n<sub>air</sub>* ~ 1

- Tedious but EUV is not primetime yet

# Lithography Misalignment / Overlay

- Mask misalignment tolerance is not keeping pace with gate CD scaling

- ASML has near monopoly on lithography tools largely because of good overlay control (global zero layer patterns)

- Many layout enclosure & spacing rules not scaling with CD

- Examples:

- Poly overhang beyond active

- Contact spacing to poly

- Active enclosure around contact

- Metal enclosure around vias

- Layout for matching must be robust against overlay errors

# **Resolution Enhancement Technology**

- Reducing  $k_1$  is the remaining ticket to better resolution

- Attack problem from all fronts: mask, source & wafer

- Imposes significant restrictions on layout design rules

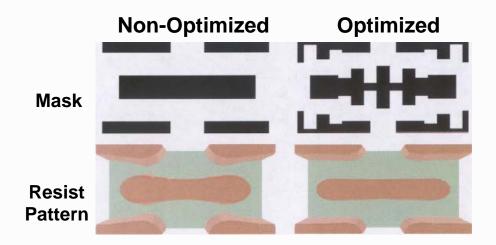

## **Mask – Optical Proximity Correction**

- Sharp features are lost because diffraction attenuates higher spatial frequencies (mask behaving as low-pass optical filter)

- Compensate for diffraction effects when feature sizes  $<< \lambda$  by managing sub- $\lambda$  constructive & destructive interference

- Exaggerate edges and corners to "equalize" cutoff spatial frequency of mask

Plummer et al., Stanford [7]

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

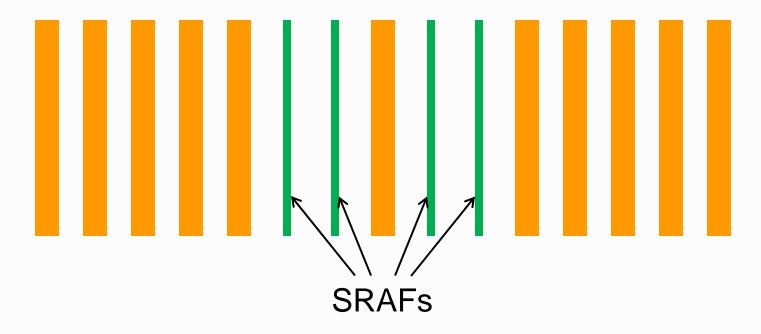

#### Mask – Sub-Resolution Assist Features

- Difficulty to concurrently print dense and isolated lines

- SRAFs are features intentionally placed on mask that are too small to print but provide enough diffraction to make isolated features print well

- Imposes forbidden pitches on layout

Sivakumar, Intel [8]

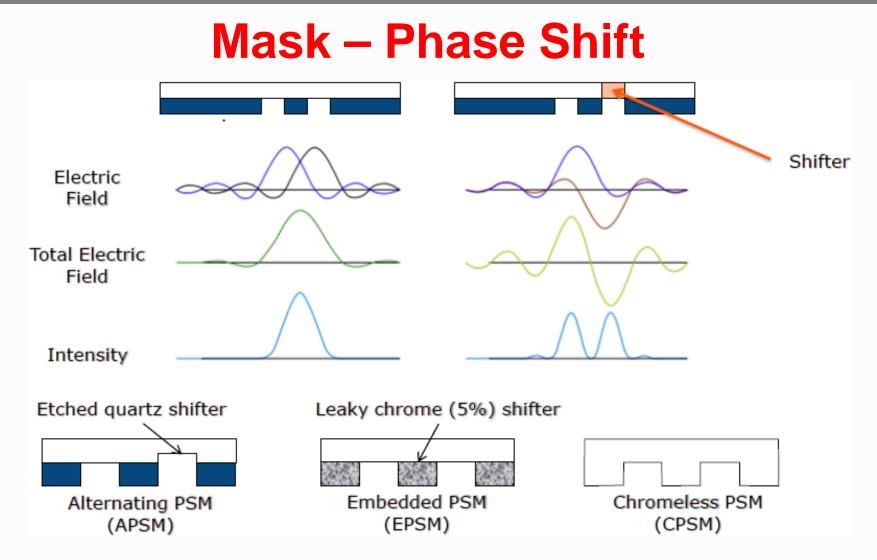

• Create differential optical path length to invert electric field of adjacent features

Sivakumar, Intel [8]

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

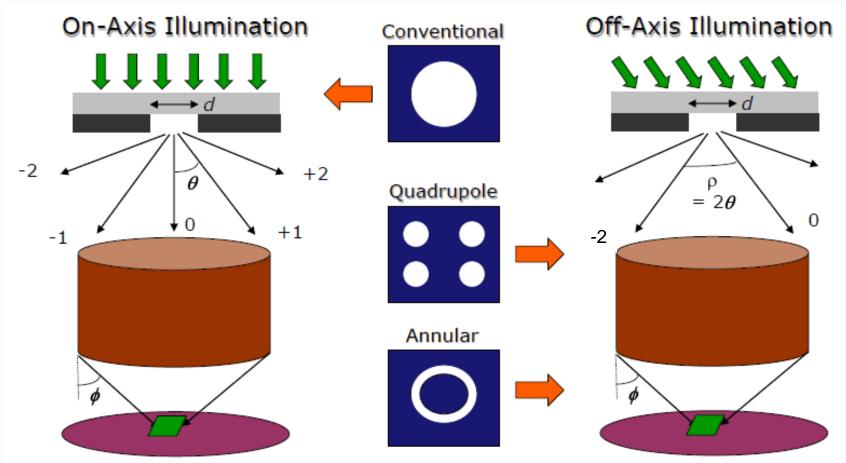

#### **Source – Off-Axis Illumination**

- Offers significant boost in resolution

- Imposes restrictions in orientation & pitch

Sivakumar, Intel [8]

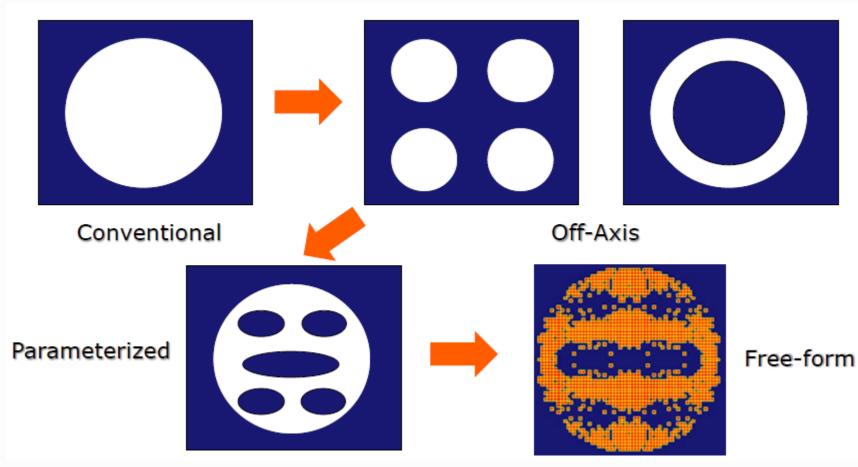

#### **Source – Aperture Shape Optimization**

- Keep pixels that contribute to image enhancement

- Discard pixels that degrade image contrast

Sivakumar, Intel [8]

#### **Double Patterning by Pitch Division**

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

#### **Breakthrough in Seat Belt Development**

- The National Highway Safety Council has done an extensive testing on a newly designed seat belt. Results show that accidents can be reduced by as much as 45% when the belt is properly installed.

- Correct installation is illustrated below.

## Outline

#### Part 1

- Motivation

- MOSFET & Short-Channel Fundamentals

- Lithography

#### - Getting to 130nm

- More MOSFET Fundamentals

- Part 2

- Strain Engineering (90nm & Beyond)

- High-K / Metal-Gate (45nm & Beyond)

- Migrating to Fully-Depleted (22nm & Beyond)

- Tri-Gate FinFETs

- Conclusions

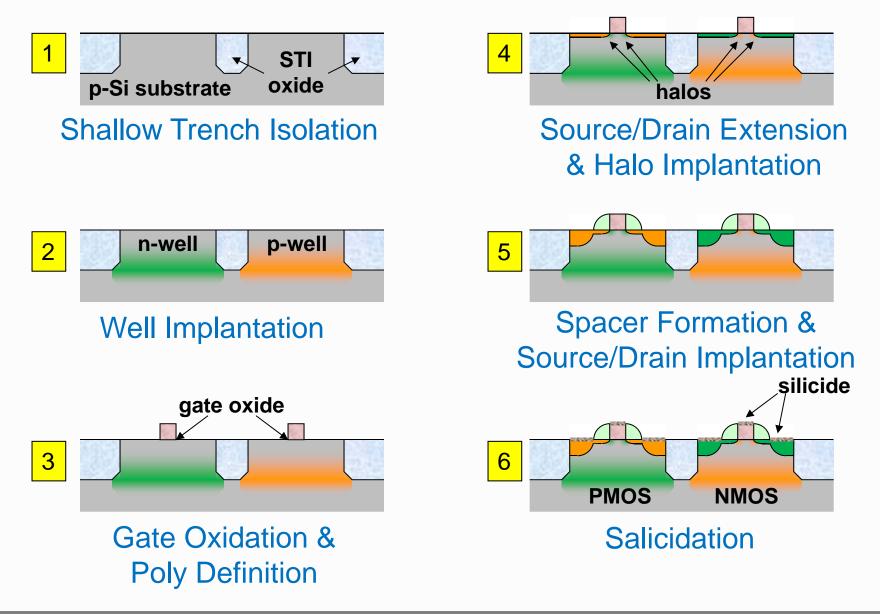

#### **130nm MOSFET Fabrication**

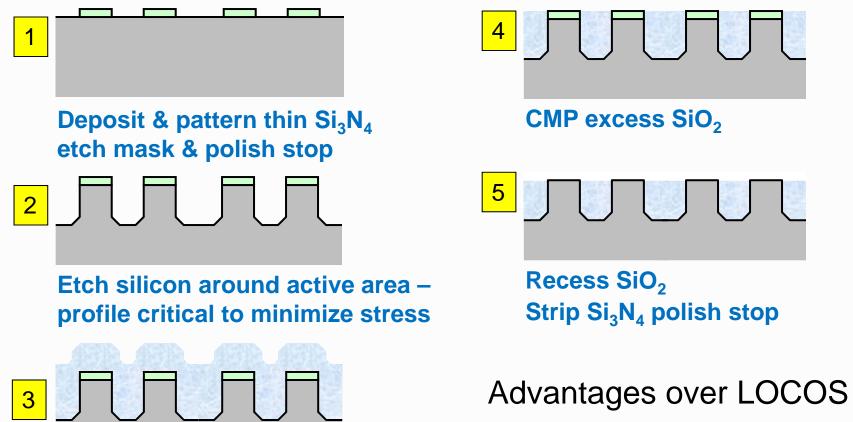

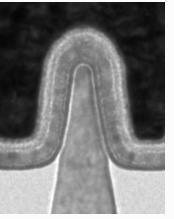

## **Shallow Trench Isolation**

- Reduced active-to-active spacing (no bird's beak)

- Planar surface for gate lithography

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

**Grow liner SiO**<sub>2</sub>, then deposit

conformal SiO<sub>2</sub> - void-free

deposition is critical

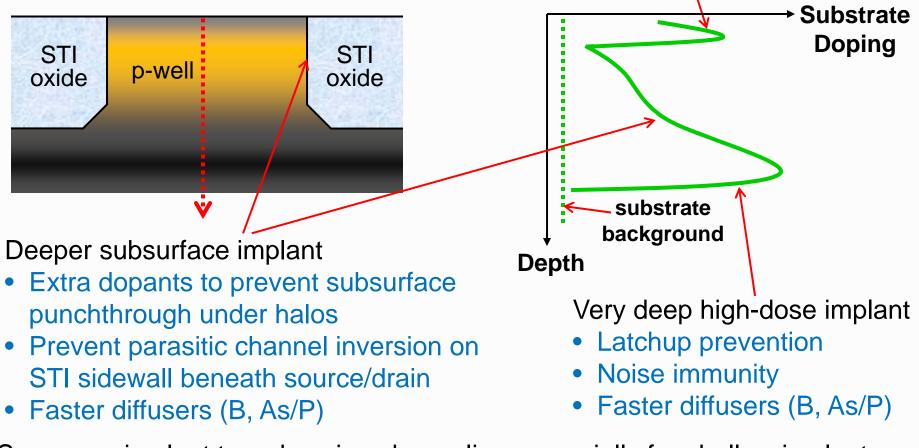

# **Well Implant Engineering**

*Retrograded* well dopant profile (implants before poly deposition)

Shallow/steep surface channel implant

- V<sub>T</sub> control

- Slow diffusers critical (In, Sb)

Sequence implant to reduce ion channeling, especially for shallow implant

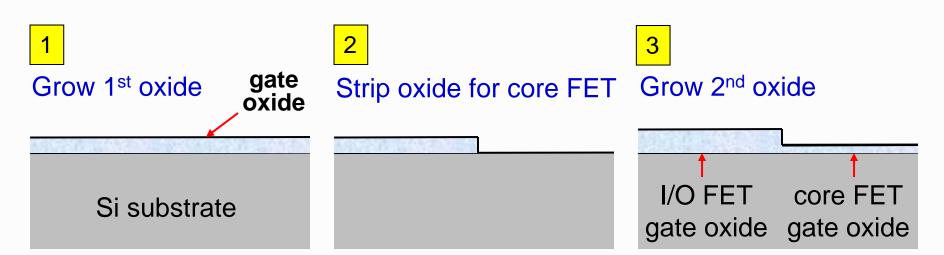

## **Gate Oxide Growth**

• Need two gate oxide  $t_{ox}$ 's – thin for core FET & thick for I/O FET

- Oxide is grown, not deposited

- Need high-quality Si-SiO<sub>2</sub> interface with low Q<sub>f</sub> & D<sub>it</sub>

- Gate oxide is really made of silicon oxynitride  $(SiO_xN_y)$

- Nitrogen prevents boron diffusion from p+ poly to channel

- Improves GOI (gate oxide integrity) reliability

- Side benefit increased  $\mathcal{E}_{ox}$

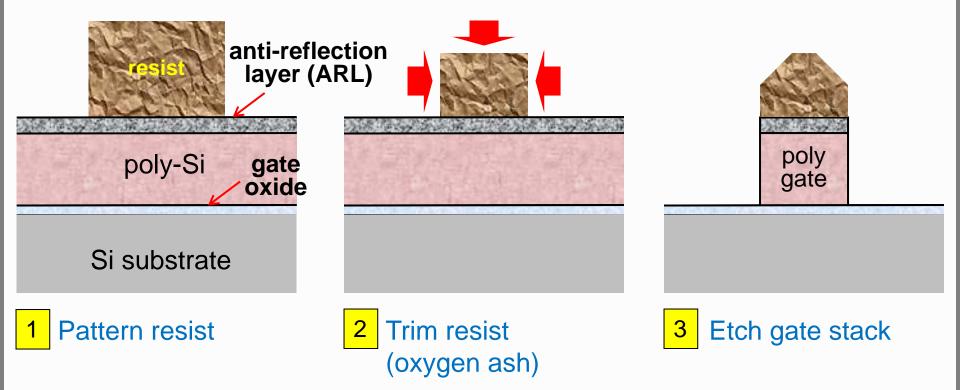

# **Poly Gate Definition**

• Gate CD way smaller than lithography capability

- Process control is everything resist & poly etch chamber conditioning is critical (don't clean residues in tea cups or woks)

- Trim more for smaller CD (requires tighter control)

- Less trimming if narrower lines can be printed  $\rightarrow$  immersion litho

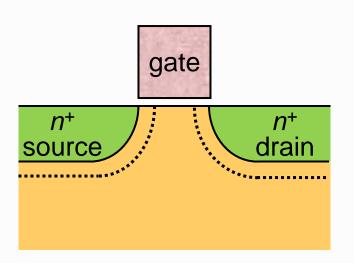

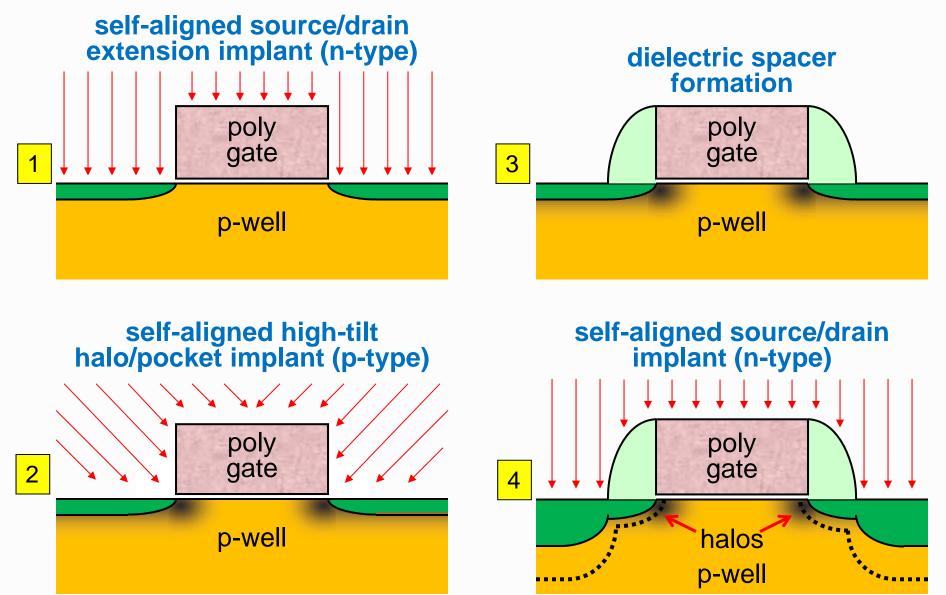

# **Channel & Source/Drain Engineering**

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

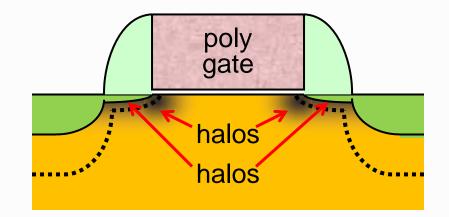

## **Benefits of Halo and Extension**

Resulting structure

- Less short-channel effect

- Shallow junction where needed most

Not to be confused with LDD in I/O FET

- Same process with spacers but lightly doped drain (LDD) is used for minimizing peak electric fields that cause hot carriers & breakdown

- Extensions need to be heavily doped to minimize series resistance

Different halo & extension/LDD implants for each FET variant

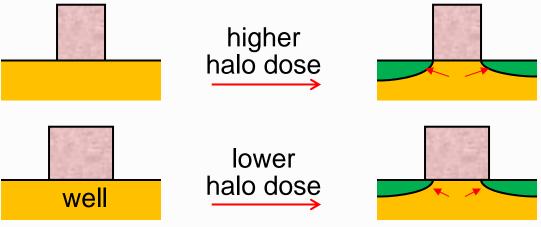

## **Feed-Forward Manufacturing Control**

Adjust resist trim ash time to compensate for poly photo variations

Adjust halo dose to compensate for poly etch variations (modulate position of *pn* junction where counter-doping occurs)

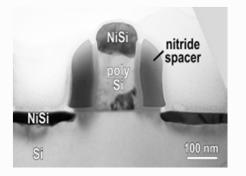

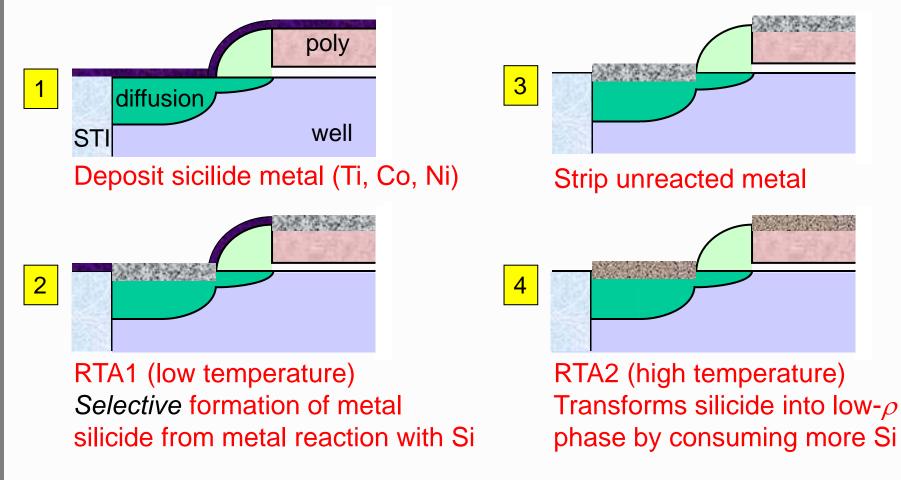

# Self-Aligned Silicidation (Salicidation)

• Need to reduce poly & diffusion  $R_s$ , or get severe  $I_{FET}$  degradation

- $TiSi_x \rightarrow CoSi_x \rightarrow Ni/PtSi_x$

- Scaling requires smaller grain size to minimize  $R_s$  variation

# Outline

#### Part 1

- Motivation

- MOSFET & Short-Channel Fundamentals

- Lithography

- Getting to 130nm

#### – More MOSFET Fundamentals

- Part 2

- Strain Engineering (90nm & Beyond)

- High-K / Metal-Gate (45nm & Beyond)

- Migrating to Fully-Depleted (22nm & Beyond)

- Tri-Gate FinFETs

- Conclusions

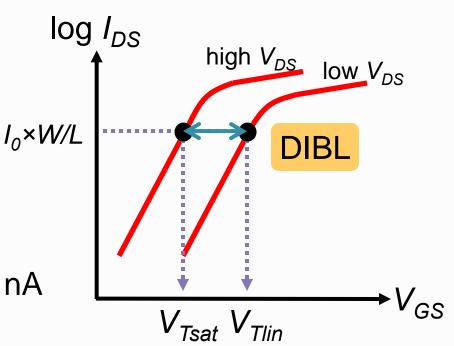

#### **Constant-Current** V<sub>7</sub> Measurement

- Onset of strong inversion near impossible to measure

- Sweep log  $I_{DS}$  vs.  $V_{GS}$

- Find V<sub>GS</sub> when I<sub>DS</sub> crosses user-specified threshold I<sub>0</sub> normalized to W/L

- Foundry-specific  $I_0 \sim 10$  to 500 nA

- No physical connection to "fundamental"  $V_{\tau}$  definition

$$V_T = V_{GS} \Big|_{I_{DS} = I_0 \times \frac{W_{drawn}}{L_{drawn}}}$$

Loke et al., AMD [9]

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

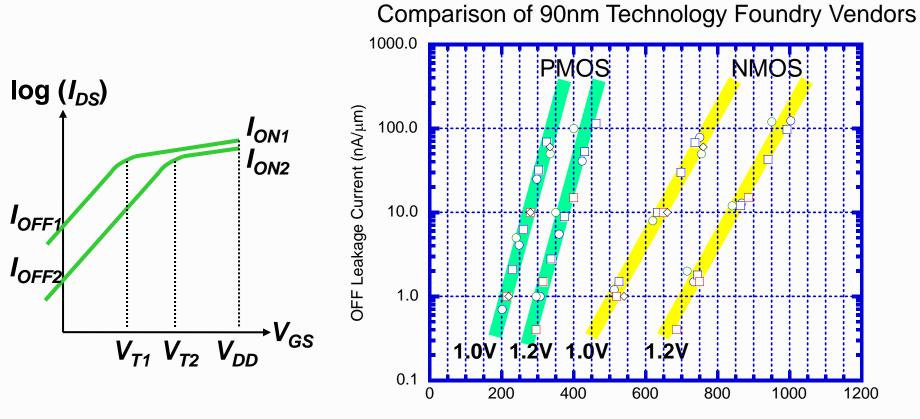

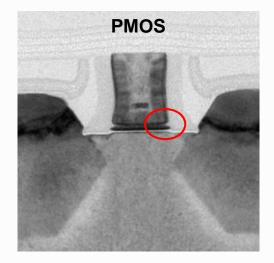

# **Not So Fundamental After All**

$$V_{T} = V_{FB} + 2\phi_b + rac{Q_{dep}}{C_{ox}}$$

- Body doping has increased by 2–3 orders of magnitude over the decades

- Surface way more conductive at strong inversion condition using "fundamental" V<sub>T</sub> definition

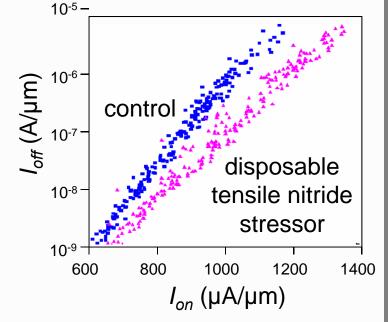

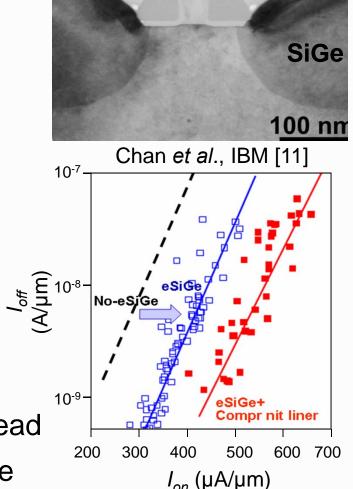

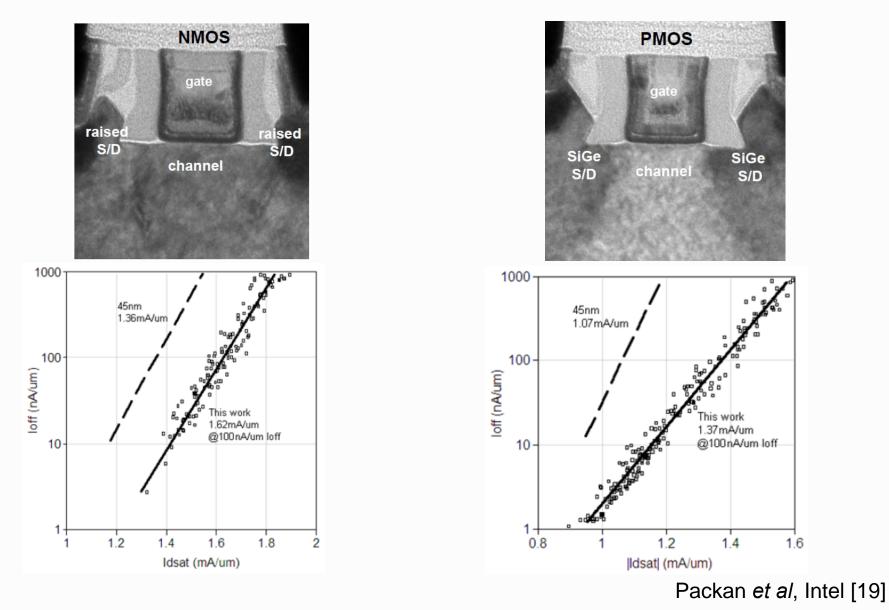

- What matters is how much OFF leakage you get for a given ON current

- *IDoff* vs. *IDsat* (or *IDeff*) universal plots have become more useful to summarize device performance

# I<sub>OFF</sub>-I<sub>ON</sub> Universal Plots

ON Drive Current ( $\mu$ A/ $\mu$ m)

- High  $I_{ON} \rightarrow$  high  $I_{OFF}$  & low  $I_{ON} \rightarrow$  low  $I_{OFF}$

- OFF leakage prevents  $V_{T}$  from scaling with gate length

- Several  $V_{\tau}$ 's enable trade-off between high speed vs. low leakage

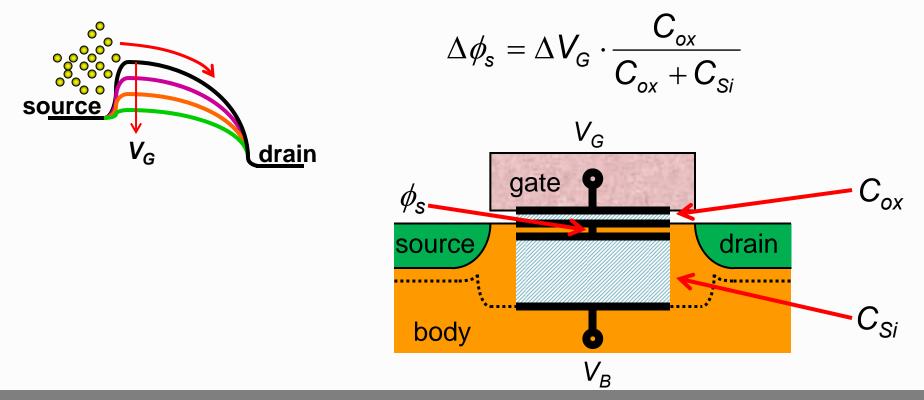

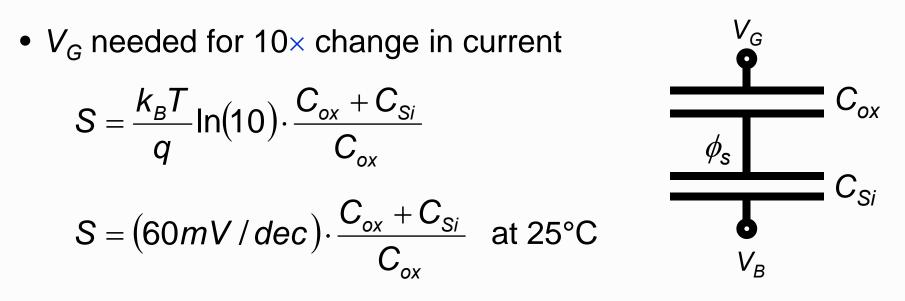

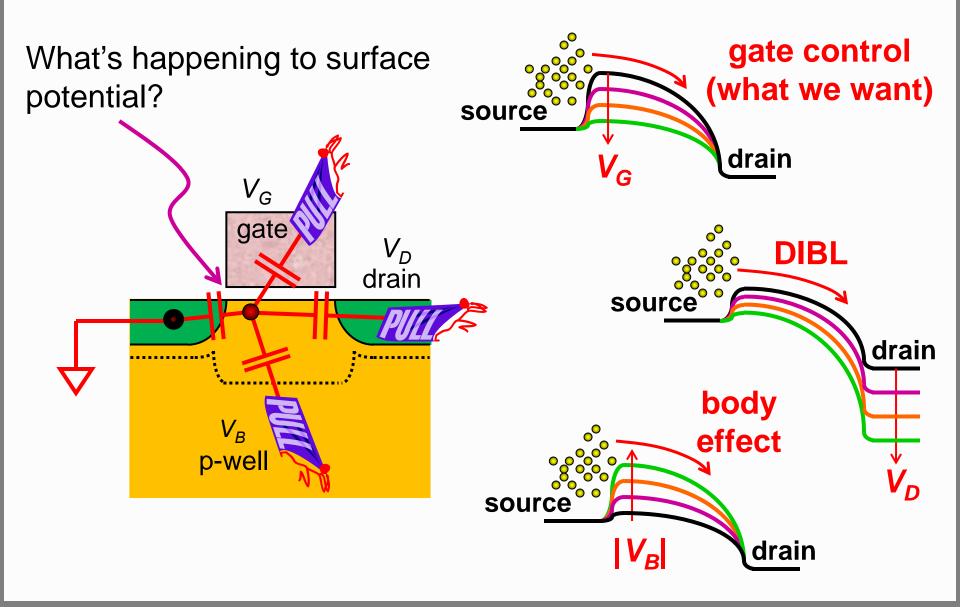

# Subthreshold Leakage

- MOSFET is not perfectly OFF below  $V_{T}$

- $V_G \uparrow \rightarrow \phi_s \uparrow \rightarrow$  lower source-to-channel barrier

- Gradually more carriers diffuse from source to drain

- Capacitive divider between gate and undepleted body

# **Subthreshold Slope**

- Planar 28nm: S = 100–110mV/dec at 25°C

- Want tight coupling of  $V_G$  to  $\phi_s$  but have to overcome  $C_{Si}$

- Large  $C_{ox} \rightarrow$  thinner gate oxide, HKMG

- Small  $C_{Si} \rightarrow$  lower body doping, FD-SOI, finFET

- Get diode limit when  $C_{ox} \rightarrow \infty \& C_{Si} \rightarrow 0 \ (\eta = 1)$

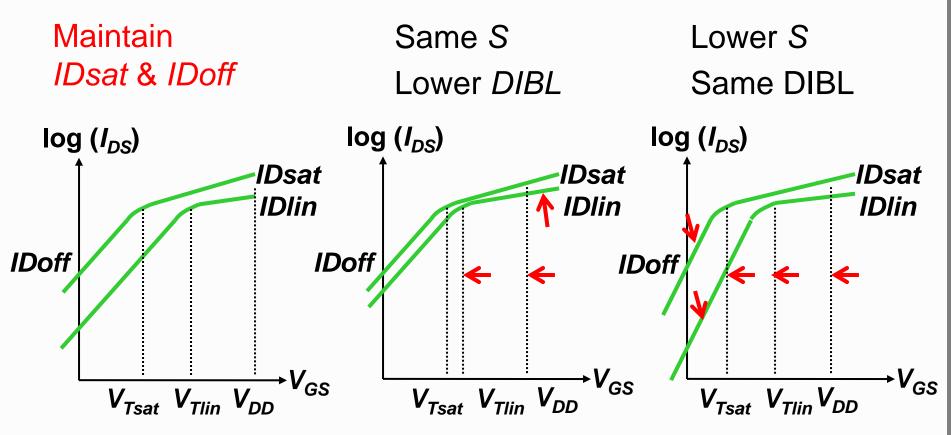

- Reducing S enables lower  $V_T$ ,  $V_{DD}$  & power for same  $I_{OFF}$

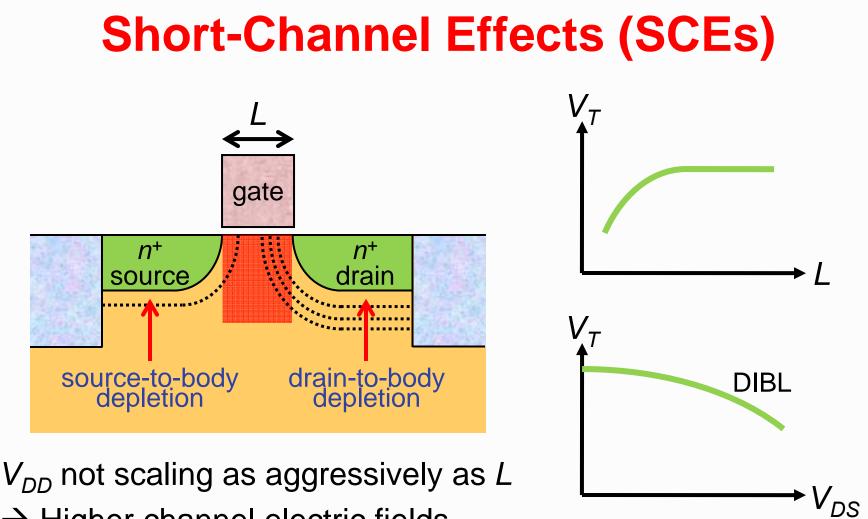

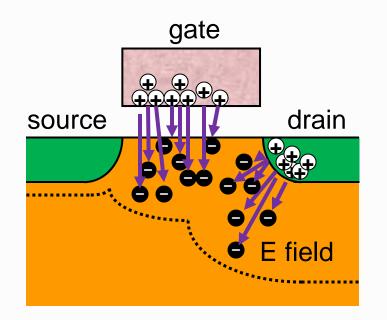

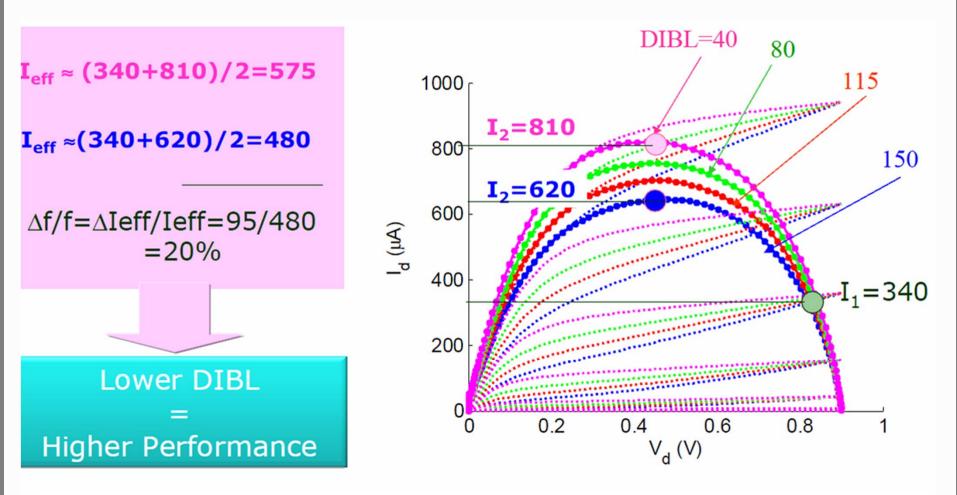

# **Drain-Induced Barrier Lowering (DIBL)**

- OFF leakage gets worse at higher V<sub>D</sub>

- E field from drain charge terminating in body, reducing gate charge required to reach  $V_T$

- Characterized as  $V_T$  reduction for some  $\Delta V_D$

- Planar 28nm: 150–160mV for  $\Delta V_D = 1V$

- Reducing DIBL also enables lower V<sub>DD</sub> & power for same I<sub>OFF</sub>

# **3-Way Competition for Body Charge**

#### **Clever Answer**

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

# Outline

#### • Part 1

- Motivation

- MOSFET & Short-Channel Fundamentals

- Lithography

- Getting to 130nm

- More MOSFET Fundamentals

#### • Part 2

#### - Strain Engineering (90nm & Beyond)

- High-K / Metal-Gate (45nm & Beyond)

- Migrating to Fully-Depleted (22nm & Beyond)

- Tri-Gate FinFETs

- Conclusions

#### **The Roads to Higher Performance**

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

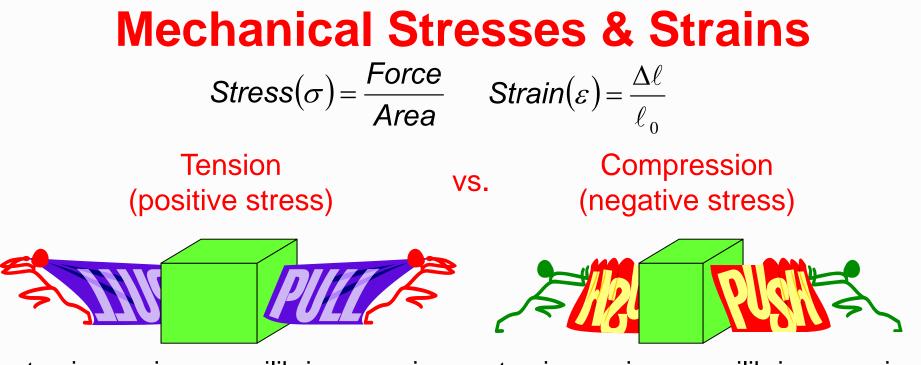

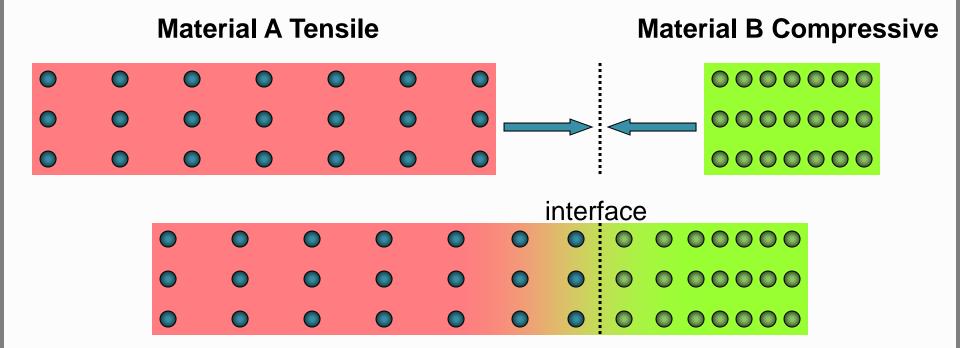

atomic spacing > equilibrium spacing

atomic spacing < equilibrium spacing

- Stretching / compressing FET channel atoms by as little as 1% can improve electron / hole mobilities by several times

- Strain perturbs crystal structure (energy bands, density of states, etc.) → changes effective mass of electrons & holes

- Increase  $I_{ON}$  for the same  $I_{OFF}$  without increasing  $C_{OX}$

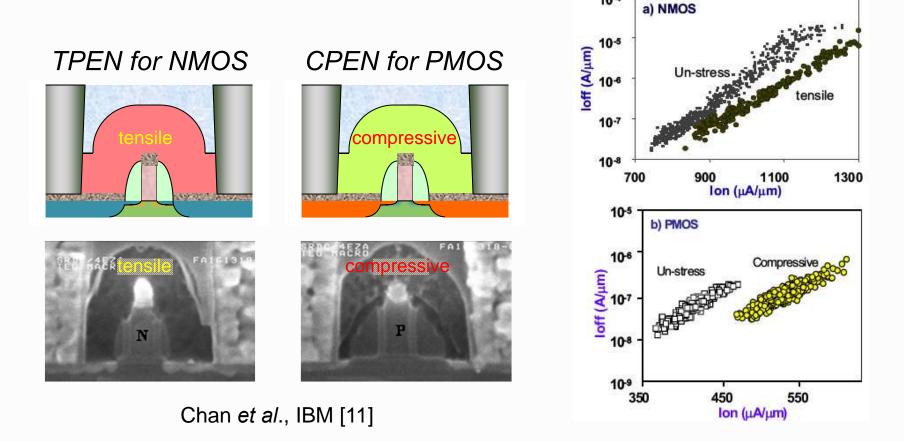

# **Longitudinal Uni-Axial Strain**

tension (stretch atoms apart)  $\rightarrow$  faster NMOS

compression (squeeze atoms together)  $\rightarrow$  faster PMOS

- Most practical means of incorporating strain for mobility boost

- Want 1-3GPa (high-strength steel breaks at 0.8GPa)

- How? Deposit strained materials around channel

- Material in tension wants to relax by pulling in

- Material in compression wants to relax by pushing out

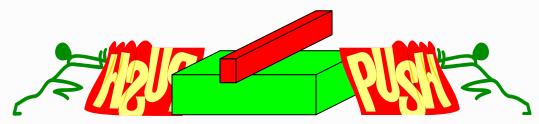

## **Transferring Strain from Material A to B**

## Ways to Incorporate Uni-Axial Strain

- NMOS wants tension, PMOS wants compression

- Un-Intentional (comes for *free*)

- Intentional (requires extra processing)

- Stress Memorization Technique NMOS ©

- Embedded-SiGe Source/Drain PMOS ③

- Embedded-SiC Source/Drain NMOS ③

- Dual-Stress Liners NMOS © & PMOS ©

- Compressive Gate Fill NMOS © / PMOS 😕

- Strain methods are additive

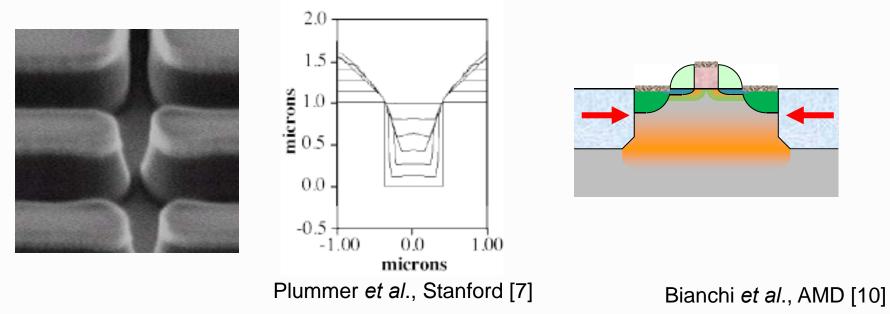

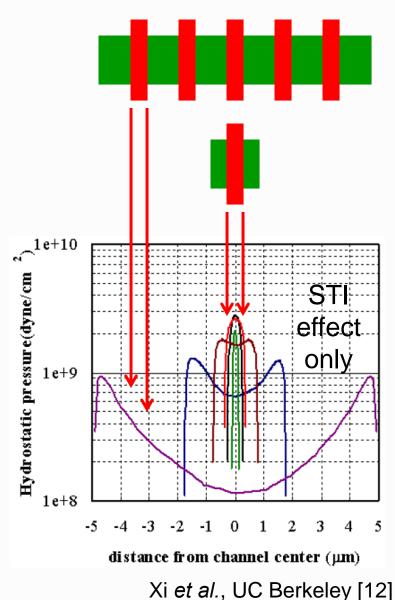

#### Shallow Trench Isolation (STI) NMOS 🛞 & PMOS 🙄

- STI oxide under compression

- High-Density Plasma CVD SiO<sub>2</sub> process (alternating deposition/etch) deposits intrinsically compressive oxide for good trench fill

- $10 \times \text{CTE}$  mismatch between Si & SiO<sub>2</sub> increases compression when cooled from deposition temperature

- Migrated to High Aspect Ratio Process (HARP) fill in recent nodes

→ less compressive oxide

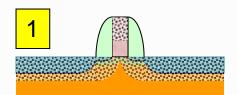

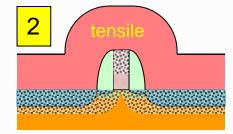

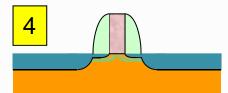

#### Stress Memorization Technique (SMT) NMOS ©

Amorphize poly & diffusion with silicon implant

Deposit tensile nitride

Anneal to *make nitride more tensile* and transfer nitride tension to crystallizing amorphous channel

Remove nitride stressor (tension now frozen in diffusion)

Chan et al., IBM [11]

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

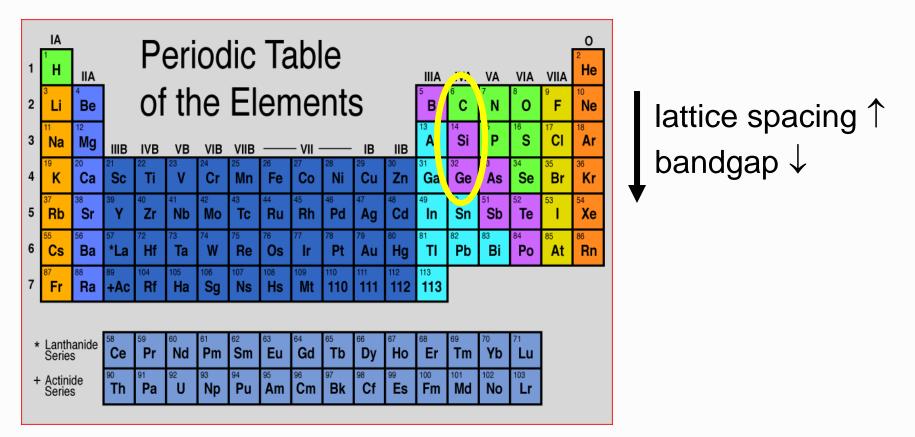

## **Periodic Table Trends**

- Compound semiconductor like Si<sub>x</sub>Ge<sub>1-x</sub> has lattice spacing & bandgap between Si & Ge

- Same idea with Si<sub>x</sub>C<sub>1-x</sub>

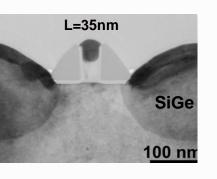

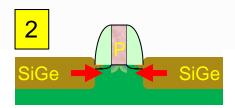

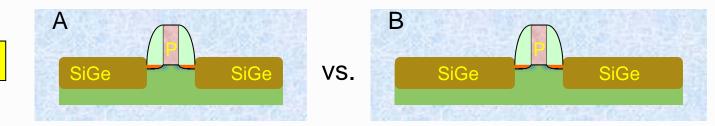

## Embedded-SiGe Source/Drain (e-SiGe) PMOS ©

- SiGe constrained to Si lattice will be in compression

- Compressive SiGe source/drain transfers compression to Si channel

Etch source/drain recess

Grow SiGe epitaxially in recessed regions

- e-SiC is similar but introduces tension instead

- Epitaxial SiC much tougher to do than SiGe

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

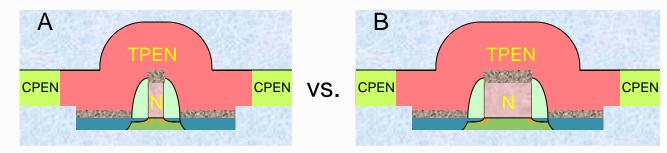

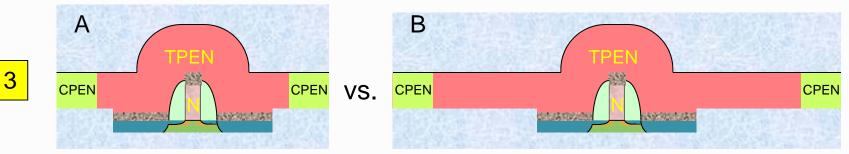

#### Dual-Stress Liners NMOS © & PMOS ©

- Deposit tensile/compressive PECVD SiN (PEN) liners on N/PMOS

- Liner stress is dialed in by liner deposition conditions (gas flow, pressure, temperature, etc.)

# **Strain Relaxation**

When materials of different strain come together...

- Both materials will relax at the interface

- Extent of relaxation is gradual, depends on distance from interface

- No relaxation far away from interface

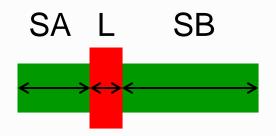

# **Strain Depends on Channel Location**

SA, L & SB specify where channel is located along active area

- Critical for modeling device mobility change due to STI, SMT & e-SiGe/e-SiC

- Strain at source & drain ends of channel may be different

- Important consideration for matching, e.g., current mirrors

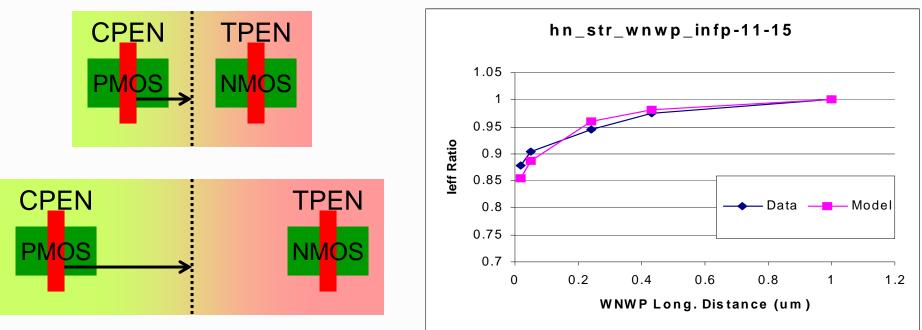

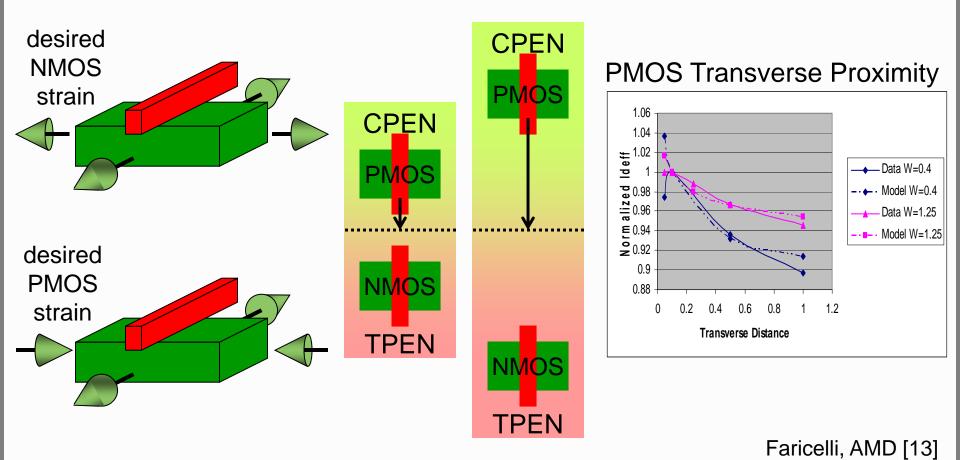

# **Longitudinal DSL Proximity**

- Opposite device type nearby in longitudinal direction reduces impact of stress liner → mutually slow each other down

- Opposite PEN liner absorbs/relieves stress introduced by PEN

#### **PMOS Longitudinal Proximity**

Faricelli, AMD [13]

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

## **Transverse DSL Proximity**

- Both NMOS & PMOS like tension in transverse direction, unlike longitudinal direction

- NMOS near PMOS in width direction  $\rightarrow$  helps PMOS, hurts NMOS

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

#### **Pop Quiz** Which FET has more channel strain?

B. Extending SiGe source/drain transfers more compression to channel

2

A. Shorter channel feels more surrounding stresses – short L vs. long L

B. Extending PEN liner transfers more stress to channel

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

# **Solving Limits**

After explaining to a student through various lessons and examples that:

$$\lim_{x \to 8} \frac{1}{x-8} = \infty$$

I tried to check if she really understood that, so I gave her a different example. This was the result:

$$\lim_{x \to 5} \frac{1}{x-5} = \infty$$

# Outline

#### • Part 1

- Motivation

- MOSFET & Short-Channel Fundamentals

- Lithography

- Getting to 130nm

- More MOSFET Fundamentals

#### • Part 2

- Strain Engineering (90nm & Beyond)

- High-K / Metal-Gate (45nm & Beyond)

- Migrating to Fully-Depleted (22nm & Beyond)

- Tri-Gate FinFETs

- Conclusions

#### **The Roads to Higher Performance**

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

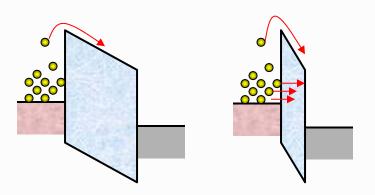

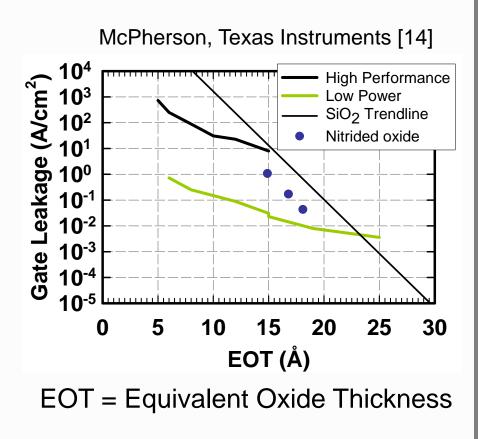

# **Direct Tunneling Gate Leakage**

- t<sub>ox</sub> had to scale with channel length to maintain gate control

- Less SCE

- Better FET performance

- Significant direct tunneling for t<sub>ox</sub>

2nm

• High-K gate dielectric achieves same  $C_{ox}$  with much thicker  $t_{ox}$

$$C_{ox} = rac{\mathcal{E}_{gate}}{t_{gate}} = rac{\mathcal{E}_{ox}}{EOT}$$

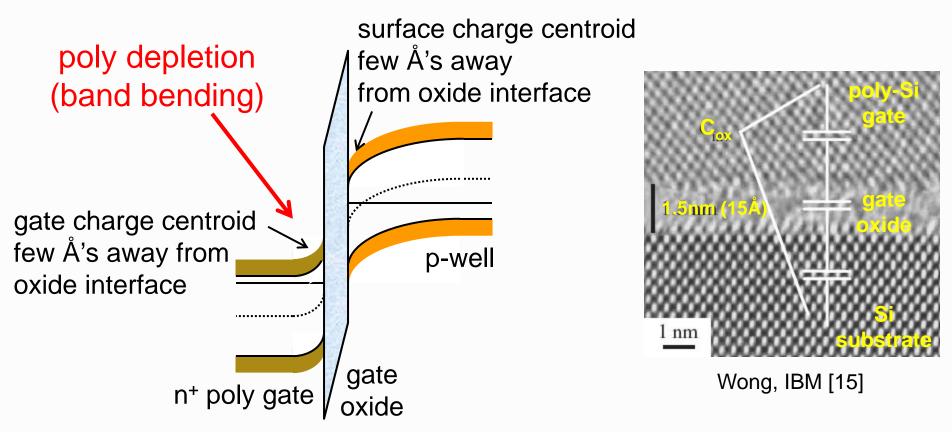

#### Poly Depletion & Charge Centroid Dielectric Only Half the Story

- Even heavily-doped poly is a limited conductor

- Discrepancy between electrical & physical thicknesses since charge is not intimately in contact with oxide interface

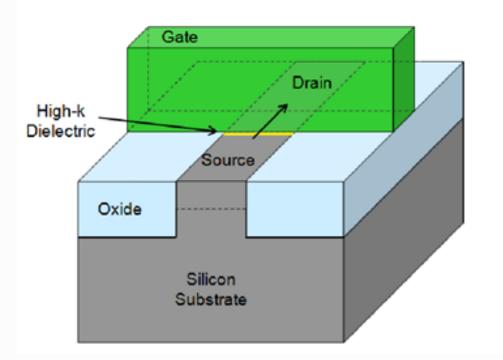

## Enter High-K Dielectric + Metal-Gate

- High-K Dielectric (HK)

- Hf-based material with K~20–30 (Zr-based also considered)

- Need to overcome hysteretic polarization

- High deposition temperature for good film quality

- Metal-Gate (MG)

- Thin conductive film intimately in contact with high-K dielectric to set gate work function  $\Phi_M \rightarrow V_{FB} \rightarrow V_T$

- Want band-edge  $\Phi_M$ , i.e., NMOS @  $E_C$  & PMOS @  $E_V$ (just like n<sup>+</sup> poly & p<sup>+</sup> poly)  $\rightarrow$  different MG for NMOS & PMOS

- Typically complex stack of different metal layers → secret sauce

- Key challenges

- INTEGRATION, INTEGRATION, INTEGRATION

- Getting the right  $V_T$  for both NMOS & PMOS

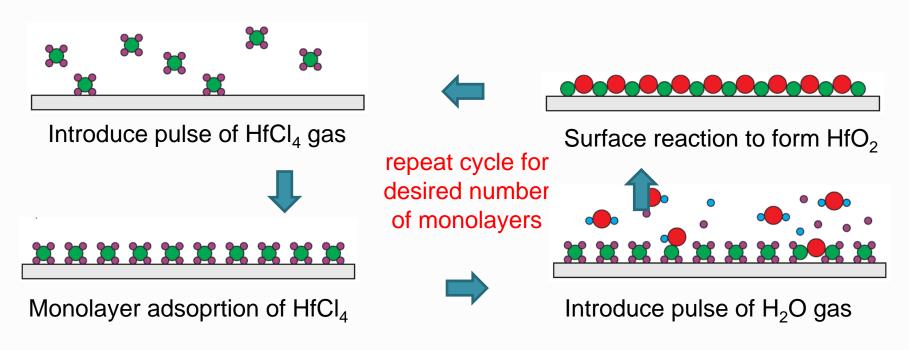

# **Atomic Layer Deposition**

- Deposit monolayer at a time using sequential pulses of gases

- Introduce one reactant at a time & purge before introducing next reactant

- Key to precise film thickness control of HKMG stack

- e.g.,  $SiO_2$  (SiCl<sub>4</sub>+H<sub>2</sub>O)  $\rightarrow$  HfO<sub>2</sub> (HfCl<sub>4</sub>+H<sub>2</sub>O)  $\rightarrow$  TiN (TiCl<sub>4</sub>+NH<sub>3</sub>)

ICKnowledge.com [16]

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

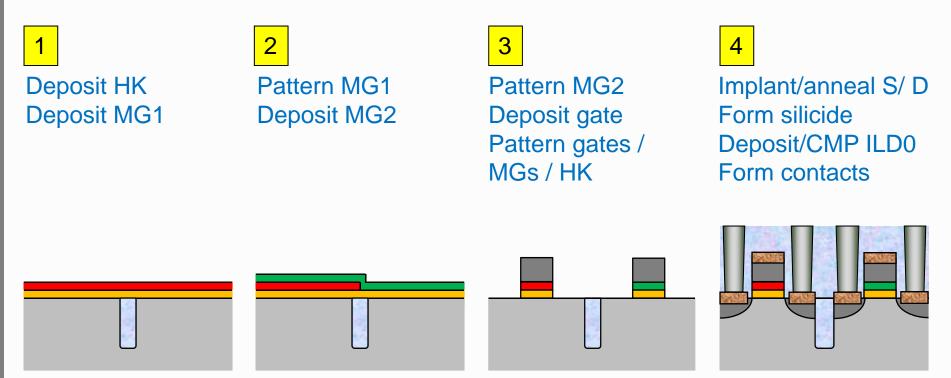

# **HK-First / MG-First Integration**

- Obvious extension of poly-Si gate integration

- Seems obvious & "easy" at first but plagued with unstable work function when HKMG is exposed to activation anneals

- Especially problematic with PMOS  $V_{\tau}$  coming out too high

### **GlobalFoundries 32nm-SOI**

Horstmann et al., GlobalFoundries [17]

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

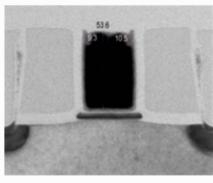

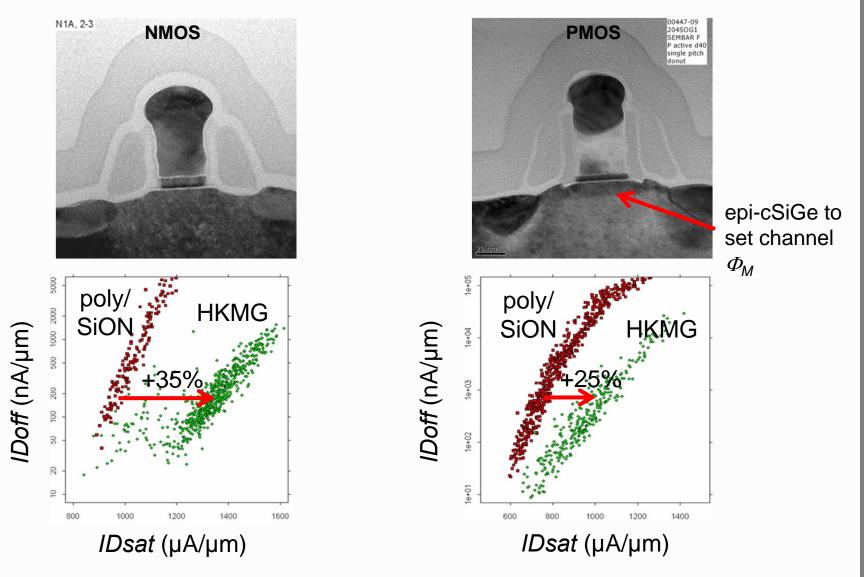

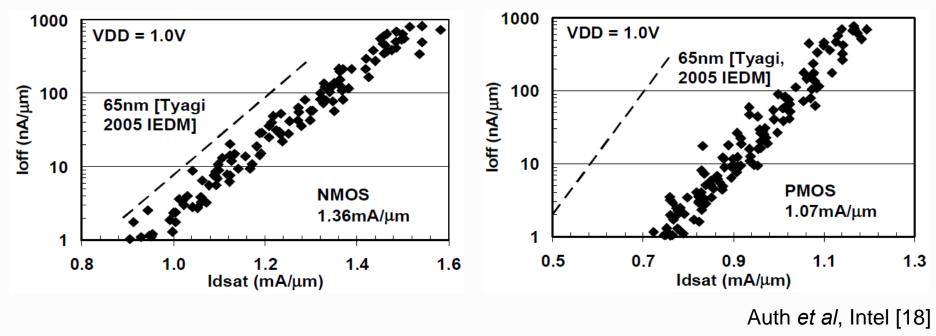

# **HK-First / MG-Last Integration**

- High thermal budget available for middle-of-line

- Low thermal budget for metal gate  $\rightarrow$  more gate metal choices

- Enhanced strain when sacrificial poly is removed & resulting trench is filled with gate fill metal

#### Intel 45nm

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

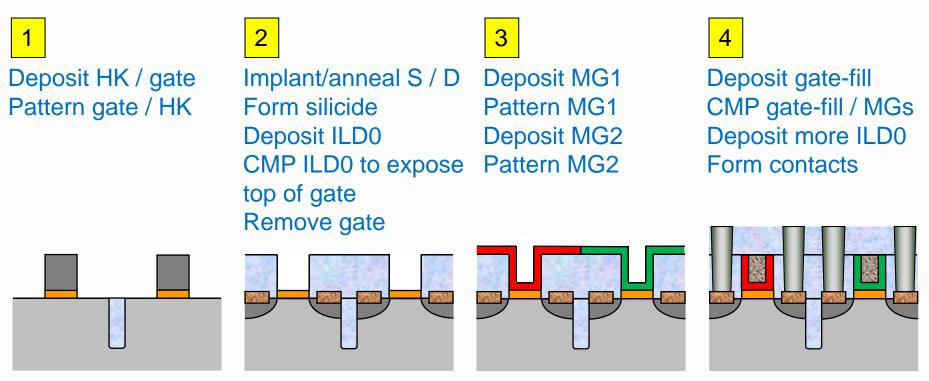

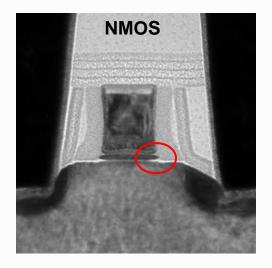

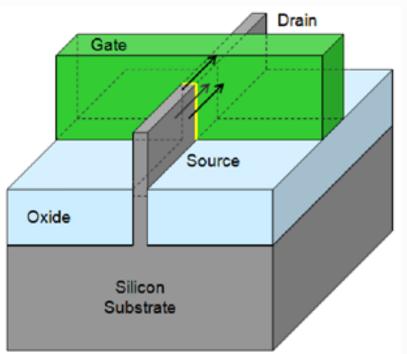

### **HK-Last / MG-Last Integration**

- Same advantages as HK-first / MG-last integration

- Overcomes EOT scaling limitations in HK-first / MG-last

- Need to postpone silicidation to after opening source/drain etch

- DSL relax & no longer useful since contacts cut through FET width

#### Intel 32nm

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

# Outline

#### • Part 1

- Motivation

- MOSFET & Short-Channel Fundamentals

- Lithography

- Getting to 130nm

- More MOSFET Fundamentals

#### • Part 2

- Strain Engineering (90nm & Beyond)

- High-K / Metal-Gate (45nm & Beyond)

#### - Migrating to Fully-Depleted (22nm & Beyond)

- Tri-Gate FinFETs

- Conclusions

### Gentlemen, at this point, reality set in...

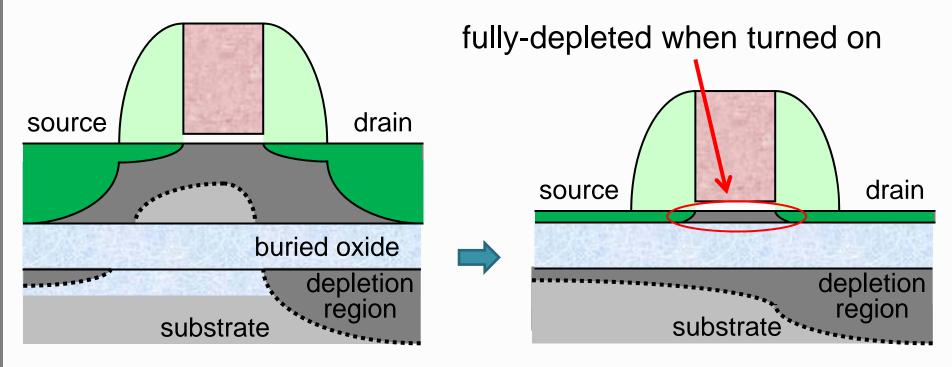

# What Does Fully-Depleted Really Mean?

Consider what happens when SOI layer thins down

- Conservation of charge cannot be violated

- So once body is fully depleted, extra gate charge must be balanced by charge elsewhere, e.g., beneath buried oxide

- If substrate is insulator, then charge must come from source/drain

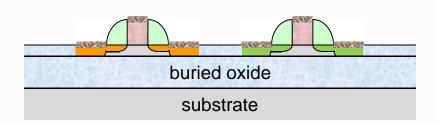

### **Benefits of Lower DIBL & S**

- Fully-depleted options

- Planar: FD-SOI, Bulk with retrograded well

- 3-D: FinFET or Tri-Gate SOI or Bulk

### **The Big Deal with Lower DIBL**

Higher performance for the same IDsat & IDoff

L. Wei et al, Stanford [20]

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

## **Body Thickness for Fully-Depleted**

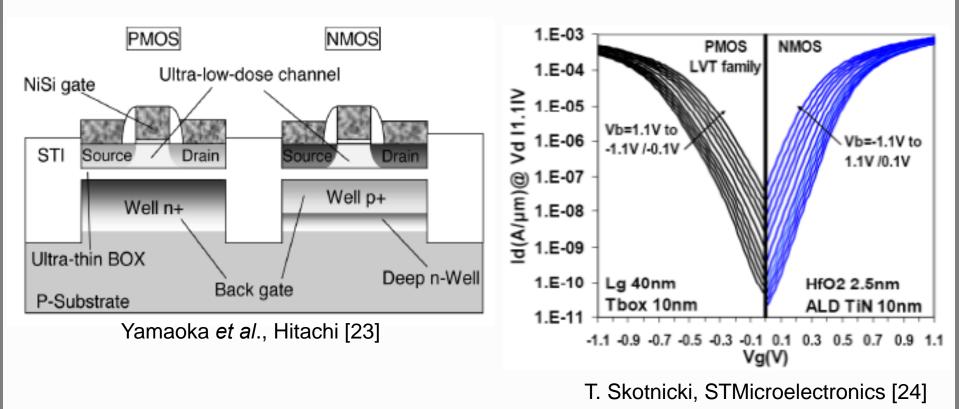

# **Fully-Depleted Planar on SOI**

- a.k.a. ET (Extremely Thin) or UTBB (Ultra-Thin Body & BOX) SOI to refer to very thin SOI and Buried Oxide (BOX) layers

- SOI Si layer is so thin that charge mirroring gate charge comes from beneath BOX

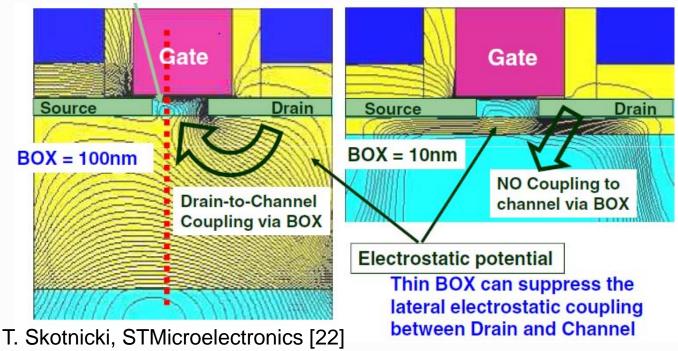

## **Thin BOX to Suppress SCE**

- Fully-depleted alone does not eliminate SCE

- Field lines from drain are still competing for body charge

- If body is fully depleted, these field lines cannot terminate in the body since there's no charge to terminate to → no DIBL

- Charge elsewhere must be nearby or field lines from drain will terminate on source charge <sup>(3)</sup>

# **Performance Tuning with Backgate Bias**

- Like a "body effect" in planar bulk with  $C_{Si}$  spanning SOI & BOX

- Backgate bias can modulate both NMOS and PMOS  $V_{\tau}$  at 80mV/V

- Not option in finFETs but finFET subthreshold slope is better

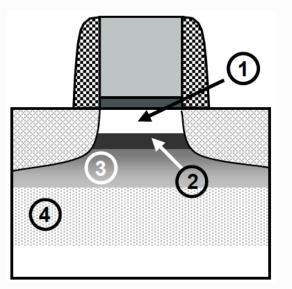

# **Fully-Depleted Planar on Bulk**

- 1 Low-doped layer for RDF reduction (fully depleted)

- 2  $V_{T}$  setting layer for multiple  $V_{T}$  devices

- 3 Highly-doped screening layer to terminate depletion

- 4 Sub-surface punchthrough prevention

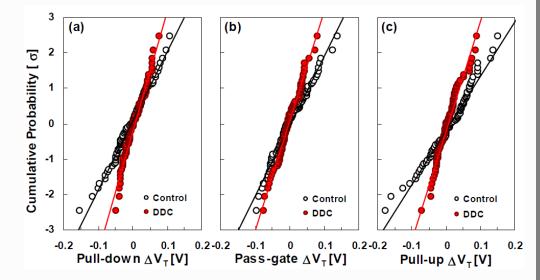

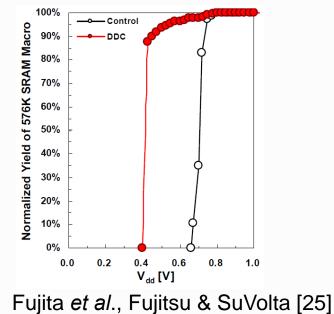

Reduced RDF for tighter  $V_T$  control & lower SRAM  $V_{DDmin}$

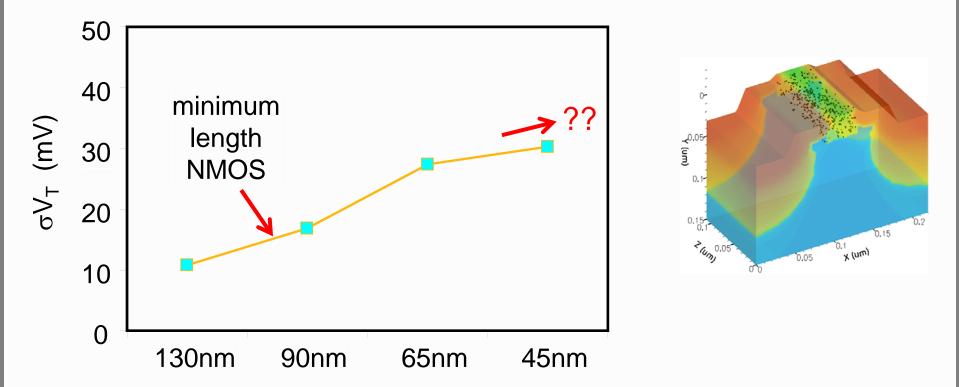

# **Random Dopant Fluctuation (RDF)**

- RDF more prevalent with scaling since number of dopants is decreasing with each MOS generation

- Why does RDF impact magically disappear in fully-depleted?

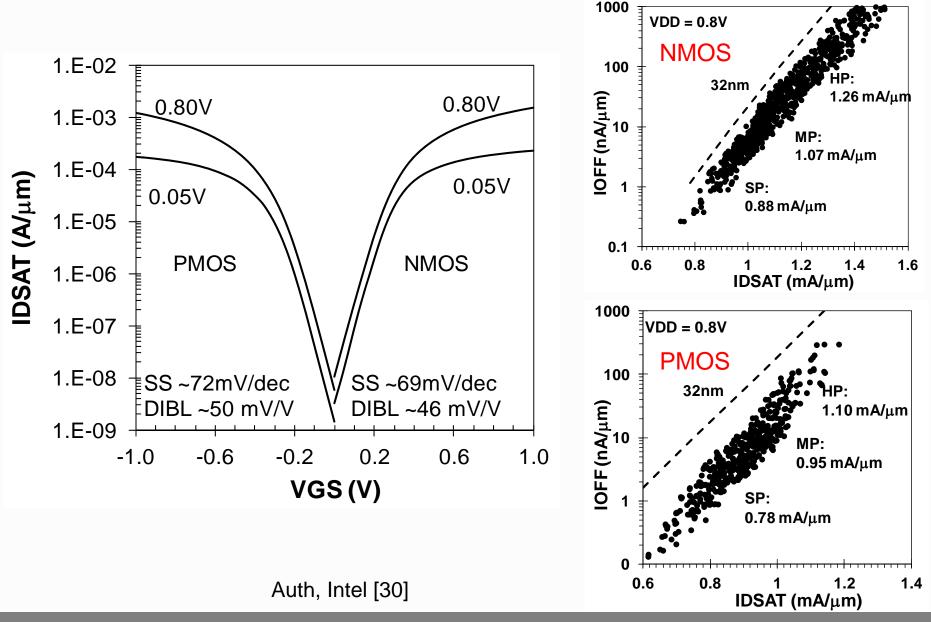

Auth, Intel [18]

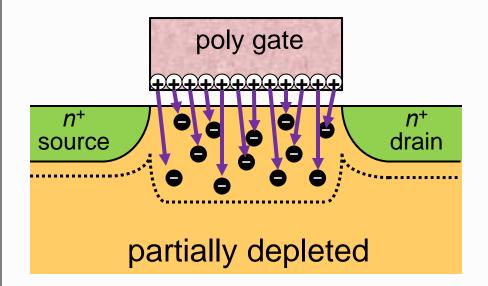

## **RDF in Conventional MOS**

- Back to basics

- Conservation of charge

- Electric field lines start at +ve charge & end at -ve charge

- Random locations of dopant atoms

- Lengths of field lines exhibit variation

- Integrated field (voltage or band bending) has  $V_T$  variation

$$V = -\int E \cdot dx$$

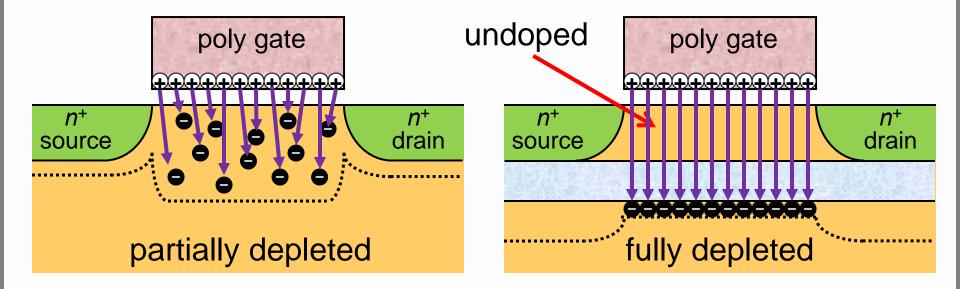

# Why Fully-Depleted Eliminates RDF

- In fully-depleted SOI, field lines from gate cannot terminate in the undoped body (no charge there)

- Mirror charges are localized beneath BOX

- Lengths of field lines have very tight distribution

- $V_{T}$  variation is small

- However,  $V_T$  now very sensitive to dimensional variation, e.g., SOI and BOX thickness

#### **Creative Answer**

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

# Outline

#### • Part 1

- Motivation

- MOSFET & Short-Channel Fundamentals

- Lithography

- Getting to 130nm

- More MOSFET Fundamentals

#### • Part 2

- Strain Engineering (90nm & Beyond)

- High-K / Metal-Gate (45nm & Beyond)

- Migrating to Fully-Depleted (22nm & Beyond)

#### – Tri-Gate FinFETs

Conclusions

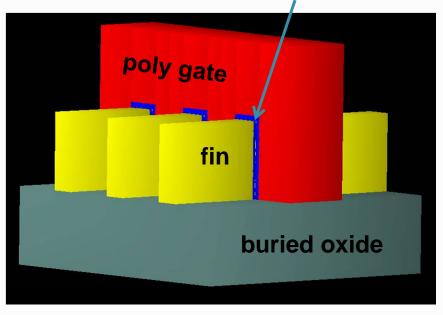

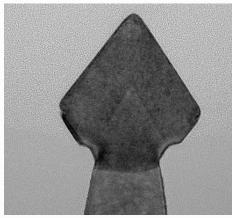

# What is Fully-Depleted Tri-Gate?

#### 32nm planar

#### 22nm tri-gate

- Channel on 3 sides

- Fin width is *quantized* (SRAM & logic implications)

Hu, UC Berkeley [26] M. Bohr, Intel [27]

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

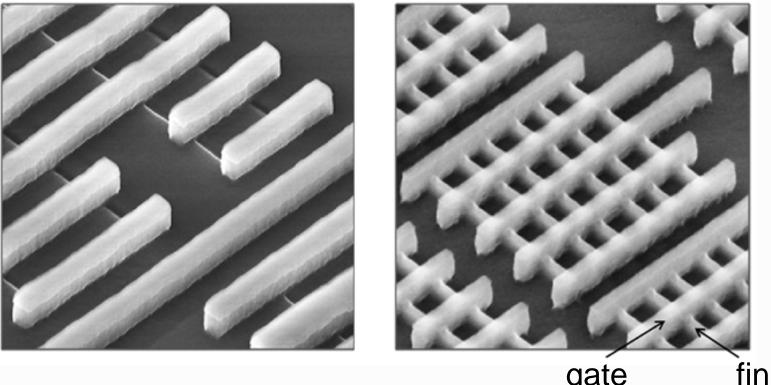

### **Tri-Gate FinFETs in Production**

#### 32nm planar

#### 22nm tri-gate

gate

#### Truly impressive!!!

M. Bohr, Intel [27]

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

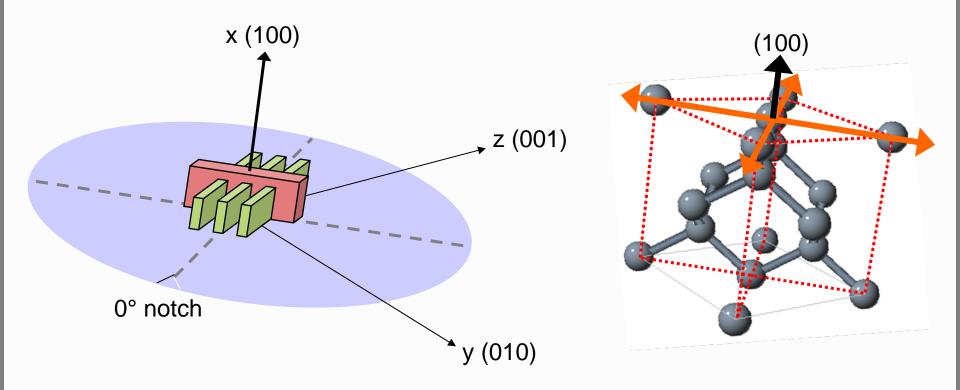

# **Conventional Wafer Surface Orientation & Channel Direction**

- Wafer normal is (100), current flows in <110> direction

- Tri-Gate FinFET: top surface (100), sidewall surfaces (110)

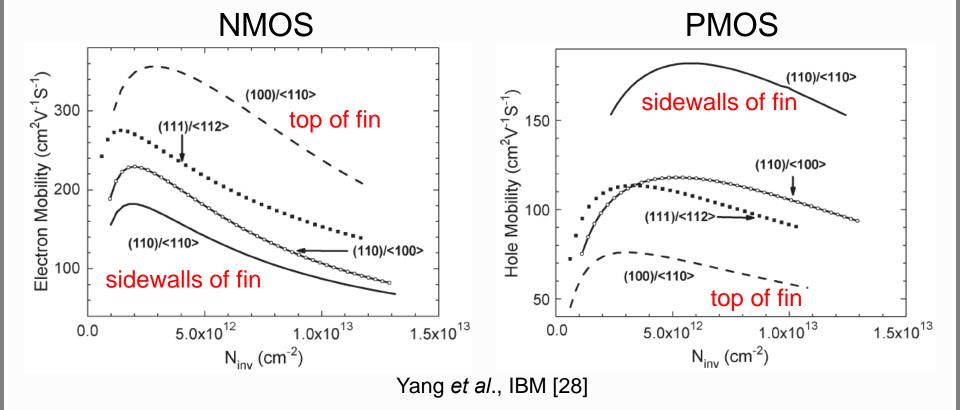

# Mobility Dependence on Surface Orientation & Direction of Current

Strain-induced mobility boost also depends on surface orientation & channel direction – not as strong for current along sidewalls vs. top of fin

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

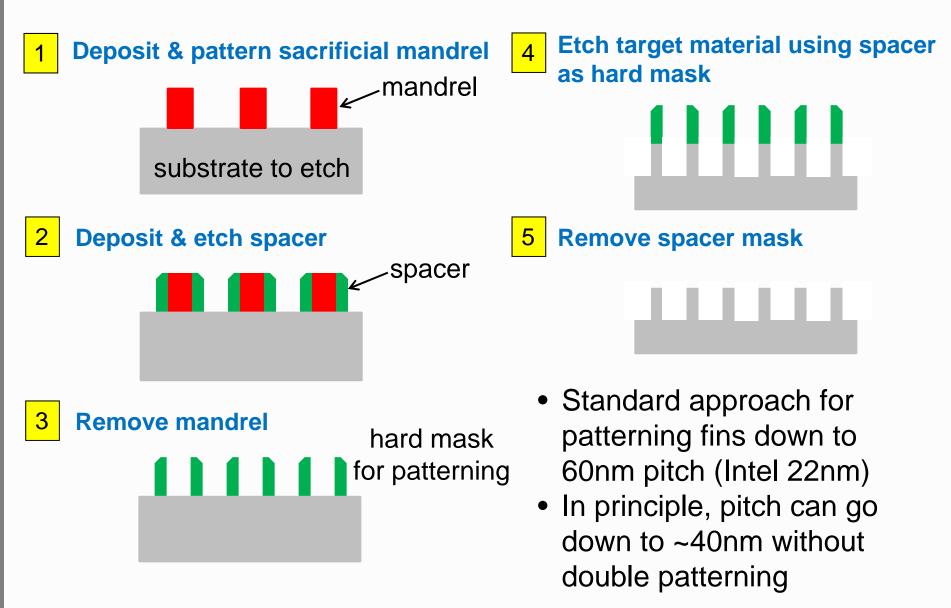

# Fin Patterning – Sidewall Image Transfer

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

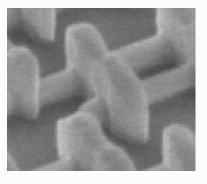

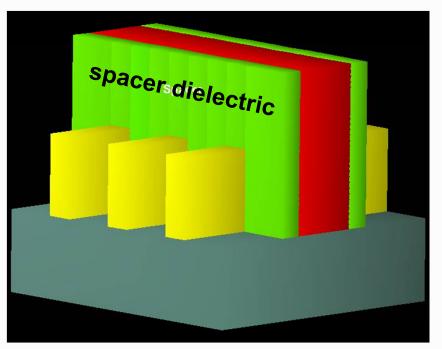

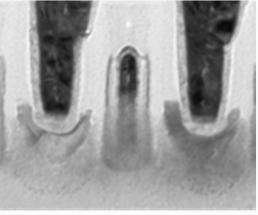

### **Process Flow Summary I**

- Example shows tri-gate on SOI but bulk flow is similar

- Pattern fins using SIT

- Deposit/CMP STI oxide

- Recess STI oxide by fin height

- Deposit, CMP & pattern poly

gate oxide on top & both sidewalls of fin

- Deposit spacer dielectric & etch, leaving spacer on gate sidewalls

- Spacer must be removed on fin sidewall

#### Paul, AMD [29]

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

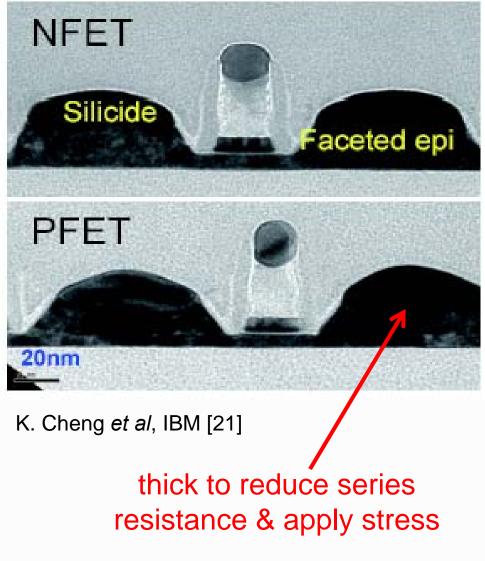

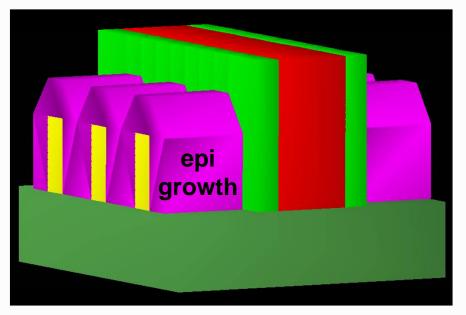

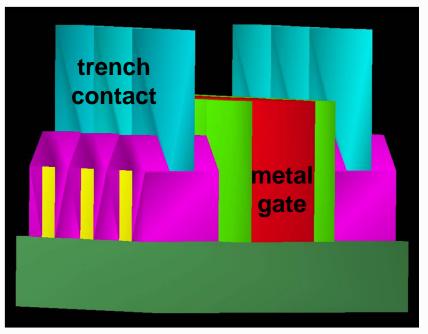

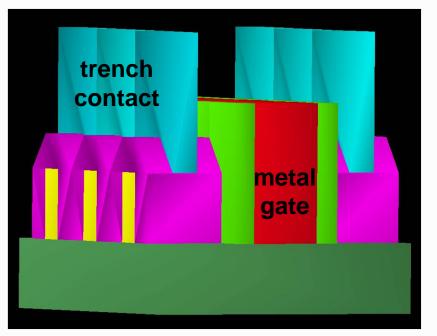

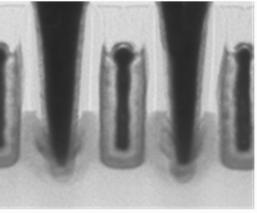

# **Process Flow Summary II**

- Recess fins

- Grow Si epitaxially to merge fins together for reduced source/drain resistance

- Induce uni-axial channel strain by growing e-SiGe or e-SiC

- Source/drain dopants come from in situ doping during epi

- Deposit ILD0 & CMP to top of poly

- Do replacement-gate HKMG module

- Deposit & pattern contact dielectric

- Form trench contacts (note overlap capacitance to gate)

Paul, AMD [29]

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

### **Some Tri-Gate Considerations**

- Field lines of from gate terminates at base of fins

- Fin base must be heavily doped for fin-to-fin isolation

- Dimensional variation of fins

→ device variation

- Current density is not uniform along *width* of device – V<sub>T</sub> & S varies along sidewall

- Series resistance vs. overlap capacitance

# **Pacifying The Multi-V<sub>7</sub> Addiction**

- 8  $V_T$ 's typical in 28nm (NMOS vs. PMOS, thick vs. thin oxide)

- Methods of achieving multiple  $V_T$

- 1. Bias channel length

- Exploit SCE ( $V_T$  rolloff with shorter L)

- Increase *L* for lower *I*<sub>ON</sub> & *I*<sub>OFF</sub>

- 2. Implant fin body with different dose

- Field lines from gate must terminate on available body dopants before terminating at base of fin

- Prone to RDF

- 3. Integrate different metal gate  $\Phi_M$

- Already 2  $\mathcal{P}_M$  s in standard HKMG flow

- More complex integration

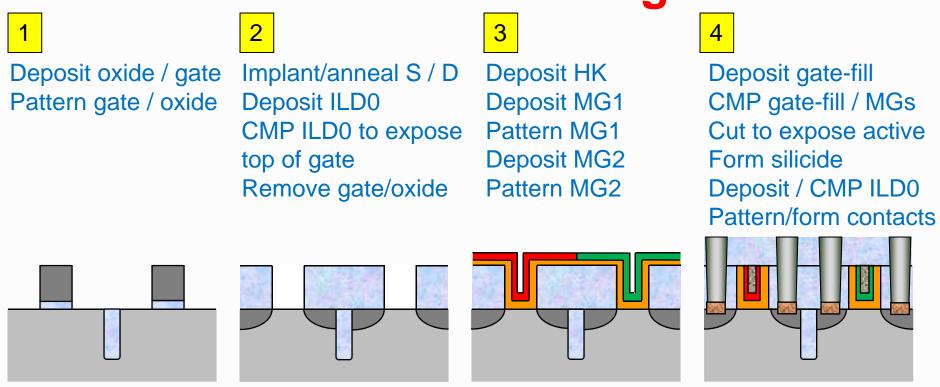

### Intel 22nm TEM Cross-Sections

#### Single fin (along W)

#### Epi merge (along W)

#### NMOS (along L)

#### PMOS (along L)

Auth, Intel [30]

© Loke et al., 2D to 3D MOS Technology Evolution for Circuit Designers

### Intel 22nm Performance at 0.8V

### Conclusions

- Digital needs will continue to drive CMOS scaling but at slower pace

- Expect new learning in 20nm & 14nm as we cope with fin design & layout

- SPICE models will lag to include new effects

- Designers with good technology knowledge are best positioned for silicon success

- Exciting time to be designing

### **References I**

- [1] M. Keating, "Science fiction or technology roadmap: a look at the future of SoC design," in *SNUG San Jose Conf.*, Mar. 2010.

- [2] L. Bair, "Process/product interactions in a concurrent design environment," in *Proc. IEEE Custom Integrated Circuits Conf.*, pp. 779–782, Sep. 2007.

- [3] M. Na *et al.*, "The effective drive current in CMOS inverters," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, pp. 121–124, Dec. 2002.

- [4] S.M. Sze, *Physics of Semiconductor Devices (2<sup>nd</sup> ed.)*, John Wiley & Sons, 1981.

- [5] A. Wei, "Foundry trends: technology challenges and opportunities beyond 32nm," in *IEEE Vail Computer Elements Workshop*, Jun. 2010.

- [6] www.nikon.com

- [7] J. Plummer et al., Silicon VLSI Technology– Fundamentals, Practice and Modeling, Prentice-Hall, 2000.

- [8] S. Sivakumar, "Lithography for the 15nm node," in *IEEE Int. Electron Devices Meeting Short Course*, Dec. 2010.

- [9] A. Loke *et al.*, "Constant-current threshold voltage extraction in HSPICE for nanoscale CMOS analog design," in *SNUG San Jose Conf.*, Mar. 2010.

- [10] R. Bianchi *et al.*, "Accurate modeling of trench isolation Induced mechanical stress effects on MOSFET electrical performance," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, pp. 117-120, Dec. 2002.

- [11] V. Chan *et al.*, "Strain for CMOS performance improvement," in *Proc. IEEE Custom Integrated Circuits Conf.*, pp. 667–674, Sep.2005.

- [12] X. Xi et al., BSIM4.3.0 MOSFET Model User's Manual, The Regents of the University of California at Berkeley, 2003

- [13] J. Faricelli, "Layout-dependent proximity effects in deep nanoscale CMOS," in *Proc. IEEE Custom Integrated Circuits Conf.*, pp. 1–8, Sep.2010.

- [14] J. McPherson, "Reliability trends with advanced CMOS scaling and the implications on design," in *Proc. IEEE Custom Integrated Circuits Conf.*, pp. 405–412, Sep. 2007.

- [15] P. Wong, "Beyond the conventional transistor," IBM J. Research & Development, pp. 133–168, vol. 2-3, no. 46, Mar. 2002.

- [16] www.ICKnowledge.com

- [17] M. Horstmann *et al.*, "Advanced SOI CMOS transistor technologies for high-performance microprocessor applications," in *Proc. IEEE Custom Integrated Circuits Conf.*, pp. 149–152, Sep. 2009.

### **References II**

- [18] C. Auth, "45nm high-k + metal-gate strain-enhanced CMOS transistors," in *Proc. IEEE Custom Integrated Circuits Conf.*, pp. 379–386, Sep. 2008.

- [19] P. Packan *et al.*, "High performance 32nm logic technology featuring 2<sup>nd</sup> generation high-k + metal gate transistors," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, pp. 1–4, Dec. 2009.

- [20] L. Wei *et al.*, "Exploration of device design space to meet circuit speed targeting 22nm and beyond," in *Proc. Int. Conf. Solid State Devices and Materials*, pp. 808–809, Sep. 2009.

- [21] K. Cheng et al., "Fully depleted extremely thin SOI technology fabricate by a novel integration scheme featuring implantfree, zero-silicon-loss, and faceted raised source/drain," in IEEE Symp. VLSI Technology Tech. Dig., pp. 212–213, Jun.2009.

- [22] T. Skotnicki, "CMOS technologies trends, scaling and issues," in *IEEE Int. Electron Devices Meeting Short Course,* Dec. 2010.

- [23] M. Yamaoka *et al.*, "SRAM circuit with expanded operating margin and reduced stand-by leakage current using thin BOX FD-SOI transistors," *IEEE J. Solid-State Circuits*, vol. 41, no.11, Nov. 2006.

- [24] T. Skotnicki, "Competitive SOC with UTBB SOI," in Proc. IEEE SOI Conf., Oct. 2011.

- [25] K. Fujita *et al.*, "Advanced channel engineering achieving aggressive reduction of V<sub>T</sub> variation for ultra-low power applications," in *IEEE Int. Electron Devices Meeting Tech. Dig.*, pp. 32.3.1–32.3.4, Dec. 2011.

- [26] C. Hu, "FinFET 3D transistor and the concept behind it," in *IEEE Electron Device Soc. Webinar*, Jul. 2011.

- [27] M. Bohr, "22 nm tri-gate transistors for industry-leading low power capabilities," in Intel Developer Forum, Sep. 2011.

- [28] M. Yang *et al.*, "Hybrid-orientation technology (HOT): opportunities and challenges," *IEEE Trans. Electron Devices*, vol. 53, no. 5, pp. 965–978, May 2006.

- [29] S. Paul, "FinFET vs. trigate: parasitic capacitance and resistance", AMD Internal Presentation, Aug. 2011.

- [30] C. Auth *et al.*, "A 22nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors," in *IEEE Symp. VLSI Technology Tech. Dig.*, pp. 131–132, Jun. 2012.

### **Acknowledgments**

Thanks to the authors of the countless published material used as illustrations in this presentation