| SCANIMETRICS                                                                      |        |

|-----------------------------------------------------------------------------------|--------|

| Current Wafer Probing Problems                                                    |        |

| <ul> <li>Contact Probes</li> <li>Pitch, till size, restricted pad size</li> </ul> |        |

| Pad Damage     Maximum allowable damaged area                                     |        |

| •ESD Structures                                                                   |        |

| How : Non-contact Test Access                                                     | 2))    |

| March 11, 2009                                                                    | Page 5 |

| SCANIMETRICS                                                                                                                                           |                          |                       |                          |                            |                     |               |              |      |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------|--------------------------|----------------------------|---------------------|---------------|--------------|------|------|

| I/O Issues – Pa                                                                                                                                        | d Pit                    | tch a                 | nd E                     | SD                         |                     |               |              |      |      |

|                                                                                                                                                        | 2006                     | 6 ITRS fc             | or Test                  |                            |                     |               | 5            |      |      |

|                                                                                                                                                        |                          |                       |                          | Year o                     | f Prod              | uction        |              |      |      |

| I/O Pad Min. Dimension (µm)                                                                                                                            | 2005                     | 2006                  | 2007                     | 2008                       | 2009                | 2010          | 2011         | 2012 | 2013 |

| Wirebond                                                                                                                                               | 35                       | 30                    | 30                       | 25                         | 25                  | 25            | 25           | 20   | 20   |

| <ul> <li>Bond / probe pad<br/>dimensions accord</li> <li>Probes: Pitches r</li> <li>Pad Damage: Madecreasing</li> <li>ESD structures accord</li> </ul> | rding<br>not sl<br>aximu | to M<br>hrink<br>um a | loore<br>ing, t<br>llowa | e's La<br>tip si<br>able o | aw<br>zes r<br>dama | not c<br>aged | hang<br>area | -    |      |

| <ul> <li>ESD structures at</li> </ul>                                                                                                                  | nect                     | sign                  | ai sp                    | eeu                        | anu                 | powe          | 31           |      |      |

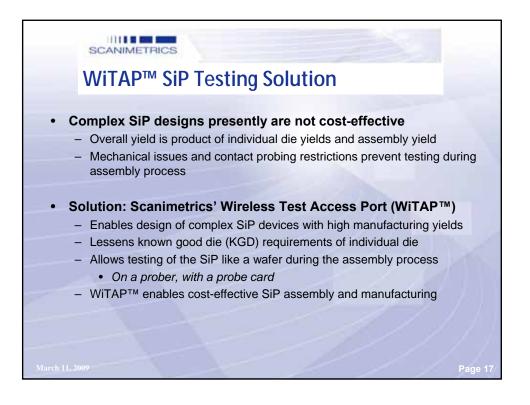

| SCANIMETRICS<br>SiP Challenges                                                                                                                                                                                                                                                                                                                                                                                    |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| <ul> <li>Assembly yields low         <ul> <li>Yield is product of die yields</li> <li>Testability during assembly is non-existent</li> <li>Probing SiP modules difficult due to                 <ul> <li>Mechanical issues</li> <li>Varying component heights</li> <li>Good die lost during substrate build-up process</li> </ul> </li> </ul> </li> <li>Design kits for SiP not available from Vendors</li> </ul> | Y - X  |

| Vendor availability for start-up volumes     – Lack of low-volume manufacturing capacity                                                                                                                                                                                                                                                                                                                          | Page 9 |

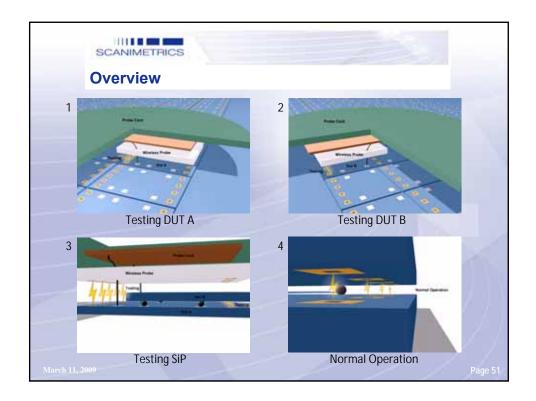

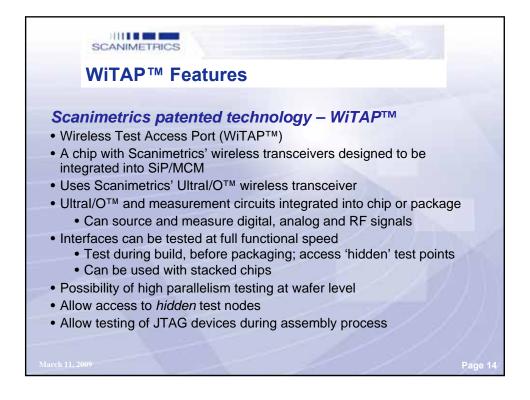

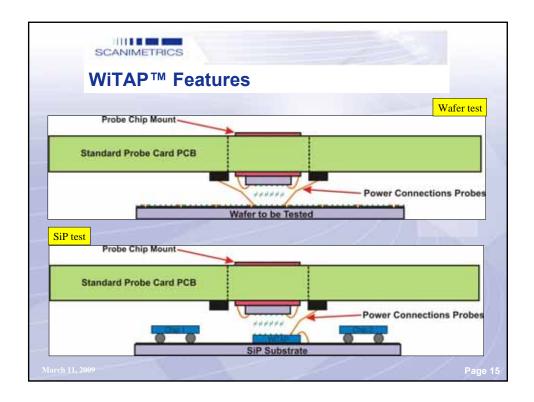

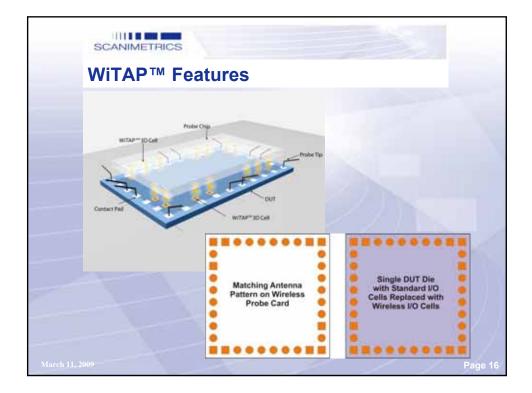

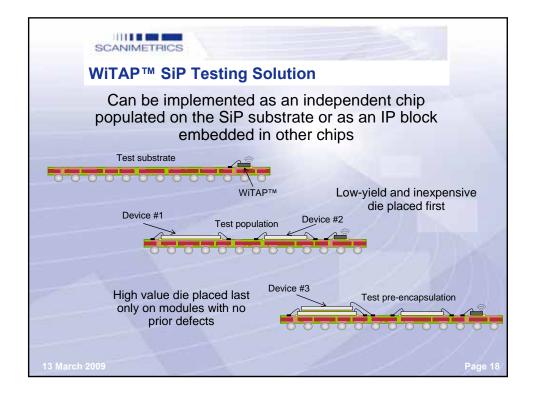

| WiTAP™ SiP Testing                             | Solution                                                                                                                                               |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Features                                       | Benefits                                                                                                                                               |

| Monitor quality of SiP<br>process in real-time | <ul> <li>Detect problems earlier<br/>in the process</li> <li>Early detection yield<br/>excursions</li> <li>Reduce number of dies<br/>wasted</li> </ul> |

|                                                | Reduce assembly cost<br>up to 30% or more                                                                                                              |

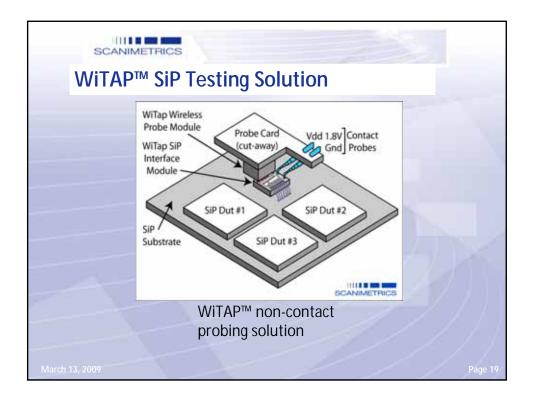

| SCANIMETRICS<br>WITAP™ SiP Testing              | Solution                                                                                                                                                   |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Features                                        | Benefits                                                                                                                                                   |

| Non-contact signal<br>probing at high<br>speeds | <ul> <li>Less probing debris</li> <li>Less damage to circuits<br/>and pads</li> <li>Less damage to probe<br/>cards</li> <li>More robust process</li> </ul> |

| 13 March 2009                                   | Full speed testing at<br>wafer level Page 2                                                                                                                |

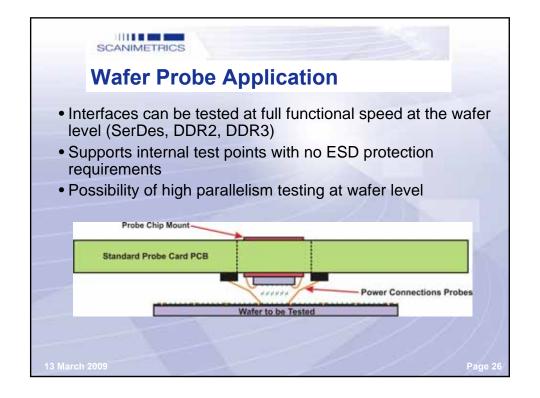

| Wafer Probe Sol                           | ution                                                                                                                         |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Features                                  | Benefits                                                                                                                      |

| Non-contact signal probing at high speeds | <ul> <li>Less probing debris</li> <li>Less damage to circuits<br/>and pads</li> <li>Less damage to probe<br/>cards</li> </ul> |

|                                           | <ul> <li>Less I/O pads and<br/>routing area</li> <li>More robust process</li> </ul>                                           |

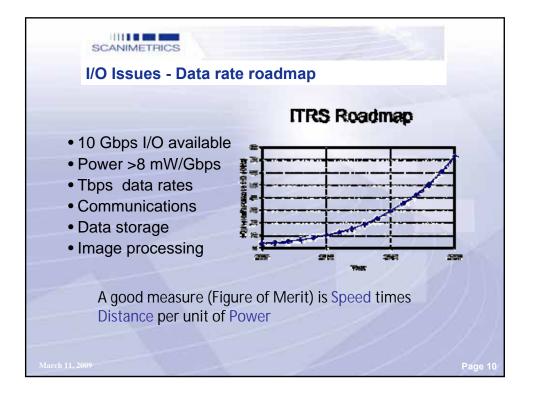

| SCANIMETRICS<br>I/O Issues - Data rate roadmap                                                                                                     |         |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Chip power density greater than a<br>'Formula One' engine<br>>1.5 kW/cu.in and increasing!                                                         |         |

| <ul> <li>Current technology is out of Gas!!!!</li> <li>I/O performance measured by speed, power, distance, density (size)</li> </ul>               |         |

| <ul> <li>I/O complexity is increasing</li> <li>Speed is available at expense of power</li> <li>I/O is not scaling with technology nodes</li> </ul> | M       |

| <ul> <li>Chips are pad and power limited</li> <li>Power at Gigabit rates needs to fall</li> <li>Testability issues</li> </ul>                      |         |

| March 13, 2009                                                                                                                                     | Page 33 |

| SCANIMETRICS                                                                                                                                                                                             |        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| The Options – Wired or Wireless                                                                                                                                                                          |        |

| Optical                                                                                                                                                                                                  |        |

| <ul> <li>Does not have many of the limitations present in electrical<br/>signals. However, to enter the optical domain electrical<br/>signals have to be converted using optical transceivers</li> </ul> |        |

| <ul> <li>These circuits dissipate almost as much power as transceive<br/>that drive PCBs and short backplanes</li> </ul>                                                                                 | ers    |

| <ul> <li>Only useful alternative is to have signal processed and<br/>transmitted entirely in optical domain. However, there are<br/>many performance problems with silicon photonics</li> </ul>          |        |

| <ul> <li>Even if performance problems are solved it is doubtful that fu<br/>optical links will be economical over short distances</li> </ul>                                                             | lly    |

| <ul> <li>Silicon having an indirect bandgap provides no easy path to<br/>the integration of optics especially with regard to photon<br/>generation</li> </ul>                                            |        |

| March 13, 2009                                                                                                                                                                                           | Page : |

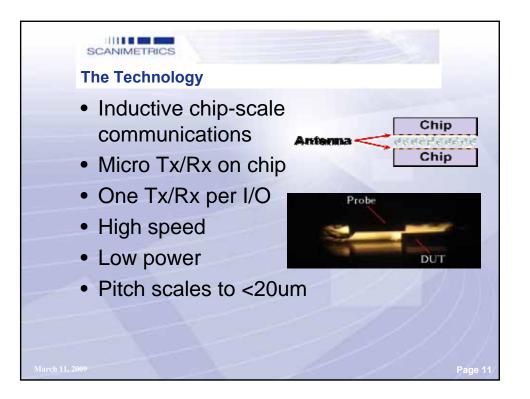

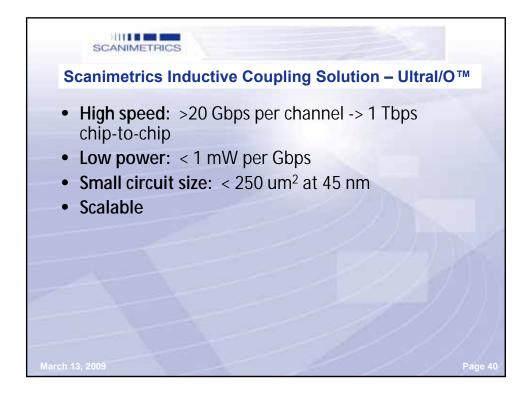

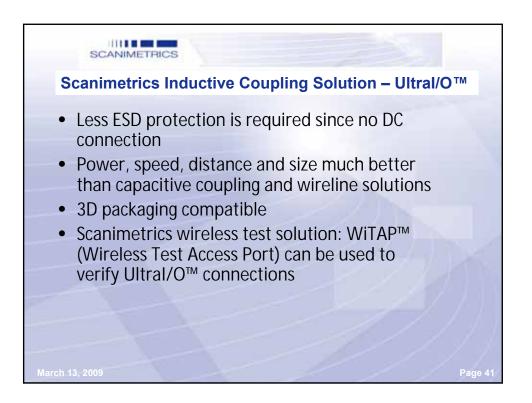

| SCANIMETRICS<br>Inductive Coupling I/O          |                                                                                                                                           |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| External<br>wire                                | Low power<br>Data rates are 2.5Gbps<br>now<br>Major target is 10 Gbps                                                                     |

| Uses the fact that tran<br>overcome input capac | <ul> <li>High Speed</li> <li>Signal Integrity</li> <li>Small Size</li> <li>Less ESD</li> <li>Sformer has inductance to itance.</li> </ul> |

| March 13, 2009                                  | Page 39                                                                                                                                   |

| SCANIMETRICS                  |                              |

|-------------------------------|------------------------------|

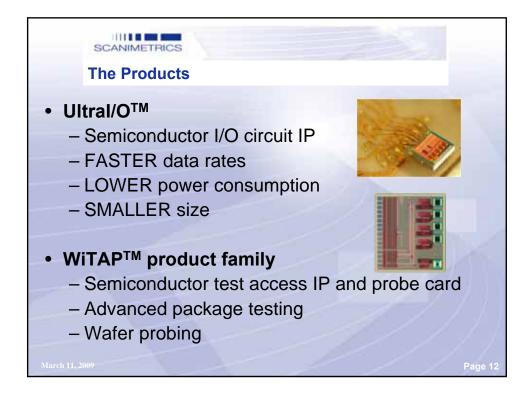

| Ultral/O™ features and        | benefits                     |

| Feature                       | Benefit                      |

| Higher Bandwidth              |                              |

| Higher performance designs    | New Applications             |

| Fewer I/Os                    | Smaller Chips                |

|                               | Less pin counts              |

|                               | Less expensive packages      |

| Lower power consumption       |                              |

| Simpler package               | Cheaper packages             |

| Less Heat                     | Simpler system level designs |

| Smaller Size                  |                              |

| Less area                     | Lower cost                   |

| Scalable                      | Future Proof                 |

| Simpler Signaling schemes     |                              |

| Easier circuit design         | Faster cycle time            |

| Simpler board/package designs | Lower cost system design     |

|                               | Page 43                      |

|             | LPDDR2 Specifications                             | Implementation Using<br>Ultral/O™                 |

|-------------|---------------------------------------------------|---------------------------------------------------|

| BOM cost    | 2 or more RAM                                     | 1 RAM                                             |

| Signal pins | 53 @ 800 Mbytes/sec<br>69 @ 3.2 Gbytes/sec        | 2 @ 800 Mbytes/sec<br>4 @ 3.3 Gbytes/sec          |

| I/O power   | 60 mW @ 800 Mbytes/sec<br>220 mW @ 3.2 Gbytes/sec | 7.2 mW @ 800 Mbytes/sec<br>30 mW @ 3.3 Gbytes/sec |

| I/O power   |                                                   |                                                   |

|             | PCI Express Gen 3<br>Specifications                | Implementation Using<br>Ultral/O™                 |

|-------------|----------------------------------------------------|---------------------------------------------------|

| Signal pins | 2 @ 800 Mbytes/sec<br>8 @ 3.2 Gbytes/sec           | 2 @ 800 Mbytes/sec<br>4 @ 3.3 Gbytes/sec          |

| I/O power   | 120 mW @ 800 Mbytes/sec<br>480 mW @ 3.2 Gbytes/sec | 7.2 mW @ 800 Mbytes/sec<br>30 mW @ 3.3 Gbytes/sec |

|             | 480 mvv @ 3.2 Gbytes/sec                           | 30 mvv @ 3.3 Gbytes/se                            |

|             | METRICS<br>arisons of Ultral/O™ to M              | IPI UniPro <sup>sm</sup>                          |

|-------------|---------------------------------------------------|---------------------------------------------------|

|             |                                                   |                                                   |

|             | MIPI UniPro Specifications                        | Implementation Using<br>Ultral/O™                 |

| Signal pins | 16 @ 800 Mbytes/sec<br>64 @ 3.2 Gbytes/sec        | 2 @ 800 Mbytes/sec<br>4 @ 3.3 Gbytes/sec          |

| I/O power   | 28 mW @ 800 Mbytes/sec<br>112 mW @ 3.2 Gbytes/sec | 7.2 mW @ 800 Mbytes/sec<br>30 mW @ 3.3 Gbytes/sec |

|             |                                                   | 111                                               |

|             |                                                   |                                                   |

|             |                                                   |                                                   |

|             |                                                   | Page                                              |