# **Embedded Passives Methodologies and Opportunities for Implementation**

#### **John Savic**

Presentation to IEEE September 24, 2009

"The Bean" in Chicago's Millennium Park

Michigan Ave skyline collapsing into the bean is a good metaphor for the product

miniaturization and the driving force for advanced integration technologies

# **Background Information**

- Collaborate with product development teams to enable manufacturing processes for improving the functionality of PWB's and advanced package substrates to meet existing and future product performance requirements.

- Focus on developing and utilizing new Embedded Passives (EP) technologies has been a consequence of pursuing the best possible solution.

- Picking a title...7 choices

- Get the Pb out with EP!

- Enabling Functionality: The Who What and How of EP

- Embedded Passives I Don't Get It!

- Embedded Passives The (For)Ever-Emerging Technology

- Embedded Passives Methodologies and Opportunities for Implementation

- Learn from what has been done and evolve

### **Outline**

- Introduction

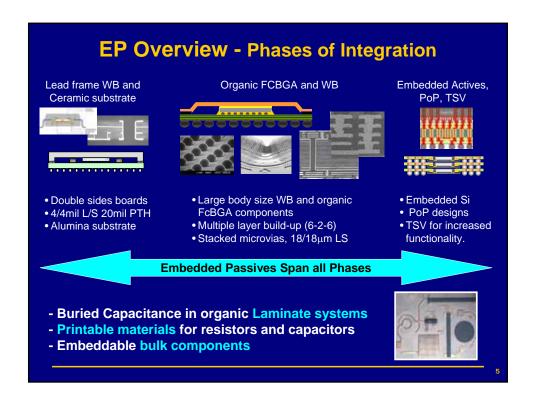

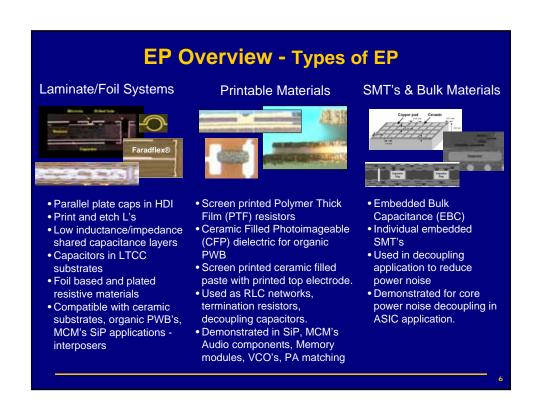

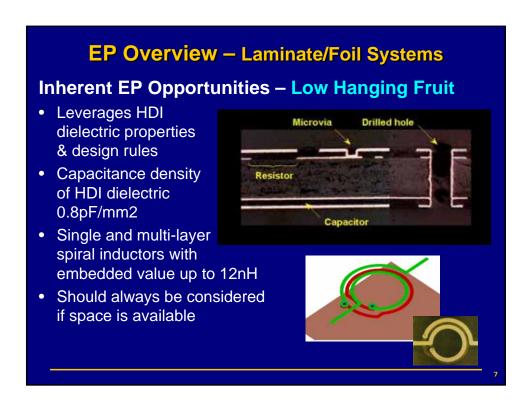

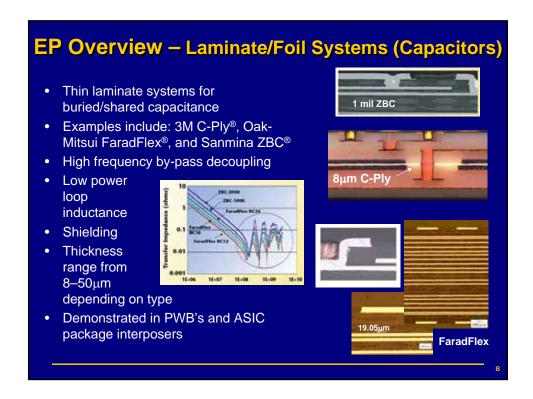

- Overview of EP technology

- EP in RF applications: Case Study of a Cost and Size Reduction Opportunity

- EP in ASIC applications: Case Study of a Performance Improvement Opportunity

- Conclusions and Key Takeaways

- Future of EP

# What are Embedded Passives (EP)? • Replace traditional Surface Mount Components with embedded equivalents - Improves electrical performance – Decoupling, lower inductance - Reduces part count - Reduces solder joints – improves reliability - Can reduce net cost in high volume applications - Reduces product thickness and overall size • Compatible with conventional manufacturing processes SMT Resistor 4-Layer FR-4 PWB

- The goal was to create an EP Rx-VCO to replace the incumbent ceramic VCO.

- Ceramic VCO was experiencing yield problems and was expensive.

- Alternative organic PWB VCO's were unable to meet size and design rule & size requirements.

- Restictions

- Must match LTCC footprint and pin-out

- Ceramic Rx-VCO

- 7 x 9 mm

- 27 SMT parts

17

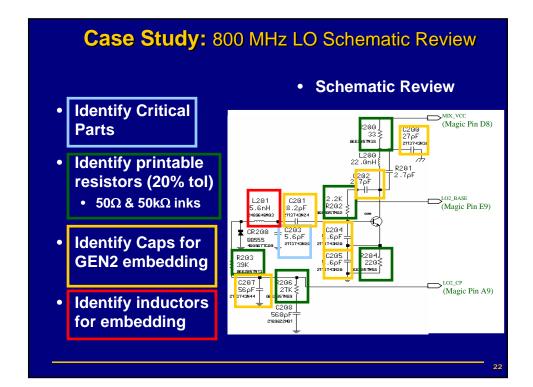

# Case A: Rx-VCO Schematic Review **Schematic review** Identify Critical **Components** Embedded R's Identify printable resistors 20% tolerance 50 & 1kΩ/□ **Identify EP caps** HDI only • 10 pF max Embedded L Identify L's Embedded C' T-lines Spiral

# Case A: RxVCO Results and Impact

- Embedded 8 resistors using 2 inks

- Embedded 3 capacitors 1.8 2.2 pF using HDI dielectric as capacitance material

- Embedded 4 inductors: Two T-Lines and two 2.5 turn spiral inductors (1.5 nH – 10 nH)

- Impact: 13 fewer parts than ceramic (10 % savings)

- Lower cost substrate (30% less) and assembly (40% less) resulting in >\$2 savings/part

- Equivalent performance and size (could have been smaller)

- Improved manufacturability and immediate high yield supply

- Implemented with Ohmega-Ply and PTF resistors

19

Case A: RxVCO Results and Impact

Spiral L's + embedded C's underneath SMTs

SMT pad on embedded C's plate

Effect of mutual capacitance

SMT pad as part of embedded C's plate/parallel C's using microvia

PTF R's terminated on embedded C's plate

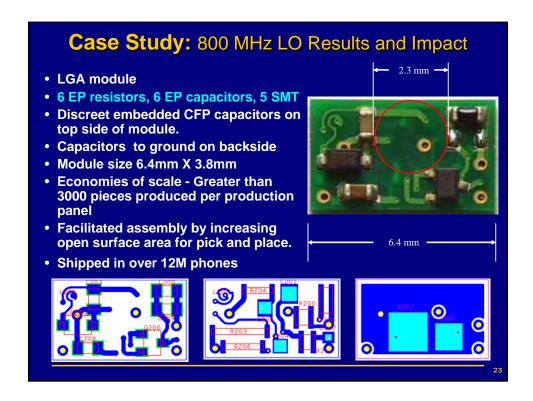

# Case B: 800 MHz LO Design Objective

- Modularize a Motherboard functionality

- Enable module reuse across products

- Must be lower cost than incumbent and offer improved yields over a non-EP based (full SMT) modular solution

#### **Incumbent Technology**

- · Discrete solution on motherboard

- Area on motherboard 48 mm<sup>2</sup>

- 18 placed parts

- Implementation cost: \$ 0.38

- DM \$ 0.20

- Conversion \$ 0.18

#### HDI EP Technology

- 1+2+1 HDI with CFP capacitors

- Module area = 24.3 mm<sup>2</sup>

- 5 placed parts

- Implementation cost: \$ 0.28

- Area reduction = 49.4 %

- Cost Reduction = 27.3 %

- Part count reduction = 13

Pick & place directly onto motherboard

EP in an ASIC Application: Case Study of a Performance Improvement Opportunity

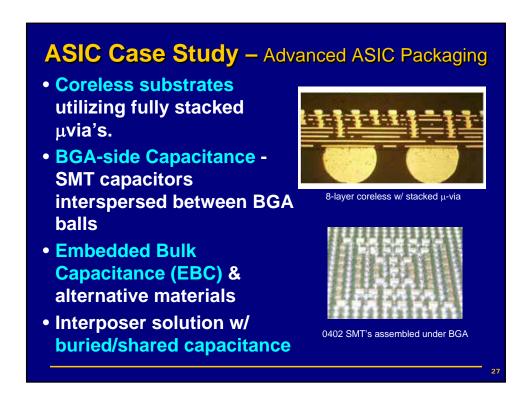

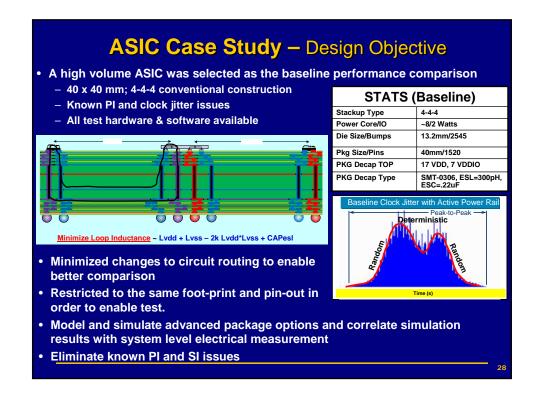

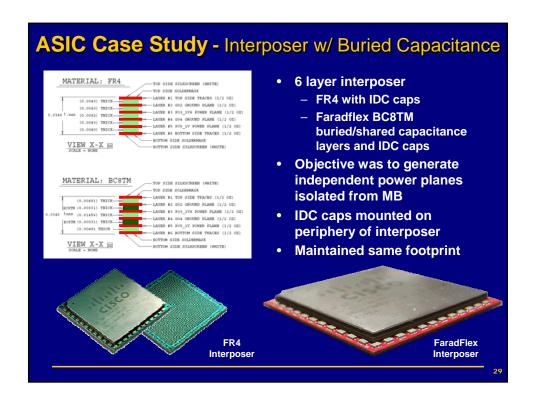

# **ASIC Case Study -** Advanced ASIC Packaging

- Next generation (90nm and below) ASIC's have significantly higher Power & Signal Integrity challenges

- Decrease in core power and higher levels of IC integration increases resultant IR drop in the power rails eroding power integrity and circuit timing margins.

- Implementation of various power saving techniques like clock gating, module power down and sleep mode, will result in steeper steps in power delivery requirements

- Noise and crosstalk will increase due to density & isolation limitations

- To overcome the challenges, next generation package substrates require revolutionary change in capability

- Decreased pkg inductance more direct connections/shorter paths

- Enable increased incidence of localized (appropriately placed) decoupling

- Increase circuit density along with methods for improved isolation

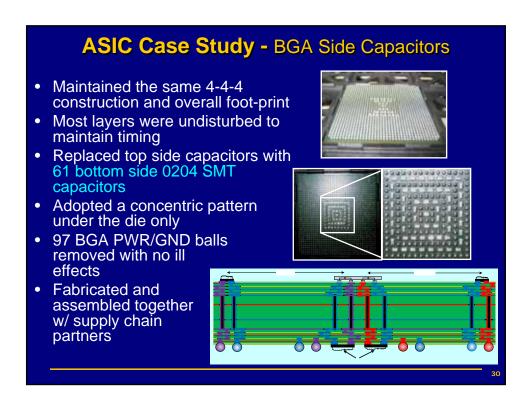

# ASIC Case Study - BGA Side Capacitor Conversion

|                  | Original<br>Package | BGA Side<br>Capacitor | Difference (%) | Number of<br>Capacitors |

|------------------|---------------------|-----------------------|----------------|-------------------------|

| GND              | 339                 | 288                   | 51<br>(15%)    |                         |

| VDD<br>(1.0V)    | 126                 | 104                   | 22<br>(17.5%)  | 31                      |

| VDDO18<br>(1.8V) | 98                  | 74                    | 24<br>(24.5%)  | 27                      |

| VDDO25<br>(2.5V) | 6                   | 6                     | 0<br>(0%)      | 3                       |

| Total            | 569                 | 472                   | 97<br>(17%)    | 61                      |

#### **Capacitor Choice dictated by the following factors:**

- Low ESL value was the key factor 83 pH.

- Size: Needed to fit in a row where the BGA balls were depopulated and the height needed to be less than the package standoff height 0204-2T t=0.35 mm. max.

- Capacitance Value: With the above constraints the maximum capacitance value available today is 0.47uF

31

# ASIC Case Study – Embedded Bulk Capacitance

- Currently it is Confidential Design information and cannot be shared

- Conventional PCB materials layer stack-up

- "Next best thing" to capacitance on the die

- Available commercially in low volume

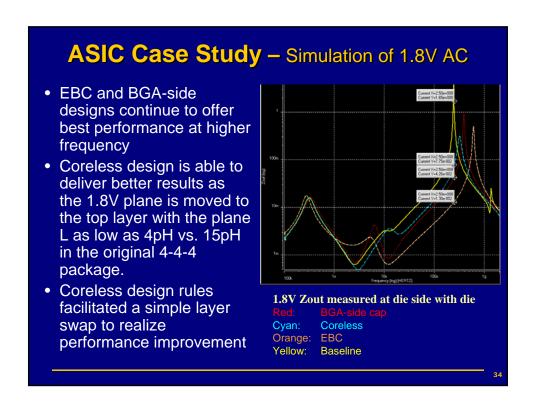

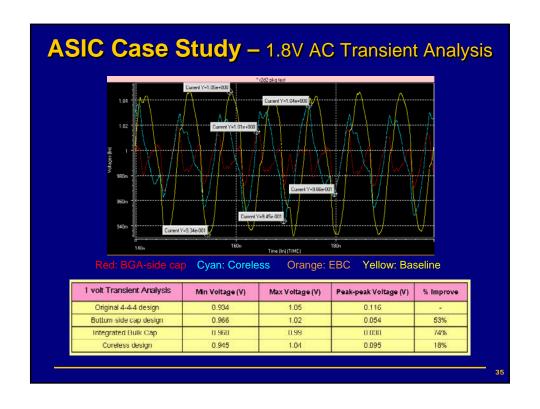

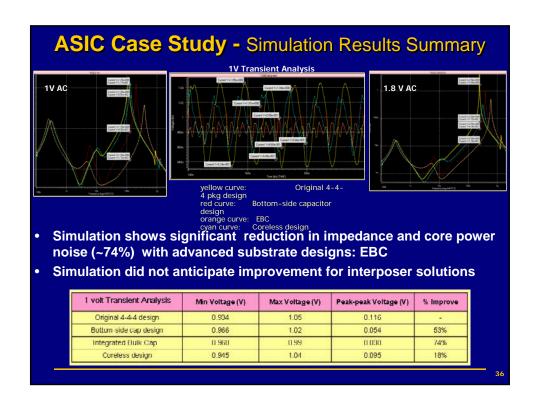

#### ASIC Case Study - Simulation of 1V AC EBC predicts lowest impedance at higher frequency BGA-side capacitor design second best Mounting L is negligible for EBC and ~4x lower for BGA side when compared to caps mounted on the top layer (~40pH/cap on the bottom vs. ~160pH/cap on the top). Coreless shows minimal 1.0V Zout measured at die side with die improvement for 1.0 volt plane because minimal Coreless change to relevant Orange: layers Yellow: Baseline

- ASIC's with advanced substrates were placed onto a functional Motherboard for system level test

- 12Gbps traffic generated with IXIA packet generator

- Measurements were made on bottom side of motherboard and at special test points through opening in lid.

37

# **ASIC Case Study – Measured Performance Results**

- · Excellent correlation with simulation results

- EBC show greatest improvement in power noise and clock jitter (54%)

- FaradFlex interposer and BGA-side caps show similar improvement (~20%)

- Deterministic jitter leading to bimodal clock is eliminated with BGA-side capacitance and FaradFlex interposer solutions

- Much more stable clock as a result of lower power noise

|                |                 | Performance               |                       |                           |                        |  |  |

|----------------|-----------------|---------------------------|-----------------------|---------------------------|------------------------|--|--|

|                |                 | Power Noise (normailized) | % Improvement (Noise) | Clock Jitter (normalized) | % Improvement (Jitter) |  |  |

| 1.0 Volt Plane | Baseline        | 1                         | N/A                   | 1.00                      | N/A                    |  |  |

|                | Interposer-FR4  | 0.82                      | 18%                   | 0.87                      | 13%                    |  |  |

|                | Interposer-Flex | 0.64                      | 36%                   | 0.76                      | 24%                    |  |  |

|                | BGA-side        | 0.69                      | 32%                   | 0.79                      | 21%                    |  |  |

|                | Int. Bulk Cap   | TBD                       | TBD                   | 0.46                      | 54%                    |  |  |

|                | Coreless        | TBD                       | TBD                   | TBD                       | TBD                    |  |  |

|                |                 |                           |                       |                           |                        |  |  |

FR4 Interposer

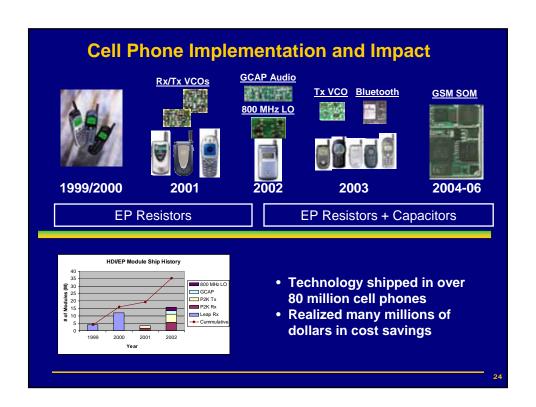

# **Conclusion and Key Takeaways**

- EP can provide value for PWB, organic and ceramic packages, MCM's and SiP by enabling cost and size reduction, and performance improvement

- EP technology and materials are available in many formats and multiple commercial vendors to accommodate various application needs

- Value of printed resistor and capacitor technology has been demonstrated in over 100M cell phone and memory module applications

- Laminate based buried capacitance materials have been used for years in server boards and other large format PCB's

now being demonstrated for ASIC and advanced packaging applications

- Buried bulk capacitance is "next best thing" to on-die decoupling offering lowest inductance and highest performance.

39

## **Future of EP – Where to Next?**

- My favorite title applies: "Embedded Passives The (For)Ever-Emerging Technology" ...unless

- More design, lay-out and modeling tools are needed to facilitate EP use.

- Engineering familiarity with the value-ads needs to grow

- Broad-based use in MCM's, SiP and advanced packaging applications will struggle until familiarity and comfort level is achieved

- As Si nodes and PI/SI margins continue to shrink, advanced packages need to bridge performance gaps

- Trade-off assessment between on-die capacitance and "next best thing". EP and other advanced packaging options become a necessity

- Space limitation on MB's will require size reduction

- Cost reduction via improved yield, part count reduction and reliability becomes a driving force

- · 2 more titles with which to conclude...

- Embedded Passives Just Shove Them Where The Sun Don't Shine

- Embedded Passives Just Do It! :)