High-Reliability

Through Silicon Via

(TSV) Solutions for

Image Sensor

Packaging

Belgacem Haba, Ph.D. TESSERA 13 January 2010

## **Outline**

- Why a Through Silicon Via (TSV)?

- Adoption and Barriers

- CMOS image sensors and TSV

- Conclusion

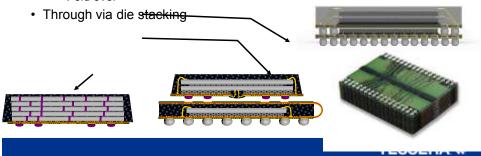

#### Third direction: Z direction

- As many die as possible in z-direction

- 3 solutions:

- Wire bondable die stacking in single package

- Package stacking (POP: package on package)

- Ball-Stack

- Fold over

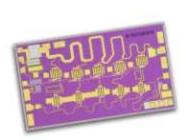

# TSV – actually an old technology Co-planar GaAs RF die always have TSVs!

Via hole grounding technology used in commercial GaAs MMICs since 1976!

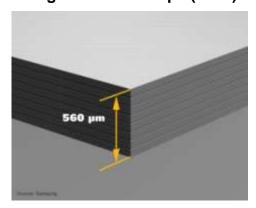

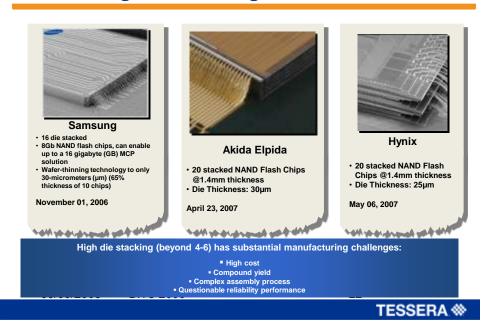

Hynix 20 stacked NAND Flash Chips @1.4mm

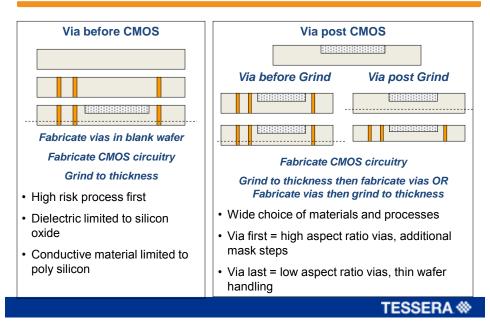

#### **TSV Process Routes**

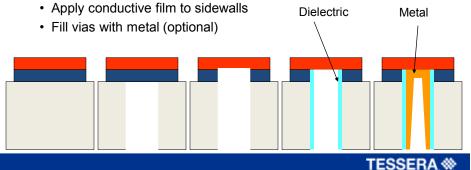

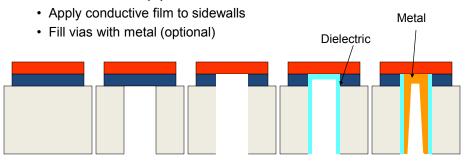

#### **TSV Process Steps**

- · Etch through thickness of silicon wafer, to oxide stop

- Etch through silicon oxide dielectric underneath bond pad, to metal stop

- Apply dielectric to sidewalls

- Form conductive pipe

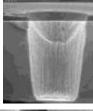

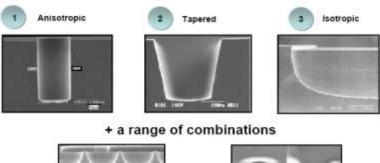

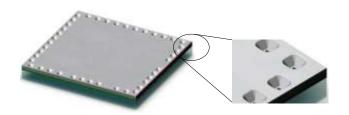

## Silicon Through-hole Formation

#### A wide variety of basic profiles

Source: Alcatel

TESSERA 🐡

#### **Plasma Etching of Silicon**

Wet chemistry has insufficient detail for this application

Plasma (dry) etching always used

- Tapered etch (SF<sub>6</sub> chemistry)

- · Anisotropic etch

- Bosch process (SF $_6$  / C $_4$ F $_8$  alternating chemistry)

- $SF_6$  etch with  $O_2$ ,  $CI_2$  and HBr sidewall passivation

## **Plasma Etching of Silicon**

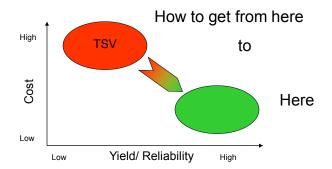

## Why a TSV ?

- When performance fails

- · When form factor is needed

- When it simplifies the structure or process

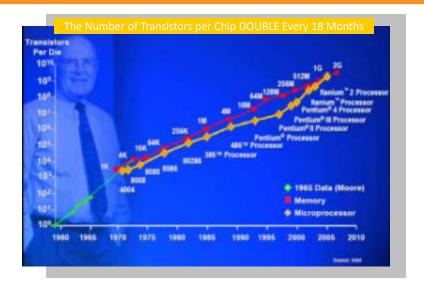

#### **Semiconductor**

#### - Moore's Law...

TESSERA 🐡

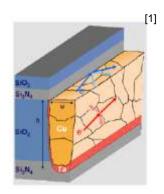

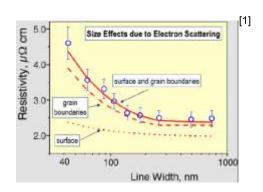

# **Scaling Conventional Wires**

More scatterings at wire surfaces and grain boundaries. Resistivity increases as cross-sectional dimensions scale.

No known technology solution to this problem [2].

- [1] W. Steinhögl, et al., Physical Rev. B, Vol. 66, 075414 (2002).

- [2] Sematech/Novellus Copper Resistivity Workshop, June 2005.

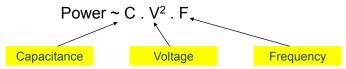

#### The Problem with Interconnects

More than 50% of electronics power is consumed by interconnects

- Interconnect length does not scale with transistor nodes

- · Complexity increases to keep chip size constant e.g. memory

TESSERA 🐡

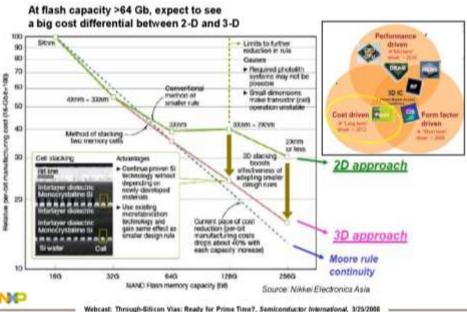

#### 3D Cost Effective way to Scale

Webcast: Through-Silicon Vias: Ready for Prime Time?, Semiconfuctor International, 3/25/2

0000

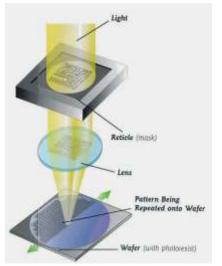

# **Optical Exposure Systems**

"Steppers and Scanners"

$$R = k \frac{\lambda}{NA}$$

TESSERA «

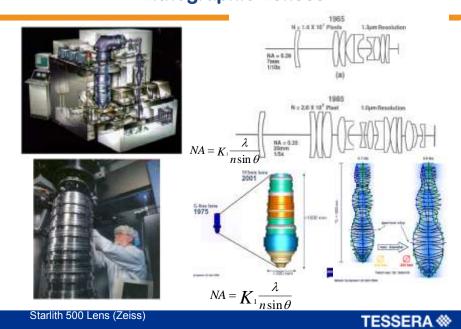

# **Lithographic Lenses**

#### **Outline**

- Why a Through Silicon Via (TSV)?

- Adoption and Barriers

- CMOS image sensors and TSV

- Conclusion

#### TESSERA «

## **Evolution of Memory**

• 5MB IBM hard drive, 1956

Jan 7<sup>th</sup> PR: SanDisk Announces the 12-Gigabyte microSDHC Card the World's Largest Capacity Card for Mobile Phones

## **Through Silicon Vias**

#### **Eight Stacked Chips (WSP)**

8-die Stack

19

TESSERA 🐡

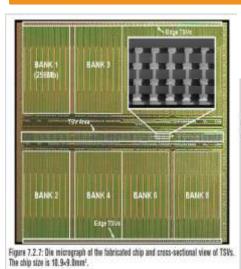

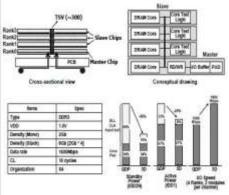

#### **Example Via Last TSS Memory Application** (Samsung ISSCC2009)

#### 8Gb DDR3 DRAM

- · 4 tiers

- 2010 ramp-up.

- · Overcomes scaling limit

TESSERA «

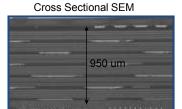

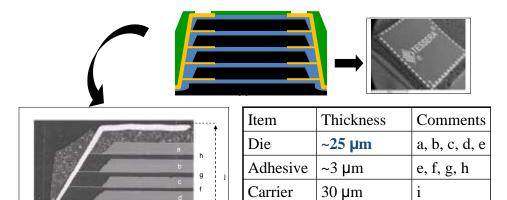

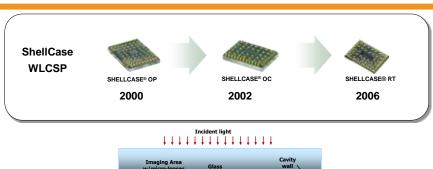

#### **SHELLCASE MVP structure**

TESSERA 🐡

## **Latest High Die Stacking Press Releases**

# **Stacking By Edge Connect**

16-die Flash Stack

16-die Flash Stack

8-die Flash Stack

TESSERA 🐡

# 24 WLS Within a Package < 1.0 mm

Micro SD Card Footprint

## **Final Product (Ready For Wire Bond)**

Total Package Thickness ~ 155 μm

TESSERA 🐡

#### **Outline**

- Why a Through Silicon Via (TSV)?

- Adoption and Barriers

- CMOS image sensors and TSV

- Conclusion

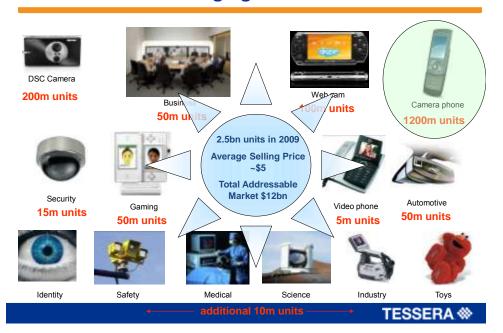

## The Potential of Imaging

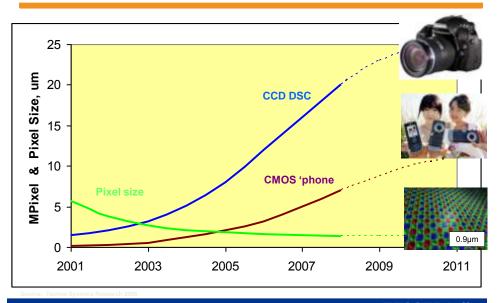

## **Image Sensor Trends**

TESSERA 🐡

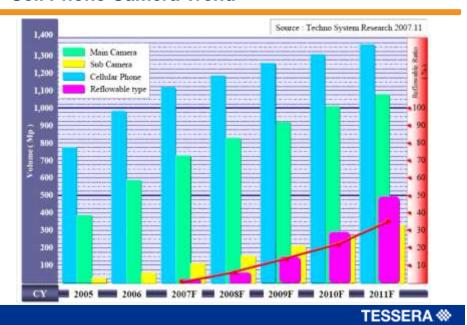

#### **Cell Phone Camera Trend**

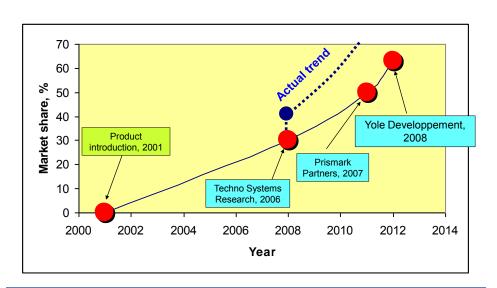

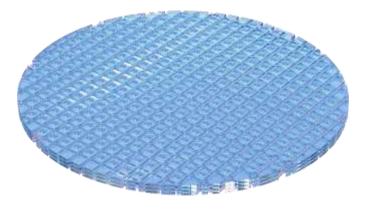

#### Market Adoption: Imager Wafer-Level Packaging (WLP)

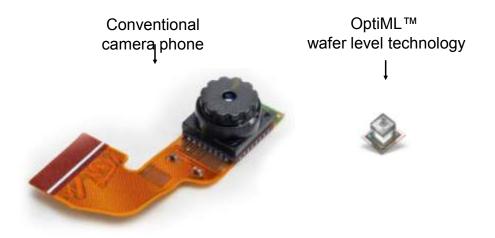

#### **Camera Module Trend**

Transition from traditional plastic lenses and barrel to reflowable camera module

TESSERA 🐡

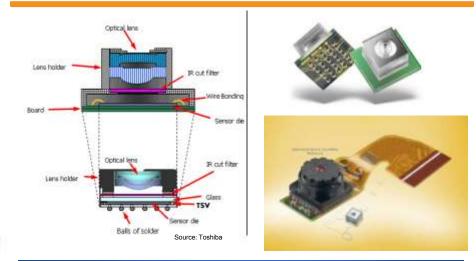

## **Image Sensor Packaging Trend**

- COB line requires Clean Room infrastructure (camera module assembly yield)

- COB requires substrate, connector, flex

- Die size shrink (more dice on wafer  $\rightarrow$  WLP cost per die is reduced)

- Industry drive for Wafer Level Camera and reflowable camera modules.

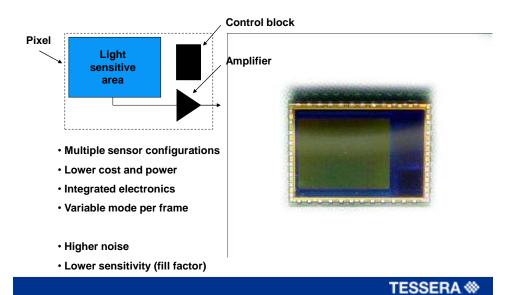

#### **CMOS Sensor**

#### **Micro Lenses**

Provide optical compensation for low fill factor of imagers, but...

- · Require air space above micro lenses

- Collect particles

- · Limit subsequent thermal excursions

# **COB Assembly Smaller pixels - More particle problems**

Lower Resolution Larger Pixels

Particle has small effect on pixel

Higher Resolution Smaller Pixels

Particle has large effect on pixel

TESSERA 🐡

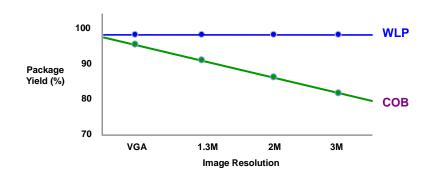

#### **COB vs WLP Module Yield**

Particle Contamination During COB Manufacturing Decreases Yield at Higher Resolution

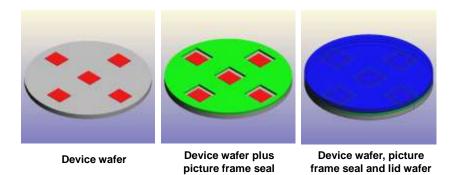

## **Wafer Level Packaging**

WLP "solves" the problem of particle contamination by applying a protective glass cover to the die, while in wafer form, as the FIRST step of the module build process.

TESSERA 🐡

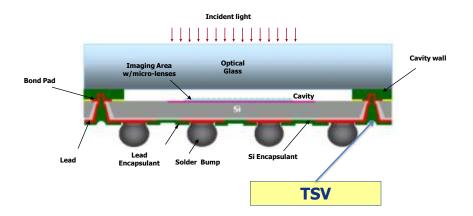

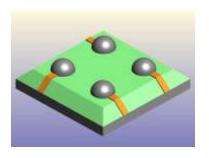

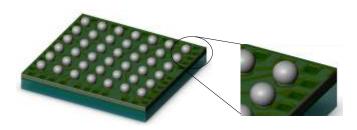

## Wafer Level Package: Ball Grid Array interconnect

- · Chip size package

- Electrical connection is through embedded leadframe and solder balls

- Entire wafer is encapsulated and then singulated

- Resulting particle-free package can then be built into a module using surface mount assembly techniques

## Wafer Level Package: Ball Grid Array interconnect

TESSERA 🐡

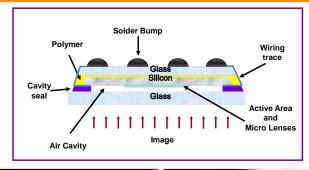

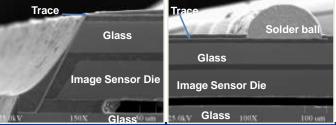

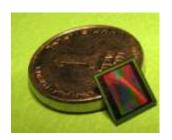

## **Image Sensor Evolution for WLP**

Imaging Area w/micro-lenses Glass Cavity wall

Cavity Si

Solder Bump Encapsulant

Lead Lead

In Future: Transition from edge connect to TSV  $\rightarrow$  WLCSP

## 2008: Introduction of TSV type WLCSP

TSV type WLP

Tessera SHELLCASE® MVP – Through Pad Interconnect

TESSERA.

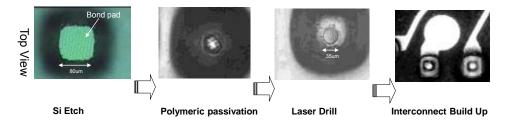

#### Typical TSV flow

- Etch through thickness of silicon wafer, to oxide stop

- Etch through silicon oxide dielectric underneath bond pad, to metal stop

- · Apply dielectric to sidewalls

- · Form conductive pipe

TESSERA «

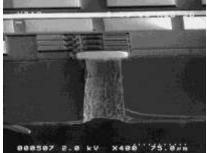

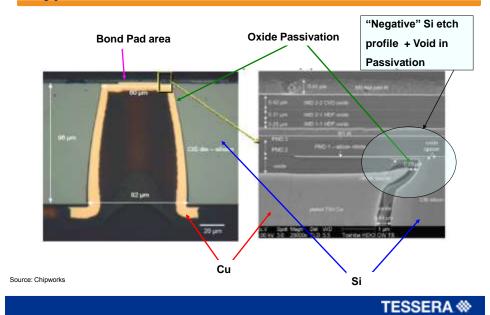

# **Typical TSV**

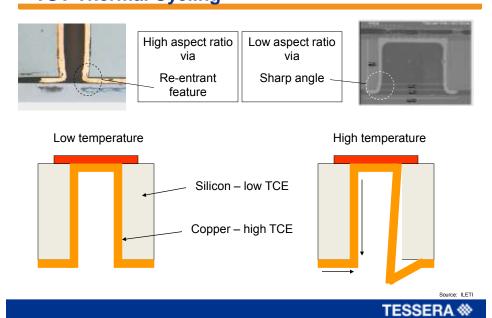

# **TSV Thermal Cycling**

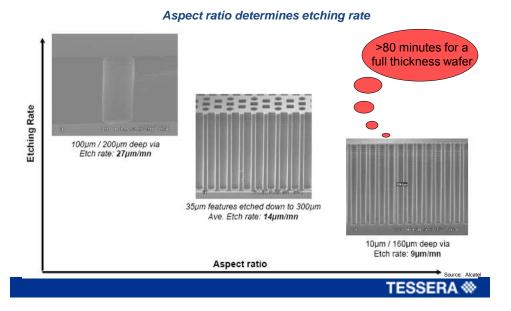

#### **Cost and Reliability Barriers**

- Semiconductor-based equipment set (expensive)

- Semiconductor-grade materials (expensive)

- Slow throughput (high capital \$ / wafer)

- Critical processes all conducted at blind end of high aspect ratio via (low yield)

- · Oxide etching

- · Ohmic contact to back side of bond pad

- · Sidewall passivation and conductive coating

- Sharp changes in section at top and bottom of via (vulnerable to fatigue during thermal cycling)

TESSERA 🐡

#### The Problem with TSV.....

# TSVs have never been widely adopted by industry

#### A New Approach to TSVs

- Low cost Si polymeric passivation

- Thicker than SiO2 (few microns instead of less than micron).

- · Passivation uniformity

- No need for very expensive tools (of the shelf coater instead of LPCVD/ PECVD).

- Make TSV structure using PCB tools

- · Laser Drill through Polymer and bond pad

- · High throughput and low cost per drilled Via

- · Of the shelf Laser tool

- Low Cost Lead Metalization

- · No need for Via fill process

- Proven Supply Chain

- · Rely on HVM proven material/ tools

TESSERA «

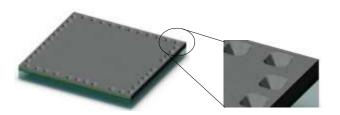

#### **SHELLCASE MVP structure**

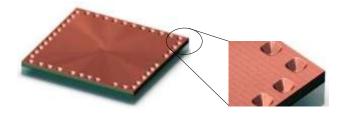

## **SHELLCASE MVP flow – cont.**

Apply PR Via mask

Etch tapered holes through silicon

Source: Tessera

TESSERA 🐡

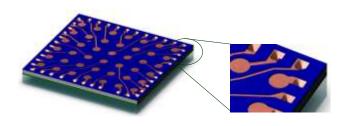

## **SHELLCASE MVP flow – cont.**

Apply polymeric passivation

Laser ablate small via through Si polymeric passivation, oxide and bond pad

Source: Tessera

## **SHELLCASE MVP flow – cont.**

Coat with metal

Pattern metal

Source: Tessera

TESSERA 🐡

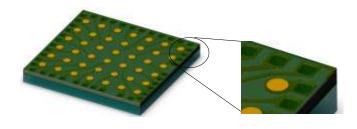

## **SHELLCASE MVP flow - cont.**

Apply and pattern solder mask

Apply solder to form BGA interface

Source: Tessera

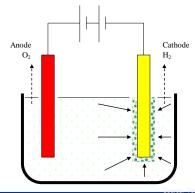

## **Electrophoretic Paint**

Electrophoretic painting is an immersion painting process in which charged paint particles are attracted to an oppositely charged metallic surface. Deposition ceases when the coating forms a dielectric layer.

TESSERA 🐡

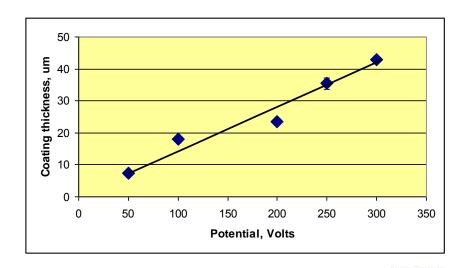

## Self-limiting coating thickness Vs applied potential

# **SHELLCASE MVP- process details**

Source: Tessera

TESSERA 🐡

# **SHELLCASE MVP - Reliability Results**

| Test                                                   | Test Conditions                                                                 | Standard       | Duration    | Results |

|--------------------------------------------------------|---------------------------------------------------------------------------------|----------------|-------------|---------|

| Automotive specification                               |                                                                                 |                |             |         |

| Moisture soak (pre-<br>conditioning)<br>Level 1 – MSL1 | • 125°C / 24hrs<br>• 85°C/85% RH/ 168 hrs<br>• Reflow (peak 265°C) /<br>3 times | JESD22-A113-D  | 1 sequence  | Pass    |

| Steady state<br>temperature<br>humidity - TH           | • 85°C/85% RH                                                                   | JESD22-A101-B  | 2000 hrs    | Pass    |

| High temperature<br>storage life<br>HTS                | • 150°C                                                                         | JESD22- A103-A | 2000 hrs    | Pass    |

| Temperature Cycling - TMCL                             | • -40°/+125°<br>• 32 cycles/ day                                                | JESD22-A104-B  | 2000 cycles | Pass    |

## **SHELLCASE MVP – Module Level Reliability**

| Test                             | Test Conditions                                                      | Standard                   | Duration                | Results                      |

|----------------------------------|----------------------------------------------------------------------|----------------------------|-------------------------|------------------------------|

| Low Temperature<br>Operation     | • -20°C                                                              | Cell Phone Maker<br>#M/ #N | 96 hrs -<br>operational | Pass: Optical and functional |

| High Temperature<br>Operation    | • 80°C                                                               | Cell Phone Maker<br>#M/ #N | 96 hrs -<br>operational | Pass: Optical and functional |

| Thermal Shock                    | • +80°C, 30min<br>• - 20°C, 30min                                    | Cell Phone Maker<br>#M/ #N | 35 Cycles               | Pass: Optical and functional |

| High Temperature<br>and Humidity | • 80°/95%RH                                                          | Cell Phone Maker<br>#M/ #N | 96 hrs -<br>operational | Pass: Optical and functional |

| Vibration Test                   | • 20-2000 Hz<br>• 0-8gr<br>• 3 axis, 15 min per plane<br>•Load 100gr | Cell Phone Maker<br>#M/ #N | 1 Cycle                 | Pass: Optical and functional |

| ESD                              | • +/- 0.5KV, 1KV, 2KV                                                | Cell Phone Maker<br>#M/ #N | 1 Cycle                 | Pass: Optical and functional |

TESSERA ₩

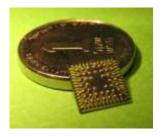

# SHELLCASE MVP: WLCP for CMOS Image Sensors

- Low cost, high yield, wafer level package

- Exceptional reliability meet MSL 1 and exceeds automotive specifications

- Micro Via Pad interconnect true TSV technology

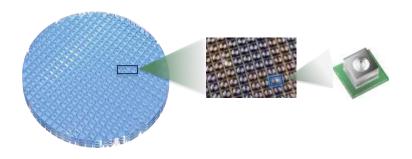

## **Wafer Level Camera: Process Overview**

Step R: Wafers of dearling mean a fact have ded

TESSERA 🐡

### **Wafer Level Camera: Process Overview**

Step C: Wafers singulated into individual optical elements

# **Wafer Level Camera: Process Overview**

Step D: Assembly optical elements on image sensors

TESSERA 🐡

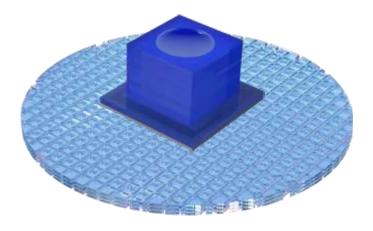

## **OptiML WLC Technology**

## **Revolutionizing the Camera Module**

TESSERA

#### **Conclusions**

- Packaging of image sensors at the wafer level

- · Cost-effective solution

- Eliminates multiple camera module elements

- · Allows reflowable camera module

- Low adoption rate of TSVs

- · High cost

- · Low yield

- Low reliability

- Leveraging PCB industry materials and tool set greatly decreases the cost of making TSVs

- SHELLCASE MVP is the TSV solution for WLP of Image Sensors

- · Low cost

- Reliable