IEEE Components, Packaging, and Manufacturing Technology Chapter, Santa Clara Valley

# 3D IC Development and Key Role of Supply Chain Collaboration

Suresh Ramalingam Xilinx Inc.

IEEE CPMT, April 28, 2011

Background and Motivation

#### Stacked Silicon Interconnect Technology

### Supply Chain Collaboration

© Copyright 2010 Xilinx

## **Background and Motivation**

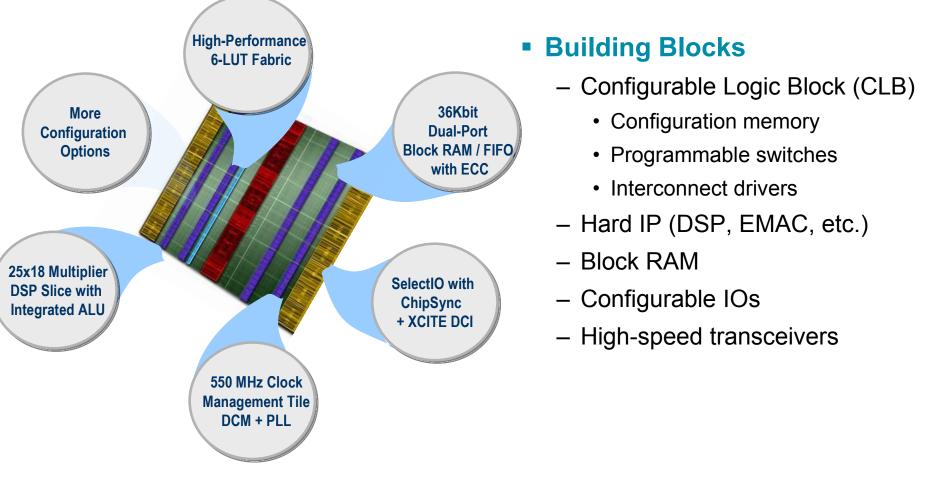

## **Background: FPGA**

#### **Programmable SoC of logic, memory, and analog circuits**

## **Customers Are Asking for More**

- <u>More</u> than 2X today's logic capacity...

- Many <u>more</u> high-speed serial transceivers...

- Many <u>more</u> processing elements...

- Much <u>more</u> internal memory to store data...

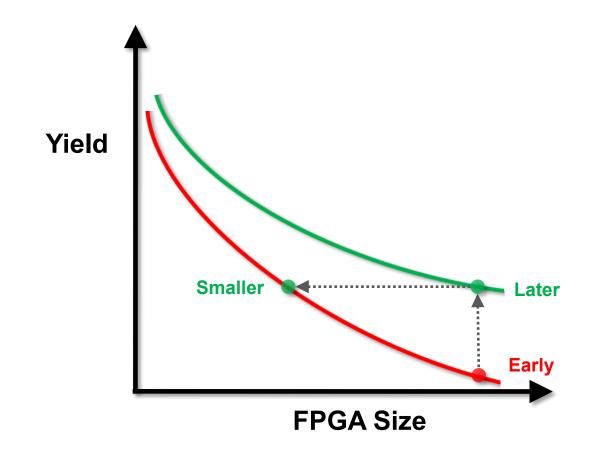

## Challenge 1: Availability and Capability Largest FPGAs only viable later in the life cycle

# **Challenge 2: Power and Bandwidth**

Traditional mitigation techniques are no longer adequate

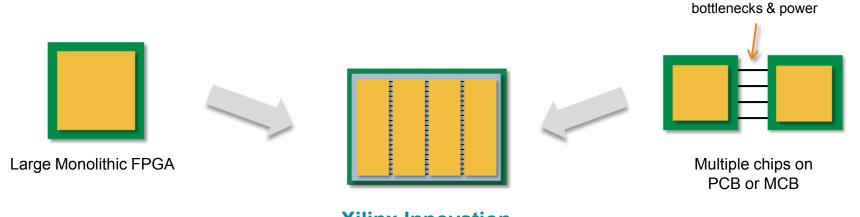

Large Monolithic FPGA

Multiple FPGAs on PCB or MCM

#### Chip-to-Chip via Standard I/Os and SerDes

More total gates, sooner, but...

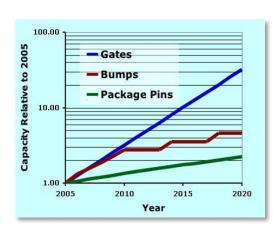

#### **Resources Not Scaling**

- 1. Not enough I/Os

- 2. I/O latencies too high

- 3. Wasted I/O power

## Introducing Stacked Silicon Interconnect Technology High Bandwidth, Low Latency, Low Power

Xilinx Innovation

Massive number of low latency, die-to-die connections

- Earlier in time

- No wasted I/O power

- Over five years of R&D

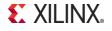

Delivers the Best of Both Worlds: High and Usable Capacity

I/O performance

## **Delivers Resource-Rich FPGAs**

# For the Most Demanding FPGA Applications

Next Gen Wired Communications

Next Gen Wireless Communications

High Performance Computing VIRTEX.<sup>7</sup>

Industry's Highest System Performance and Capacity

Aerospace & Defense

### Summary

#### SSIT Addresses IO Bottleneck

100X better BW/W over traditional IOs/SerDes

### Can offer Next Generation Density Now

### SSIT Platform Enables

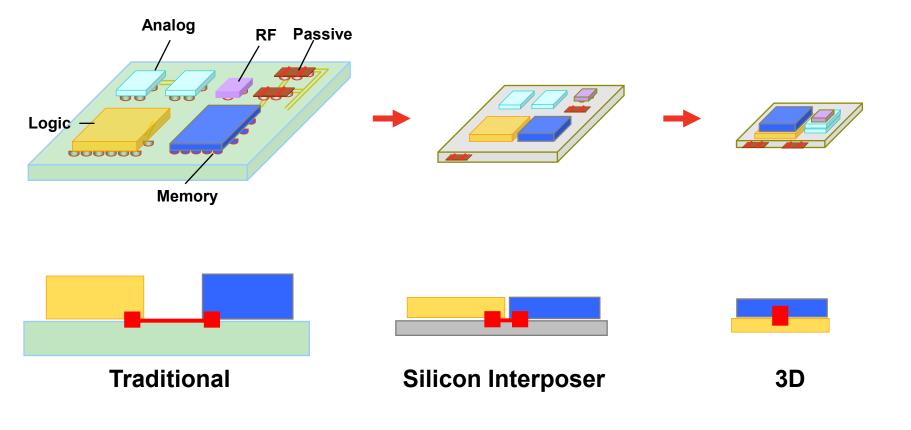

- Optimal Partitioning

- Digital and analog blocks

- IP/IC reuse

- Heterogeneous Integration

- Digital, mixed signal, & optical

- FPGA & memory

### **Stacked Silicon Interconnect Technology**

Technology Overview

#### Supply Chain Collaboration

#### Summary

# Xilinx FPGA Architectural Innovations At the Heart of the Technology

FPGA Slices Side-by-Side Silicon Interposer

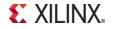

## Harnesses Proven Technology in a Unique Way

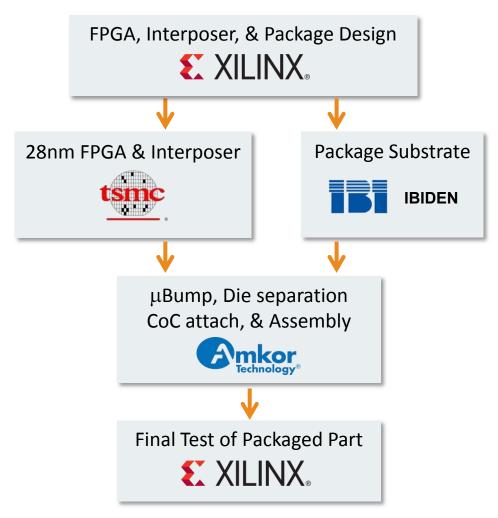

### Virtex-7 SSIT uses 28 nm FPGA and 65 nm Interposer

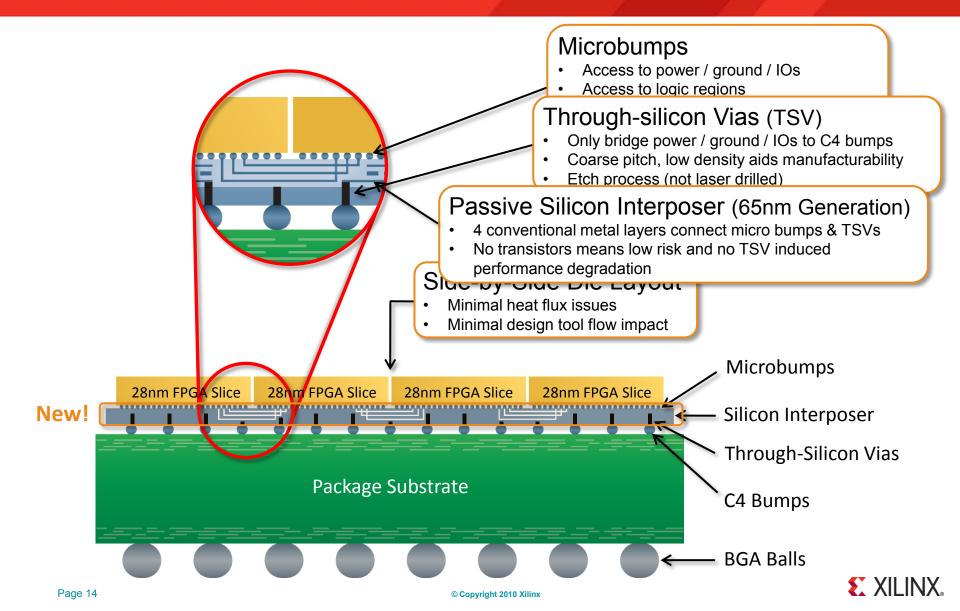

#### 28nm Test Vehicle + 65 nm Interposer

| Technology | Specs                            |

|------------|----------------------------------|

| M1-M4      | 2um pitch 4 4X layers            |

| TSV        | >10 um diameter & 210um pitch    |

| Micro-bump | 45um pitch                       |

| C4         | 210um pitch                      |

| Package    | 4-2-4 Layer, 1.0 mm<br>BGA pitch |

Courtesy of Xilinx, TSMC, Amkor

- Low risk approach to integrate TSV & u-bump

- Passive silicon interposer with 65nm interconnects & coarse-pitch TSV

- High density micro-bump for 10K-30K chip-to-chip connections

- Better FPGA low-k stress management with silicon interposer

Page 15

© Copyright 2010 Xilinx

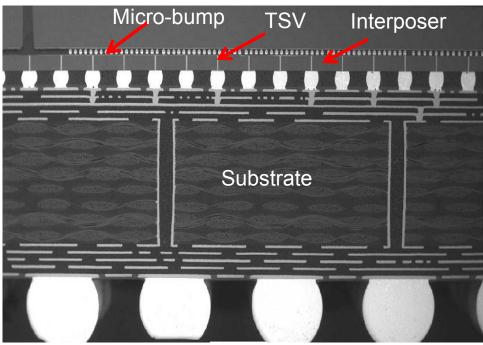

## **Correlation between Measurement and Simulation**

#### Through transmission structure using two TSVs

Dotted Red Trace – Measurement Solid Blue Trace - Simulation

© Copyright 2010 Xilinx

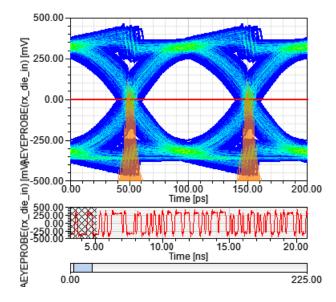

# **Eyes After TSV Optimization**

#### w/o Interposer

500.00

Line [ns] 250.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00

10Gbps

13Gbps

# **Reliability Validation Status**

| Reliability Tests                                                       | Focus Areas                                    | Results                      |

|-------------------------------------------------------------------------|------------------------------------------------|------------------------------|

| Package Level L4 Precon and TCB                                         | TSV and C4                                     | Passed 1000 TCB              |

| Wafer Level TCB                                                         | TSV& Interposer<br>Interconnects               | Passed 1000 TCB              |

| Electro-migration                                                       | Micro-bump Joint                               | Passed 0.1% CDF for 10 years |

| High Temperature Storage                                                | Micro-bump Joint                               | Passed 1000 hours            |

| Package Level L4 Precon and TCB – 1 <sup>st</sup> Leg                   | Micro-bump Joint, TSV,<br>C4 Interconnects     | Passed L4 and 500 TCB (CSAM) |

| Package Level L4 Precon and TCB – 2 <sup>st</sup> Leg                   | Micro-bump Joint, TSV,<br>C4 Interconnects     | In progress                  |

| Package Technology<br>Qualification<br>- L4 Precon, TCB, THB, HTOL, HTS | Micro-bump Joint, TSV,<br>C4, Silicon, Package | In planning                  |

## Underfill

#### **Initial Underfill**

#### HAST 48 Hours

Courtesy of Xilinx, TSMC, Amkor

#### MRT L5/250

#### **HAST 264 Hours**

### No Delamination, Post HAST: 110C, 85% RH, 264 Hours

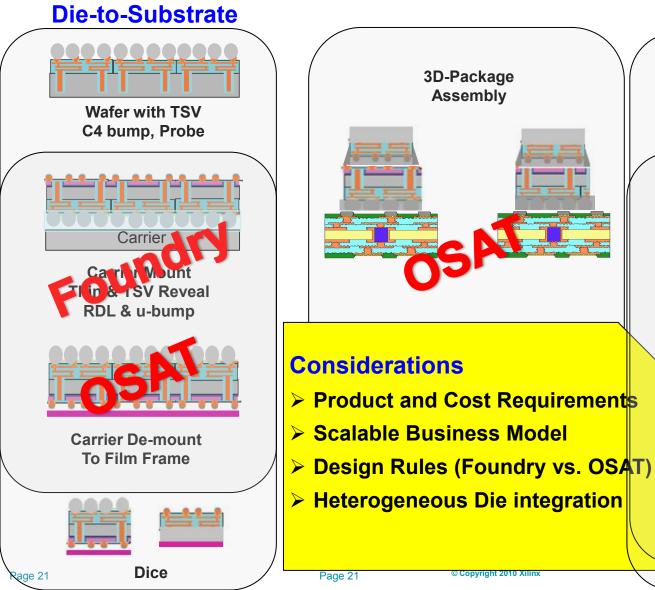

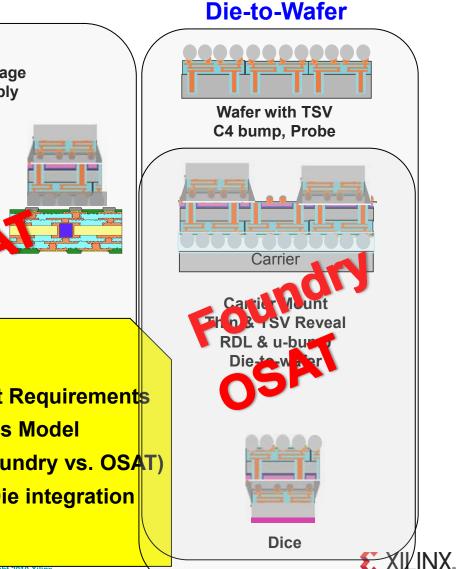

# **Establishing a Supply Chain Flow**

# Benefits from Collaboration with Other Technology Leaders

- Leading fabless & fablite companies

- Equipment manufacturers

- Fabs and OSAT

- Industry consortia

- Requirements alignment

- Industry standards setting

- Best practice sharing

## Xilinx has a Robust Supply Chain

#### Leading foundry and OSAT partners

© Copyright 2010 Xilinx

### **TSMC Discusses Stacked Silicon Interconnect**

# Dr. Shang-Yi Chiang

Senior Vice President, R&D, TSMC

# **System Migration Trend**

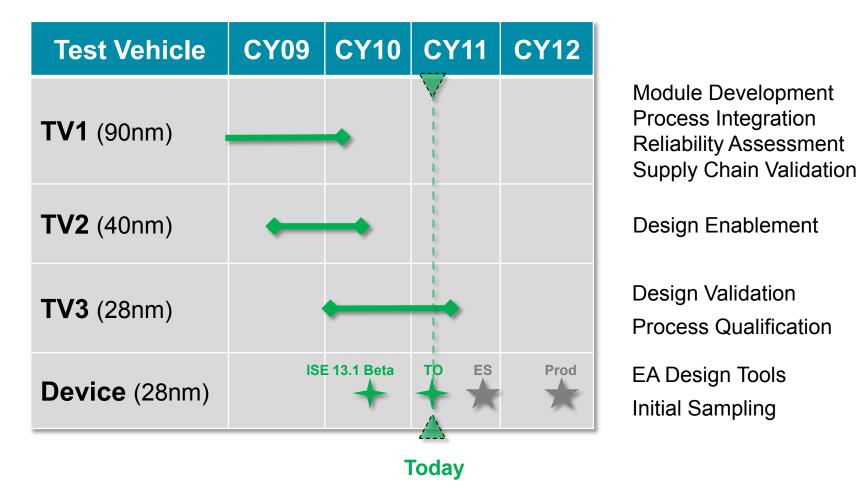

## **Xilinx Is Well on the Way to Volume Production**

### Summary

Xilinx leads industry with <u>Stacked Silicon Interconnect</u> technology delivering breakthrough capacity, bandwidth and power efficiency

#### Stacked Silicon Interconnect Technology

- 2X FPGA capacity advantage at each process node

- Core part of Virtex-7 family

- Supported by standard design flows