## Developments in low-temperature metal-based packaging

2011. 12.14

Jiyoung Chang and Liwei Lin

Ph.D. Candidate, Department of Mechanical Engineering

University of California at Berkeley

### Contents

- Project & Research goals

- Low temperature metal packaging

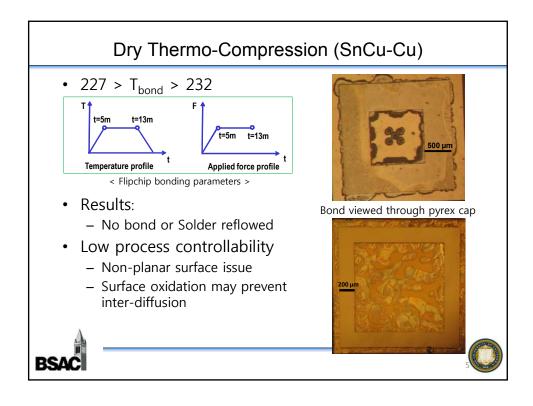

- Dry thermocompression

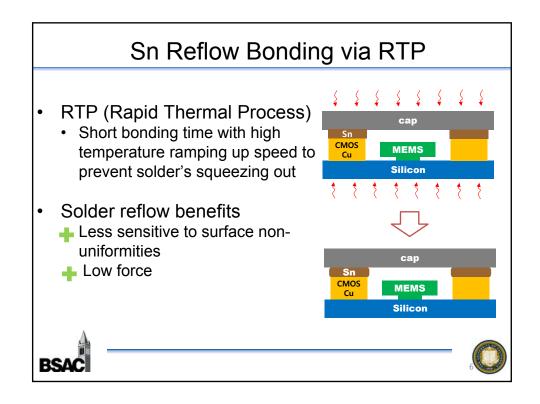

- Rapid Thermal process

- Solder pre-reflow

- Insertion of thin metal layer

- Summary

### Research goals

## Center for Micro/Nano Scaling Induced Physics (MiNaSIP) in U.C.Berkeley

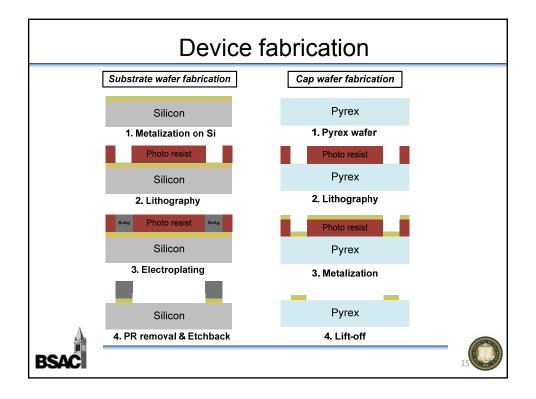

- Subgroup research with Freescale™ semiconductor

- Flux-less bonding

- Short bonding time & Low bonding temp.

- Sub-100μm width bonding ring

- → Photolithography definable & Electroplating

- Hermetic sealing

- → Low permeability required

- CMOS compatible process

# Material selection • Material Selection Criteria — Temperature — Deposition & bonding method — Permeability — Mechanical properties \*Glass Frit : Popular in MEMS packaging Min Nr Day Mo Vr 10 1000 — Deposition : Screen-printing (min.w≈150μm) — Temperature : 450 °C — Time :15-30 minutes — Metal bonding BSAC Material selection Permeability (g/cm+tory) Silicon Permeability (g/cm+tory) Function 10-0 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-10 10-

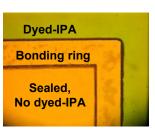

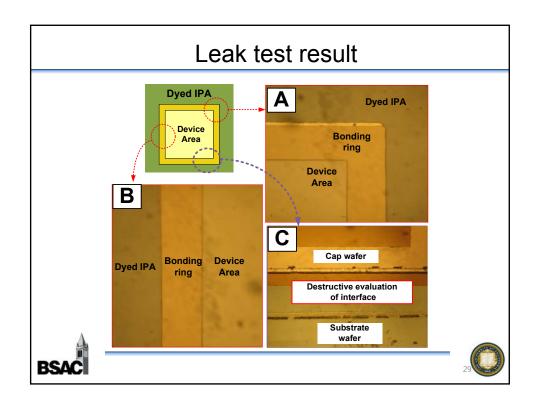

### Leak & Autoclave Test

- Dyed-IPA leak test

- Gross-leak detection

- Small surface tension of IPA allows quick permeation through voids

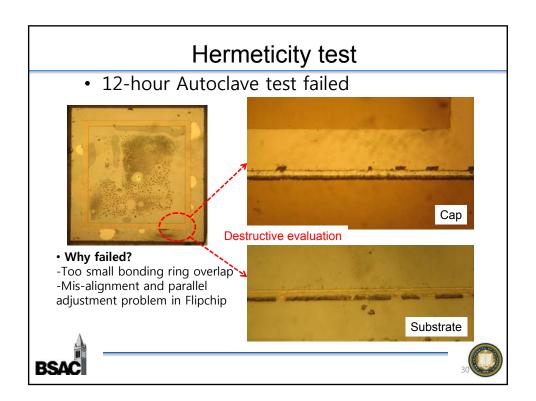

12-hour Autoclave test failed: 125°C & 24psi

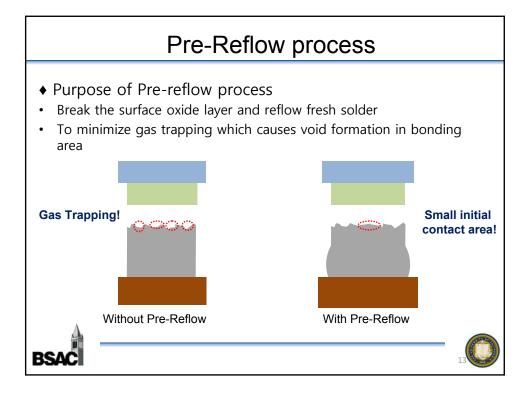

### Why hermetic test failed??

- Formation of leakage pass-through due to...

- Void formation

- Gas trapping during bonding process

- Metal oxide on surface prevents reflow of solder

- Non-uniform bonding along the bonding ring

- Lack of uniform pressure applied during bonding

- → Pre-reflow process approach

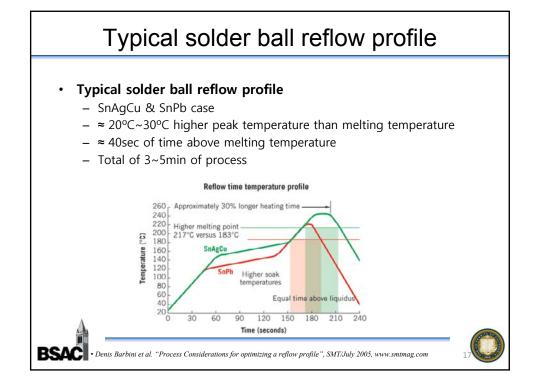

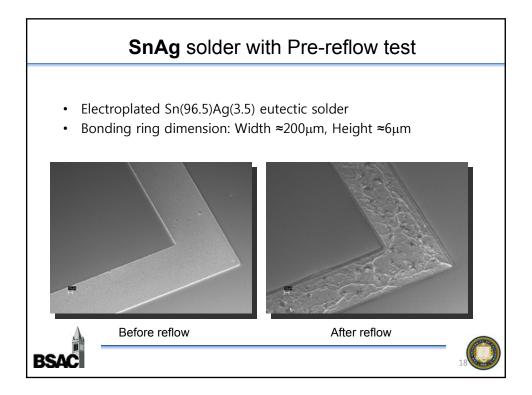

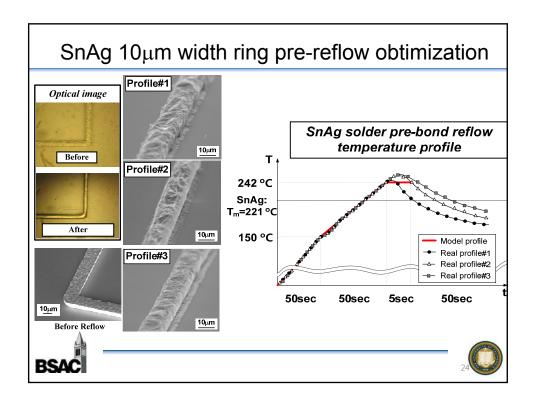

### Pre-reflow profile optimization

- Process parameters in typical solder ball reflow process

- Temperature gradient in preheat zone

- Soak temperature and time when using Flux

- Temperature gradient from soak to maximum temperature

- Maximum peak temperature

- Cooling gradient in cooling zone

- Total heating time

- Current solder reflow profile is optimized for solder ball to form sphere shape not for square line form solder

- → Reflow profile needs to be modified for line shape bonding

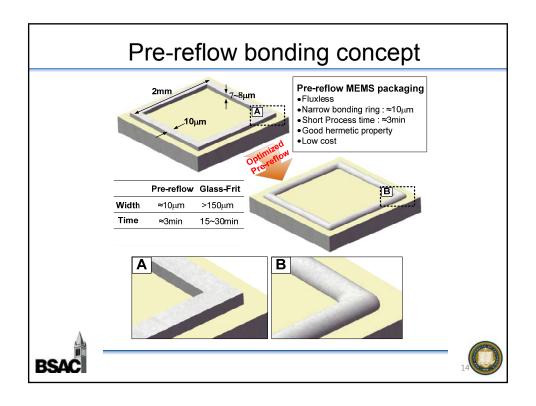

### Low Width to Height ratio bonding ring

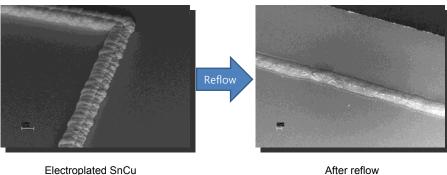

- Electroplated 10μm and 20μm width bonding ring

- Width to Height ratio 1.5:1~2:1

Electroplated SnAg with 10µm width bonding ring

Electroplated SnCu with 20µm width bonding ring

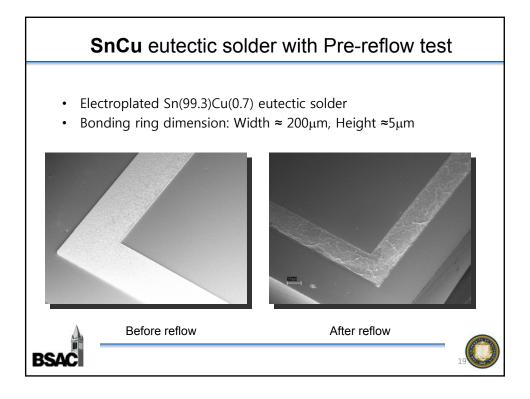

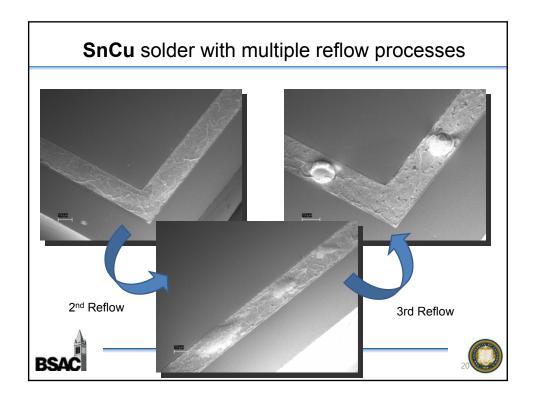

### SnCu reflow test results

- Reflow profile modification

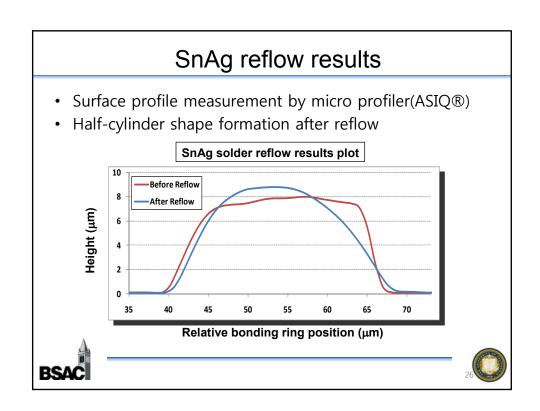

- Formed half-cylinder after reflow

- Partially non-uniform clogging surfaces observed

After reflow

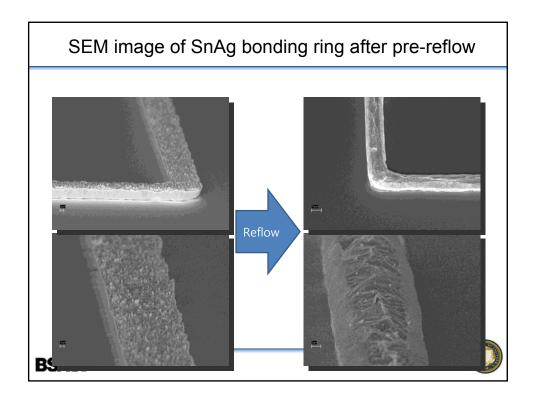

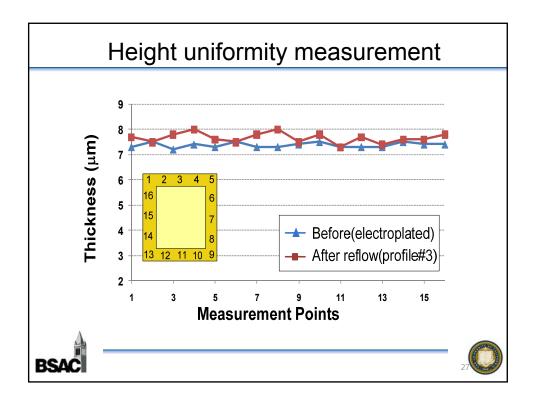

## SnAg 10µm width ring pre-reflow results • Reflow profile optimized in RTP • Uniform half-cylinder shape achieved • No clogging or solder gathering was observed Reflow Reflow After optimized reflow BSAC After optimized reflow

### Summary

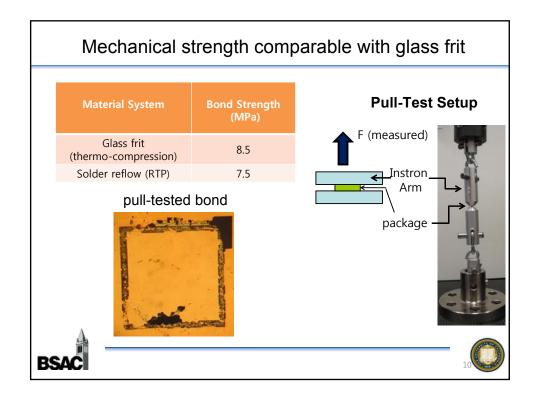

- Proof-of-Concept: Metal bonding for possible replacement of glass-frit

- CMOS-integrated process

- Compatible mechanical strength with glass-frit

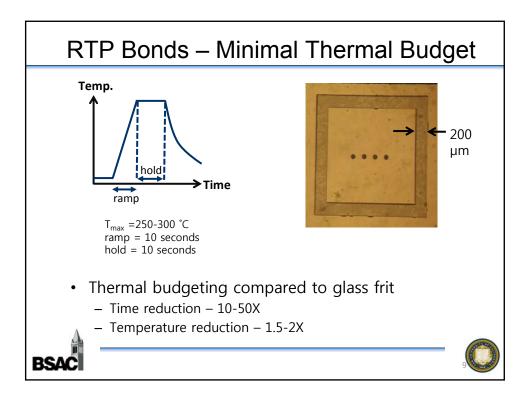

- Rapid Thermal bonding result(no pre-reflow)

- $-\,$  Successful leak-test for 200  $\mu m$  bonding ring

- Failed 12hr hermetic test

- Solder reflow profile optimization for sub-100μm metal bonding solution

- Reflow profile optimization for 10mm SnAg boding ring

- Uniform half-cylinder shape reflow results

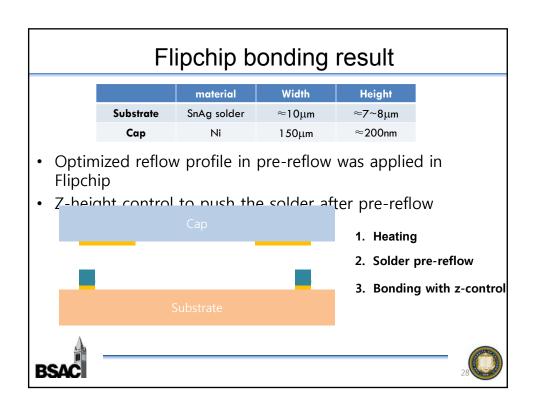

- Solder pre-reflow bonding of SnAg 10μm bonding ring using Flipchip

- Optimized reflow profile used for bonding

- Possibility of sub-100μm bonding ring in MEMS packaging

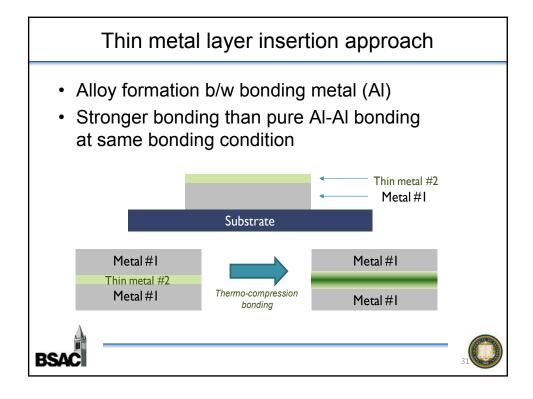

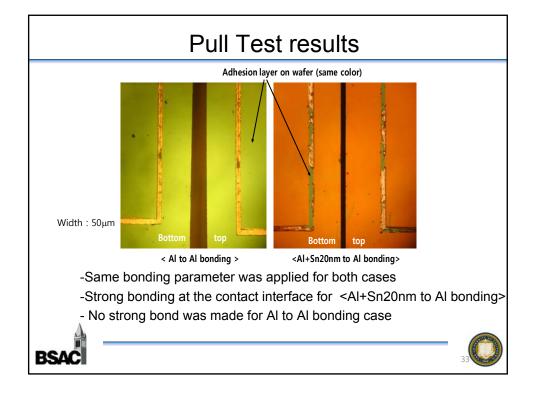

- · Metal insertion approach

- Al-Sn-Al approach showed better bonding quality than pure Al-Al bonding

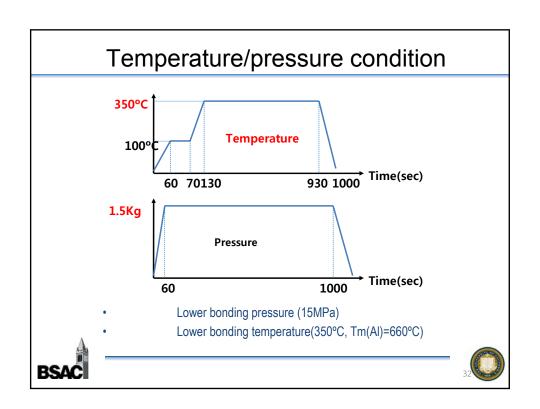

- Lower temperature and pressure

### Acknowledgement

- IEEE-CPMT

- Prof. Liwei Lin

- · Mr. Kedar Shah

- Sponsor

- Freescale™ semiconductor *≸freescale*

– DARPA (MR)

Thank you!!