Manufacturing Technology Society, SCV Chapter

# **Topics**

- Advanced Substrate Technologies

- Interposers & Role

- Embedded Die Solutions

- Package-on-Package

- Migration to System Level Integration

RELIABILITY TRUST

or Controlled Release at the IEEE/CPMT Technical Meeting

Oct-13, C. Zwenger

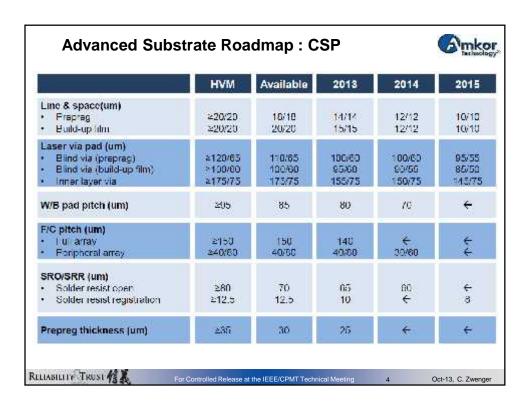

|                                           | HVM     | Available | 2013   | 2014     | 2015     |

|-------------------------------------------|---------|-----------|--------|----------|----------|

| Line & space (um)                         | 15/15   | 14/14     | 9/12   | <b>←</b> | 8/8      |

| Via / via pad (um)  Blind via             | 100/65  | 100/65    | 90/65  | 90/65    | 90/60    |

| Inner layer via                           | 250/100 | 180/80    | 155/75 | 150/75   | 145/75   |

| SRO/SRR (um)                              |         |           |        |          |          |

| <ul> <li>Solder resist opening</li> </ul> | 85      | 80        | 75     | 70       | 65       |

| Solder resist registration                | 15      | 15        | 12.5   | 10       | 8        |

| SOP pitch                                 | 150     | 150       | 140    | 130      | 125      |

| fpfc pitch                                |         |           | 40/80  | 30/60    | <b>←</b> |

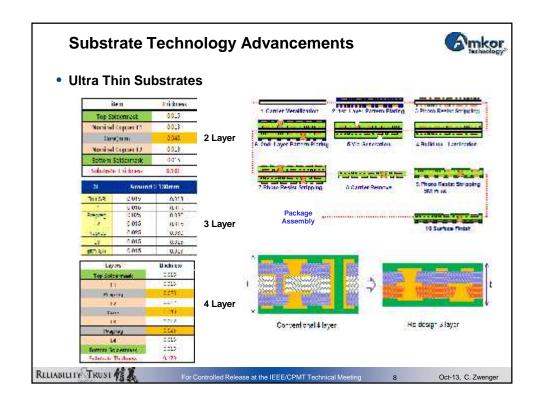

|                                          | HVM                                           | Available                 | 2013                               | 2014              | 2015             |

|------------------------------------------|-----------------------------------------------|---------------------------|------------------------------------|-------------------|------------------|

|                                          | HVIVI                                         | Available                 | 2013                               | 2014              | 2015             |

| Core thickness                           | 800, 400<br>Cored                             | 800, 400<br>Coreless      | 250<br>Coreless                    | 200<br>Coreless   | <200<br>Coreless |

| Core material                            | E679FGR<br>E700GR                             | E705G<br>R1515A<br>R1515W | E705GLH<br>HL832NSF-<br>LCA        | <b>←</b>          | 1~2 ppm<br>Core  |

| Build-up material                        | GX-13                                         | GX-92<br>GX-T31<br>GZ-41  | GX-A01<br>GY-11<br>NX-04H<br>NQ-05 | <b>←</b>          | <b>←</b>         |

| Solder mask material<br>(* film type SR) | AUS 703                                       | SR7200G<br>AUS 410*       | SR7300G<br>AUS SR-1*               | AUS G-2<br>SR7400 | <b>←</b>         |

| Surface finish FCBGA                     | ENIG (w/<br>SOP)<br>IT (w/SOP)<br>OSP (w/SOP) | <b>←</b>                  | <b>←</b>                           | +                 | <b>←</b>         |

| • fpfcBGA                                |                                               |                           | ENEPIG,<br>EPIG, OSP               | <b>←</b>          | <b>←</b>         |

# **M**mkor Low Dk / Df Dielectric Materials Dielectric material needs for future high frequency devices Need for materials with Dk < 4.0 (dielectric constant)</li> Need for materials with Df < 0.01 ~ preferably 0.005 (dissipation factor)</li> - CTE will play a larger role for the embedded die products 0.604 OUTCOME NO 6.2720 15.1329(CA) Dislactric Consumt [-HLESSNER C. CT 14,075(1.0) HL0726.34 D 16 Progressor (Sha) 5 13 Fracuenty (G-Kg) RILIABILITY TRUST For Controlled Release at the IEEE/CPMT Technical Meeting Oct-13, C. Zwenger

### **Advanced Substrates**

- Coreless

- Today = Coreless

- Qualified 45mm body and 15 x 20mm die

- Provides better electrical performance

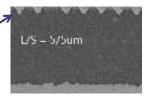

# • Future Generation Design Rules

- Lab level

- 5/5 line-space; 18/30 via-pad

- proprietary processing; new materials

- Lab level +

- 3/3 line-space; 10/22 via-pad

- wafer based equipment for panels; thin film materials

### **Next Generation Substrates**

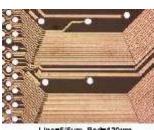

### Laser Embedded Signals & Pads

- Is it time?

- Proven on multiple formats

- Proven with multiple materials

- Advanced substrate manufacturer has capability / capacity today

Line=5/5um, Ped=120um

RILIABILITY TRUST

For Controlled Release at the IEEE/CPMT Technical Meetin

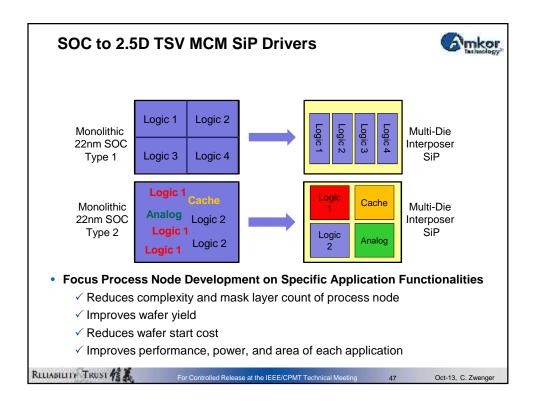

# Interposers & Role: Overview

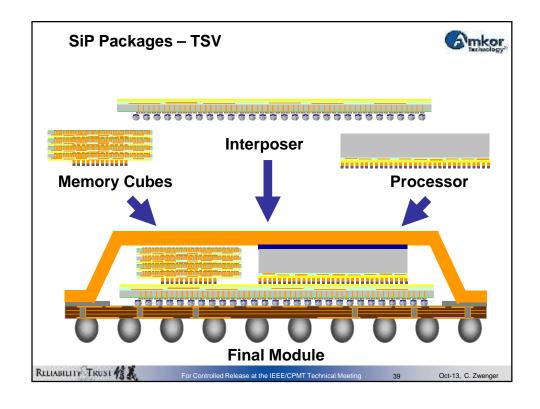

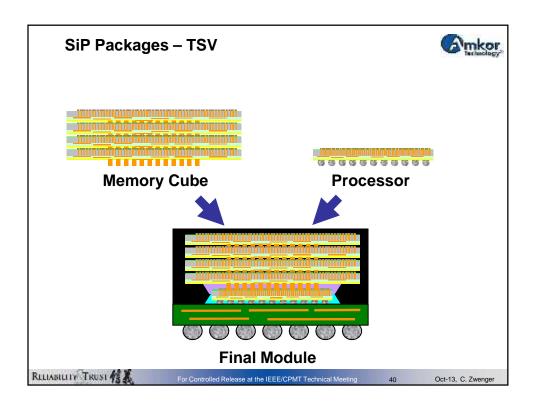

### Advanced MCM SiP Packages

- Need method to integrate advanced node die on same package platform

- Die must be integrated in close proximity; need high bandwidth and low power

- Deconstructed advanced node logic & high end memory driving integration

### Markets

- High End FPGA, ASIC, SERDES

- Mid End CPU, GPU, APU, High end Memory

- Low End Mobile

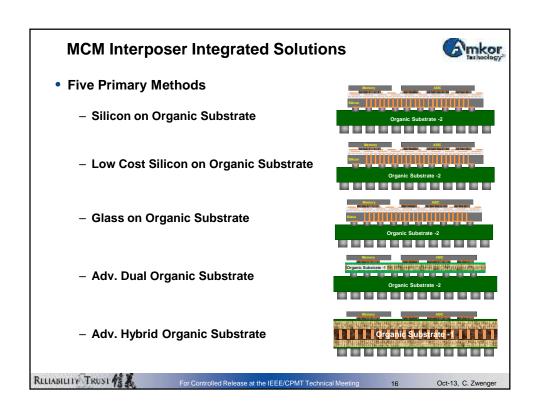

# Interposer Options

- Silicon interposer

- high end, mid end, low end

- Glass interposer

- unavailable today; could be solution for all markets in the future

- Organic interposer

- mid end, low end

For Controlled Release at the IEEE/CPMT Technical Meeting

12

ct-13, C. Zwenge

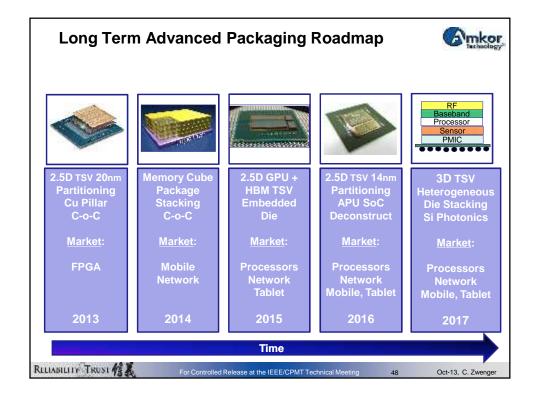

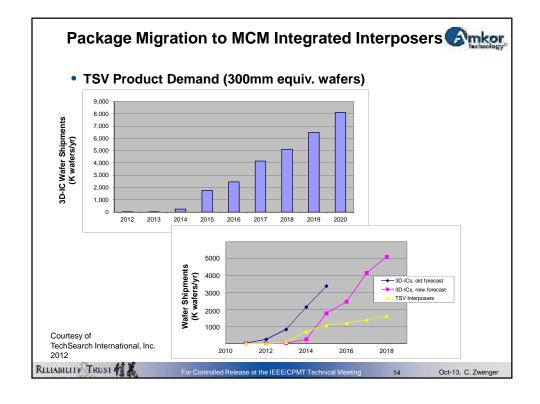

# **MCM Integrated Interposer Market**

### • Product Applications

Gaming, HD-TV, mobile, tablets, computing, servers – very broad

High end graphics cards will be initial focus with HBM memory integration

Mobile space will follow based upon availability of lower cost interposer solutions

### Market Longevity

Expect very long life cycle; production already started

Long term continued use through deconstruction of very high end node logic to address system level cost and power

### Demand Forecast

Continued low volumes with FPGAs and ASICS

Moderate volumes for high end graphics cards; HBM cost / availability driven

High volumes for mobile; interposer cost driven at \$0.01 per sq.mm

RILIABILITY TRUST

For Controlled Release at the IEEE/CPMT Technical Meeting

Oct-13, C. Zwenge

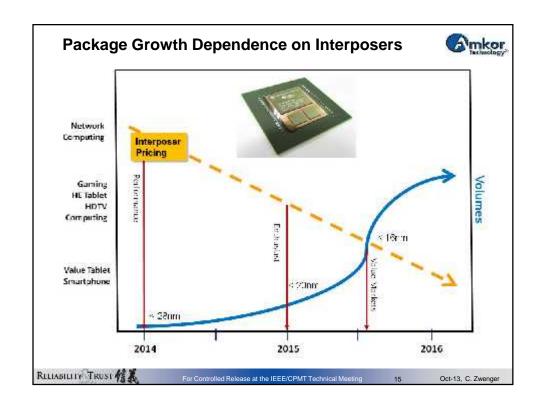

# **Integrated Interposer Summary**

### General Market Looking Forward

Expect very long life cycle; production already started at high end Long term continued use through deconstruction of very high end node SoC logic to address system level cost and power

## • Interposer Options / Sources

- High End silicon will dominate

- Mid End silicon to be prominent; organic may play role

- Low End organic??; need technology and large sourcing supply

### Other Factors

- Pricing pressure; will continue to stress Tier-1 foundries

Need Tier-2 silicon supply chain without ties to bundling

- Silicon; industry growth will necessitate more worldwide capacity than currently available

- Organic may be ultimate long term answer

For Controlled Release at the IEEE/CPMT Technical Meeting

Oct-13, C. Zwenge

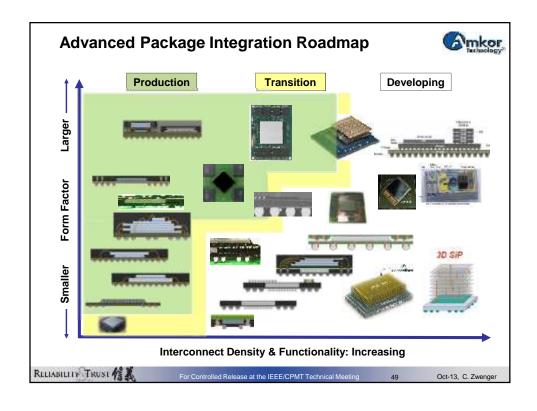

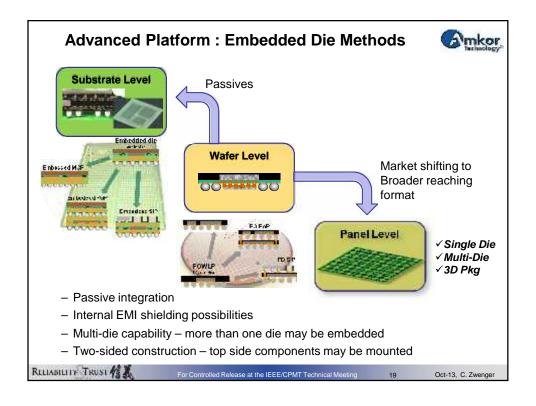

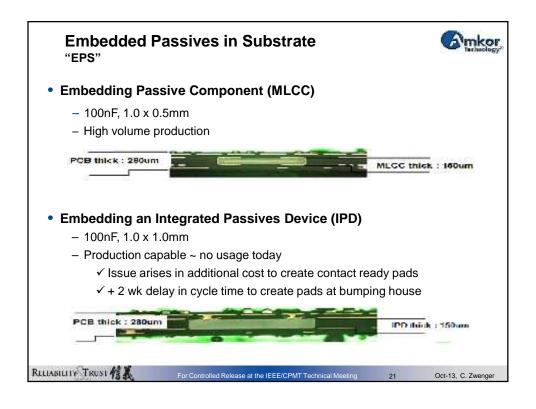

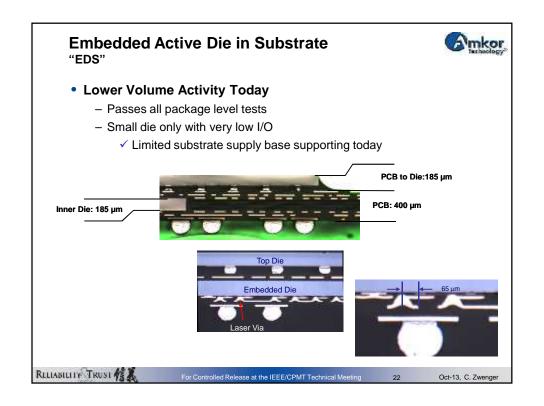

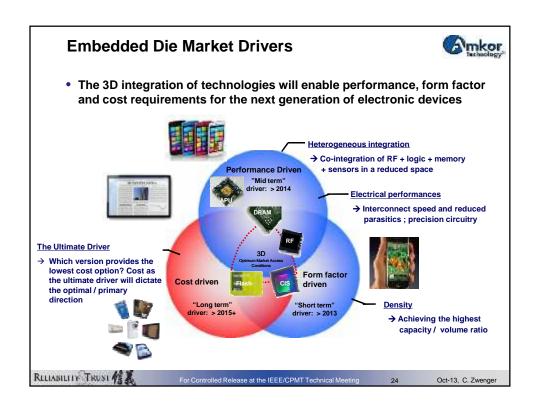

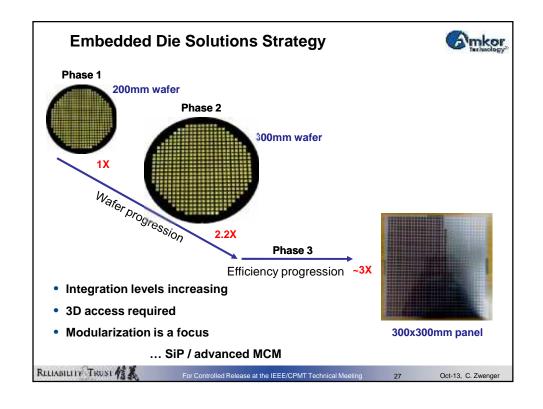

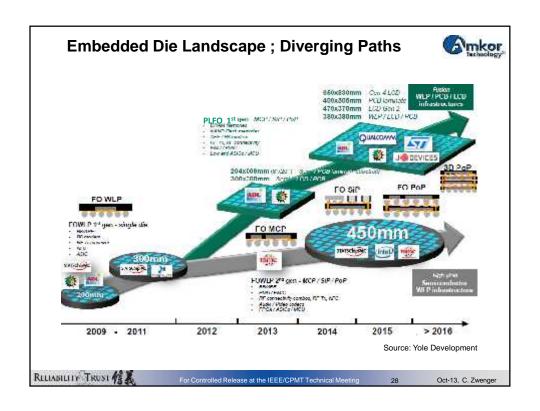

# **Embedded Die as Package Solution**

- Future package technology requires higher levels of integration, thinness, and cost effective solutions

- Planar scaling has ended

- 3D packaging necessary as integration tool

- Embedded die is a key enabling package technology that addresses key product roadmap requirements

- Embedded die in substrate already supported

- Passive integration is in high volumes already

- Active integration is restarting in the industry again

- Industry now focused on a 'Panel Level Embedded Die' platform to address cost, integration, and scalability

- The need for 3D access to the die is increasing

RILIABILITY TRUST 1 For Controlled Release at the IEEE/CPMT Technical Meeting 20 Oct-13, C. Zwenger

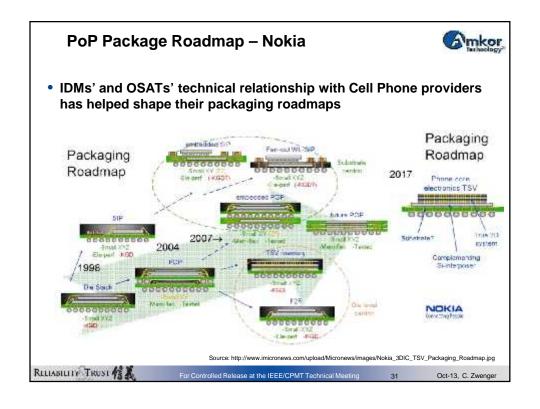

# PoP Packaging Advantages • Each device is packaged separately - Mature technology and infrastructure • Each component is tested and burned-in separately at the package level - Mature technology and infrastructure • No margin stacking - Each component is sourced separately by OEM or EMS provider • Joining technology widely available - Utilizes standard SMT process and existing manufacturing platform • Joining process is very high yielding • Relatively clear ownership of defect liability - Failure analysis methods are mature

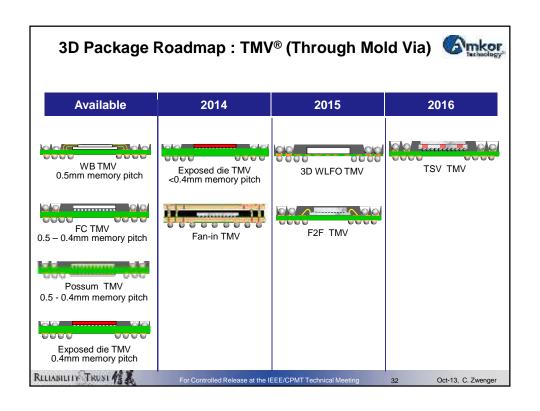

|                                    | Available | 2013     | 2014     | 2015     |

|------------------------------------|-----------|----------|----------|----------|

| Body size (mm)                     | 8~17      | <b>←</b> | <b>←</b> | <b>←</b> |

| Bottom BGA pitch (mm)              | 0.40      | <0.40    | <b>←</b> | <b>←</b> |

| Stand off height (mm)              | 0.18      | 0.13     | 0.10     | 0.08     |

| Memory pitch (mm)                  | 0.40      | <0.40    | <b>←</b> | <b>←</b> |

| Min. mold cap thickness*<br>(mm)   | 0.15      | 0.10     | <b>←</b> | <b>←</b> |

| Substrate thickness (mm) (4-layer) | 0.30      | 0.25     | 0.23     | 0.21     |

| Package height(nom., mm)           | 0.63      | 0.48     | 0.43     | 0.39     |

| Max. stacked-up height**<br>(mm)   | 1.24      | 1.09     | 1.04     | 1.00     |