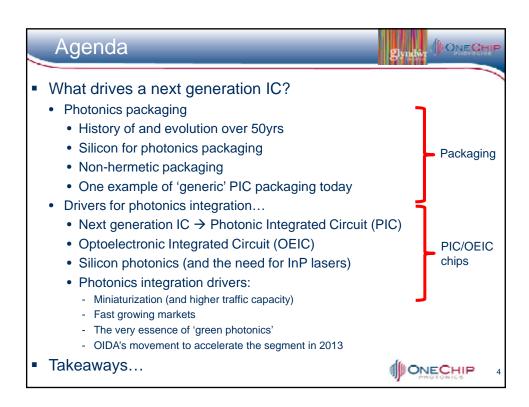

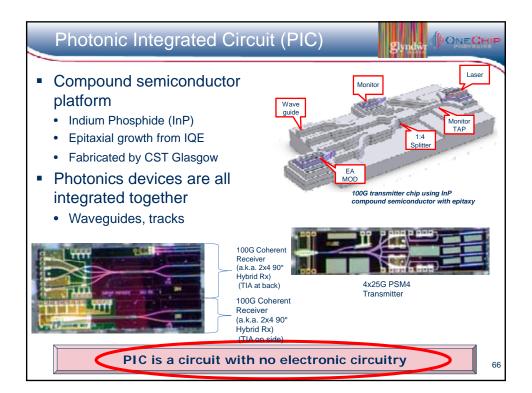

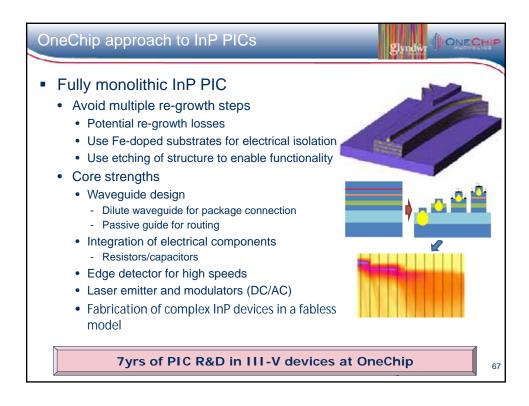

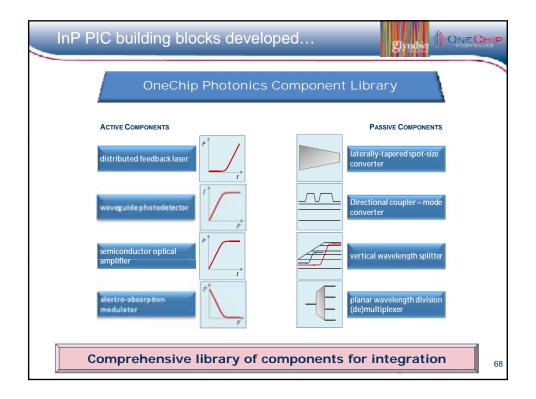

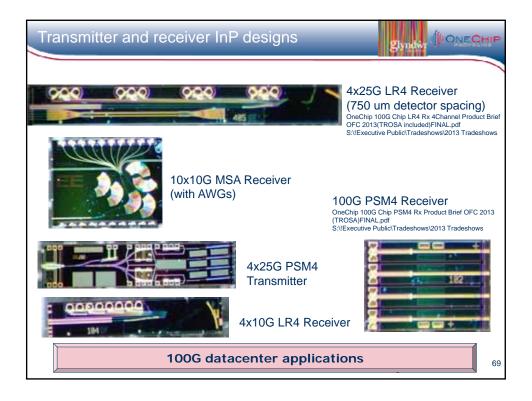

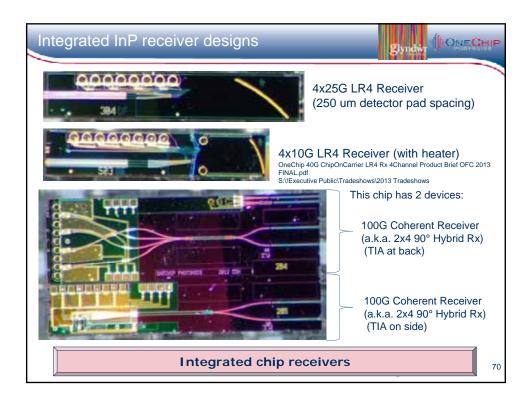

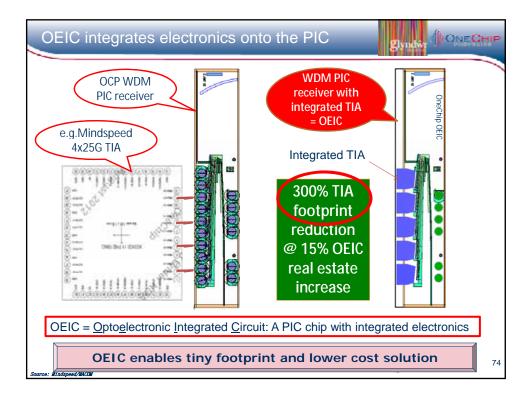

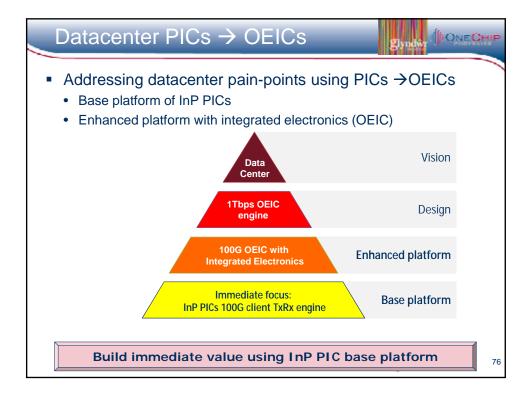

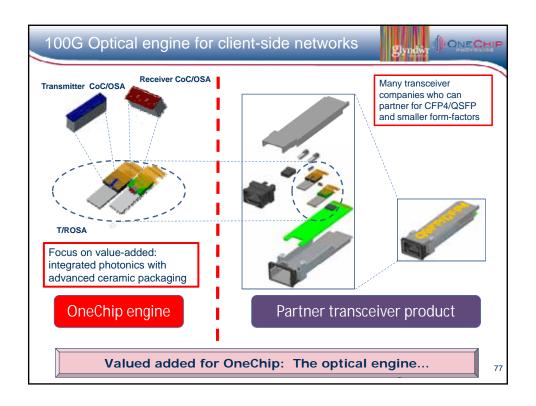

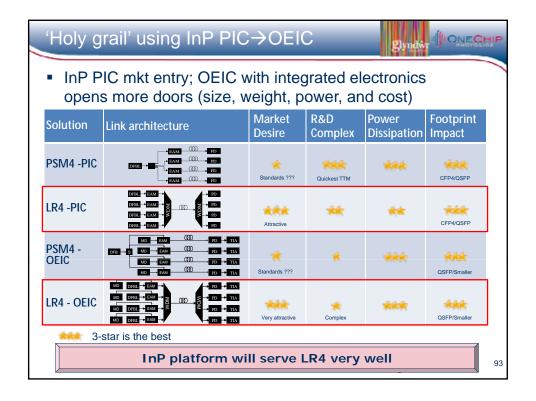

## Overview Is a high-performance datacenter platform using InP a silicon photonics play? This issue will be addressed. Designing and packaging InP-based PICs (Photonic Integrated Circuits) & OEICs (Optoelectronic Integrated Circuits) will be discussed. A review of packaging technologies for datacom products will be made. Particular attention will be a focus on a highly reliable and robust platform with Photonic Integrated Circuits (PICs) that have included lasers, modulators, detectors, waveguides, Mux/Demux, and large spot converters by OneChip Photonics. Current products are focused on both client-side and line-side applications in data and tele-communications networks. Initial performance levels indicate suitability for 100Gb/s datacenter and

50Gb/s metro opportunities using OneChip's InP-based OEIC platform.

Common denominator is packaging...

# Drive by OIDA/OSA in 2013

- Status and future of photonic integration:

- Classic USA roadmap workshop

- ~60 attendees: all from photonics integration field

- Both InP and silicon photonics senior engineers/leaders

- 1 day workshop with sessions on

- · Industry, role of government agency

- · Customer needs for PICs

- Consortia experience

- White paper with high points:

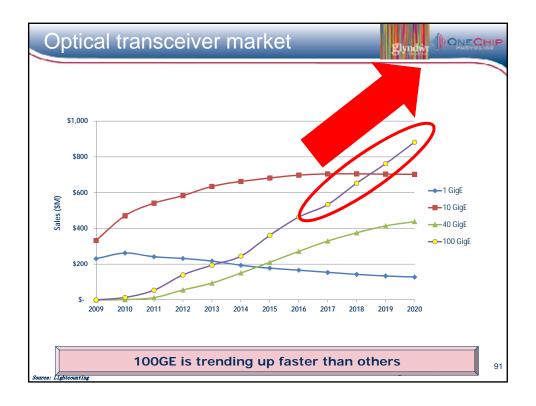

- Growing bandwidth requirements

- · Need to support scaling in challenged industry economics

- Exploration of industry partnerships sharing common technology and manufacturing platforms

- Ways to improve the competitiveness of US industry

- Roadmaps and areas of focus

Drive to position USA to be more competitive in PICs

97

# OIDA takeaways (from my perspective)

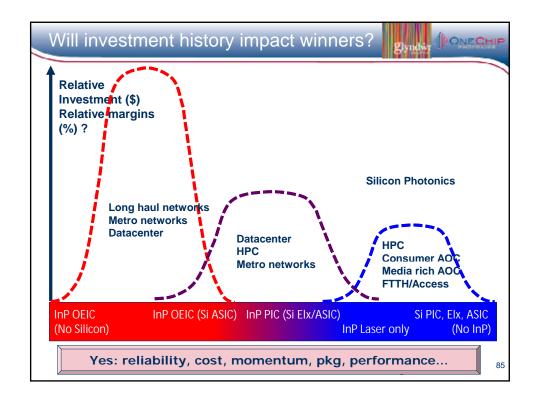

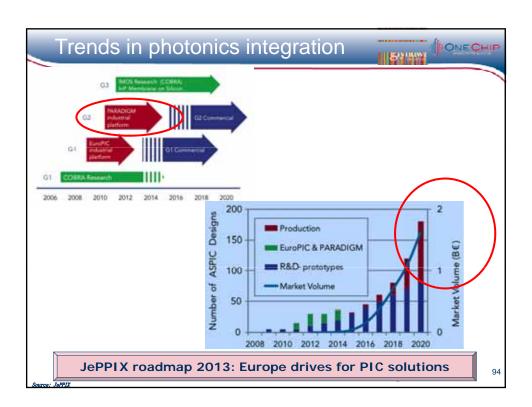

- Photonics integration is here to stay

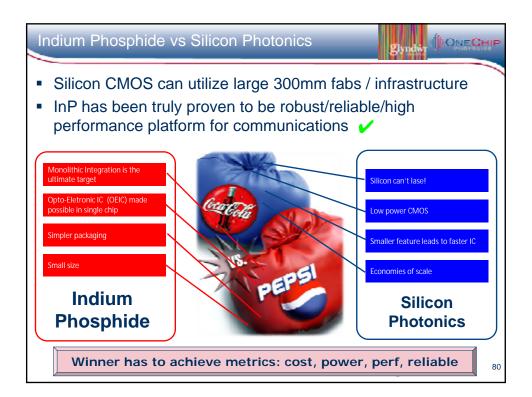

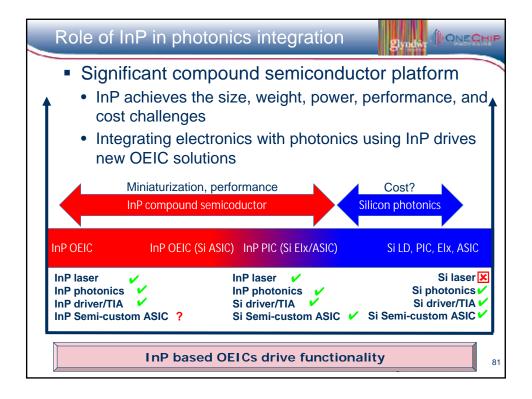

- Complex technology: requires use of CMOS silicon infrastructure and InP experience in communications

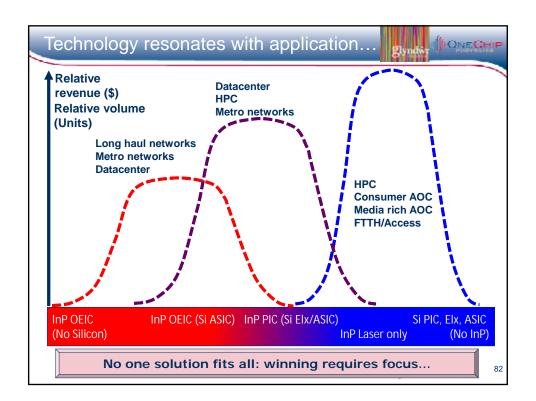

- Combination of silicon and InP will be a successful vehicle for communications (at all levels) consumer, HPC, DC, to metro/long haul

- Stakeholders in USA need:

- Collaborative programs between industry, government, and academia

- Testing/characterization sharing of resources

- Foundry for packaging, assembly and prototyping new PIC/OEIC platforms

- Building of software libraries for advanced photonic components (both silicon and InP)

Drive collaboration in USA...not an easy thing to achieve

98

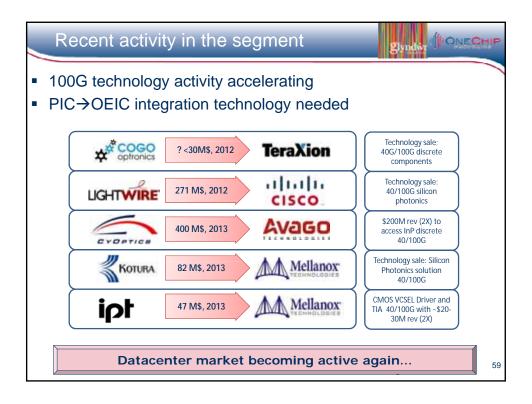

# Takeaways...

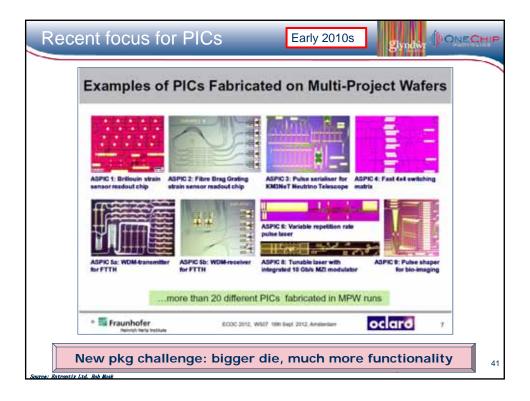

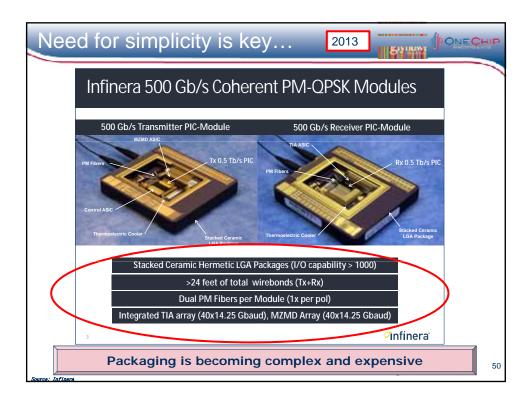

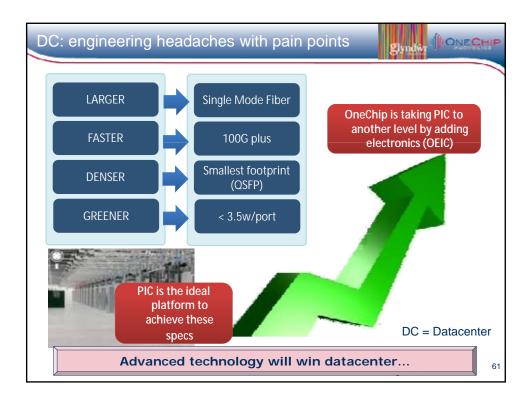

- Packaging of photonics now challenged by integration

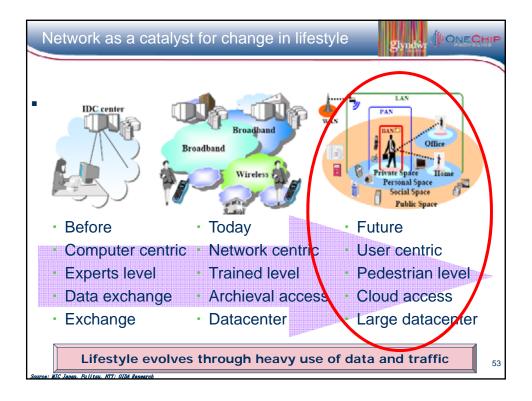

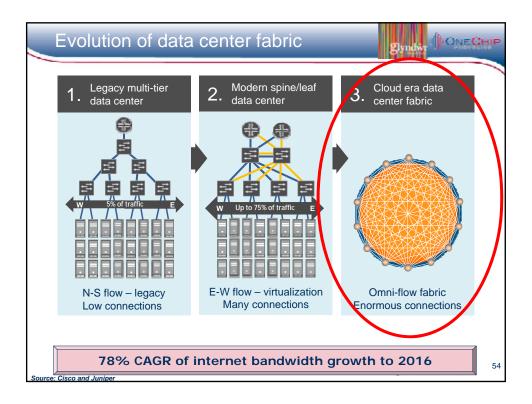

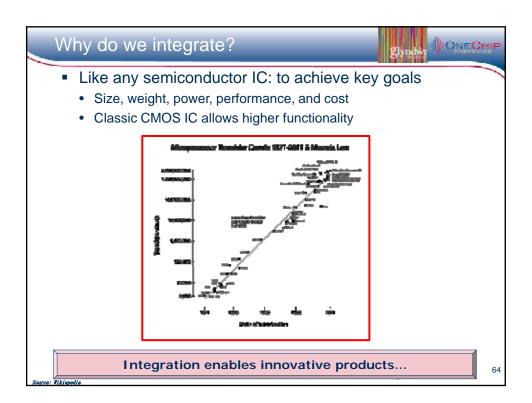

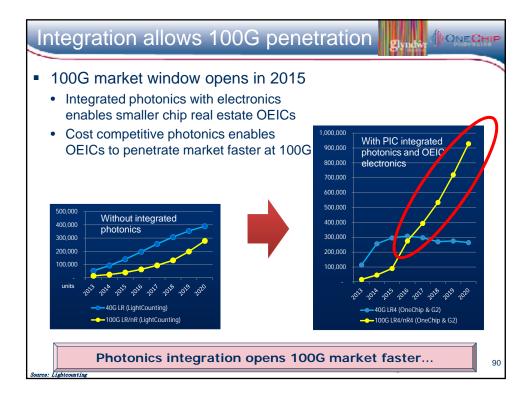

- Next generation ICs will be integrated photonics

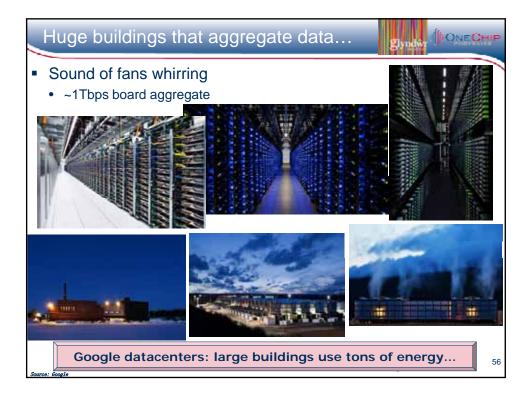

- · Driven by traffic into datacenters

- Datacenter pain points drive photonics integration

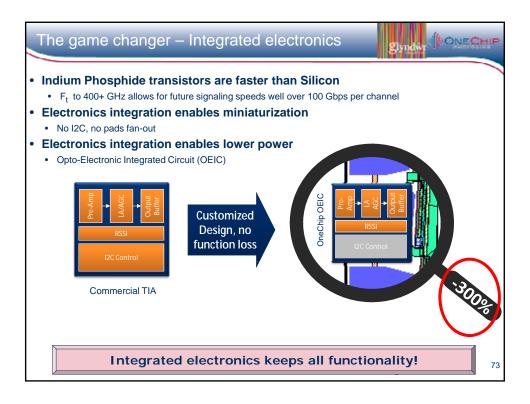

- Photonics integration will grow to include electronics

- PIC → OEIC (optoelectronic integrated circuit)

- Silicon photonics will play a role using InP and impact high volume opportunities

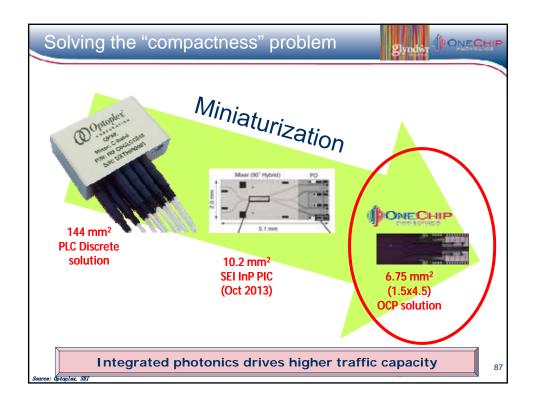

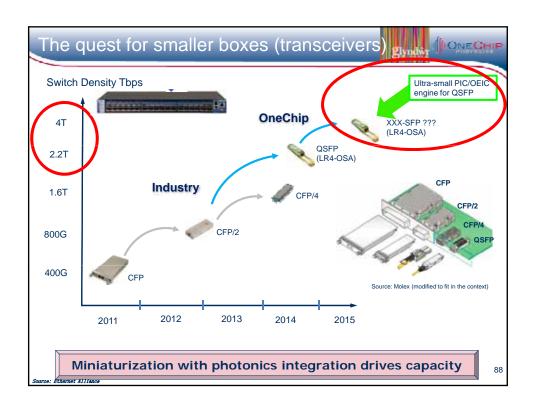

- Miniaturization through integration drives higher traffic capacity through performance (package & thermal issues important)

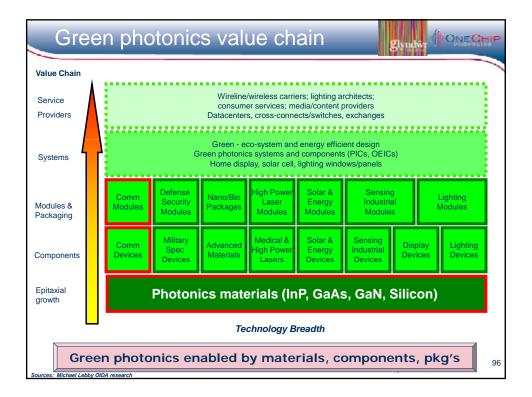

- Photonics is green and will enable new technologies and products that will also be green...

- Photonics integration happening today...

- OIDA uncovered weaknesses → Innovation, funding, collaboration, design tools for chips/packages, test/characterization...

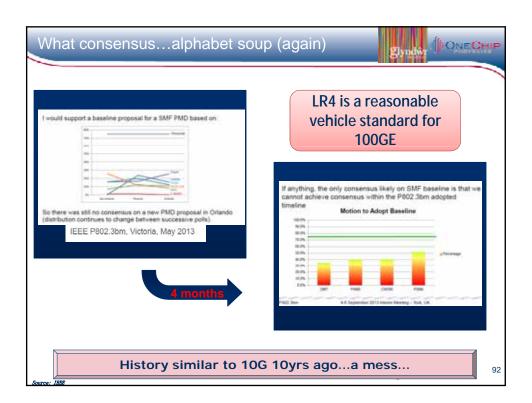

- · Standards: chips, packages, test, simulation, characterization all needed

Photonics integration is emerging...both InP are Si can win

90

# End (thanks for listening) michael.lebby@onechipphotonics.com m.lebby@glyndwr.ac.uk michael@lebby.com

# Background and driver to the workshop

- National Photonics Initiative (NPI)

- Founding sponsors OSA and SPIE (with APS, IEEE, LIA)

- · Making photonics a priority for USA

- Harnessing Light (National Academy report 1998) → NPI

- Identify and advance areas of photonics critical to maintaining competitiveness and national security

- (1) Drive funding and investment in areas of photonics critical to maintaining USA competitiveness and national security

- Advanced manufacturing, defense, energy, health and medicine, IT, and communications

- (2) Develop federal programs that encourage great collaboration between USA industry, academia, and gvt labs

- To better support the R&D of next-generation photonics technologies

- (3) Increase investment in education and job training programs

- To reduce the shortage of technically skilled workers in photonics positions

- (4) Expand federal investments for university and industry collaborative research

- To develop new manufacturing methods that incorporate photonics

- (5) Collaborate with USA industry to review international trade practices

- impeding free trade and the current USA criteria restricting sale of certain photonic technologies overseas

Make USA more competitive in photonics

102

# Datacenter vs HPC perspective:

- Key observations

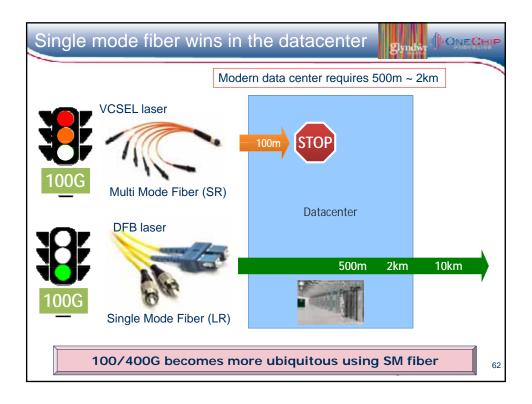

- 10c per Gbps metric (distances up to 2km) maybe 1 solution fits all

- Expectation that DC pricing fall in line with HPC (soon)

- 400G to 1.6T range for total data rates

- HPC thinking about SM fiber in addition to MM fiber

- Move data rates from 25G to 50G; wavelengths from 4 to ~16

- Packaging trending towards optics being close to signal sources

- · PIC technologies aiming for next generation super computer

- Power constraints problematic but not seen to be extreme

- Creating eco-system that allows performance to go form teraflops to exaflops

- Create 400G/1T interfaces (100/200G parallel not attractive solution)

- Extend OOK to alternative modulation techniques (non-coherent), and increase use of DSP as complexity increases

Challenge in cost and performance

103

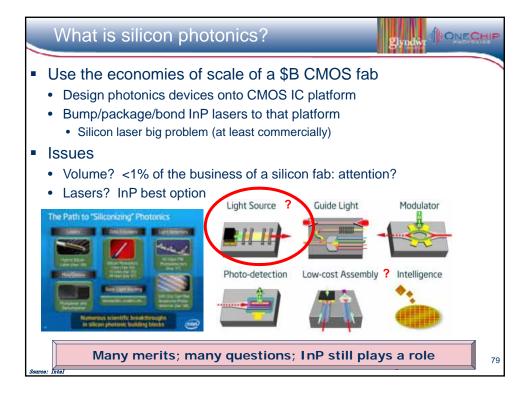

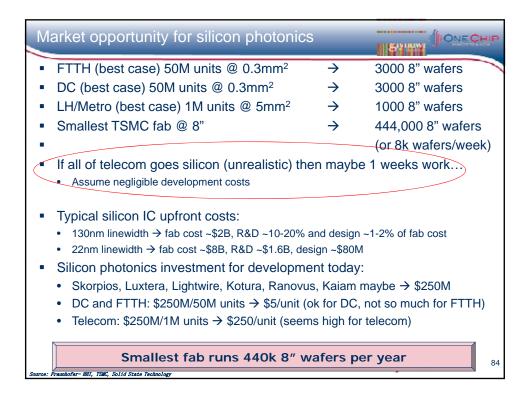

### Silicon photonics perspective:

- Silicon photonics observations:

- Focus on PIC interfacing with optics and chip

- Focus on testing and evaluation

- Exploring single materials platform for all device types (going for best overall performance even if device is not best in class)

- Looking at ubiquitous interfaces with electronics (more work required)

- · Aiming to achieve goals of 1pj/bit in optical links

- Today Tx ~50pj/bit @10Gbps & Rx 250fj/bit @10Gbps

- Aiming to communication >1Tbps between photonic chips

- CMOS industry: leverage, leverage, leverage

- 300mm wafers, how to achieve economies of scale (volume) and serious attention when photonic throughput is 1% of CMOS capacity

- Excite CMOS industry to design and package optics

- Need package innovation high performance optics on a par with ICs

Leverage CMOS industry; test/evaluation; package

www.cpmt.org/scv/ 52

104

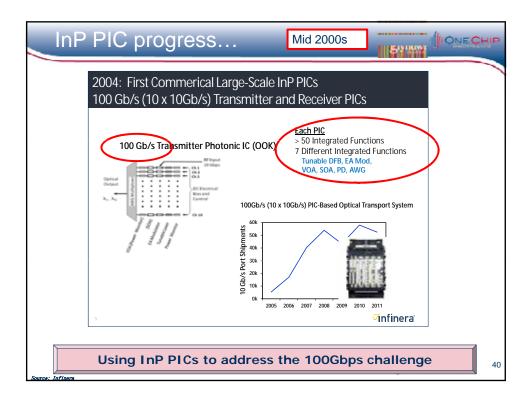

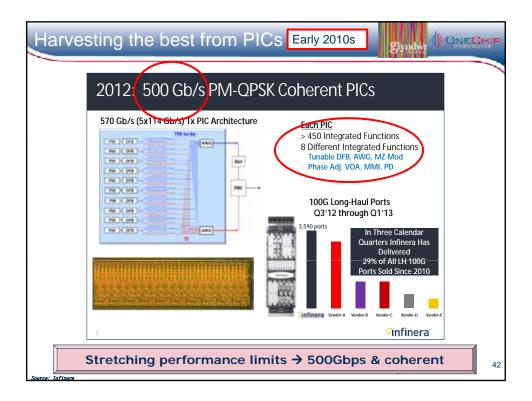

# InP PIC perspectives:

- InP material system observations:

- Extend performance to 4Tbyte devices using more complex modulation schemes (line side)

- Push performance beyond 500Gbps (5x114Gbps) Tx PIC architecture

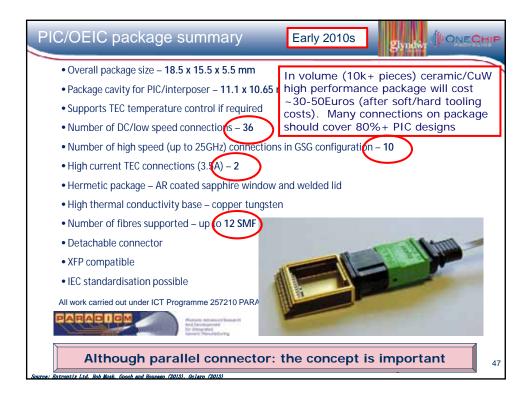

- Find easier ways to package using ceramic CoC engines

- Maintain reliability levels in the <10Fit rates (down to 1Fit)

- Drive cost reduction 5-10x in \$ per Gbps

- Explore ways to integrate driver/TIA functions in InP

- Create common platforms for testing and evaluation (similar to ICs)

- Drive client-side DC solutions to 50Gbps

- Create more cost effective CoC/OSAs for QSFP and smaller Tx/Rx boxes

- Challenge to improve packaging → look at 2.5D and 3D assembly with advanced Flip-chip and BGA approaches

Cost reduction, package, higher performance, smaller

105

# System & fiber perspectives

- System (line-side)

- Extend use of QPSK even though QAM being deployed in field

- 16QAM is complex

- Increase card performance from 100G to 500G with PIC if it helps reduce the overall equipment cost

- Promote CD ROADM (Colorless, Directionless, ROADM)

- 80-100 wavelengths/fiber and 50GHz spacing with 32G symbol rates

- System (metro)

- PIC preferred for many designs

- Fiber cable:

- Explore multicore fiber to increase capacity

- Explore fiber-chip coupling issues

- Explore ways to increase MM performance to 300m at 25G (1310nm with SM/MM launch

Make the system more efficient

106