# Tools for Thermal Analysis: Thermal Test Chips

TOM TARTER, PRESIDENT, PACKAGE SCIENCE SERVICES LLC

IEEE/CPMT SCV EVENING TECHNICAL DINNER

DECEMBER 10, 2014

PACKAGE SCIENCE SERVICES LLC 3287 Kifer Rd. Santa Clara, CA 1-408-969-2388 www.pkgscience.com

#### Introduction

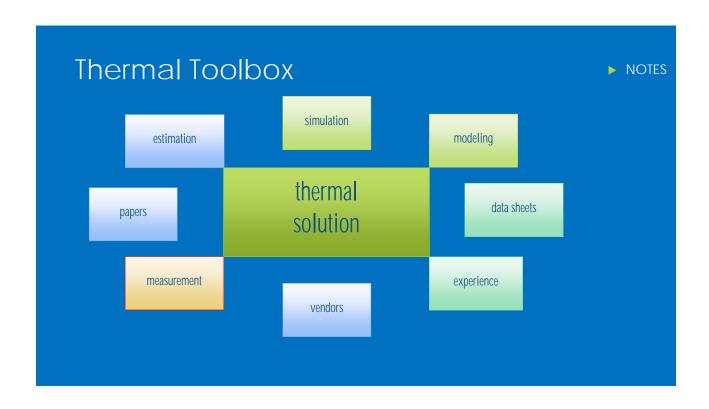

- Most products today need some knowledge of the cooling solution, often before the device or system is complete

- Many times prior to having working silicon or complete system information the thermal components must be identified, procured and evaluated

- ► Estimations based on experience, models, supplier input, data sheets, etc. guide the design team to the most cost-effective solution

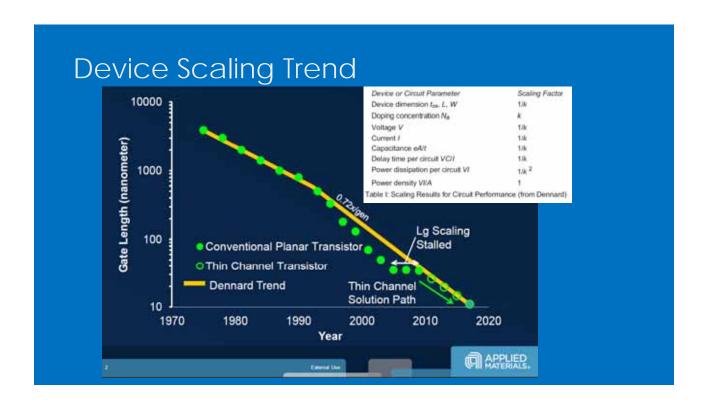

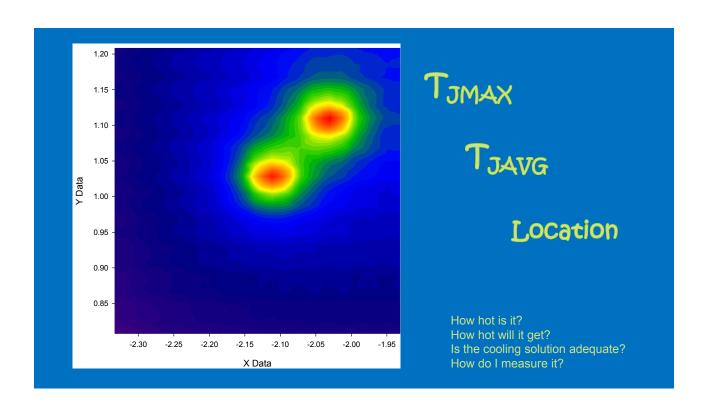

- With decreasing gate length and pitch, many more functions can be placed in smaller regions, creating hot spots and temperature gradients

### Test Chip Study

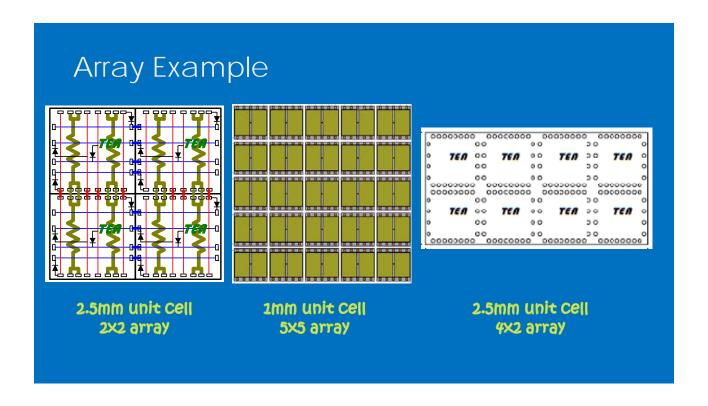

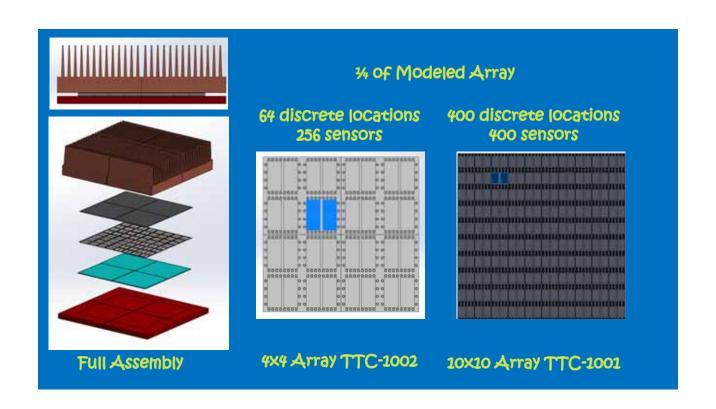

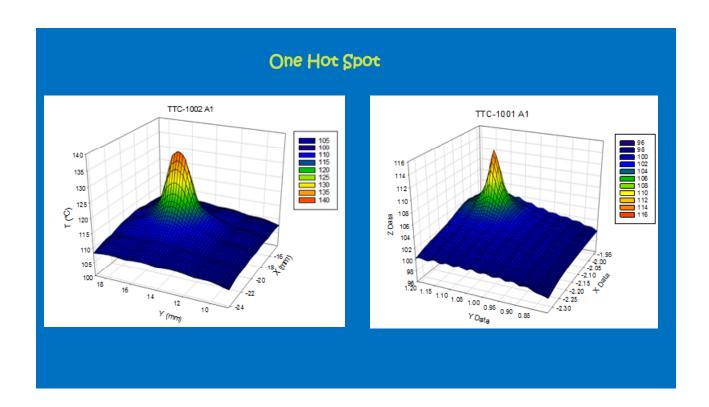

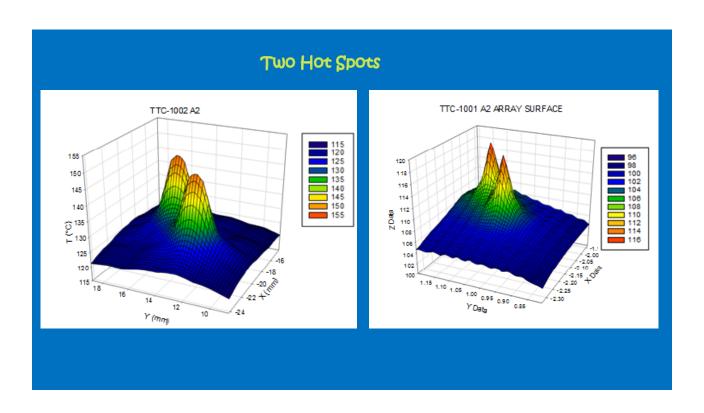

- Thermal models are generated to illustrate an application of an array of unit cells

- Meant to simulate a typical flip-chip attached microprocessor or ASIC chip on a package

- Shows the capability to produce hot spots and the versatility of a typical array

- Quarter symmetry

| # |                     |                 |                          |  |  |

|---|---------------------|-----------------|--------------------------|--|--|

|   | Component           | Geometry        | Description              |  |  |

|   | Chip array          | 20.32mm, square | 8x8 (1002), 20x20 (1001) |  |  |

|   | Bump 24x165um bumps |                 | 100um standoff height,   |  |  |

|   | per unit cell       |                 | underfill                |  |  |

|   | TIM                 | 20.32mm x 0.1mm | Between chip backside    |  |  |

|   |                     |                 | and heat sink            |  |  |

|   | Heat sink           | 27mm, 2.54mm    | Cu, 1mm pitch            |  |  |

|   | base, 5mm fin       |                 |                          |  |  |

|   | Substrate           | 27mm x .5mm     | BGA package              |  |  |

| Table 2. Power Density (PD) T <sub>J</sub> ≤125°C |       |         |                   |  |  |

|---------------------------------------------------|-------|---------|-------------------|--|--|

| Parameter                                         | 2.5mm | 1mm     | Unit              |  |  |

| $I_{ m IM}$                                       | 0.89  | 0.55    | A                 |  |  |

| R                                                 | 7.5   | 10      | Ω                 |  |  |

| Pd (per R)                                        | 5.9   | 3.0     | W                 |  |  |

| Area (min)                                        | 0.018 | 0.00606 | cm <sup>2</sup>   |  |  |

| $PD_{MAX}$                                        | 330   | 499     | W/cm <sup>2</sup> |  |  |

| # | Table 3. Power Mapping (20mm square die size)    |                 |             |                 |                |             |  |

|---|--------------------------------------------------|-----------------|-------------|-----------------|----------------|-------------|--|

|   | Cell Size                                        | No.<br>Resistor | Pd/<br>Cell | Pd/<br>Hotspot* | No.<br>Hotspot | Pd<br>Total |  |

|   | 2.5mm                                            | 128             | 0.5         |                 | 0              | 64          |  |

|   | 2.5mm                                            | 127             | 0.5         | 5               | 1              | 68.5        |  |

|   | 2.5mm                                            | 127             | 0.5         | 5               | 2              | 73.5        |  |

|   | 1mm                                              | 800             | 0.08        |                 | 0              | 64          |  |

|   | 1mm                                              | 798             | 0.08        | 1.66            | 1              | 65.5        |  |

|   | 1mm                                              | 796             | 0.08        | 1.66            | 2              | 67          |  |

|   | *Power density is equivalent for both chip sizes |                 |             |                 |                |             |  |

| Table 4. Power Calculations, smallest area in cell |                      |              |               |                    |  |  |

|----------------------------------------------------|----------------------|--------------|---------------|--------------------|--|--|

| Cell<br>Size                                       | Cell R Area<br>(cm²) | Pd/<br>R (W) | PD<br>(W/cm²) | Cell R Dim<br>(mm) |  |  |

| 2.5mm                                              | 0.0182513            | 0.5          | 27.39525      | 1.986 x .919       |  |  |

| 1mm                                                | 0.0060613            | 0.08         | 13.19845      | .678 x .447 (2)    |  |  |

| 2.5mm                                              | 0.0182513            | 5            | 273.9525      | 1.986 x .919       |  |  |

| 1mm                                                | 0.0060613            | 1.660        | 273.8677      | .687 x .447 (2)    |  |  |

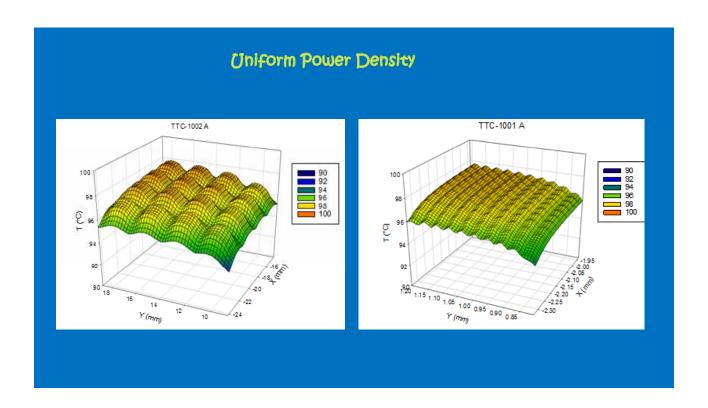

| Table 5. Min, Max, Average Array Model Results |        |            |       |            |  |  |

|------------------------------------------------|--------|------------|-------|------------|--|--|

| Tjmin                                          | 2.5mm  | $\Delta T$ | 1mm   | $\Delta T$ |  |  |

| uniform                                        | 93.75  |            | 94.36 |            |  |  |

| 1 hot spot                                     | 105.9  | 12.15      | 98.4  | 4.04       |  |  |

| 2 hot spot                                     | 119.7  | 25.95      | 102.6 | 8.24       |  |  |

| Tjmax                                          | 2.5mm  | ΔT         | 1mm   | $\Delta T$ |  |  |

| uniform                                        | 98.1   | -          | 97.7  |            |  |  |

| 1 hot spot                                     | 135.8  | 37.7       | 114   | 16.3       |  |  |

| 2 hot spot                                     | 150    | 51.9       | 119.2 | 21.5       |  |  |

| Tjavg                                          | 2.5mm  | ΔT         | 1mm   | ΔT         |  |  |

| uniform                                        | 95.925 | -          | 96.03 |            |  |  |

| 1 hot spot                                     | 120.85 | 24.925     | 106.2 | 10.17      |  |  |

| 2 hot spot                                     | 134.85 | 38.925     | 110.9 | 14.87      |  |  |

## Model Summary

- ▶ Shows versatility of test chip for evaluating thermal behavior

- ▶ Can create hot spots, sections with varied power dissipation

- ▶ Very high power density, allows simulation of extreme chips

- ► Can array into any size, up to ~100mm square

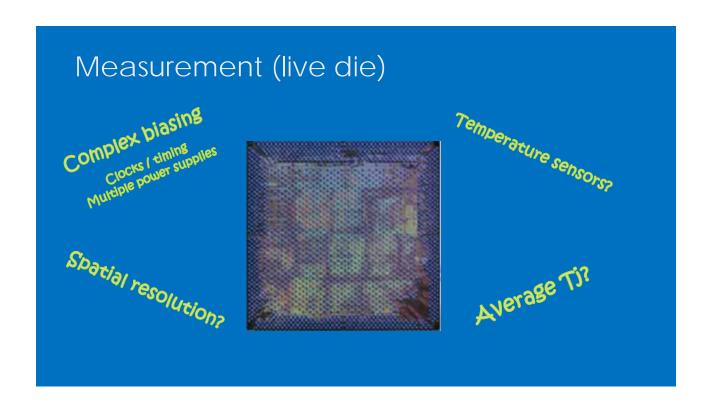

### Why Use Test Chips?

- ▶ EASE OF USE

- ► ACCURACY

- ▶ ARRAYABLE ADDRESSABLE VERSATILE

- ▶ LOOK AHEAD

- ▶ STACKED, MCM, 2.5 or 3D packaging

- ▶ Reduces Time-to-Market

- ▶ COOLING SOLUTION AT THE RIGHT TIME, RIGHT COST

## THANK YOU!

WWW.PKGSCIENCE.COM

WWW.THERMENGR.NET

PACKAGE SCIENCE SERVICES LLC 3287 Kifer Rd. Santa Clara, CA 1-408-969-2388 www.pkgscience.com

#### **Acknowledgements**

- ▶ Thanks to Bernie Siegal of Thermal Engineering Associates

- ► A 30 Year Retrospective on Dennard's MOSFET Scaling Paper, Mark Bohr, Intel Corporation

- Precision Materials to Meet Scaling Challenges Beyond 14nm, Semicon 2013, Adam Brand, SSG Transistor Technology Group, Applied Materials

- ▶ B. Siegal, J. Galloway, "Thermal Test Chip Design and Performance Considerations", 24<sup>th</sup> Annual SEMI-THERM Symposium, 2008.

- "Ball Grid Array Technology", J. H. Lau, Editor, Mcgraw-hill, Inc. 1995, ISBN 0-07-036608-X

- K. Matsumoto; K. Sakuma; F. Yamada; Y. Taira, "Investigation of the thermal resistance of a three-dimensional (3D) chip stack from the thermal resistance measurement and modeling of a single-stackedchip", International Conference on Electronics Packaging, p.478, 2008

#### References

- ▶ T.-Y. Chiang; K. Banerjee; K. C. Saraswat,. "Analytical thermal model for multilevel VLSI interconnects incorporating via effect", IEEE ELECTRON DEVICE LETTERS, vol.23, p.31, 2002.

- ▶ B. Zhan, "Evaluation of Simplified and Complex Thermal Fnite Element Models for a 3-die Stacked Chip Scale Ball Grid Array Package", 29<sup>th</sup> IEEE/CPMT/SEMI International Electronics Manufacturing Technology symposium, July, 2004.

- Z. Celik, "Thermal Characterization of Various 2.5 and 3D Package Configurations for Logic and Memory Applications", MEPTEC 2.5D, 3D and Beyond: Bringing 3D Integration to the Packaging Mainstream seminar, MEPTEC/SEMI, November, 2011.

- M. Janicki, A. Napieralski, J. H. Collet and A. Louri, "Hot Spots and Core-Core Thermal Coupling in Future Multicore Architectures", 26<sup>th</sup> Annual IEEE SEMI-THERM Symposium, March 2010.

- ► Thermal Engineering Associates, Inc. Technical Briefs, www.thermengr.net/TechBrief/.