Configurable Sintered Interconnect (CSI™) for Semiconductor Packaging

#### **About EoPlex**

- Headquartered in San Jose, CA

- Subsidiary of ASTI since 2012

- 14 factories, 4 R&D centers located in 8 countries

- 2,300 employees world wide

- Production Facilities in Penang

- Expanding Manufacturing Capability in Cavite, Philippines - Q3 2015

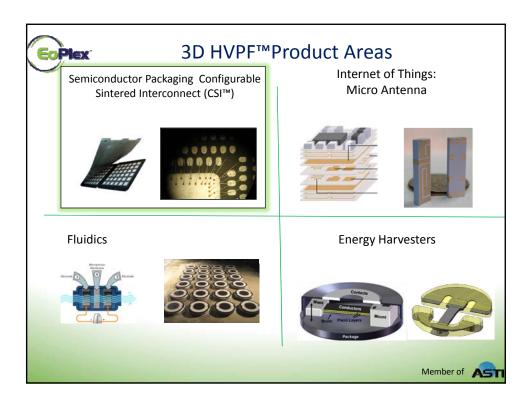

- Creator of 3D High Volume Print Forming process (HVPF™) for multi material 3D printing

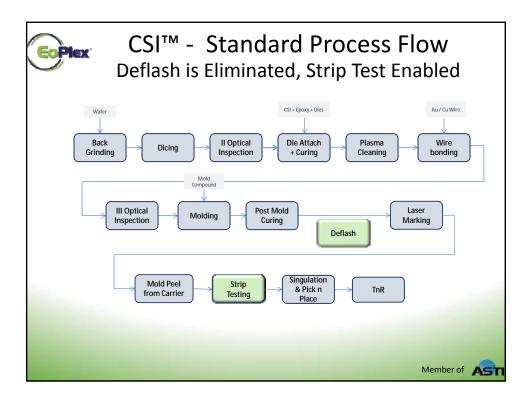

# CSI is Fully Compatible with Standard QFN Infrastructure

No Etching or plating required

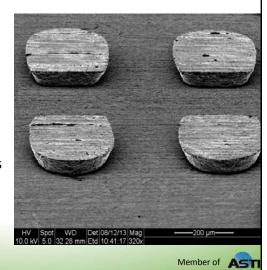

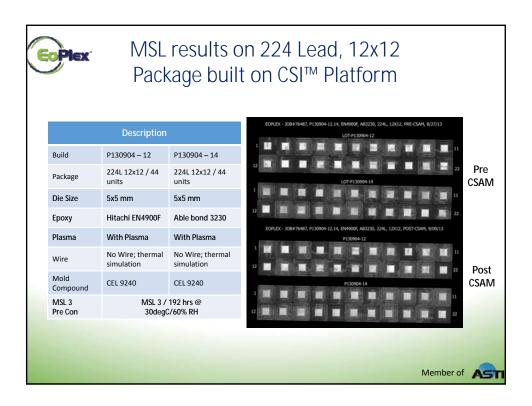

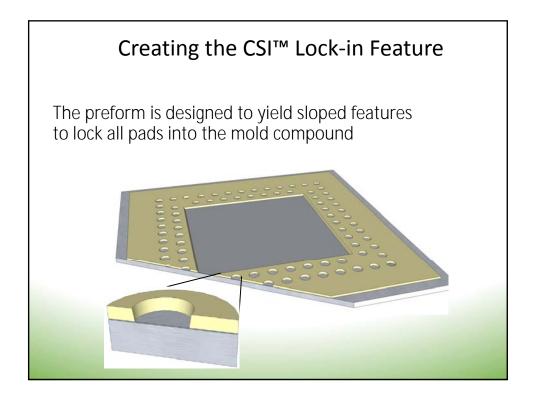

## Pad Shape Provides Lock-in Feature and Surface Texture Improves MSL Performance

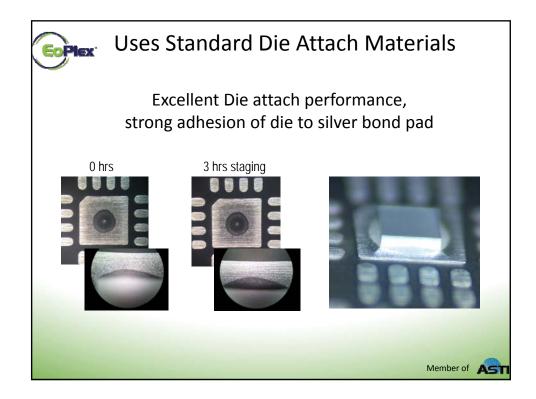

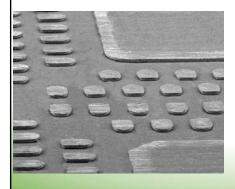

- Surface roughness of sintered silver improves adhesion

- Die Pad Avg: 0.87umBond Pad Avg: 0.45um

- Conical frustum shaped pads

- Excellent locking of Leads with mold compound

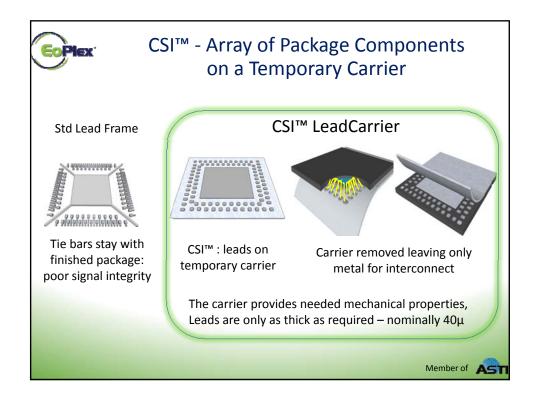

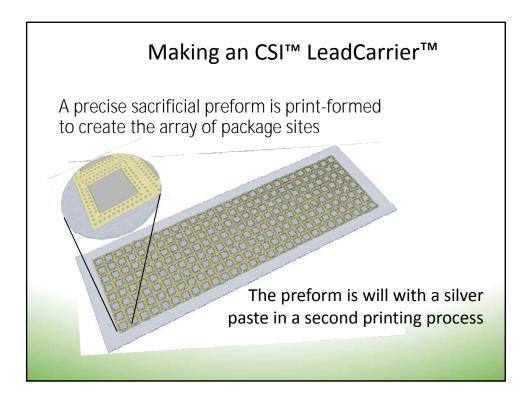

Manufacturing Process For EoPlex CSI™ LeadCarrier

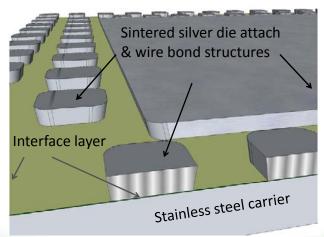

#### Remove the Preform & Sinter the Silver

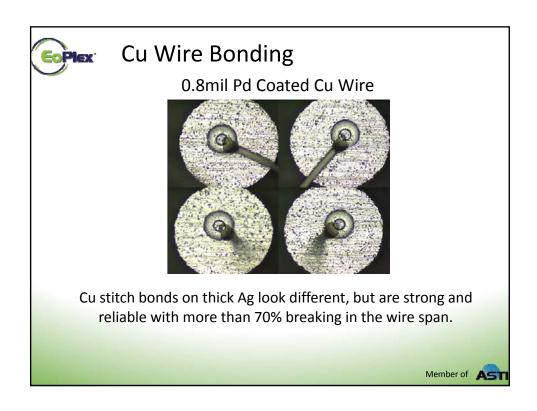

Strips are fired to remove the preform and sinter the metal to high density, giving an excellent wire bonding surface

Result is an array of pads with excellent bonding surfaces, controlled adhesion to the carrier and a shape that locks the pads to the mold compound

#### Interface Chemistry: A Key to CSI™Success

Chemistry of the interface layer provides good adhesion and clean release, with no treatment of solderable surfaces necessary.

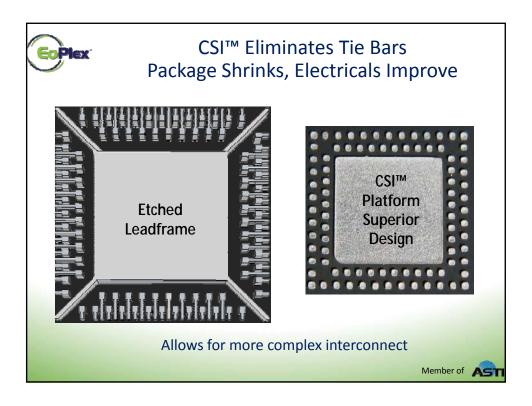

### Comparison to Standard **Etched Leadframe**

#### Relative to total cost of ownership

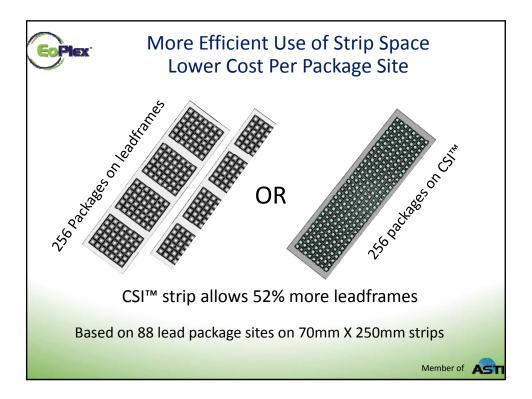

- Strip pricing: ≈50% higher

- Strip utilization: As much as 50% greater

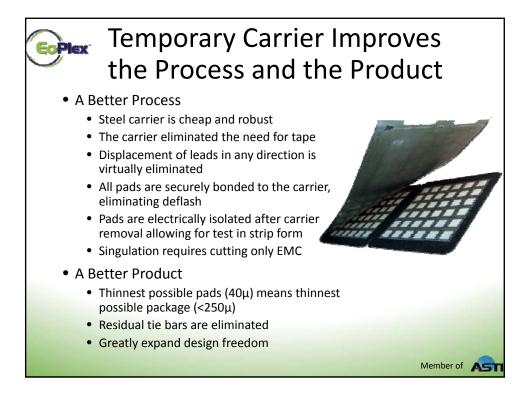

- No tape required

- Cut only thin EMC for singulation

- Test in strip is possible

#### Relative to performance metrics

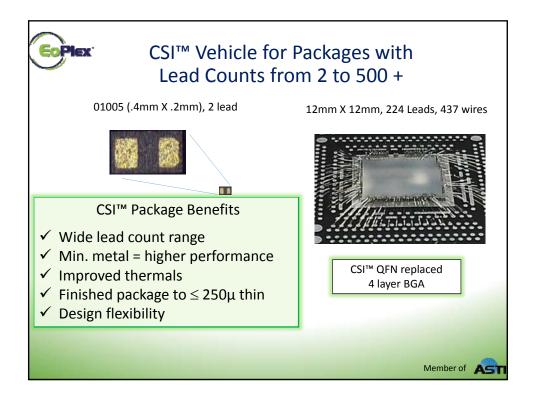

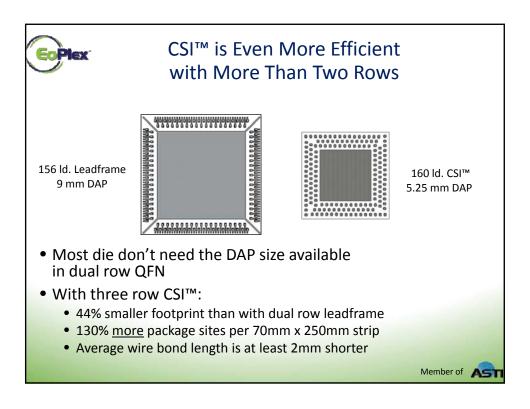

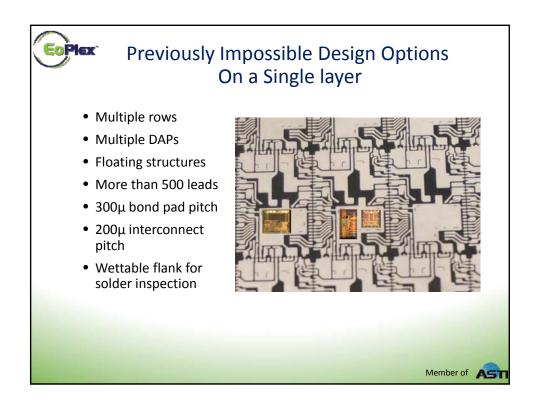

- Multiple rows, up to around 500 leads

- Design freedom includes multi-chip, redistribution

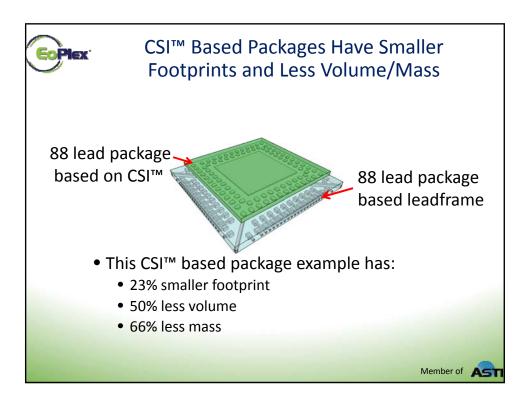

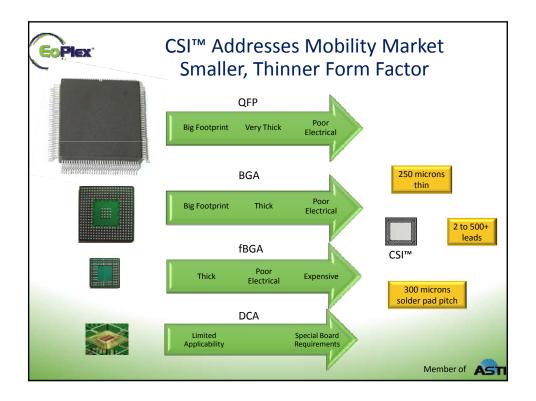

- Minimum package thickness to 0.2mm vs 0.3mm

- No tie bar stubs = better electrical performance

- Very low thermal resistance

- Solderable lead flank as singulated

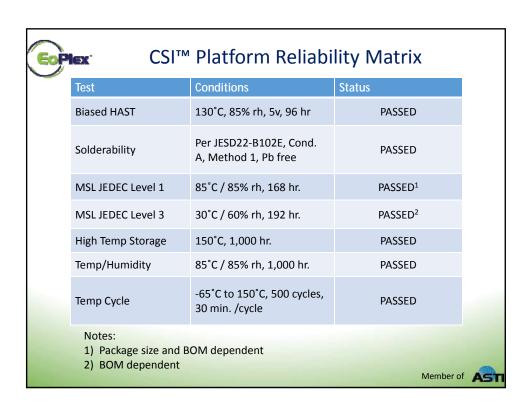

#### Summary: EoPlex CSI™ Platform Driving a New Interconnect Paradigm

#### Final cost per lead up to 50% less

- ➤ Improves strip density by up to 50%

- ➤ No tape backing saves cost and disposal

- > Faster lower cost singulation only plastic is cut

- > Electrical testability in the strip after peel

- ➤ No plating or etching "green process"

- > Fits standard process

#### Improved performance, enables replacement of more expensive packages like BGAs

- ➤ Packages from 2 to 500+ leads

- ➤ Minimum metal = better electrical performance

- > Excellent thermal performance

- Enables smaller and thinnest (200u) packages

Member of AS