© 2014

# Consideration for Advancing **Technology in Computer** System Packaging

Dale Becker, Ph.D. IBM Corporation, Poughkeepsie, NY

#### **Motivation**

- Modern Computing is driven by

- -Cloud

- -Analytics

- -Mobile

- -Social

- -Security

- With many data inputs

- Demanding sophisticated analytics

- Sent back to distributed users

- Securely

- ➔More Data Bandwidth

- →Less Data Latency

- →Higher integration of computing, networking and storage

3

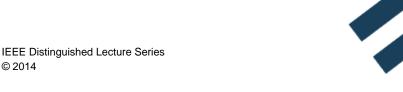

#### Big Data: Why we must move to a new era of computing.

# What is Technology? zEnterprise EC12:

### Proposed Ecosystem Enablement

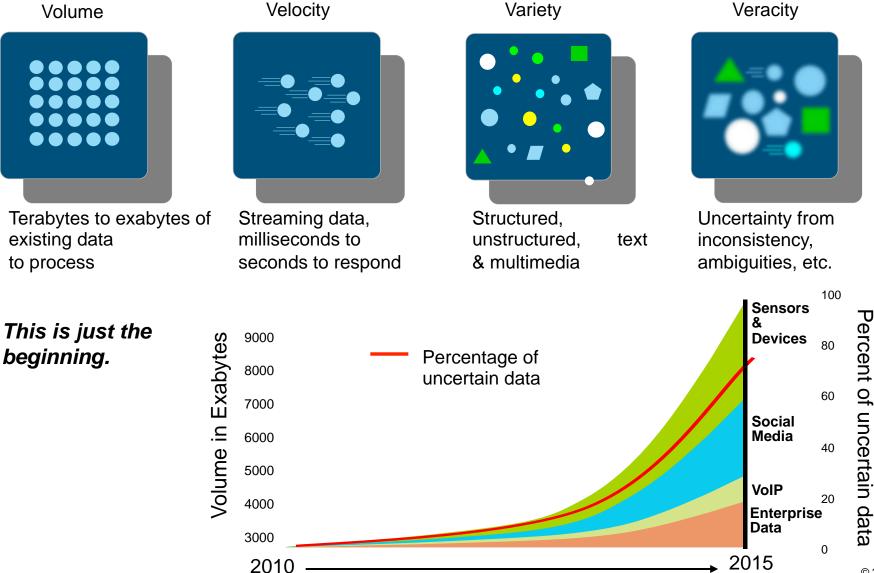

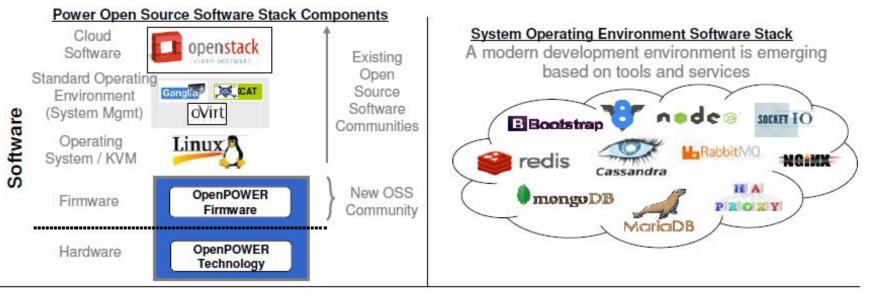

#### Multiple Options to Design with POWER Technology Within OpenPOWER

2015

#### 50 Years of Mainframe - 1964 IBM S/360

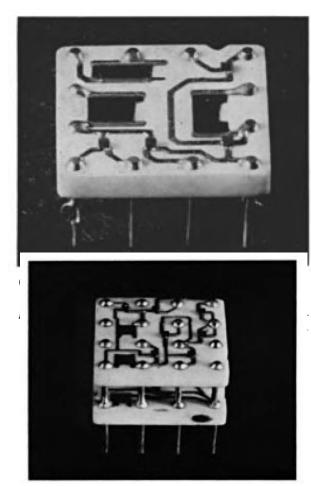

Figure 1 AND/OR INVERT logic module. (a) Completed AOI module, without overcoating. (b) Logic circuit.

| Resistors       | 28 | 19 | (All R: 5%) |

|-----------------|----|----|-------------|

| Transistor      | 7  | 0  |             |

| $D_1, D_2, D_3$ | 0  | 2  |             |

| $D_4$           | 1  | 1  |             |

| $D_5$           | _1 | _1 |             |

| Total           | 37 | 23 |             |

|                 |    |    |             |

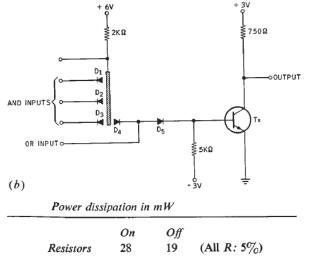

Figure 13 Stacked module.

Solid Logic Technology: Versatile, High-Performance Microelectronics Davis, E.M.; Harding, W.E.; Schwartz, R.S.; Corning, J.J. IBM Journal of Research and Development Volume: 8, Issue: 2 Publication Year: 1964, Page(s): 102 - 114

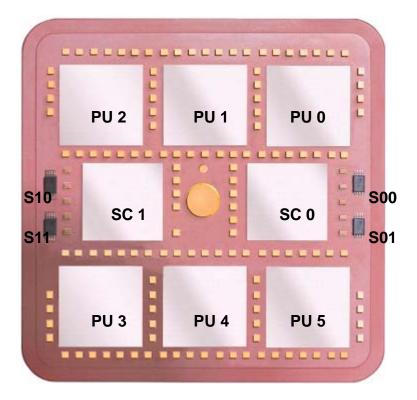

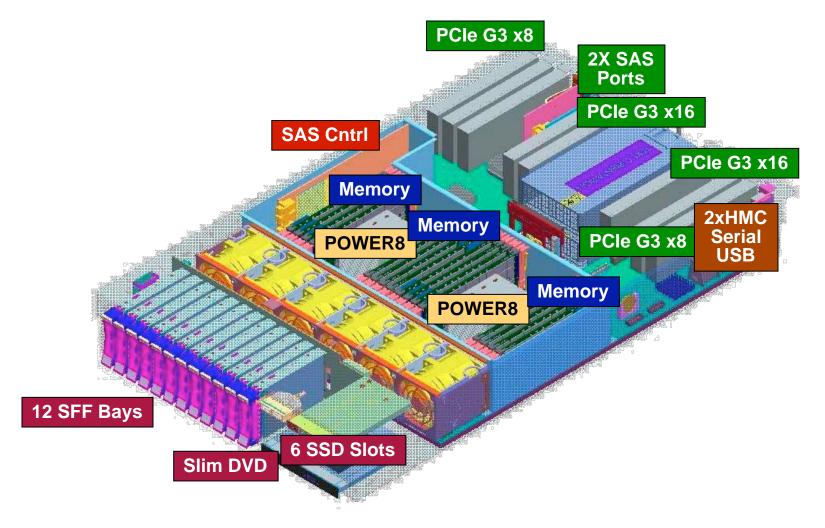

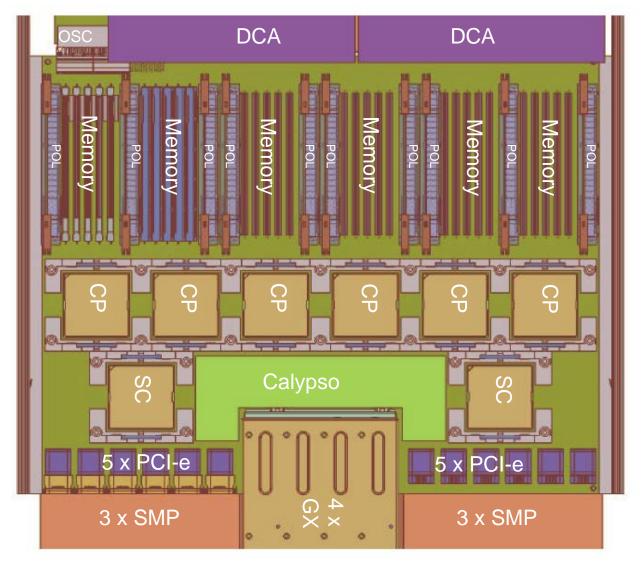

#### **POWER Die**

|            |                 |            | 222                             |            |            |            |

|------------|-----------------|------------|---------------------------------|------------|------------|------------|

| Core       | Core            | Core       | Local SMP Links<br>Accelerators | Core       | Core       | Core       |

| L2         | L2              | L2         | WP L<br>erato                   | L2         | L2         | L2         |

|            | 8M L3<br>Region | 10         | inks                            | er -       |            |            |

| MemCtrl    | L3 C            | ache an    | d Chip                          | Intercor   | nnect      | MemCtr     |

|            | 111             | 1.1        | Remote<br>PCI Ge                |            |            |            |

|            |                 |            |                                 |            |            |            |

| L2         | L2              | L2         | lote                            | L2         | L2         | L2         |

| L2<br>Core | L2<br>Core      | L2<br>Core | iote SMP Links<br>I Gen 3 Links | L2<br>Core | L2<br>Core | L2<br>Core |

Figure 5.1.7: Annotated POWER8 die photo.

POWER8: A 12-core server-class processor in 22nm SOI with 7.6Tb/s off-chip bandwidth Fluhr, E.J. ; et. al. <u>Solid-State Circuits Conference Digest of Technical Papers (ISSCC)</u>, 2014 IEEE International Publication Year: 2014 , Page(s): 96 - 97

Ongoing Challenges for system packaging

- Cost development and product cost

- Physical form factor Incremental changes

- Signal bandwidth density Increasing quickly

- Voltage regulation (Power In) Integrate closer to load

- Cooling (Power out) Constant power density

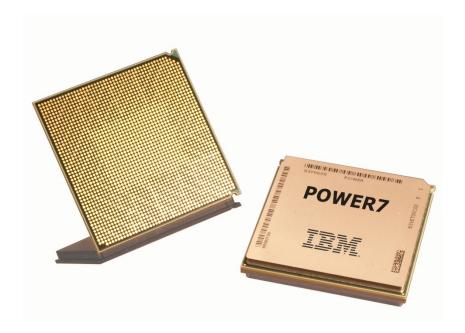

#### **Processor Packaging**

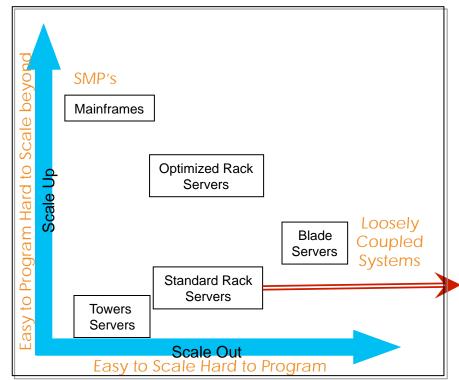

### **Traditional vs. "Cloudified" Hardware**

- "Scale-Up"

- Symmetrical Multiprocessing Systems

- Large shared memory machines

- Expensive to scale beyond a certain size

- 4 / 8 / 16 / 32 sockets

- 4U/10U/Rack Sized Systems

- "Scale-Out"

- Loosely coupled systems

- "Infinite" Scale

- Mostly 1 & 2 sockets

- 1U / 2U Form Factor (0.33/0.5/1 wide)

- Significant changes in programming & application paradigms

Hadoop/HDFS / NoSQL DB's....

- Open source software community driven

- → Linux / OpenStack ...

# **Scale-out**

#### http://www.ibm.com

# Scale-up

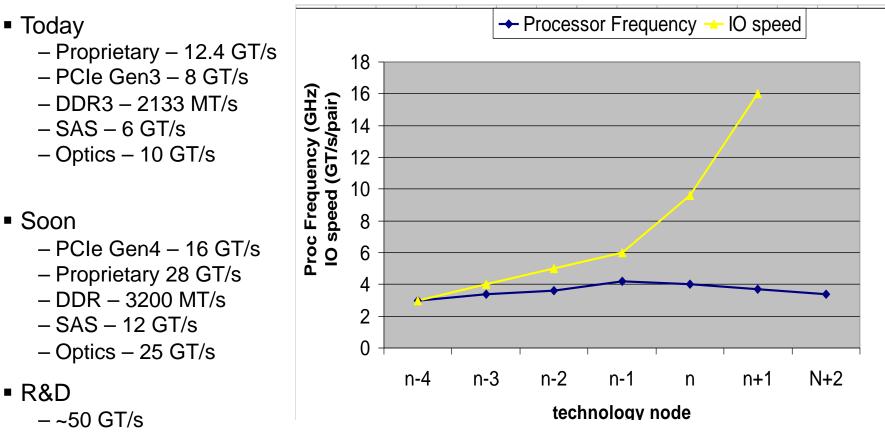

## Data rates are increasing

- PAM4 vs NRZ

- Tighter optics integration

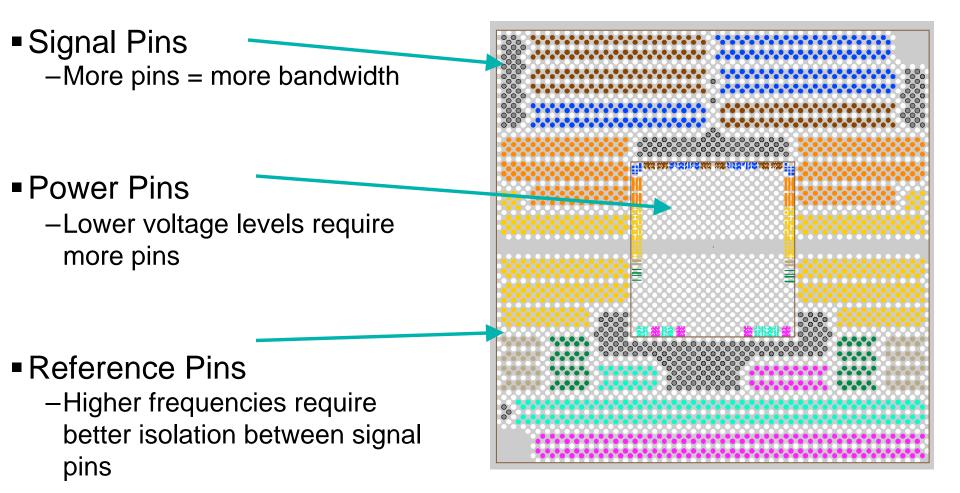

#### Socket Pin Assignment

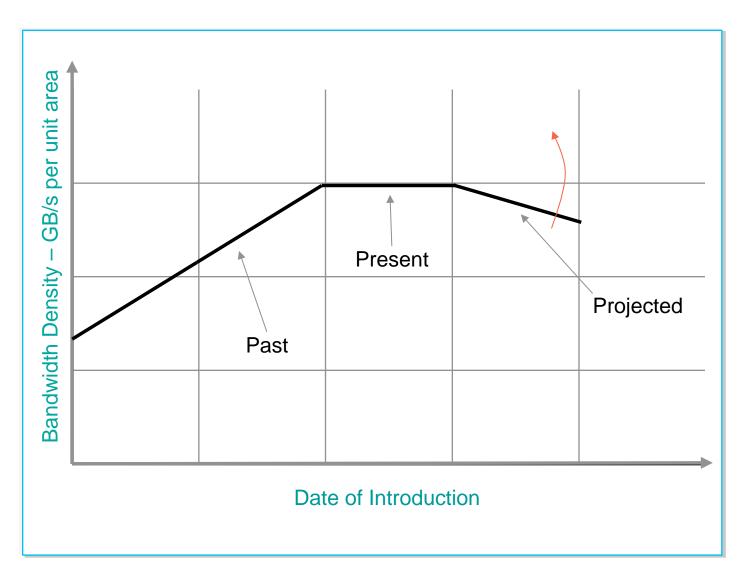

#### Reaching a bandwidth breakpoint at the socket level

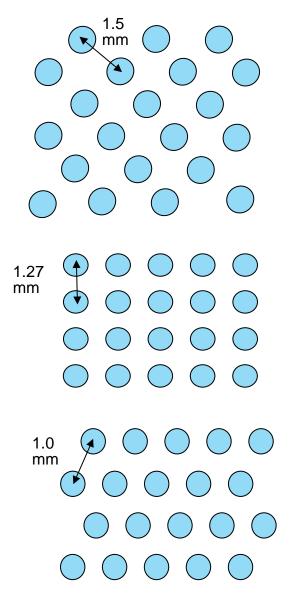

#### **Pin Density Increases Incrementally**

- Over 20 years

- -1.5 mm min pitch interstitial

- -50 mil (1.27 mm) square

- -1 mm square

- -1 mm min pitch hexagonal

- Sockets are pin limited

- Crosstalk needs to be managed

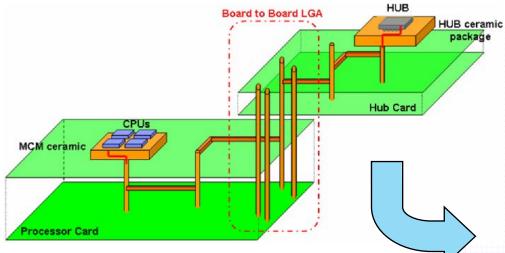

#### Form factor limitations

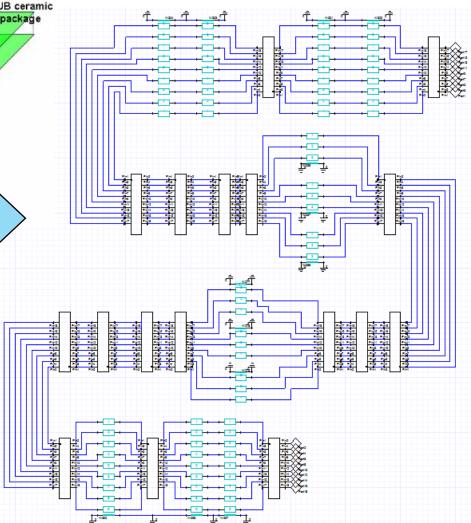

- The system under analysis is composed by two PCBs, two MCMs and three connectors

- To represent it adequately 52 models are needed:

- 1. W-elements to model the TL portions

- 2. S-parameters (Touchstone) for the 3D parts (Vias and connectors).

- 3. Mpilog Precompensation Driver macromodel

- 4. Frequency step for touchstone: 50 MHz

- Total channel length ~ 70cm

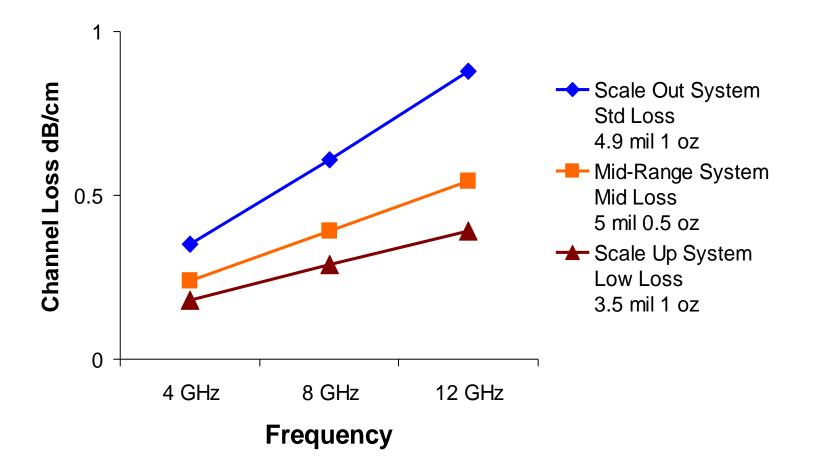

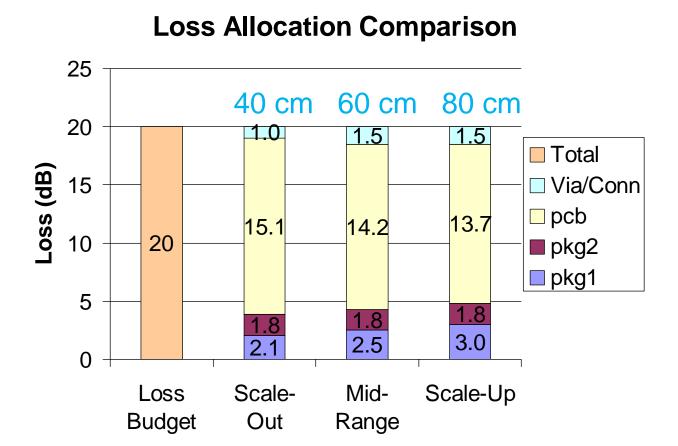

PCB Technology Choices Same speed, different technology

All systems are 8 GT/s meet 20dB total channel loss

## Impact of PCB loss – Size of system, length of PCB trace

015

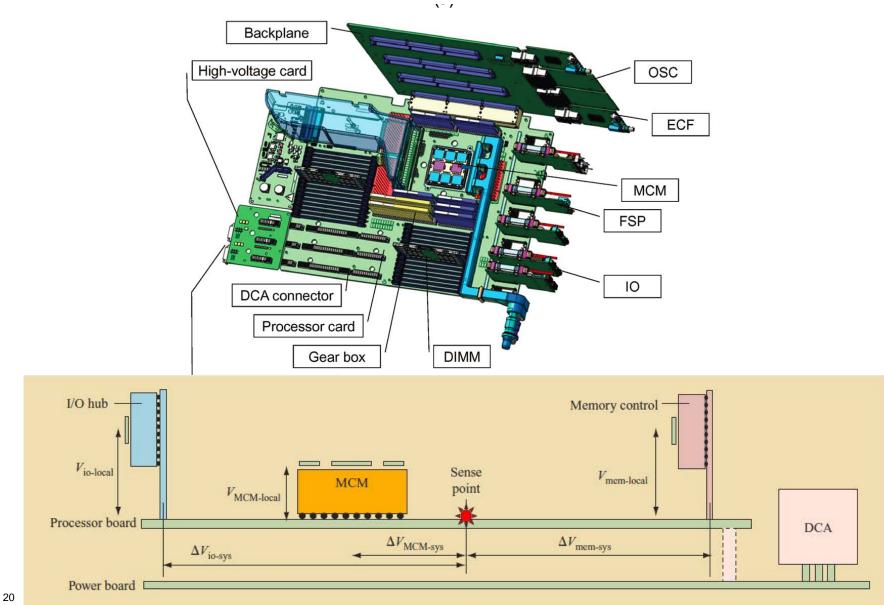

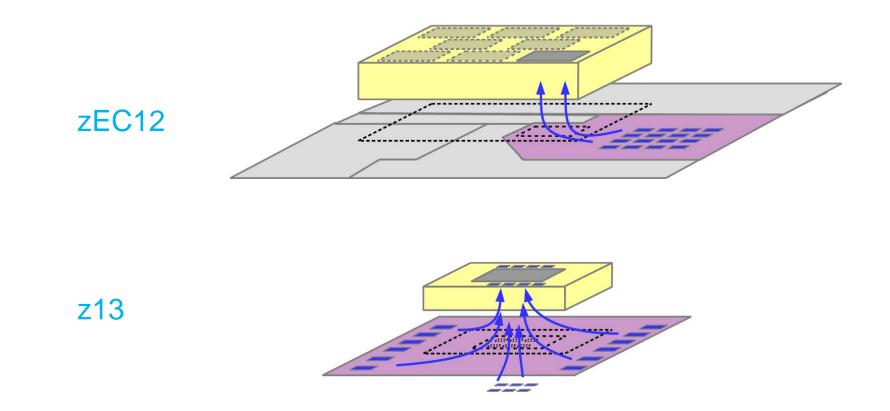

#### z196/EC12 Compute Cage

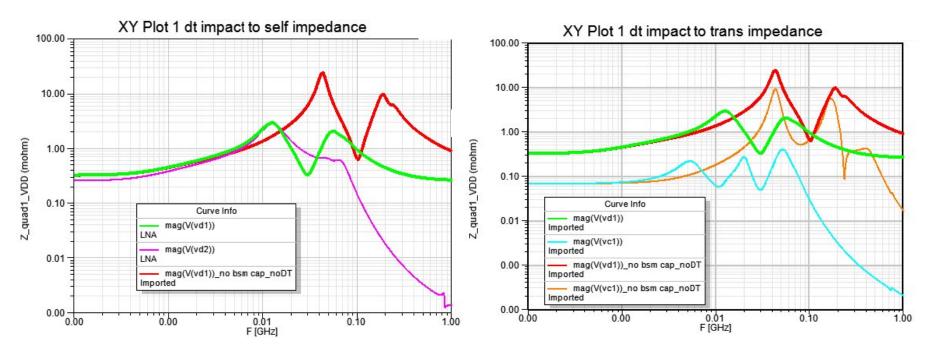

### **Decoupling improvement**

#### Improved power distribution often counters increased density

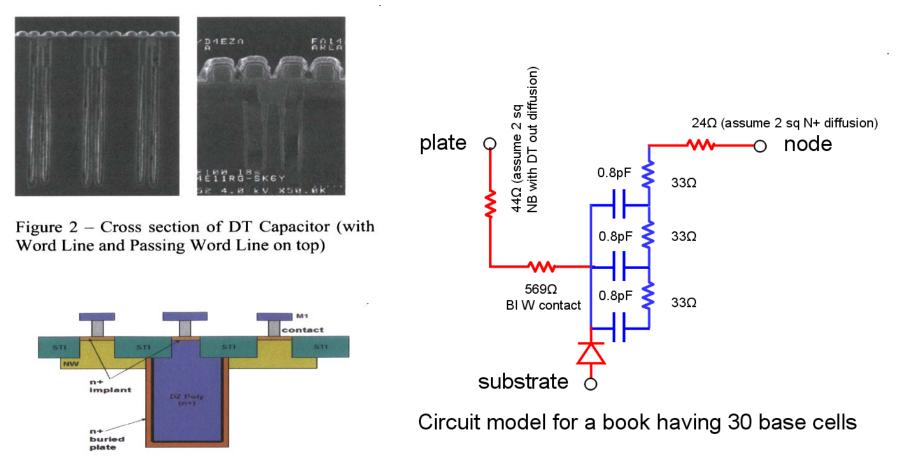

#### Deep trench technology – DT capacitors

Figure3: Schematic cross section of DZ capacitor

C. Pei, "A novel, low-cost deep trench decoupling capacitor for high-performance, low-power bulk CMOS applications," 9<sup>th</sup> 22 ICSECT, pp. 1146-1149, 2008

© 2015

Power issues : On-chip Caps – Deep Trench

- Deep Trench capacitors

- -Enables significant increase (~20uF) in on-chip decoupling.

- -Mid/high-freq noise significantly reduced

- -Facilitates on-chip voltage regulation

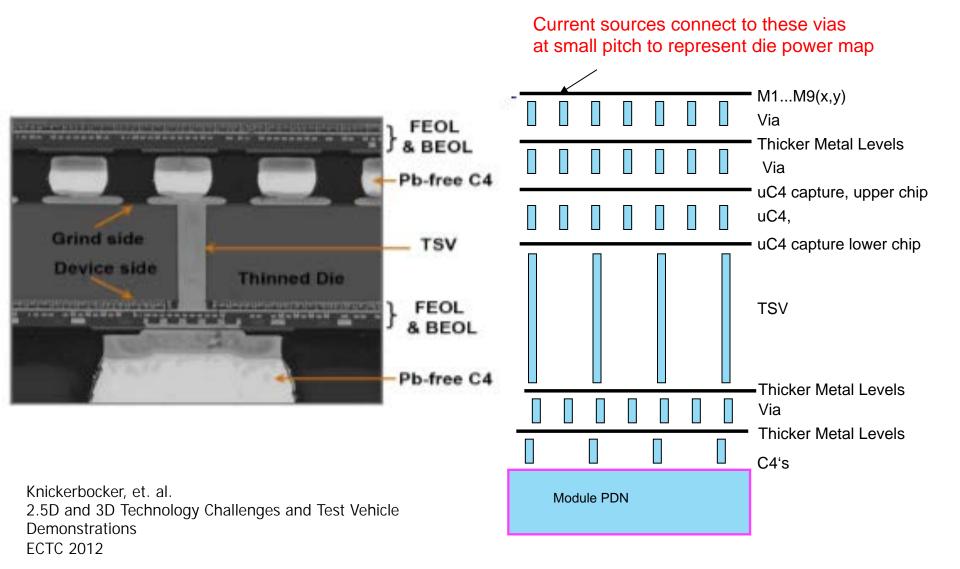

#### 3D chip stacking modeling

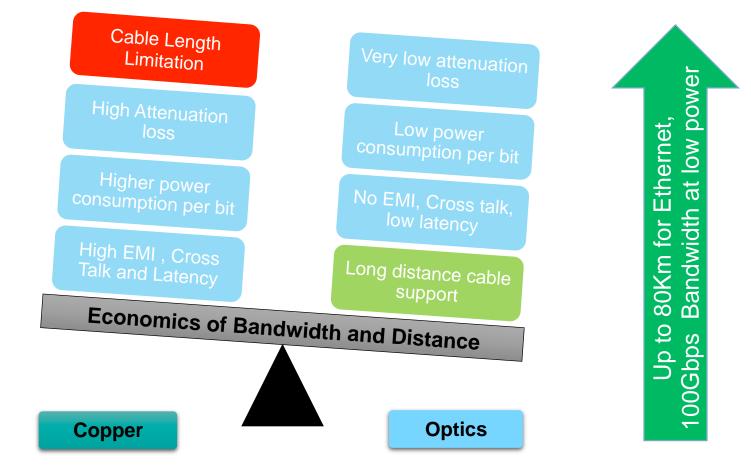

### **The Case for Optics**

- Increasing benefits with optical, but products generally cost more than copper

- Optics less expensive when integrated with silicon Silicon Photonics

- Photonics integrated into silicon base

- Reduces cost and provides higher bandwidth

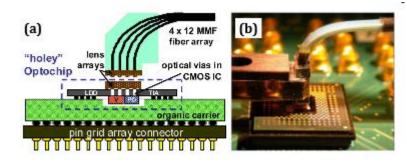

#### **Future Integration**

#### Increasing Bandwidth Density in Future Optical Interconnects

B. G. Lee, C. Baks, F. E. Doany, C. Jahnes, R. John, D. M. Kuchta, P. Pepeljugoski, A. V. Rylyakov, C. L. Schow, S. Assefa, W. M. J. Green, Y. A. Vlasov, J. A. Kash IBM T. J. Watson Research Center, 1101 Kitchawan Road, Yorktown Heights, NY 10598 bglee@us.ibm.com

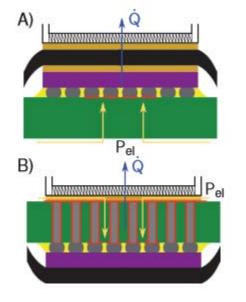

Cold Plate TIM1 Thermal Vias Solder Interface IC Component

CIPS 2014, February, 25 - 27, 2014, Nuremberg/Germany

#### Laminate with Thermal - Power Insert for Efficient Front-Side Heat Removal and Power Delivery

Dominic Gschwend\*, Timo Tick\*, Stefano Oggioni<sup>†</sup>, Stephan Paredes\*, Keiji Matsumoto<sup>‡</sup>, Manish K. Tiwari<sup>¶</sup>, Dimos Poulikakos<sup>¶</sup> and Thomas Brunschwiler\*<sup>§</sup>

Ongoing Challenges for system packaging

### Cost

## -Technology Reuse

- Physical form factor

- Form factors change slowly

- Scale-in functional integration

- Signal bandwidth density

- Frequency per lane

- Voltage regulation (Power In)

- Regulation moves closer to load

- More effective decoupling capacitors

- Cooling (Power out)

#### Conclusions

- IT boundaries are becoming less clearly defined

- -Processor, Storage, Networking Integrated

- Systems

- -Cloud, Analytics, Mobile, Social, Security

- System Hardware

- Drives system capacity with cores and computing capacity

- -Drives interconnect bandwidth at processor, node, system and network level

- All electrical performance elements must be balanced

- -Bandwidth

- Power Distribution

- -Thermal

- Technology enables the innovation that systems provide, we must choose wisely.