# Industry Trends 2016: A Few Observations....

- · Industry is in an unprecedented "era of change" as our industry matures

- Trend in mergers and acquisitions will continue this year

- This year will be a "strange" year

- . PC industry unit volumes remain flat

- Despite IoT "hype" mobile devices such as smartphones still driving unit volumes in semiconductor industry

- · Thin products are driving thin package solutions

- Must meet steep ramp with high volume

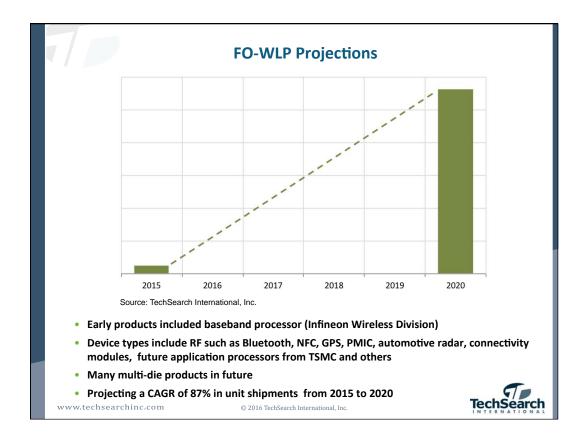

- Trend in WLP use for mobile products such as smartphones continues

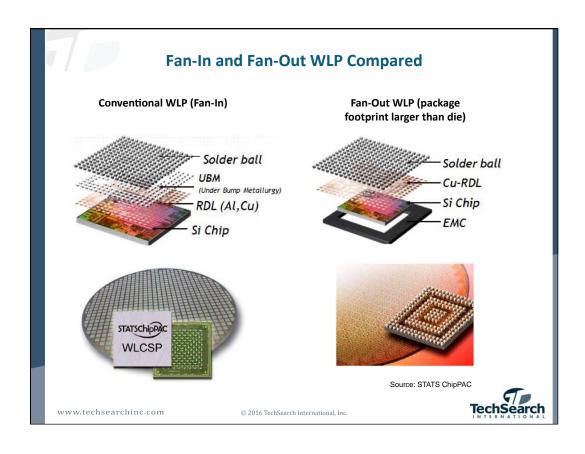

- Conventional WLP

- FO-WLP

- . Growth in the use of flip chip packages continues, with quest for lower cost solutions

- . Wire bond still workhorse of industry, but higher growth rates in FC and WLP

- · Moore's Law proving more difficult to maintain

- Next technology nodes become more expensive

- Rely on semiconductor packaging to achieve lower system cost

- Driving multi-die and system-in-package (SiP) solutions

- · The road ahead requires new developments to lower packaging cost

- Adoption of new technologies to achieve cost/performance trade-off

www.techsearchinc.com

© 2016 TechSearch International, Inc

### **Drivers for WLP**

- Major applications for WLP......

- Smartphones (highest volume application)

- Digital cameras and camcorders

- Laptops and tablets

- Medical

- Automotive

- Wearable electronics such as watch

- WLP meets system packaging needs

- Small form factor

- Need for low profile packages

- Lower cost (less material)

- Form Factor is key

- Low profile

- Limited space on PCB

Source: TPSS.

TechSearch

www.techsearchinc.com

© 2016 TechSearch International. In

### It's Not Just iPhones with Lots of WLPs.....

- Samsung smartphones with WLPs

- 6 years ago, no WLPs

- Galaxy 6S has 13 WLPs on main board

- · Japanese domestic smartphones

- Sony Xperia Z4 has 13 WLPs

- Sharp Aquos Zeta has 13 WLPs

- China handset makers increasingly using WLPs

- Huawei Asend G620S has 4 WLPs

- ZTE Goophone has 3 WLPs

- Even low-end OPPO Joy has one....

- On average 5 to 7 WLPs per smartphone and the numbers continue to increase.....

www.techsearchinc.com

© 2016 TechSearch International, Inc

# **Conventional WLP Applications**

- Conventional WLPs for many device types (analog, digital, sensor, discrete)

- Power management IC (PMIC)

- Audio CODEC

- RF

- IPD, ESD protection, filter

- LED driver

- Electronic compass

- Controller

- MOSFET

- CMOS image sensors

- Ambient light sensors

- EEPROM

- CAGR of almost 9% from 2014 to 2019

- Conventional WLPs trends

- Highest I/O count 309 (Fujitsu power management IC)

- Largest body size in HVM Qualcomm PMIC 6.5 mm x 6.5 mmx 0.71 mm, 0.4mm pitch

- Increasing number of 0.4mm pitch parts, some 0.35mm pitch

- Fine pitch parts need high-density PCB to route signals

www.techsearchinc.com

© 2016 TechSearch International, Inc

Source: ASE.

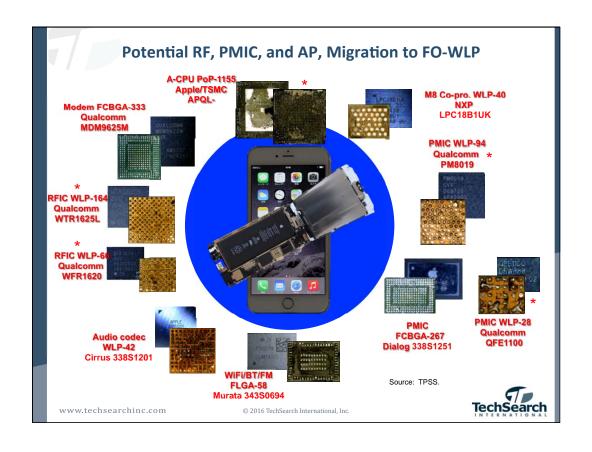

### **Drivers for FO-WLP**

- Smaller form factor, lower profile package: similar to conventional WLP in profile (can be ≤0.4 mm)

- Thinner than flip chip package (no substrate)

- Can enable a low-profile PoP solution as large as 15mm x 15mm body

- Support increased I/O density

- Fine L/S (10/10μm)

- Roadmaps for <5/5μm L/S, future 2/2μm L/S

- Allows use of WLP with advanced semiconductor technology nodes with die shrinks

- With increased I/O and smaller die can't "fan-in" using conventional WLP

- Smaller diameter balls and ball pitch ≤0.3mm board level reliability issues (Qualcomm studies)

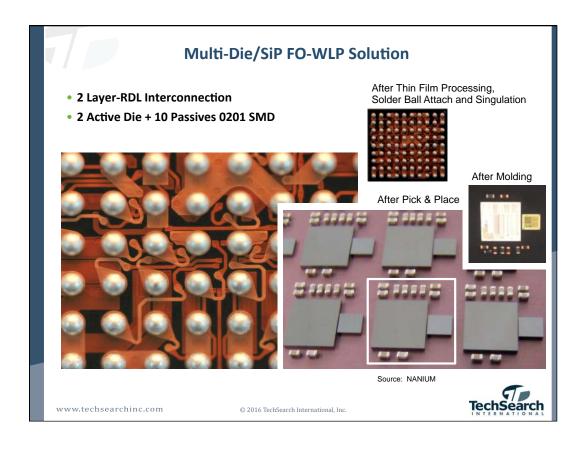

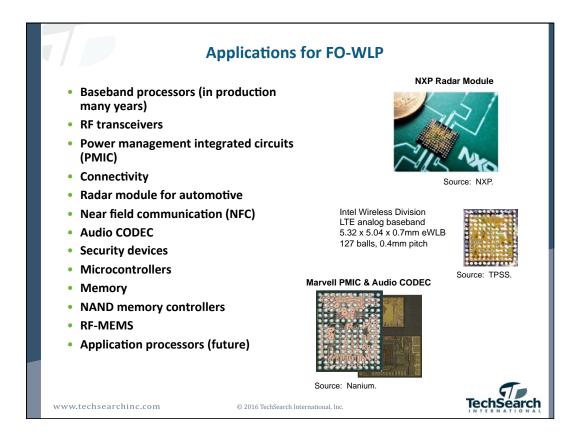

- Split die package or multi-die package/SiP

- Multiple die in package possible

- Die fabricated from different technology nodes can be assembled in a single package

- Can integrate passives

- **Excellent electrical and thermal performance**

- Excellent high temperature warpage performance

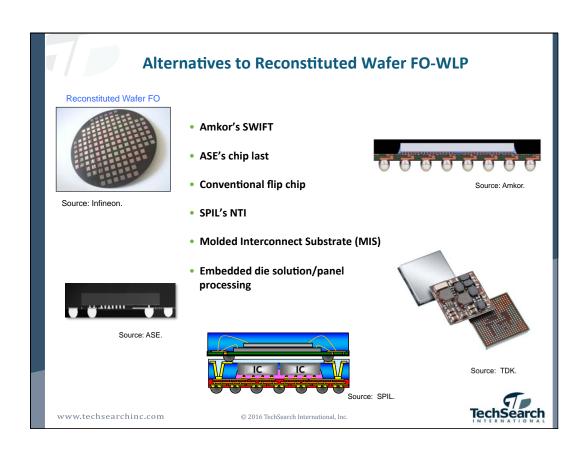

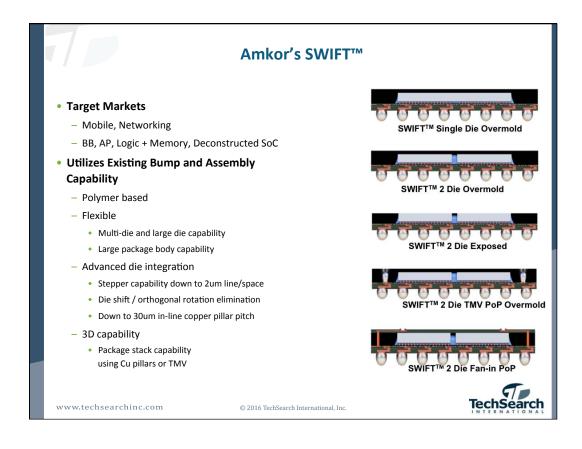

## **Application Processor Packaging Trends** • Thinner package and smaller footprint Today's PoP (1.0mm) - Today 1.0mm height requirement Future ≤0.8 mm · 3D IC with TSV provides the ultimate in package height reduction, but continues to be pushed out Silicon interposers too expensive for many mobile products PoP in high-end smartphones - Option 1: Continue with FC on thin substrate FO-WLP as Bottom PoP (<0.8mm) Option 2: Embedded AP in bottom laminate substrate Option 3: Fan-out WLP with application processor as bottom package Option 4: Some new format (SWIFT, NTI, etc.) FO-WLP AP in bottom PoP - Low profile - High routing density - System integration with competitive cost www.techsearchinc.com © 2016 TechSearch International, Inc

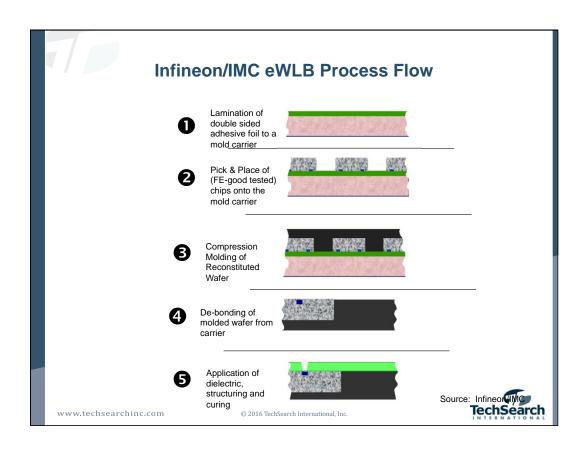

# Why is FO-WLP A Disruptive Technology?

#### No substrate

- Thin-film metallization used for substrate (can go below 5μm L/S)

- No traditional laminate substrate

- No underfill

- Most application processors had been using laminate substrate with flip chip bump interconnect

- Removes substrate supplier as design partner

### Infrastructure changes

- All packaging can take place at the foundry

- Assembly can also take place at OSAT but uses a non-traditional OSAT assembly line

- Requires IC/package co-design

Source: Nanium.

www.techsearchinc.com

© 2016 TechSearch International. In

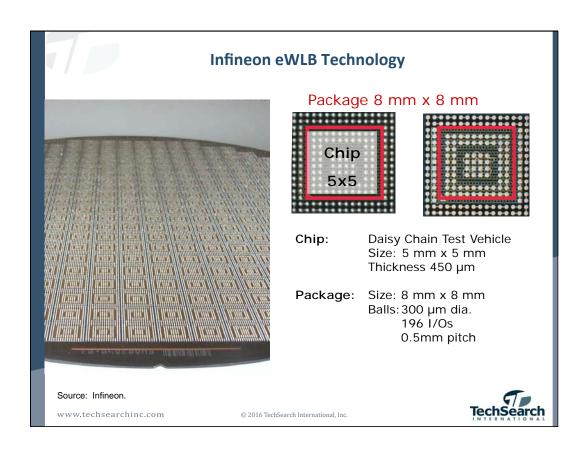

# **FO-WLP Suppliers Status**

- Amkor Technology redeploying FO-WLP with new 300mm line (eWLB) in K4

- ADL Engineering 200mm pilot line in Taiwan

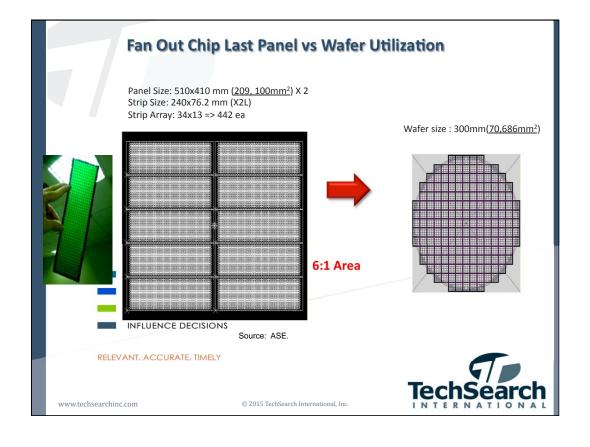

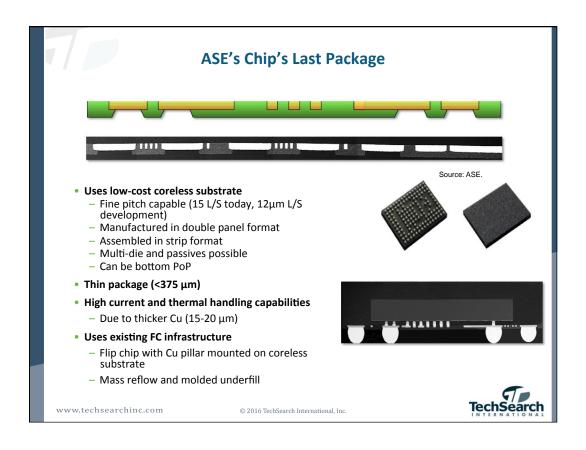

- ASE license for Infineon's eWLB with 300mm in Taiwan, also offers "chip last" panel version

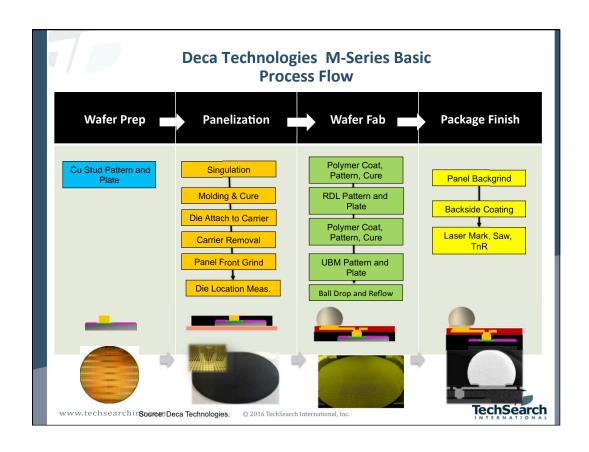

- Deca Technologies (300mm "panel" format)

- NANIUM (300mm wafer) license for Infineon's eWLB

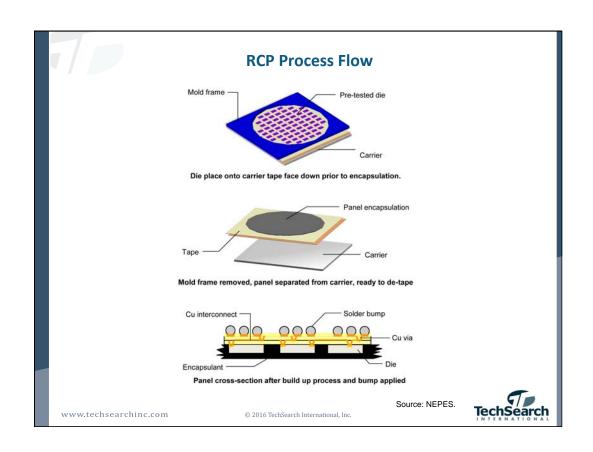

- NEPES (300mm line in Korea)

- PowerTech Technology (300mm line future, R&D on panel)

- SPIL (300mm wafer)

- STS Semiconductor and Telecommunications (300mm production line in qualification)

- STATS ChipPAC (300mm wafer) purchased by JCET, license for Infineon's eWLB

- Samsung (internal production expected)

- TSMC (300mm wafer InFO process)

- All China OSATs will offer versions in future

- YOUR NAME HERE

www.techsearchinc.com

© 2016 TechSearch International, Inc.

### **Conclusions**

- Mobile products require low profile packages that meet performance needs

- Fan-in WLP

- FO-WLP

- Shrinking technology nodes => shrinking die => less area for I/O (if pitch does not shrink)

- Drives migration from Fan-In to Fan-Out WLP

- Single and multi-die packages with FO-WLP

- FO-WLP is a disruptive technology

- Introduction with have impact similar to Intel's introduction of Cu pillar bump

- Demand for low-cost packaging solutions drives adoption of new package designs and formats

- New chip last packages?

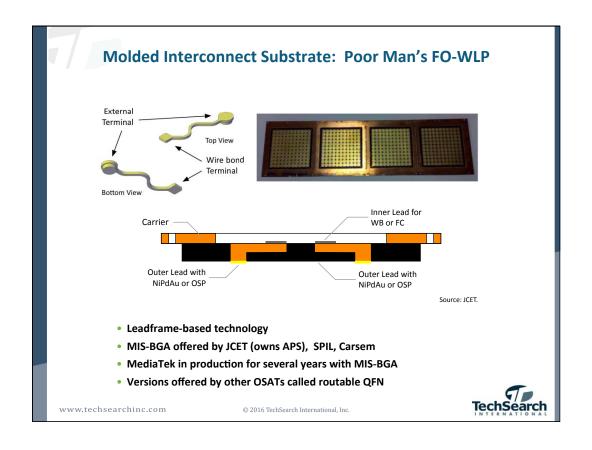

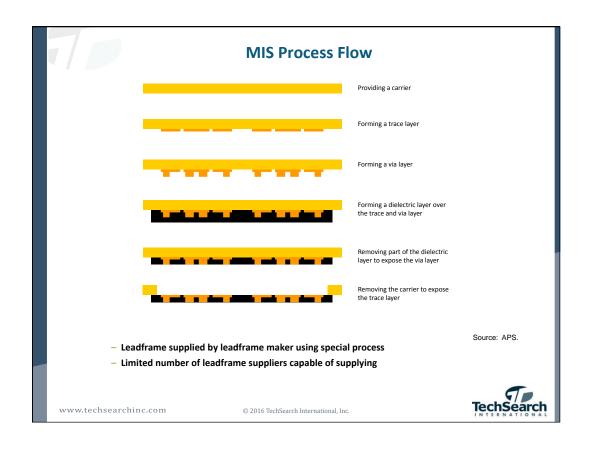

- MIS on modified leadframe?

- Panel-level processing?

- In the year of the Monkey, one must be swift and agile.......

TechSearch

www.techsearchinc.com

© 2016 TechSearch International, Inc.

# Thank you!

TechSearch International, Inc.

4801 Spicewood Springs Road, Suite 150

Austin, Texas 78759 USA

+1.512.372.8887

tsi@techsearchinc.com

RELEVANT, ACCURATE, TIMELY

www.techsearchinc.com

© 2015 TechSearch International, In