## "Trends, Transitions, and Inflection Points in Semiconductor Packaging"

**February 14, 2018**

Dan Tracy, Sr. Director SEMI Industry Research & Statistics

#### Outline

- Quick 2017 Overview

- · Semiconductor Industry Outlook and Market Drivers

- Packaging Market Trends

- Business and Technology

- Material Segments

- China

- Summary

#### 2017 Overview

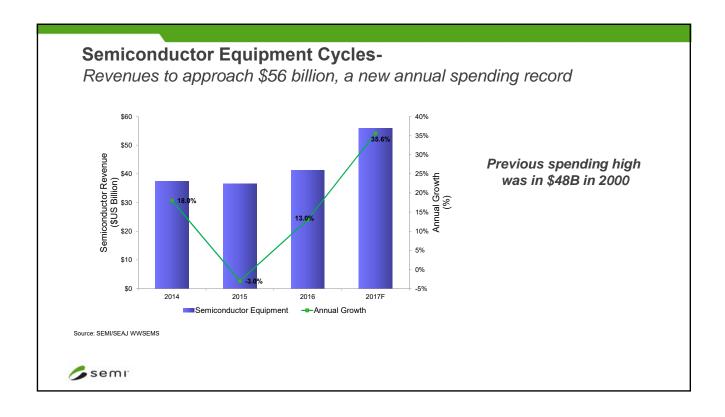

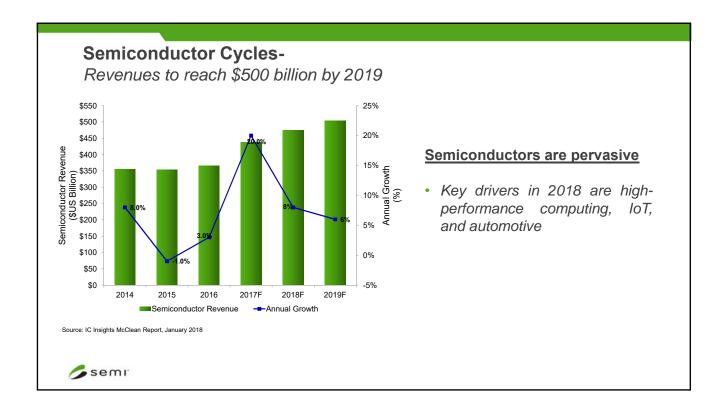

#### 2017- A Record Setting Year

- 2017 is a record setting year for the industry

- Semiconductor sales: **>\$400B** for the first time

- Fabless sales reach the \$100B mark for the first time

- Investments

- All-time high for CAPEX by single company (Samsung)

- Equipment spending in Korea will smash previous regional spending record

- Worldwide equipment billings: ~\$56B

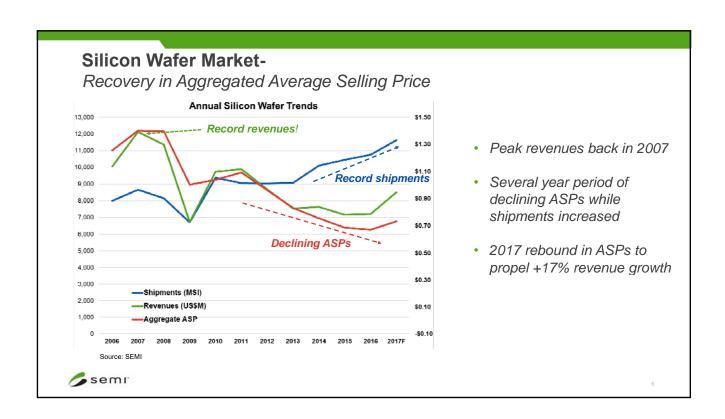

- Silicon shipments

- · Also, a rebound in wafer pricing

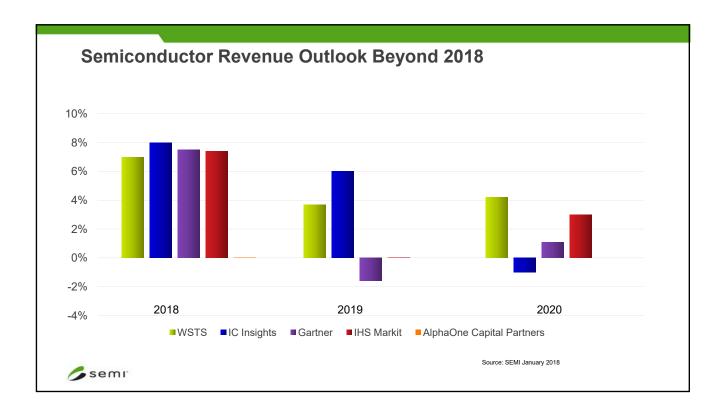

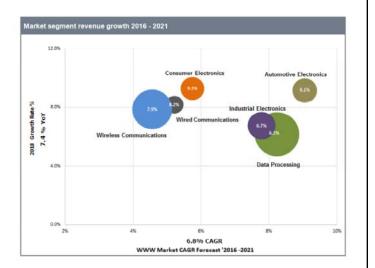

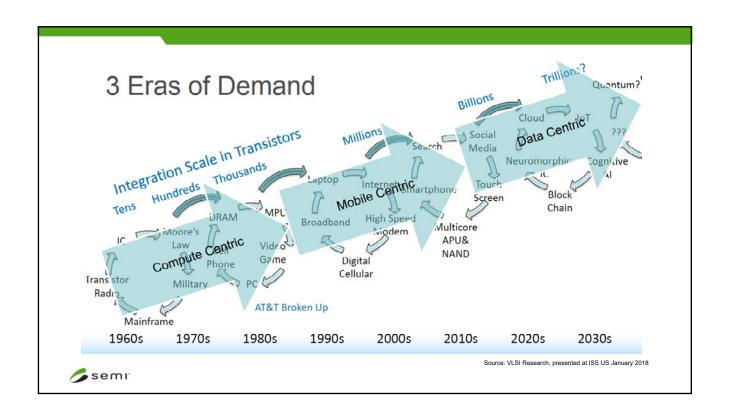

# Semiconductor Industry Outlook and Market Drivers

#### **Industry Trends and Growth Drivers**

- Data Centers

- Big Digital SoCs

- Storage Solid State Memory

- Gateways

- Data Collection Hubs

- IoT Nodes

- Sensors

- Actuators

- Imagers

- Transmitters

Source: Mentor, A Siemens Business, presented at ISS US January 2018

Source: IHS Markit, presented at ISS US January 2018

# Packaging Market Trends

#### **Business and Technology**

∕ semi

🥏 semi

#### **Packaging Trends and Transitions**

- Wire bond is not dead, but industry evolving to increased packaging and assembly at the wafer level

- · Memory inflection point:

- Leadframe to organic substrate packages

- WB to FC

- FO-WLP is a disruptive technology

- Traditional model:

- Wafer is processed in fab then sent to assembly facility for singulation, assembly, and test

- · New model:

- Some wafers stay at the foundry for packaging and assembly

- Some OSATs install wafer processing ("like") equipment to create package on the wafer

Image Source: TechSearch International

© 2018 TechSearch International, Inc.

#### **Emergence of Outsource Packaging**

#### Today:

- >50+% of packaging revenues

- · Leading new packaging development...Cu pillar,

- FO-WLP, SiP, and more...

#### 2005:

- ~40% of packaging revenues

- Fabless companies grow; IDMs shift to outsourcing

#### 1995:

- ~18% of packaging revenues

- · Emergence of leading Taiwanese and

- Korean OSAT companies

#### 1985:

- ~5% of packaging revenues

- · Manufacturing focus in the Philippines

- PDIP & Transistors

Source: Gartner and SEMI

Image Source: Siliconware

#### **Packaging and Assembly Trends**

- · SiP remains a hot topic

- Drivers remain the same...miniaturization #1

- Heterogeneous integration drives this into high-performance applications

- Silicon interposer finally moved into volume production (but small volumes)

- FPGA with homogeneous and heterogeneous solution

- GPU + stacked memory

- Network systems

- · Artificial intelligence

- Still waiting for the big TSV market, but we have production volume

- DRAM with TSVs for servers

- HMC

- HBM

Image Source: Xilinx

Image Source: SK Hynix

© 2018 TechSearch International, Inc.

#### **Trends Driving Heterogeneous Integration**

- As the industry moves to the next silicon nodes (10nm, 7nm, etc.) new packaging solutions are need to achieve the economic advantages that were previously met with silicon scaling

- Heterogeneous integration is considered the answer and is taking various forms:

- Silicon interposers

- Alternatives such as Intel's EMIB or Fan-out on Substrate

- Future organic interposers

Requires collaboration across the entire supply chain

© 2018 TechSearch International, Inc.

#### **Growing Number of FO-WLP Applications**

- Baseband processors

- Application processors

- RF transceivers, switches, etc.

- Power management integrated circuits (PMIC)

- Audio CODECs

- Connectivity modules

- · Radar modules (77GHz) for automotive

- Microcontrollers

- Sensors

- Logic + memory for data centers and cloud servers

© 2018 TechSearch International, Inc.

Audio CODEC (4.25mm x 3.9 mm)

Image Source: TechInsights

#### **Materials**

#### **Laminate Substrates**

- ~\$7B market

- Stable supply base

- Wire bond CSP and BGA are declining; while flip chip CSP and BGA are seeing some increase

- · Flat growth in PC; slowing growth in mobile

- Some substrate suppliers have reduced production with the transition to FO-WLP

- Some customers relaxing extensive price pressure on suppliers

- China suppliers increasing capabilities

Image Source: Unimicron

Source: SEMI/TechSearch International, Global Semiconductor Packaging Materials Outlook (to be published 1Q 2018)

#### Wafer Level Dielectrics

- ~\$200M market currently

- Numerous suppliers currently in the market

- New RDL formulations still in development, especially for multi-layer applications

- Low cure temperatures a must

- WLP dielectrics with good adhesion to metal (Cu) layers and epoxy (in the case of FO-WLP reconstituted wafer) without delamination

- Low stress WLP dielectric (to match the CTE of the chip) and/or low modulus (for less wafer bow)

Source: SEMI/TechSearch International, Global Semiconductor Packaging Materials Outlook (to be published 1Q 2018)

#### **Mold Compounds**

- ~\$1.3B market

- Stable supply base with Japanese suppliers maintaining strong market position

- Formulations to pass Moisture Sensitivity Level 1 (MSL1) for small packages.

- Critical for board-level reliability

- Need smaller fillers and narrower particle size distribution for better warpage control. Especially critical in FOWLP.

- Clear compounds for optical devices: limited material available as warpage and adhesion issues need to be addressed.

Image Source: Kyocera Chemical

Image Source: Towa Corp.

Source: SEMI/TechSearch International, Global Semiconductor Packaging Materials Outlook (to be published 1Q 2018)

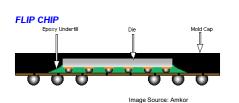

#### Underfill

- >\$200M market for flip chip (higher if under package is included)

- · Stable supply base led by Japanese suppliers

- Capillary applications challenged with void-free filling for finer pitched Cu pillar

- Flip chip dimensions:

| Flip Chip | Key Features  | Current         | 2021 Estimate  |

|-----------|---------------|-----------------|----------------|

| Cu Pillar | Bump Pitch    | 100 μm to 50 μm | 40 μm to 30 μm |

|           | Bump Diameter | 40 μm           | 25 μm          |

Affordable Non-Conductive Film (NCF) underfill with higher throughput

Source: SEMI/TechSearch International, Global Semiconductor Packaging Materials Outlook (to be published 1Q 2018)

13

#### Leadframes

- ~\$3.1B market

- · Copper alloy supply constraints affecting lead-times

- Growing etch capacity and capabilities for surface treatments

- · Routable QFN/MIS to increase I/O count

- Currently limited sources/supply

- Pre-molded QFN is a new technology

- Improved handling, though needs to provide attractive cost-down benefit

- RF and analog expected to switch from QFN to WLCSP

Image Source: Shinko

Image Source: Chang Wah Technology Co.

Source: SEMI/TechSearch International, Global Semiconductor Packaging Materials Outlook (to be published 1Q 2018)

semi

www.cpmt.org/scv/

#### Other Packaging Material Issues and Needs

| Material Segment   | Need/Issues                                                                                                                                                                                                                                                                                                                                               |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Other Issue/Topics | Plating     Higher throughput for Cu pillar                                                                                                                                                                                                                                                                                                               |

|                    | <ul> <li>Panel Fan-out</li> <li>Driven by desire for a lower cost solution</li> <li>Need big product volume to drive the economics</li> <li>Need standards (equipment companies waiting for standards to "fully" support initiatives)</li> <li>&lt;10μm/10μm lines and spaces may be difficult to achieve with multiple layers with high yield</li> </ul> |

|                    | Dicing/Grinding  Dicing and Grinding for thin wafers: 80µm in production, developing 50µm, looking at 30um and below  Non-blade techniques need to get Cost of Ownership equal to blade processing  Sustainability  Sustainability—recycle and reuse—is a major issue. Also pertains to shipping                                                          |

|                    | and packing materials used for packaged devices                                                                                                                                                                                                                                                                                                           |

Source: SEMI/TechSearch International, Global Semiconductor Packaging Materials Outlook (to be published 1Q 2018)

### Semiconductor Packaging Materials Markets 4% Revenue Growth in 2017; 2% Growth Forecasted for 2018

2016 = \$19.1 billion

2017F 2018F Region \$US B \$US B China \$5.11 \$5.30 N. America/Europe 1.21 1.23 Japan 2.53 2.57 South Korea 2.26 2.35 SEA/ROW 4.50 4.45 Taiwan 4.24 4.29 Total \$19.8 \$20.2

Totals may not add due to rounding

Source: SEMI Materials Market Data Subscription, January 2018

#### China

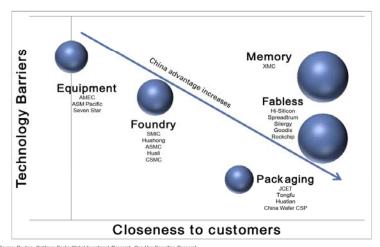

#### **China IC Industry Faces Challenges and Opportunities**

#### **Packaging Opportunities in China**

- Lowest barriers to success and is poised for growth and technical advancement

- · Closeness to customer

- Large electronics manufacturing base there

- Technology barriers

- Lower capex requirements (compared to wafer fabrication)

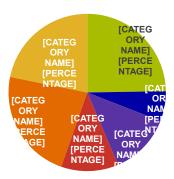

#### **China Packaging Market**

China is the largest market consuming packaging materials

#### 2017 Packaging Materials Regional Revenue Share

Source: SEMI Materials Market Data Subscription, January 2018

🏂 semi

/semi

- Packaging is a mature industry in China

- 45% of bonding wire shipments are to China

- 150+ package & assembly plants located in China

- 80+ OSAT Plants

- 17 Bumping Facilities

- China OSAT companies mainly focused on traditional packaging, though are increasing capabilities and offerings of advanced packaging solutions

| Category                                          | Company                                                        | Est. Market Share                                                                        |

|---------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Leadframes                                        | Kangqiang, Hualong, Trinity Sanjia,<br>Others                  | 11% Revenue Share WW Total ~30% Revenue Share of China Market                            |

| Substrates                                        | Shennan Circuits, Zhuhai Yueya,<br>AKM                         | N/A                                                                                      |

| Bonding Wire                                      | Doublink, Kangqiang, Yes/No, Youk<br>Wire, (Many, many) Others | <ul><li>10% Shipment Share WW Total</li><li>20% Shipment Share of China Market</li></ul> |

| Encapsulation Resins (including LED applications) | Sinopaco, HHCK, ANPIN Silicone,<br>BJKMT, Darbond, Others      | ~6% Revenue Share WW Total ~20% Revenue Share of China Market                            |

| Die Attach                                        | Darbond, Others                                                | N/A                                                                                      |

| Ceramic Packages                                  | Zhongwei, Yixing                                               | N/A                                                                                      |

#### **Summary**

- 2017 was record setting year for the industry

- · Record fab investments; All-time high for total equipment spending

- · Spending in Korea will smash previous regional spending record

- Significant packaging transitions underway as function of mobility, connectivity, and performance

- Need to address materials challenges pertaining to package performance and reliability, e.g. warpage, adhesion, interfacial/surface interactions, etc., for 3D, SiP, and Heterogenous Integration

- Packaging will continue to grow rapidly in China

- Domestic companies increasing capabilities; demand for locally produced materials to grow