# **Beyond Scaling**

# - Teaching the Old Dog some New Tricks!

Subramanian lyer, ssiyer@us.ibm.com

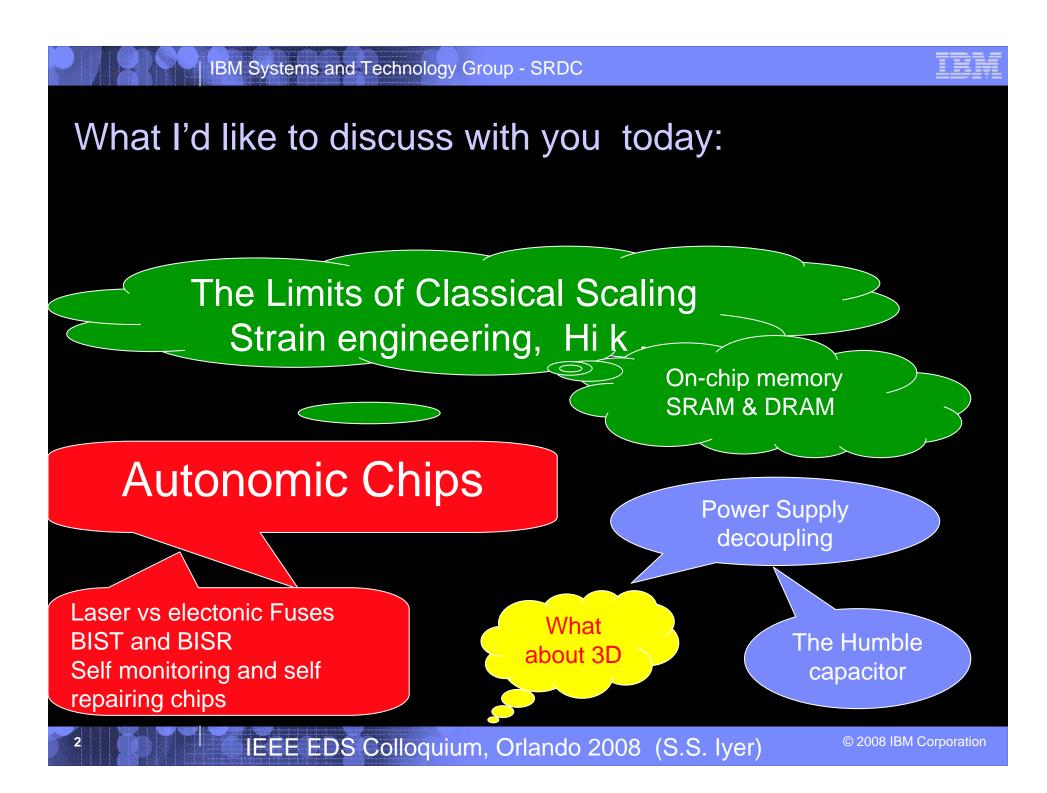

### What are these functions ?

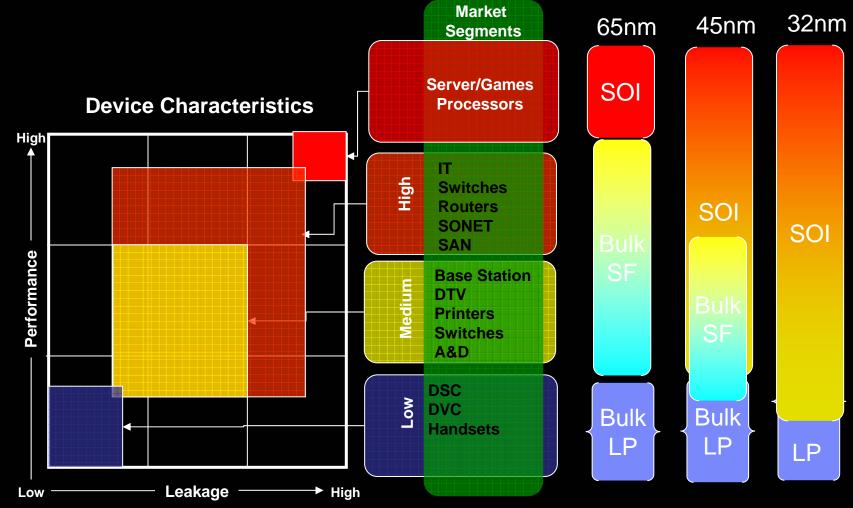

Customers need the flexibility to mix high performance and low leakage devices on the same die to optimize power and performance

IEEE EDS Colloquium, Orlando 2008 (S.S. lyer)

#### BM Systems and Technology Group - SRDC Where Are We Going with Scaling?

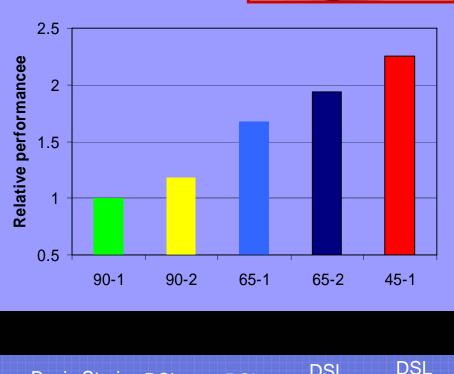

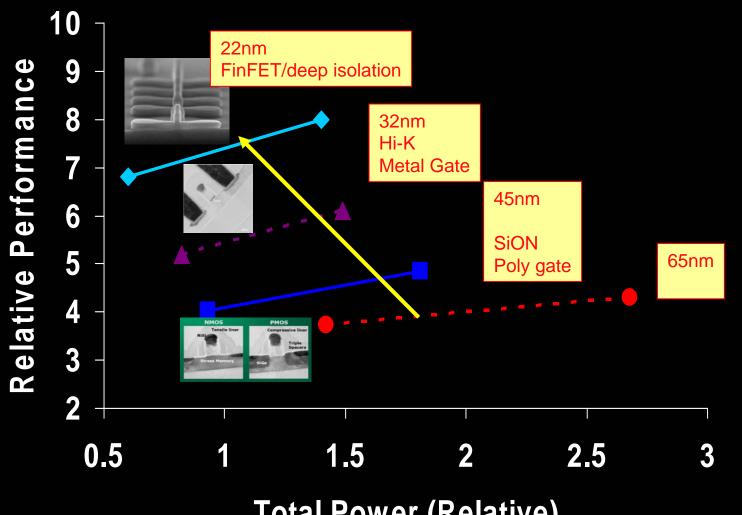

Historically constant field scaling came to a grinding halt at 90nm

- Stress engineering saved the day

- At 32nm HiK is a game changer

- It is designed to allow us to mix higher performance and low leakage on the same die at reasonable cost

At 22nm further innovations are called for

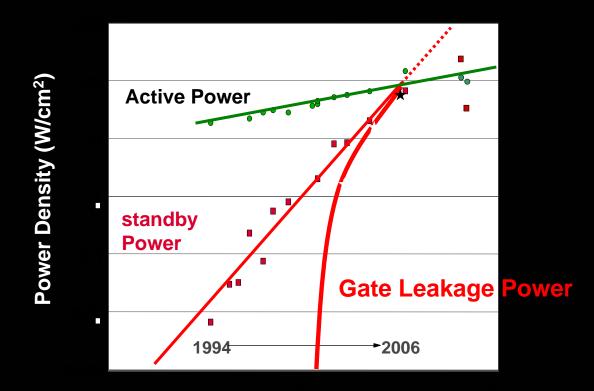

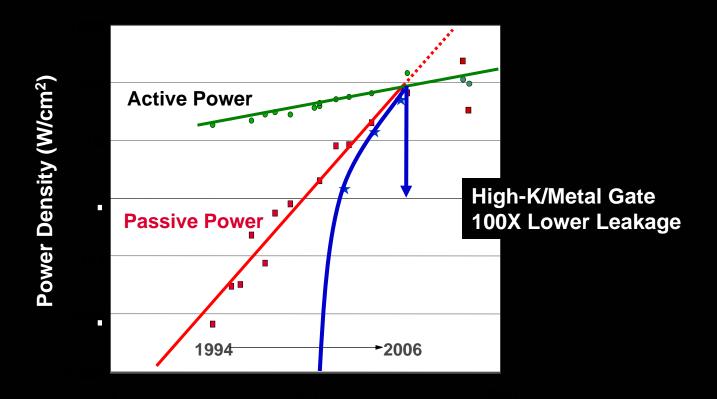

# Power Density Keeps Growing !

Gate Length (microns) ;)

- Non-scaling causing power density to increase

- Gate leakage power growing exponentially !!

# Strained Silicon: Achieving Relentless Performance Improvement

- Dual Stress Liner (DSL)

- Stress Memorization Technique (SMT)

- Embedded SiGe (eSiGe)

- Stress Proximity Technique (SPT)

DSL

SMT

Basic Strain DSL

DSL DSL SMT SMT eSiGe eSiGe SPT

#### IEEE EDS Colloquium, Orlando 2008 (S.S. Iyer)

#### High-K/MetaterGaterEmedatesPorter Reduction

Gate Length (microns) ;)

High-K/Metal Gate reduces gate leakage power by 100X

IEEE EDS Colloquium, Orlando 2008 (S.S. lyer)

# Where are Hi K materials when you need them ?

PM Systems and Tachnology Group

- Material Issues

- Compatible gate materialsBand edge vs Near Bandedge

- •Performance vs Power Tradeoffs

- Temperature Stability

- Integration Schemes

- Scaling channel length

ST

SOI

BOX

ST

PFF

NFFT

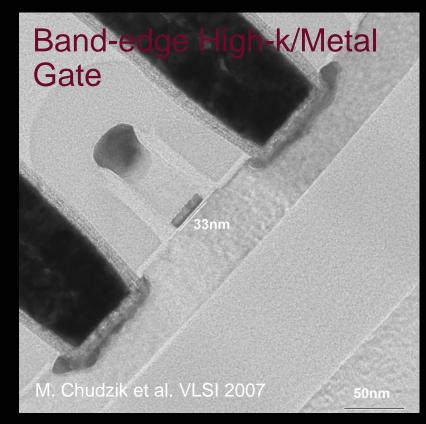

# Scaling to 32 nm and beyond

•TEM cross-sectional images of band-edge NFET HKMG stacks after full build showing a physical gate length of <40nm

10

•Hi K allows us to return to scaling as we knew it

•Lower leakage devices will be possible by adjusting threshold

•But there are better ways of adjusting threshold

•So we will be able to offer both high performance as well as low leakage devices with a single gate dielectric without suffering from gate leakage limitations

# But you must be able to scale the channel length !!

IEEE EDS Colloquium, Orlando 2008 (S.S. lyer)

#### Life antexstats anonechnology Group - SRDC

11

Total Power (Relative)

IEEE EDS Colloquium, Orlando 2008 (S.S. lyer)

# Key Issues Facing our Industry

12

- Scaling for performance is getting more difficult and very expensive

- Chip Power both standby and active are getting to be un-manageable

- Manufacturing cost is becoming huge while more and more parts are being commoditized

- Technology development is getting very expensive

# Net: Value needs to come from system concepts applied to ICs

# Going beyond Scaling and New Materials

- Scaling, strain engineering, and improved materials will continue to improve performance, though at diminishing rates and certainly with diminishing returns

- A combination of voltage supply reduction, power budget constraints and design IP migration suggest that the days of dramatic raw performance gains are over

- Performance must come from elsewhere

15

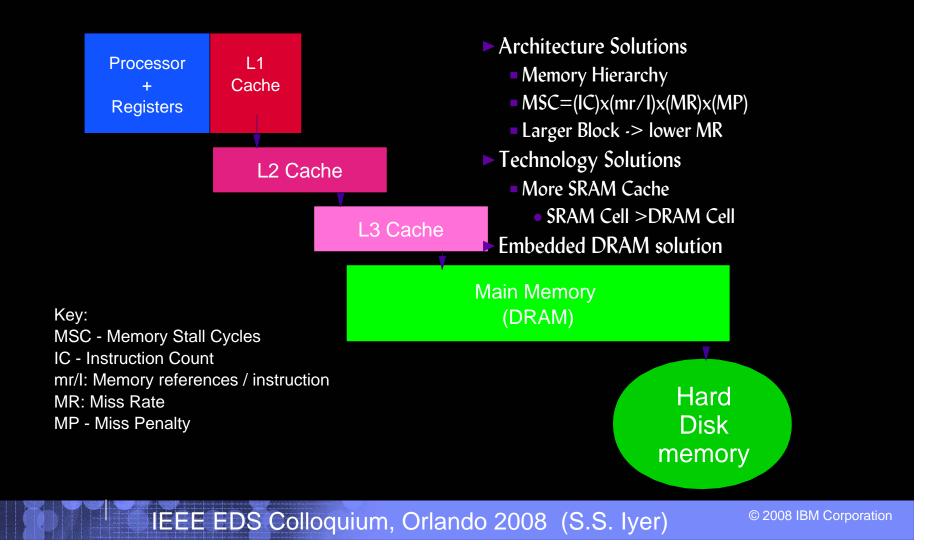

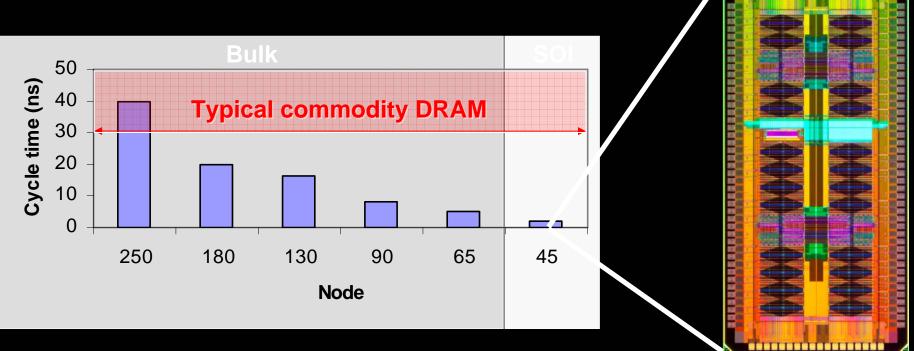

### Memory Hierarchy in a Modern Processor

At the system level, you never have enough memory!

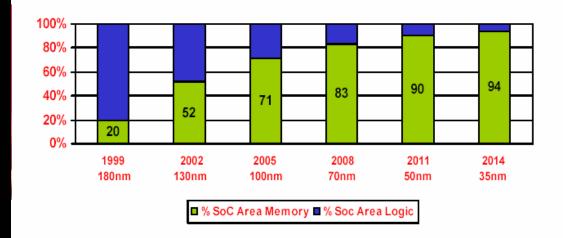

How do you integrate large amounts of dense memory on chip ?

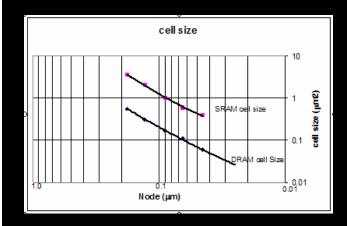

DRAM cells are 6X smaller than SRAM cells about 3.5X as dense / Mb And about half as fast

16

Integrate DRAMs on a logic chip additionally they Save power Have 10<sup>4</sup> lower SER and are more stable

© 2008 IES APPTERS

# The SRAM conundrum

- SRAMs are not aging with dignity

- Vmin stability due to

- Dopant fluctuation

- Gate oxide leakage

- Solutions

- Slow down scaling of both area and voltage

- Multiple cells with unique devices and layouts

- Power

17

Soft Error Rate continues to rise

C.

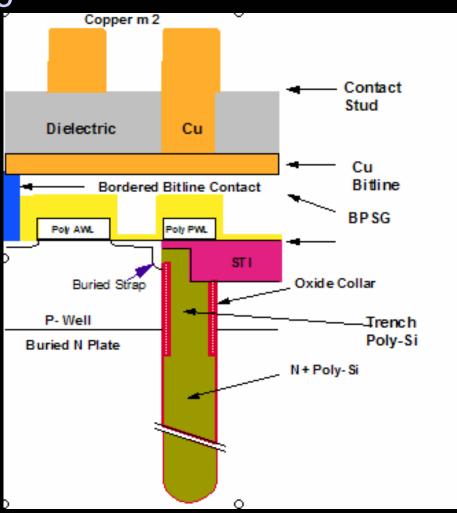

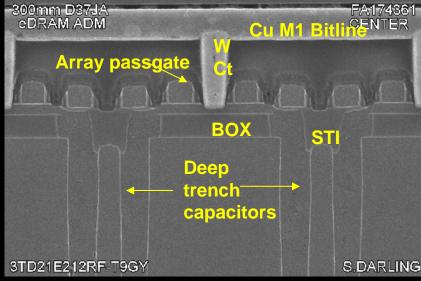

# Integrating DRAM and Logic

Integrate with Logic without impacting logic Performance, Reliability or Yields

•The Deep Trench process is intrinsically logic friendly

•Capacitor fabricated first

•No perturbation of the remaining logic flow

Significant Process & Test knowhow in DRAMs using deep trench technology

18

Over five generations, embedded DRAM has adapted to logic technology resulting In simpler processes and significantly higher cell performance

IEEE EDS Colloquium, Orlando 2008 (S.S. lyer)

IEEE EDS Colloquium, Orlando 2008 (S.S. lyer)

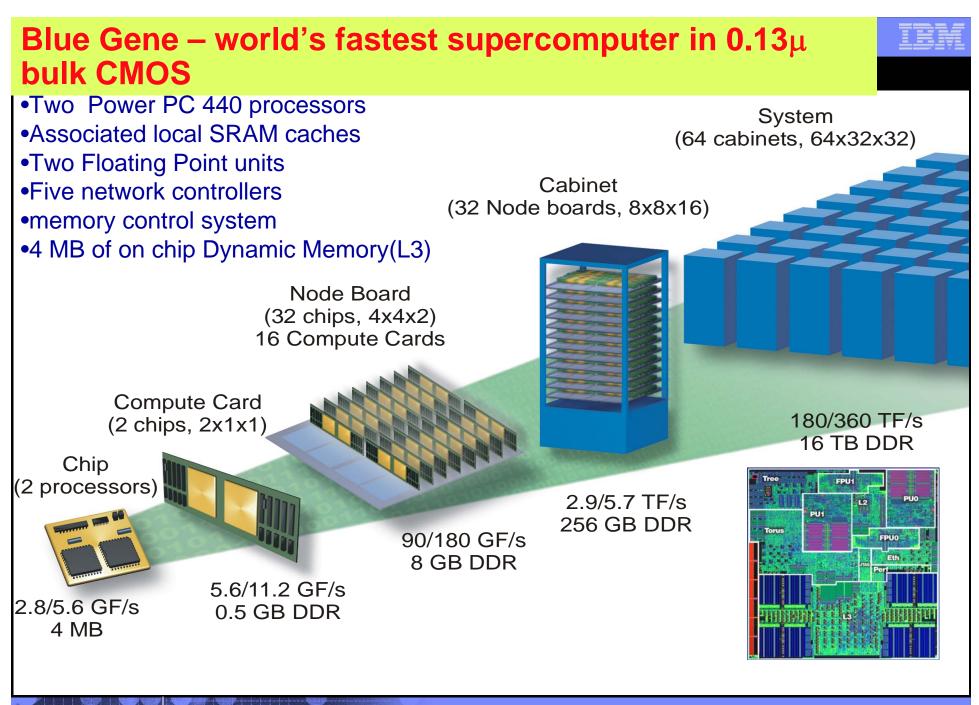

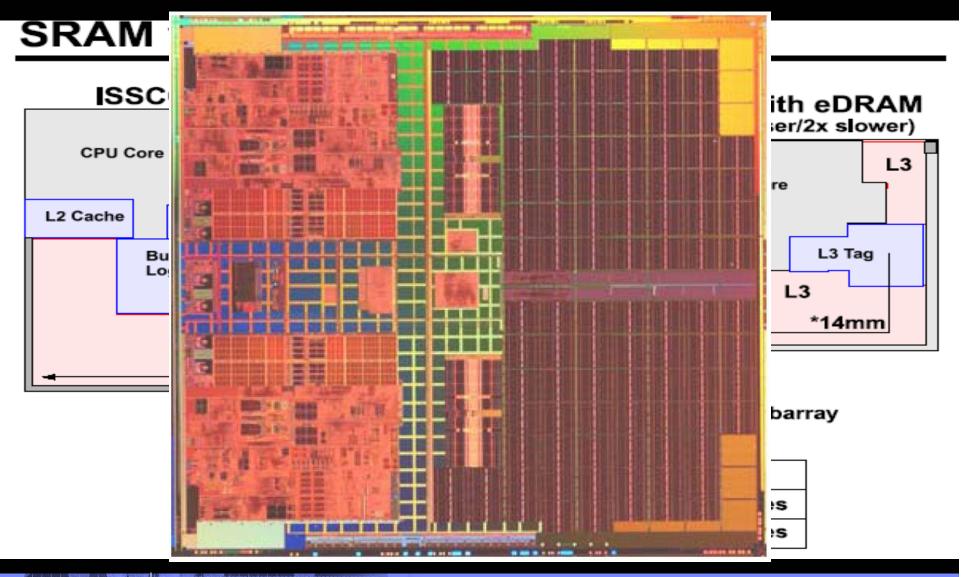

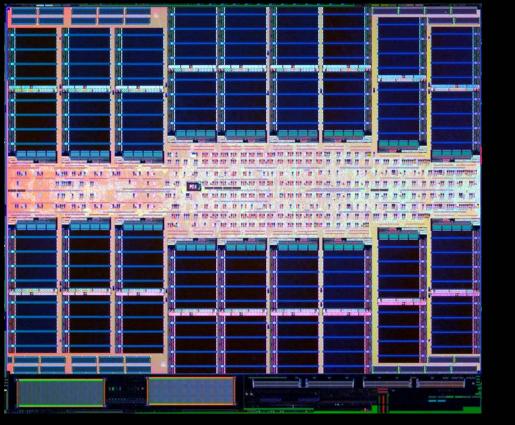

# Power 5 – L3 cache

- 430 Million Transistors... Largest ASIC Chip Ever Produced

- 344Mb of L3 Memory per Die

- 4x to 6x larger than SRAMs used by competitors

- Enables a 50% improvement in System Performance

"We consider IBM's reworking of the Level 3 cache design to be one of the top design wins in Power5."

#### IBM Systems and Technology Group - SRDC

# Case Study: hypothetical processor chip w/ eDRAM

IEEE EDS Colloquium, Orlando 2008 (S.S. lyer)

Scaling: Introduction of DRAM is equivalent to scaling (memory) *additional* two generations

DRAM introduction allows for a 0.28X scaling of memory block size at the time of introduction in addition to the assumed 0.7 scaling i.e. total scaling of 0.17

Scaling: Introduction of DRAM is equivalent to scaling (memory) *additional* two generations

DRAM introduction allows for a 0.28X scaling of memory block size at the time of introduction in addition to the assumed 0.6 scaling i.e. total scaling of 0.17

# Going forward

The next step is integration with the processor

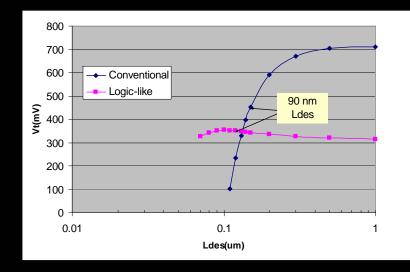

# What are the challenges ? Scaling and performance

# What is the approach

#### Power 4,5, 6 MCM

#### P5 CPU (SOI)

#### 36MB eDRAM L3 cache (Bulk)

# Performance eDRAM

- 70% of performance is gated by logic performance

Address Decoding functions

Row system Logic

Sensing circuits

- 30% of performance dictated by cell (writeback)

- Subarray architecture plays an overall role in optimizing performance-area-power tradeoff

- Logic based technologies comeout ahead on all fronts

# Performance eDRAM

- 70% of performance is gated by logic performance

Address Decoding functions

Row system Logic

Sensing circuits

- 30% of performance dictated by cell (writeback)

- Subarray architecture plays an overall role in optimizing performance-area-power tradeoff

- Logic based technologies comeout ahead on all fronts

| IBM Systems and Technology Group - SRDC

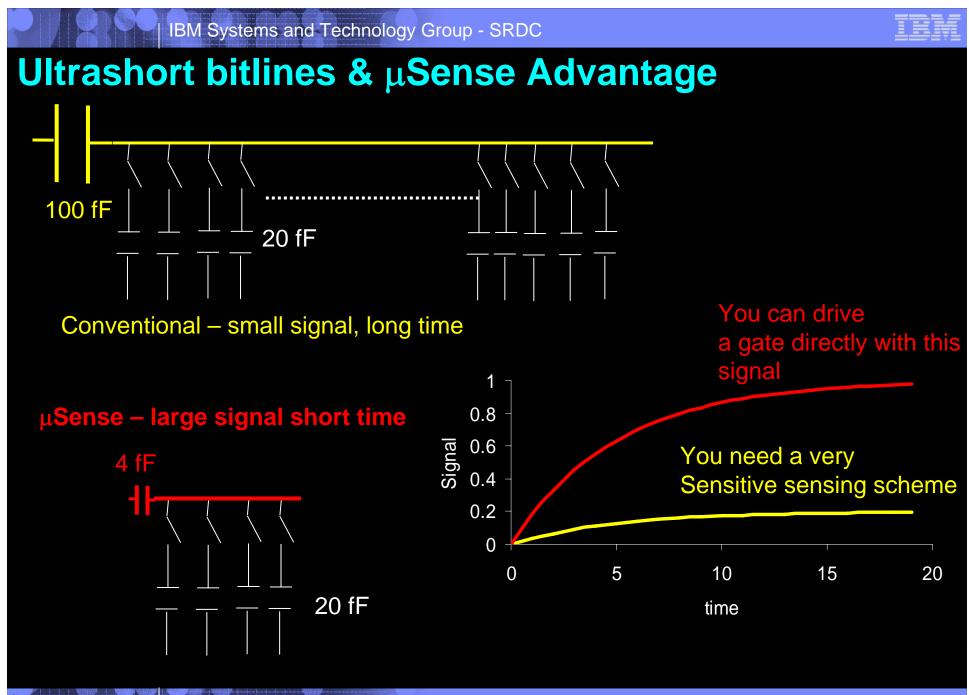

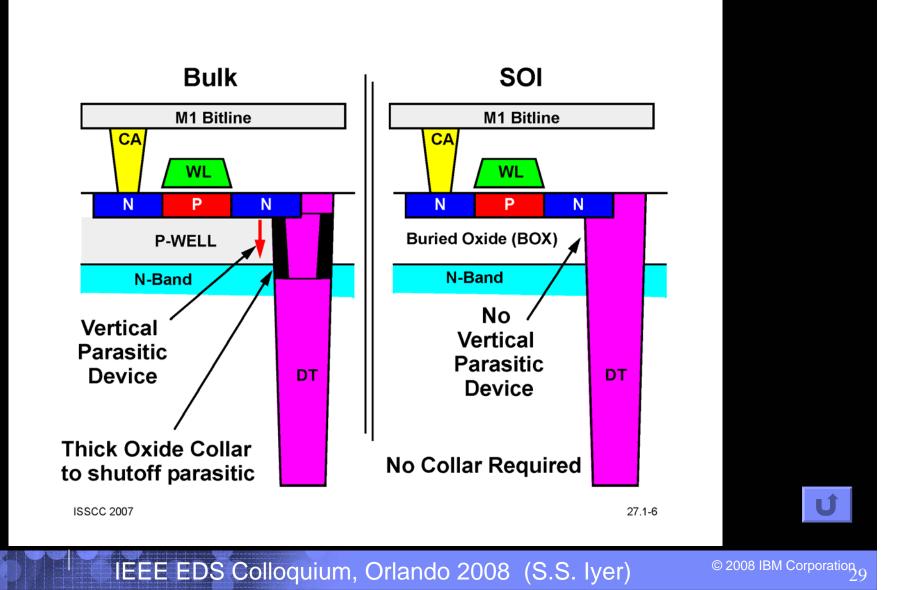

# Technology Innovation – Development of SOI DRAM cell • Technology:

Use the Buried oxide to simplify the process & reduce parasitics – half the cost of bulk eDRAM

Scale the pass transistor for higher performance

### Design

Address retention through concurrent refresh

Ultra short bitlines with direct sense architecture

IEEE EDS Colloquium, Orlando 2008 (S.S. lyer)

IEEE EDS Colloquium, Orlando 2008 (S.S. lyer)

# **Collar Process Elimination**

29

# SOI eDRAM

#### Advantages:

30

- SRAM like performance @ DRAM density, power and Soft Error Rate

- Full Logic compatibility

- -3.5X reduction in memory area (3 additional mask levels)

# L3 caches in servers

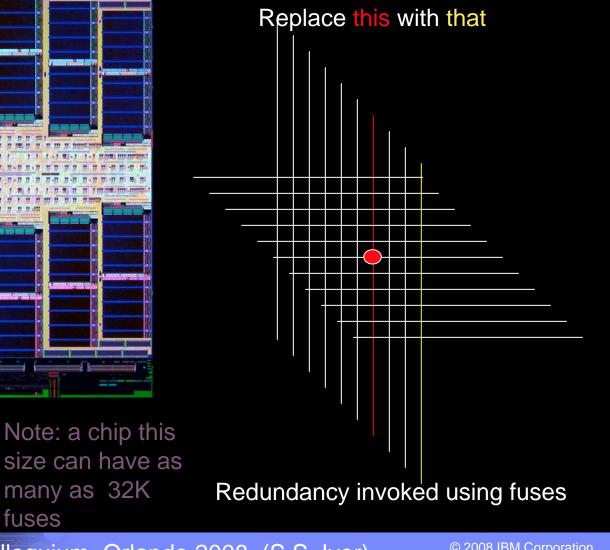

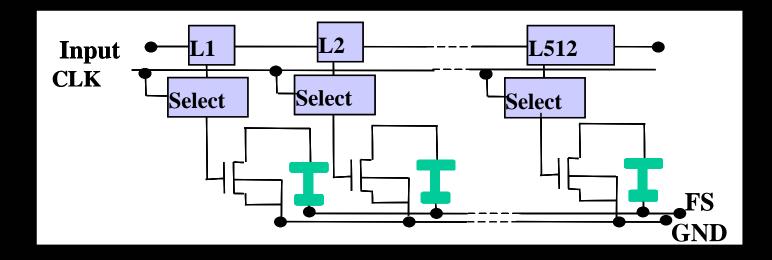

# Yielding Large Memory Chips Requires redundancy

L3 cache used in P5 344 Mb, 430M transistors Largest ASIC made at IBM

IEEE EDS Colloquium, Orlando 2008 (S.S. lyer)

Note: a chip this

many as 32K

fuses

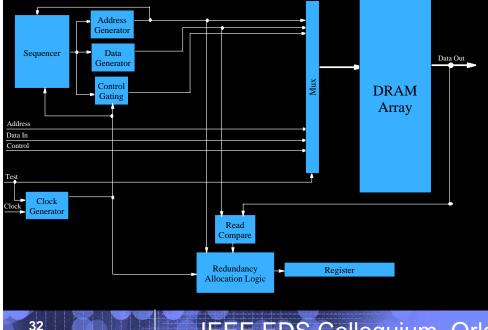

# Built-in Self Test and repair

# Key Enablers: BIST & Redundancy

- •Test at High speed

- •Very large bandwidth but very few pin-outs

•Solution : Since you have access to a high speed logic technology why not build the tester on-chip

•Next step : repair faulty chips!

#### **General Architecture of BIST**

- On chip test engine

- Hard & Soft Patterns

- Allocates Redundancy

- Tests redundant elements

- Generates Fuse String

#### IBM Systems and Technology Group - SRDC

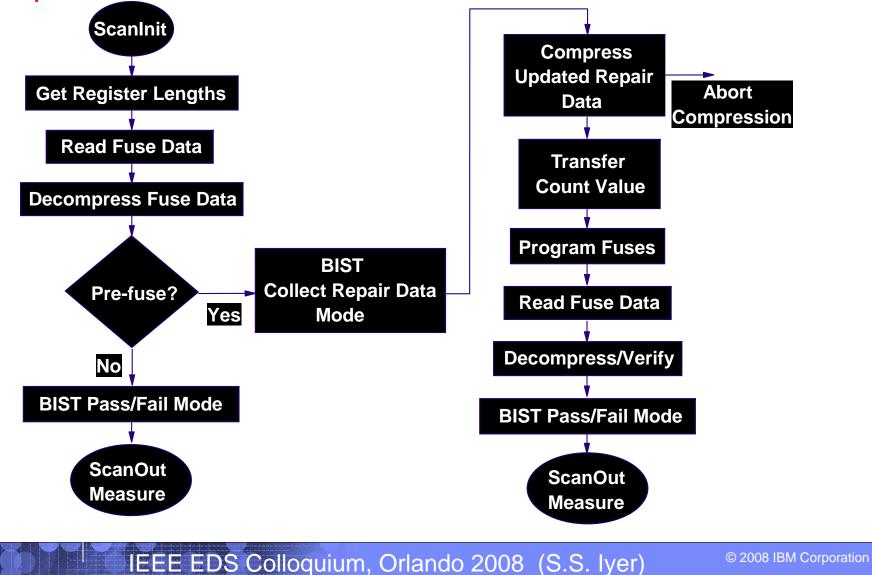

#### Test

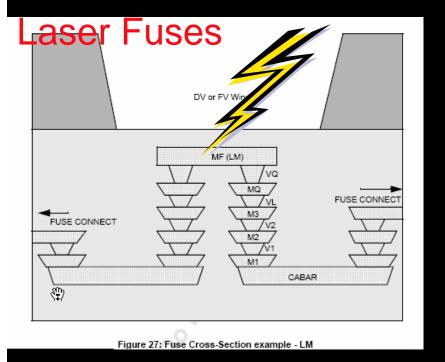

Determine repairs Move wafer to laser fuser Move repair data to laser fuse Blow laser fuses Take wafer back to tester Test again to verify Hope nothing break again ever! Do not scale & occupy too much space

- Block wiring and C4s

- Need to be exposed

- Can be blown only at wafer leve

- Need precise mechanical alignment

- Require a complex laser fuser

- Require multiple wafer handling and data manipulation

Net: Laser Fuses are a pain!!

#### IBM

# So, For ages DRAM yogis have pondered important questions:

What is the origin of the Universe ? Why are we doing DRAMs ?

How do you eliminate laser fuses ?

An electronic fuse would answer these questions

You could use circuits on the chip to program them!

Maybe you could even make the chip autonomic !!

# What are Autonomic Chips?

- Chips that can identify, test and repair themselves In the Fab at wafer level, In the package, In the field multiple times

- Repairs are self-consistent and contained on chip without need to access the rest of the system

They need to be hard-coded on the die

- Chips that can maximize their yield within a predefined parametric space

- Chips that ensure only authorized access

- Chips that identify hazardous operating conditions

Temperature, excessive device drifts .....

Chips that can track their history

35

# Achieving autonomic chips

36

- Need on-chip monitor to be aware of things going wrong

- Built-in-Self Test (BIST) engine (processor or dedicated)

- A self-repair methodology

- At the algorithmic level

- Aware of previous repairs

- Aware of available repair opportunities

- Decides on irreparability and functional disablement

- A method to execute the same permanently on chip

- A non-volatile memory element that is easy to implement (e.g., Fuse)

#### | IBM Systems and Technology Group - SRDC

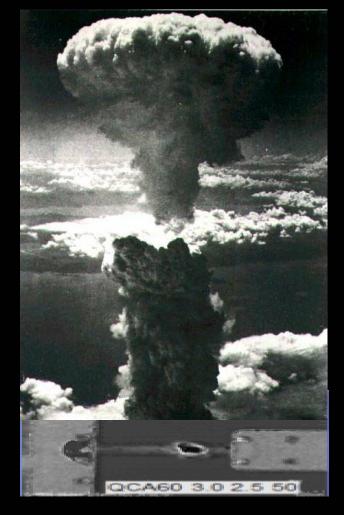

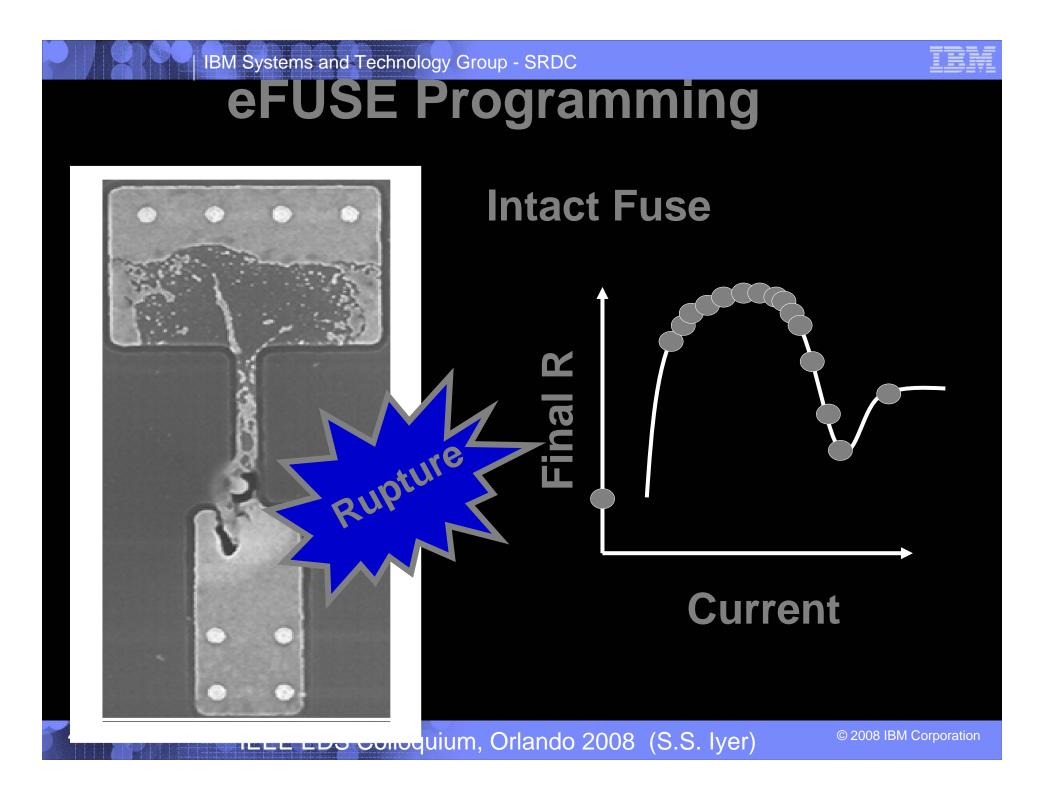

## **But seriously**

## Do you want this on your chip?

Fine Print: Explosion here has been somewhat exaggerated

37

Poly Si Fuse Programmed by rupture

IEEE EDS Colloquium, Orlando 2008 (S.S. lyer)

## The eFUSE Philosophy

# No new processes No New Masks No Technology Dev

No new materials

Technology Independent

38

Fuse must work even if die is marginal

Programming time should be short

Should be programmable on chip

Use design levels and Booleans to create Fuse link

Understand the physics of the blow mechanism

Design innovative circuits to program and sense the fuses

IEEE EDS Colloquium, Orlando 2008 (S.S. lyer)

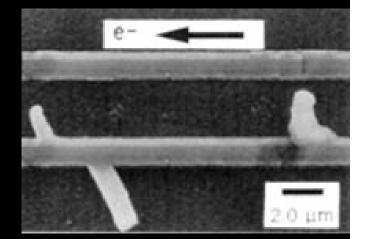

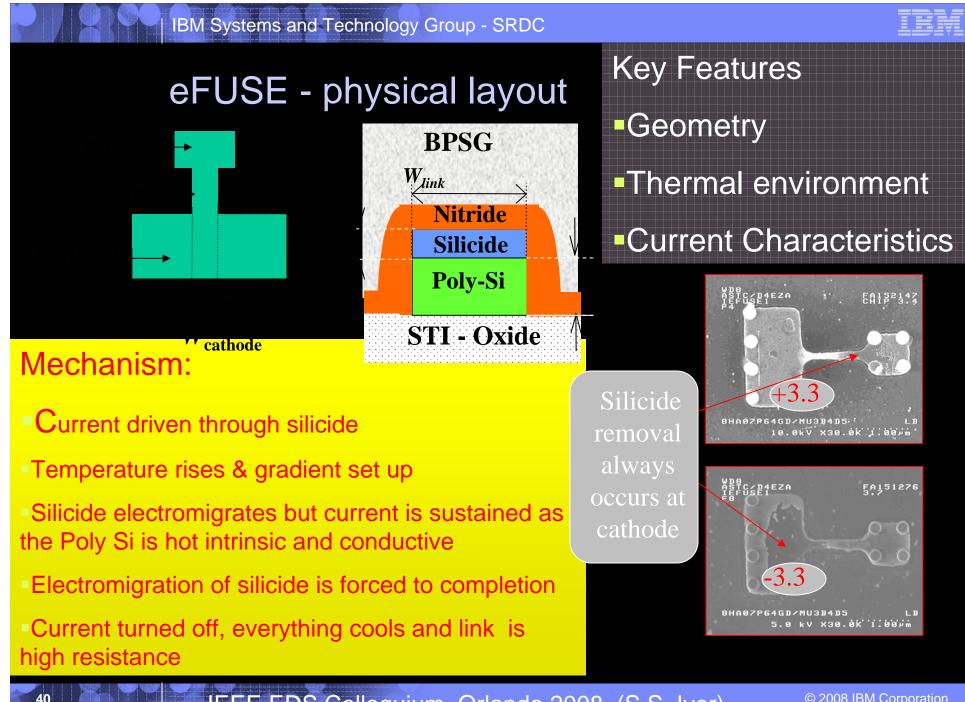

## The Kinder Gentler Fuse

We need to induce an electrical open without needing material to disappear.

39

$\nabla \cdot \neq \mathbf{0}$

Can we employ electromigration of metal lines ? Modern interconnects are electromigration resistant Need to control the electromigration and complete in a reasonable time e.g. 200  $\mu$ s – Cu line not an option

IEEE EDS Colloquium, Orlando 2008 (S.S. lyer)

IEEE EDS Colloquium, Orlando 2008 (S.S. lyer)

## **Circuit details**

43

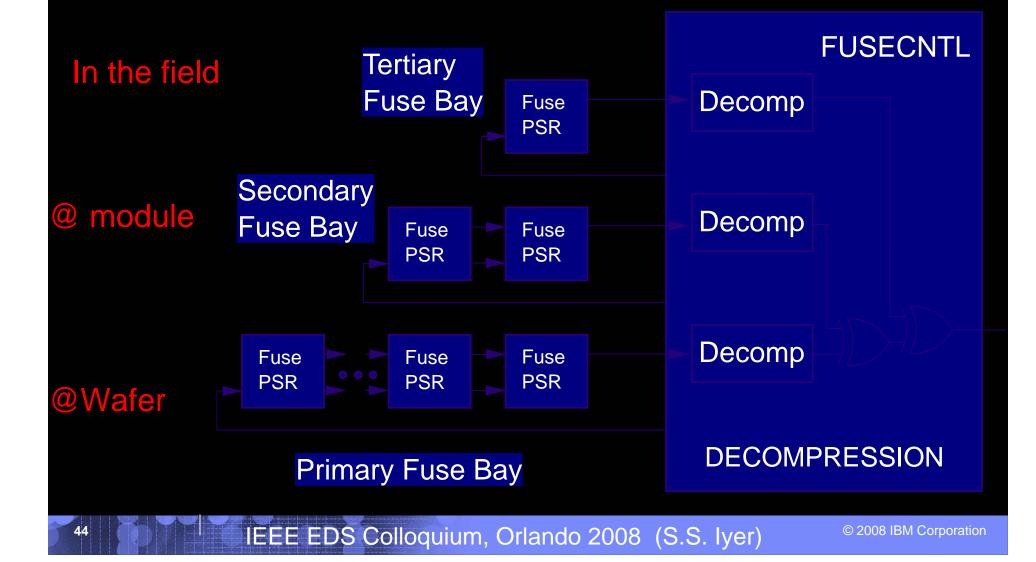

# Self-Test and Repair Flow – one touch test, repair & verify as implemented in Cu08

# Hierarchical Repair - Combining Three Repair Steps as implemented in Cu08

#### IBM

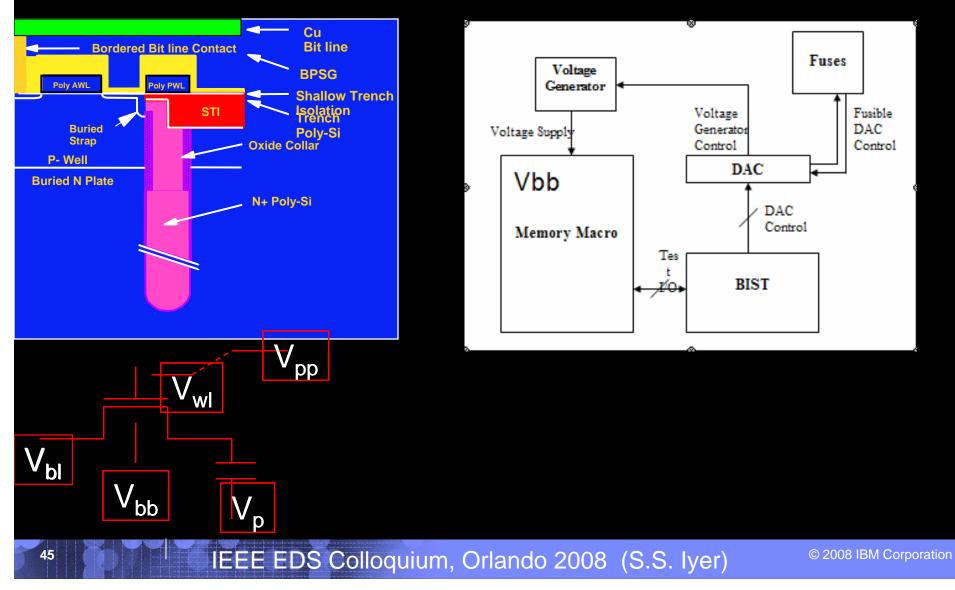

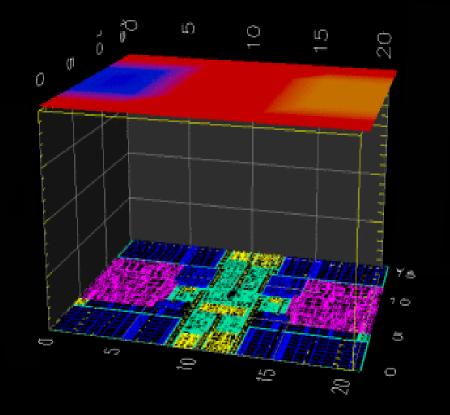

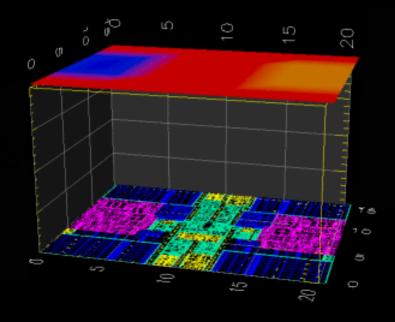

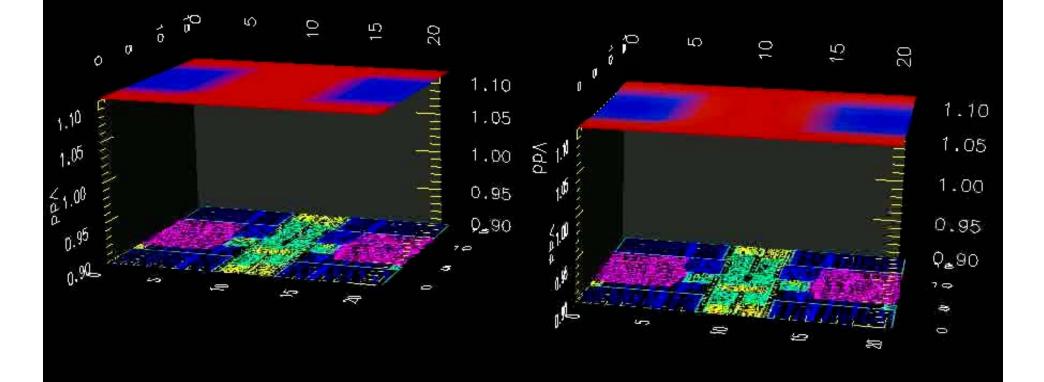

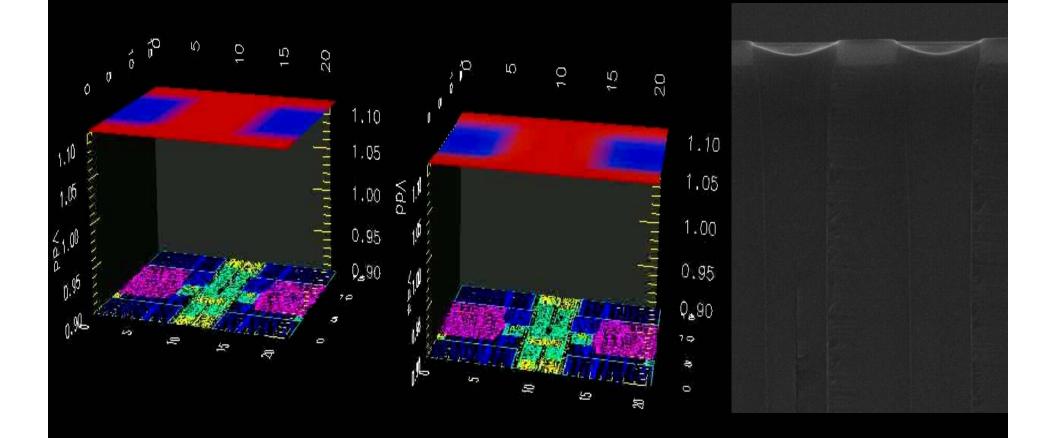

### Die specific Yield optimization: Voltage setting using eFUSE in embedded DRAM

Based on our electromigration Fuse technology – - - - No added process Cost

Memory architecture allows for ~15X improvement in bit density (115  $\mu$ m<sup>2</sup>/bit to 7  $\mu$ m<sup>2</sup>/bit)

Compilable in 2Kb blocks

Centralized repair, code and autonomic functions

### IBM

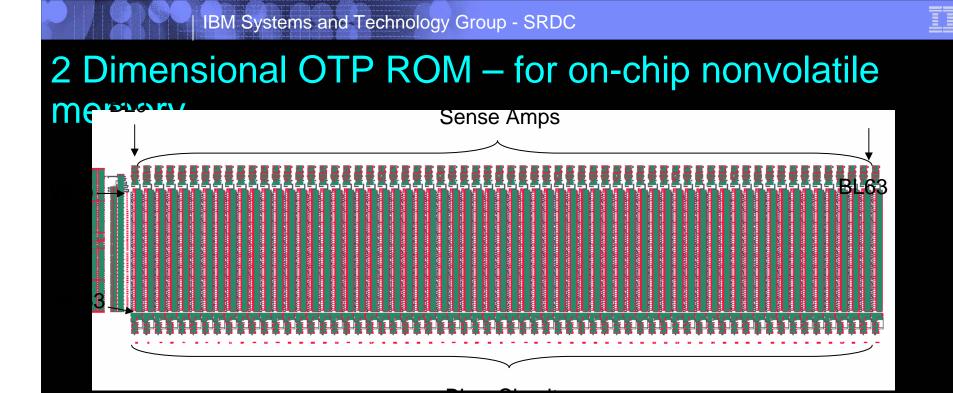

# What's next ?

- Optimizing chips for power and performance

- More autonomic functions

- Supply Chain management

- Chip identifiers for authentication

- RFID tags

- Logic compatible 2D OTP ROM

- Exploit other phenomena: Hot carrier, NBTI to self balance mismatched circuits

## Power supply decoupling

Why is decoupling important ? The concept of voltage compression

48

- Decoupling today is mostly an afterthought but compression is a serious problem

- A judicious of decoupling can allow for upto 10% reduction in Vdd due to reduced compression

### Noise Traveling Across Chip (Connected cores)

• Noise travels from active core to idle core

~4ns delay between

#### cores

• Noise is attenuated at quiet core

James et al, ISSCC 2007

49

## Noise Traveling Across Chip (Connected cores)

- Decoupling today is mostly an afterthought but Transient voltage droops due switching activity is a serious problem

- •Planar Caps are large and leak tremendously

- •So we cannot isolate this noise and must increase power supply to overcome

- •Can be a serious issue in high performance multicore applications

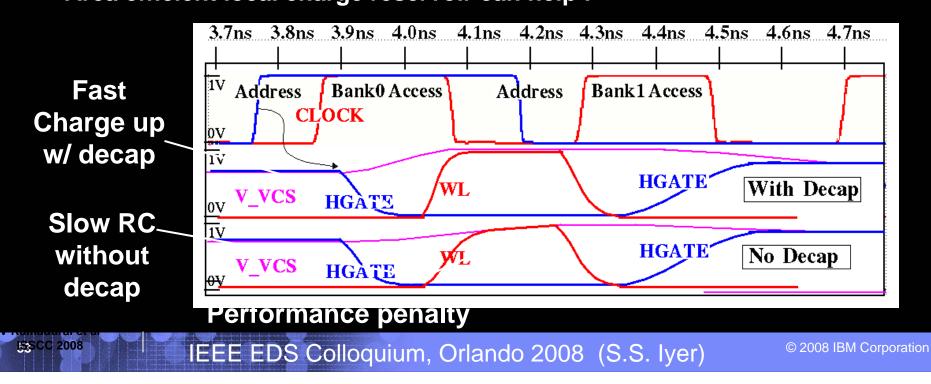

# **Trench based Decoupling**

•Deep trench decoupling reduces this by over 100mV and enables a 10% reduction of power supply voltage at same performance

•Comes free with our embedded DRAM

## Trench based Decoupling

#### SRAM DC Bowere Read Etfonology Group - SRDC

#### Current Solutions / Problems

Header / Footer based power gating popular

Lower array supply to save on leakage (reduce V<sub>DS</sub>)

Problem occurs during Wake Up (access cycle)

Most schemes have wake up cycles for DI/DT

Power supply response time > 1ns

Need multiple wake cycles @ 3-4 GHz frequencies

Area efficient local charge reservoir can help !

#### | IBM Systems and Technology Group - SRDC

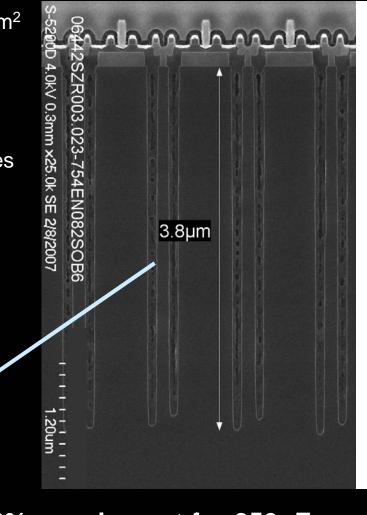

#### The DT Decoupling Cap 20X Advantage

- DT decoupling capacitance: 200fF/μm<sup>2</sup> vs. 11fF/μm<sup>2</sup> for thick-oxide depletion device

- Incorporated in 45nm ASIC Methodology

C' m

JUE

1st Stage SA

2nd Stage SA

Local array-supply charge reservoir to enable dynamic leakage reduction with NO wake-up cycles for > 2GHz operation

128-BL

Deep Trench decoupling cap

Half-Bank: power-gating granularity

Controls

#### < 2% area impact for 250pF of Embedded DT CAP

IEEE EDS Colloquium, Orlando 2008 (S.S. lyer)

**IO Block**

128-WL

128x128 <u>Su</u>barray

© 2008 IBM Corporation

512Kb

SRAM

ASIC

# Three Dimensional Integration – scaling in the third dimension

IEEE EDS Colloquium, Orlando 2008 (S.S. Iyer)

#### IBM

## Summary

- Scaling provides some density benefit

- Technology performance comes from technology features rather than scaling: eg Strain Engineering

- Hi K if can get us back to scaling for a short time

- Memory integration is a very big thing

- Chips will have more autonomic system level like functions enabled by technology features such as eFUSE

- Innovative decoupling can provide for upto a 10% performance improvement

- Three Dimensional Integration is the next huge thing

### I would like to acknowledge the contributions of the 45nm, Hi K, embedded DRAM and eFUSE teams

# Yes..... The Old Dog does learn new tricks

IEEE EDS Colloquium, Orlando 2008 (S.S. lyer)