### Continuous-time ΔΣ Modulators with Improved Linearity and Reduced Clock Jitter Sensitivity using the SCRZ DAC

Shanthi Pavan Indian Institute of Technology, Madras Chennai 600 036

- Work of my M.S students

- Timir Nandi, now at TI, India

- Karthikeya Boominathan

- Part of this presented at

- CICC 2012

## Outline

- Introduction

- Limitations of conventional DAC pulses

- Switched-C Return-to-Zero Principle

- Modulator Architecture

- Circuit Design

- Measurement Results

- Conclusion

# Motivation

- Continuous-time DSMs

- Resistive input impedance

- Relaxed opamp gain requirements

- Most high performance CTDSMs

- Multibit loops

- Focus of this research

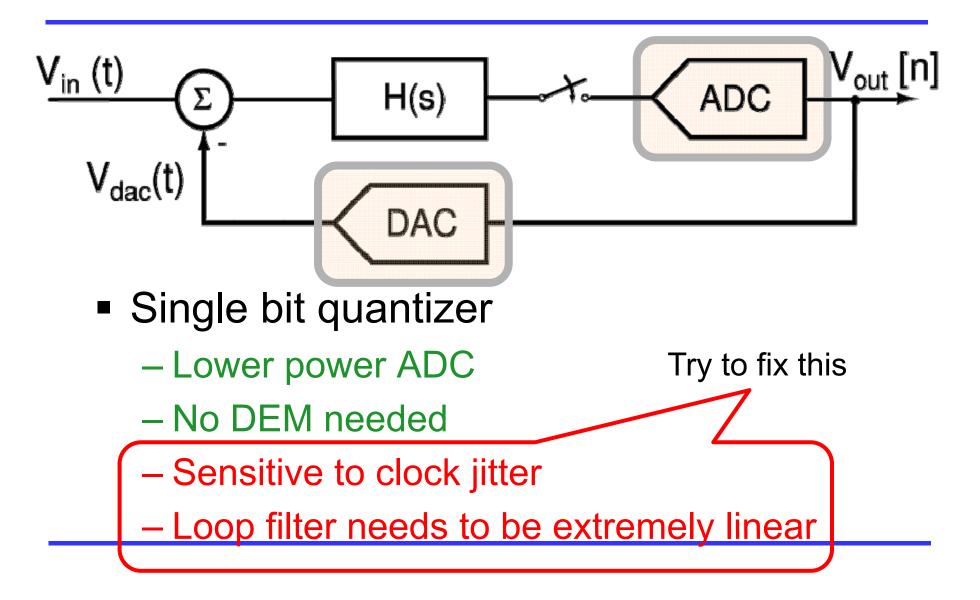

- Can we do better with single-bit loops?

- Case study

- 14 bit ENOB, 2 MHz Bandwidth, 0.18  $\mu m$  CMOS

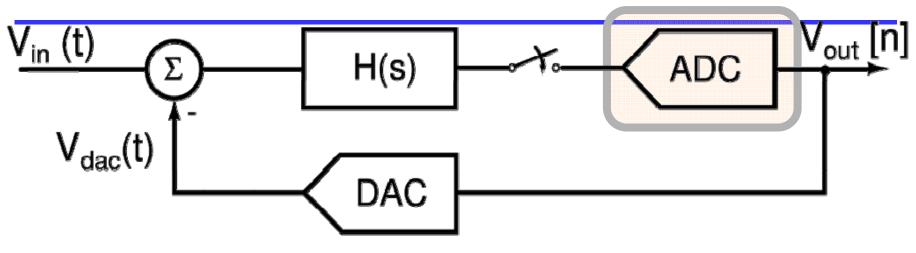

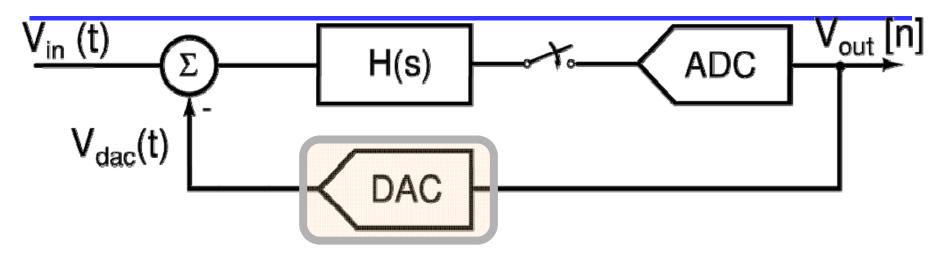

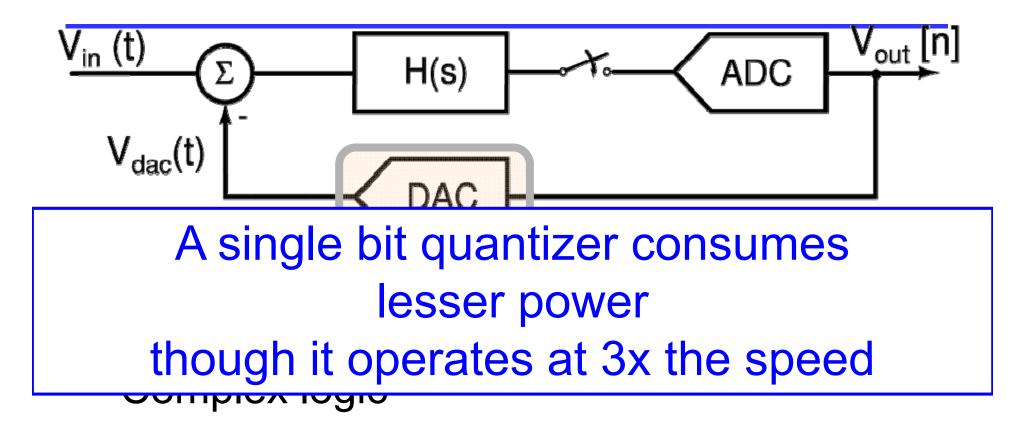

## Multibit versus Single-bit Modulators

# **Design Targets**

| Dynamic Range    | 86dB (14 ENOB) |       |

|------------------|----------------|-------|

| Bandwidth        | 2 MHz          |       |

| Order            | 4              |       |

| Quantizer        | 1 bit          | 4 bit |

| Out of Band Gain |                |       |

| OSR Needed       |                |       |

| Sampling Rate    |                |       |

# **Design Targets**

| Dynamic Range    | 86dB (14 ENOB) |       |

|------------------|----------------|-------|

| Bandwidth        | 2 MHz          |       |

| Order            | 4              |       |

| Quantizer        | 1 bit          | 4 bit |

| Out of Band Gain | 1.5            |       |

| OSR Needed       | 64             |       |

| Sampling Rate    | 256 MHz        |       |

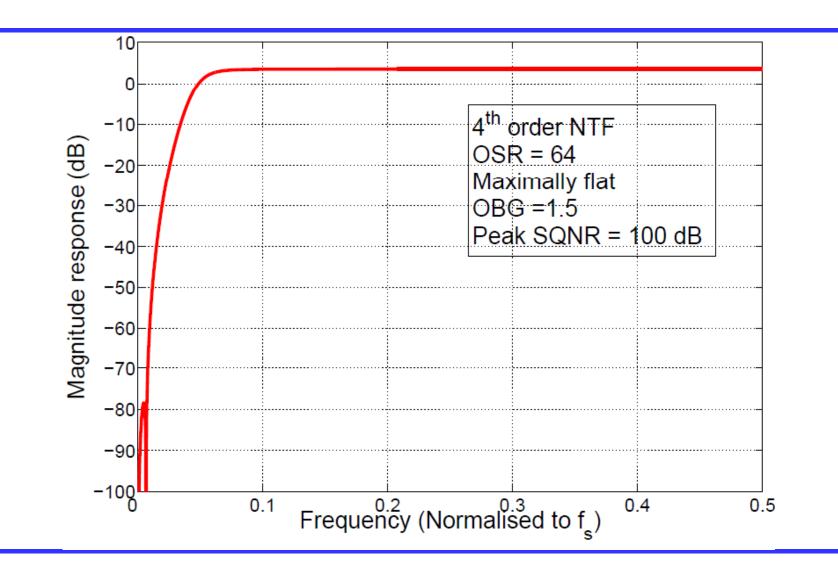

# **Design Targets**

| Dynamic Range    | 86dB (14 ENOB) |        |

|------------------|----------------|--------|

| Bandwidth        | 2 MHz          |        |

| Order            | 4              |        |

| Quantizer        | 1 bit          | 4 bit  |

| Out of Band Gain | 1.5            | 2.5    |

| OSR Needed       | 64             | 20     |

| Sampling Rate    | 256 MHz        | 80 MHz |

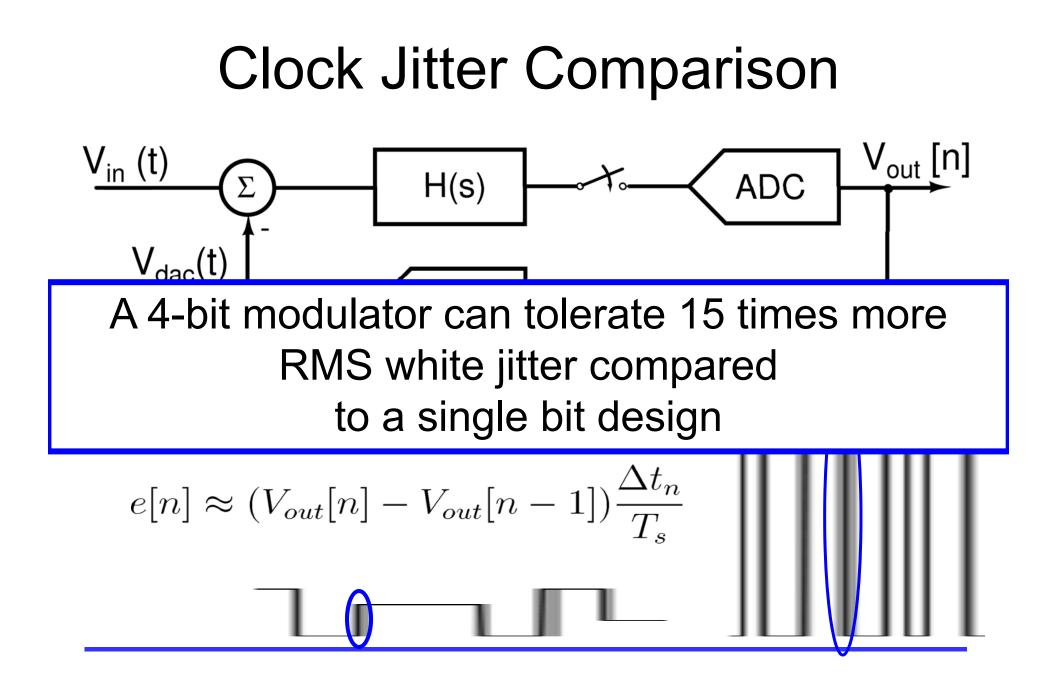

## ADC: 1 bit versus 4 bit

- 4 bit ADC

- 15x more comparators @ 1/3<sup>rd</sup> speed

- 5x more ADC power, 15x more area

- 15x loop filter & clock path loading

## DAC: 1 bit versus 4 bit

- 4 bit DAC

- -Needs Dynamic Element Matching

- -DEM adds excess delay & power

-Not very effective @ low OSR

## DAC: 1 bit versus 4 bit

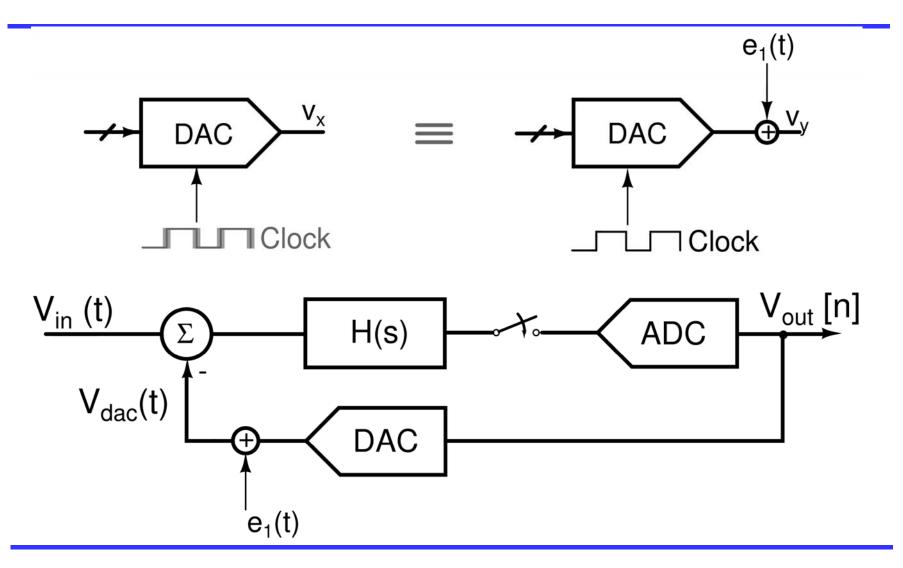

## Modeling Clock Jitter

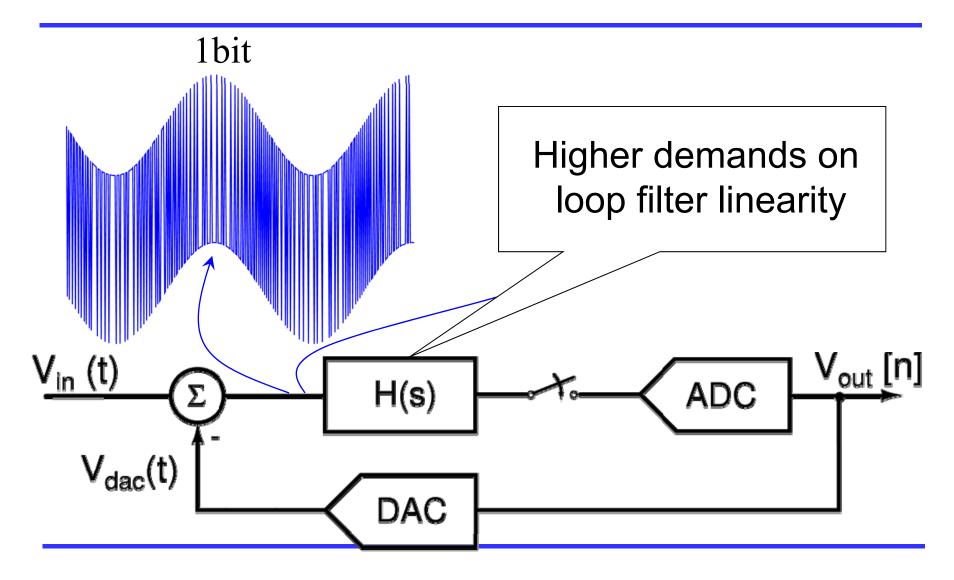

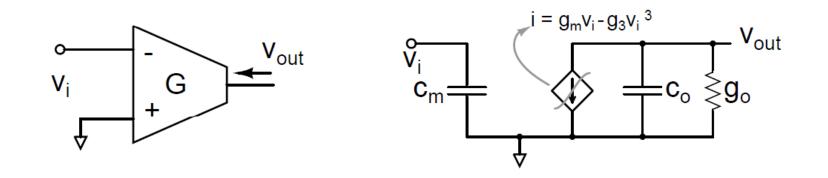

# Loop Filter Linearity

## Choice of Quantizer

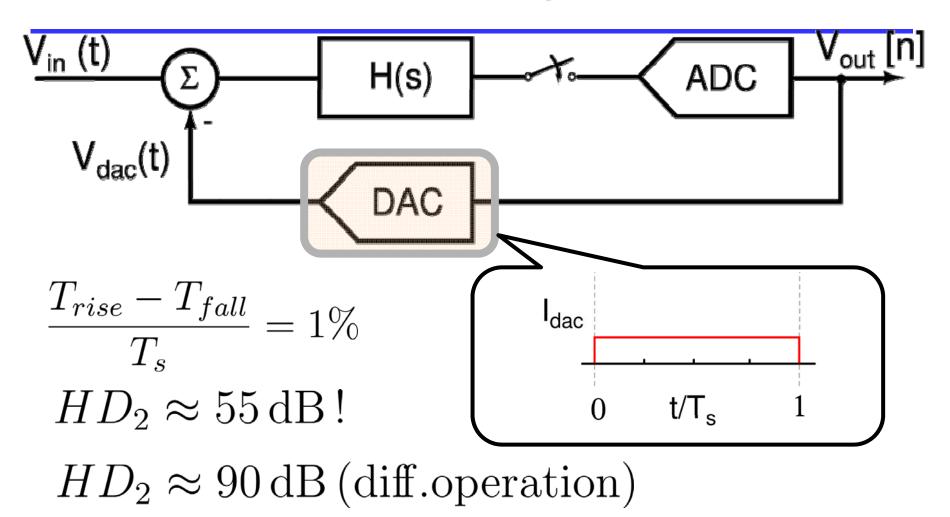

Inherently nonlinear (rise-fall asymmetry)

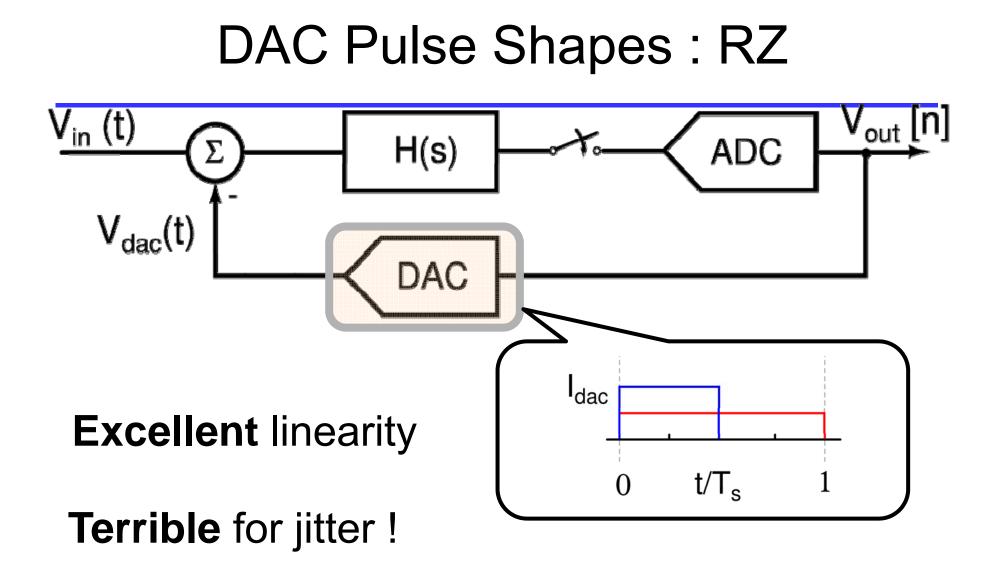

#### **DAC Pulse Shapes : NRZ**

### DAC Pulse Shapes : NRZ

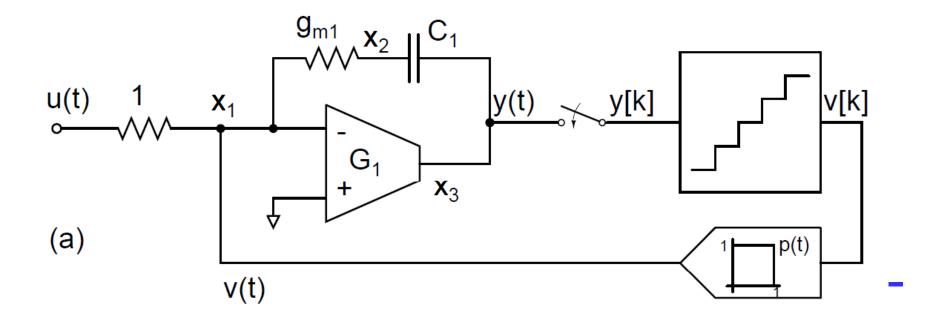

# Digression : Weak Nonlinearities in CTDSMs

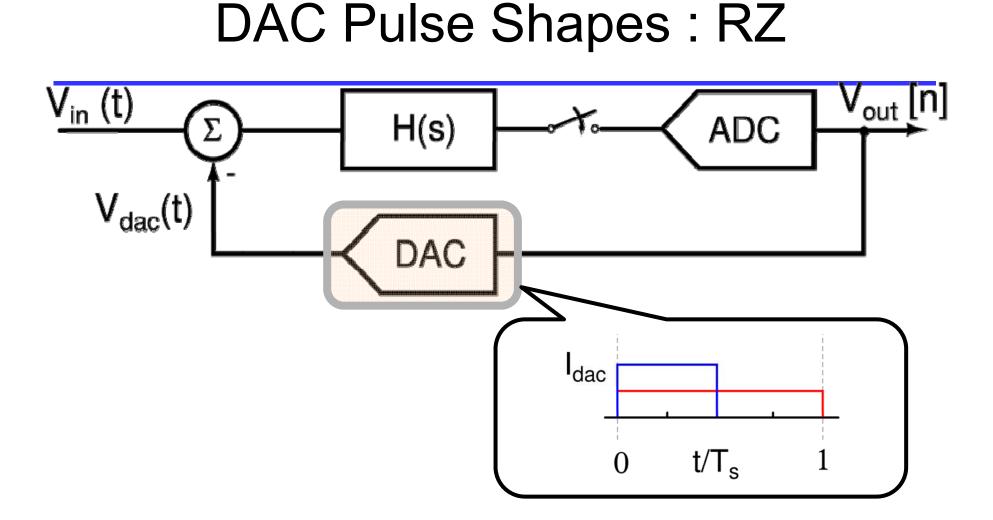

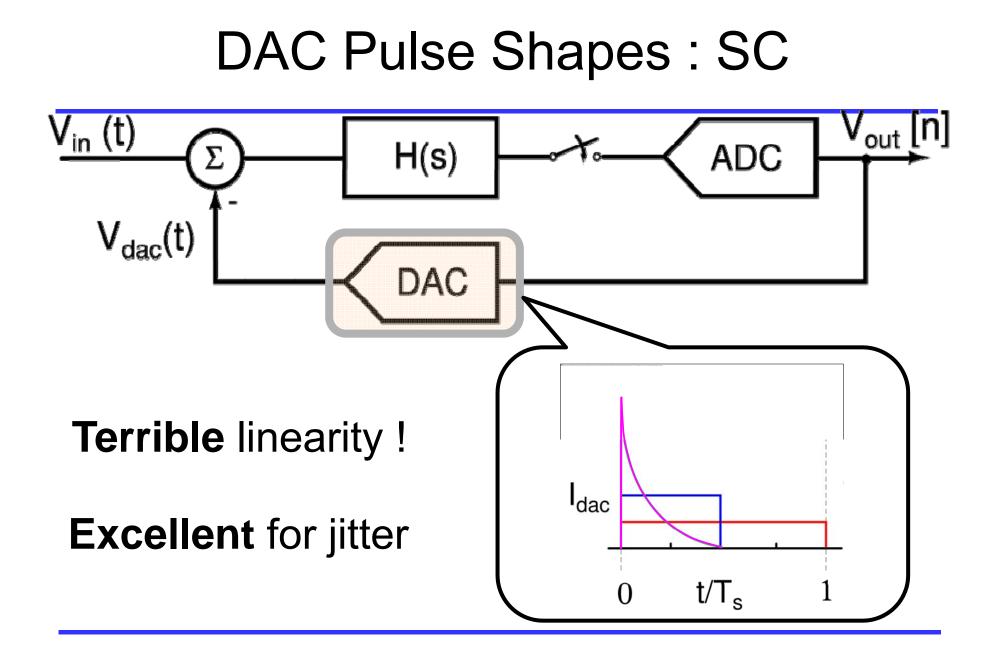

### **RZ DAC : Linearity**

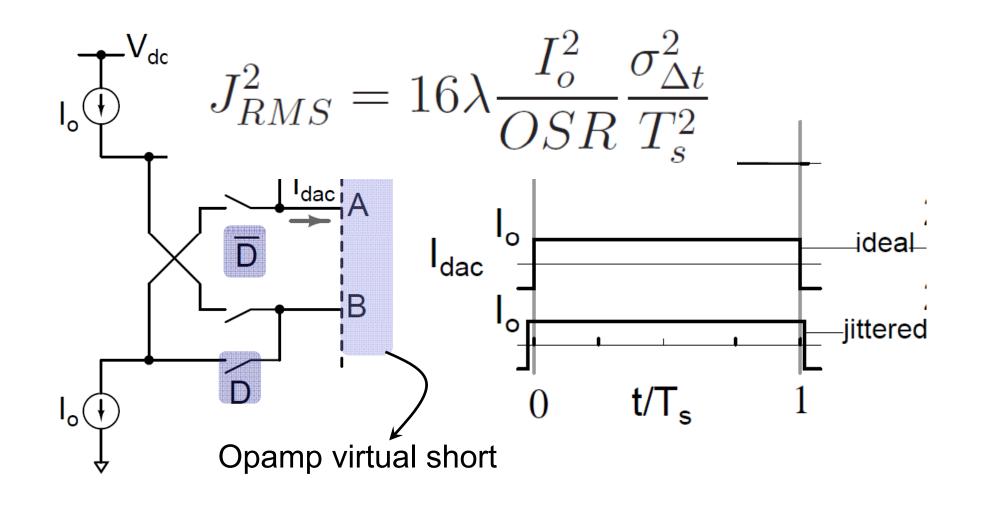

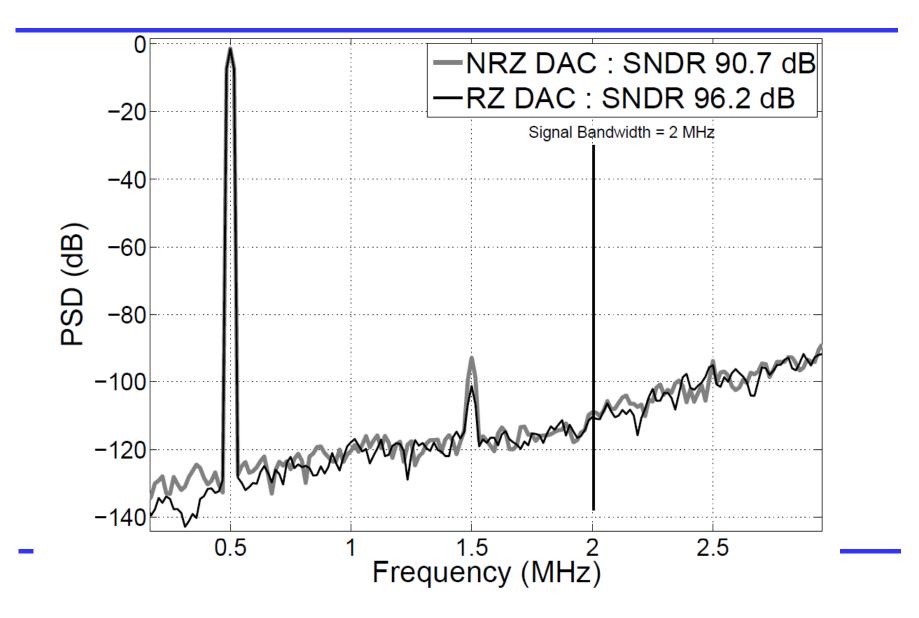

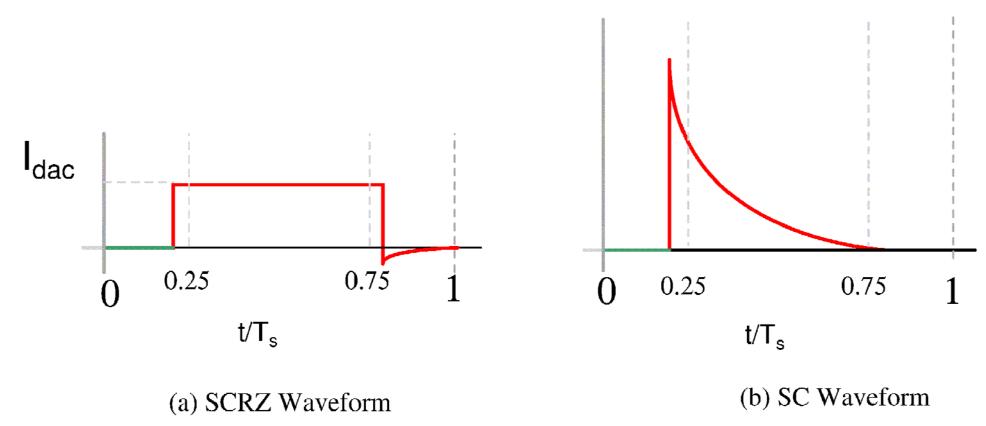

### **RZ DAC : Jitter**

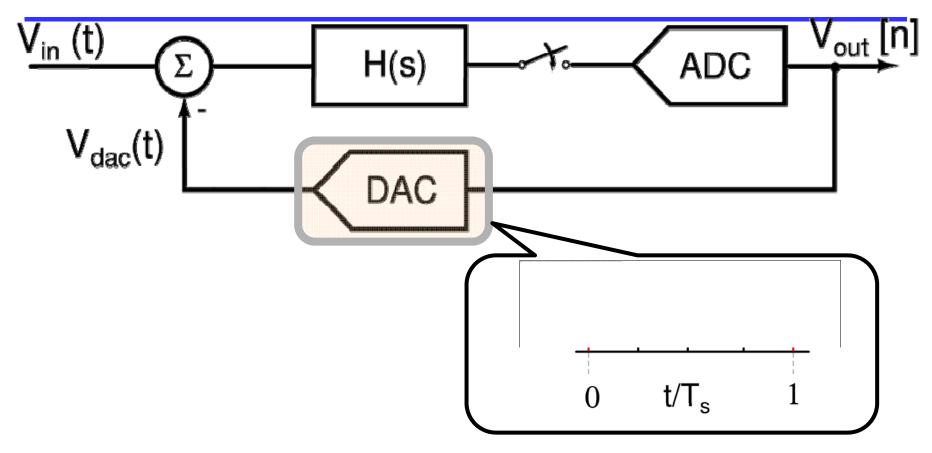

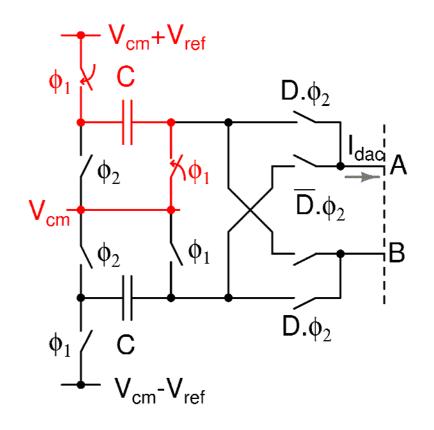

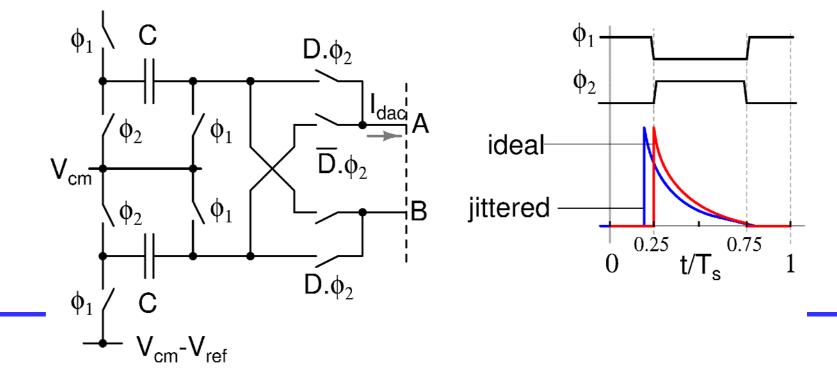

## SC DAC

- Capacitors are charged to  $\pm V_{ref}$  during  $\Phi_1$

- They are discharged into the loopfilter during  $\Phi_2$

- Charge transferred = ±CV<sub>ref</sub>

### SC DAC

- Capacitors are charged to  $\pm V_{ref}$  during  $\Phi_1$

- They are discharged into the loopfilter during Φ<sub>2</sub>

- Charge transferred = ±CV<sub>ref</sub>

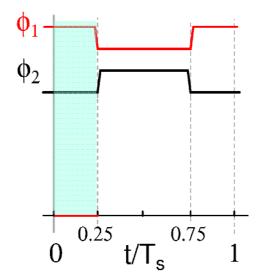

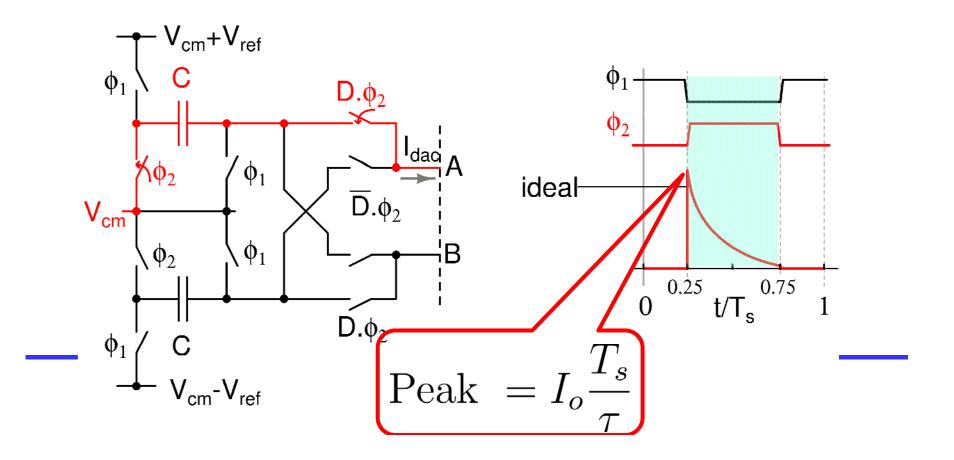

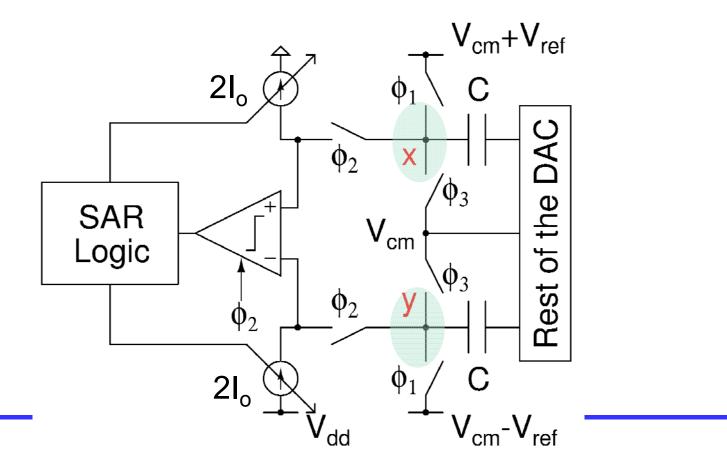

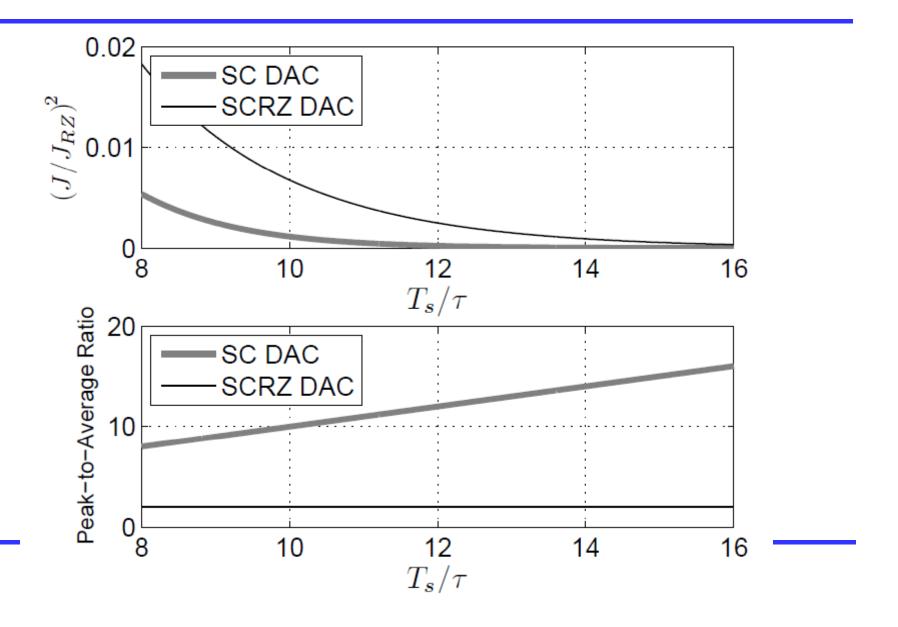

### SC DAC with Jitter

Transfers most of the charge in a short period

$$J_{RMS}^2 = 8 \frac{I_o^2}{OSR} \left(\frac{T_s}{\tau}\right)^2 \exp\left(-\frac{T_s}{\tau}\right) \frac{\sigma_{\Delta t}^2}{T_s^2}$$

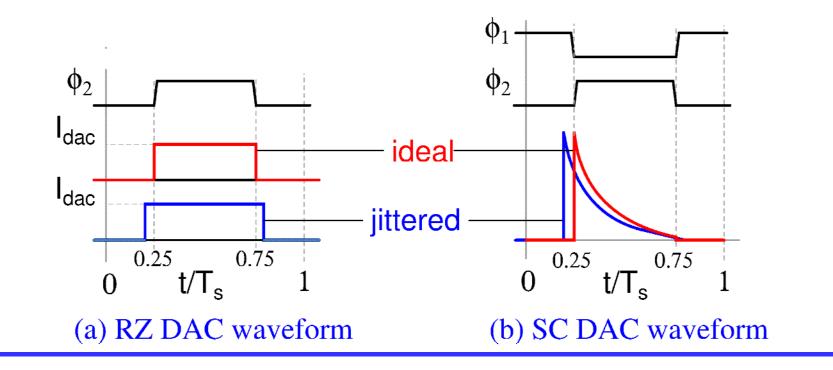

## SC DAC

- DAC output peak current is higher

- Higher demands on the linearity of the loop filter

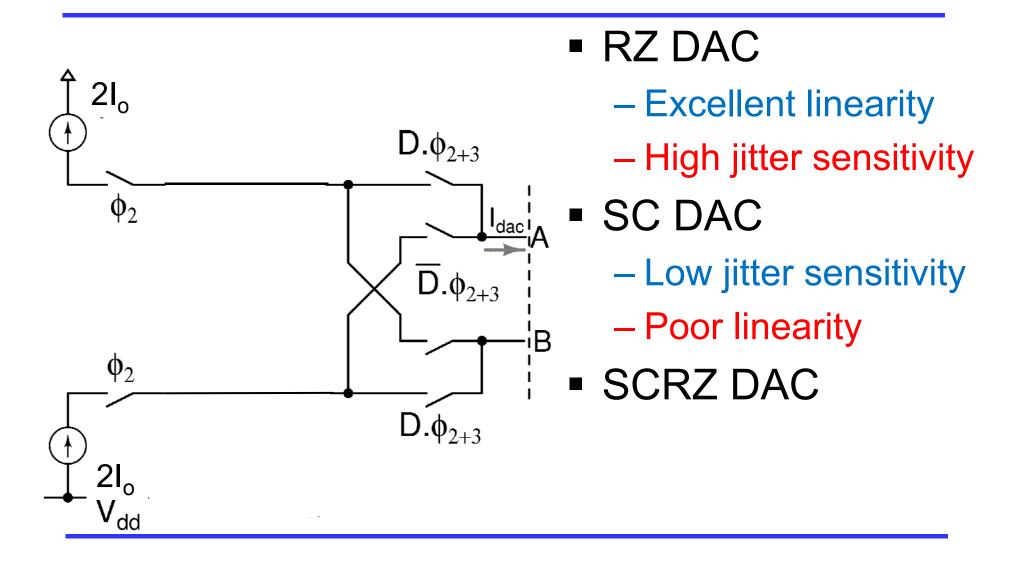

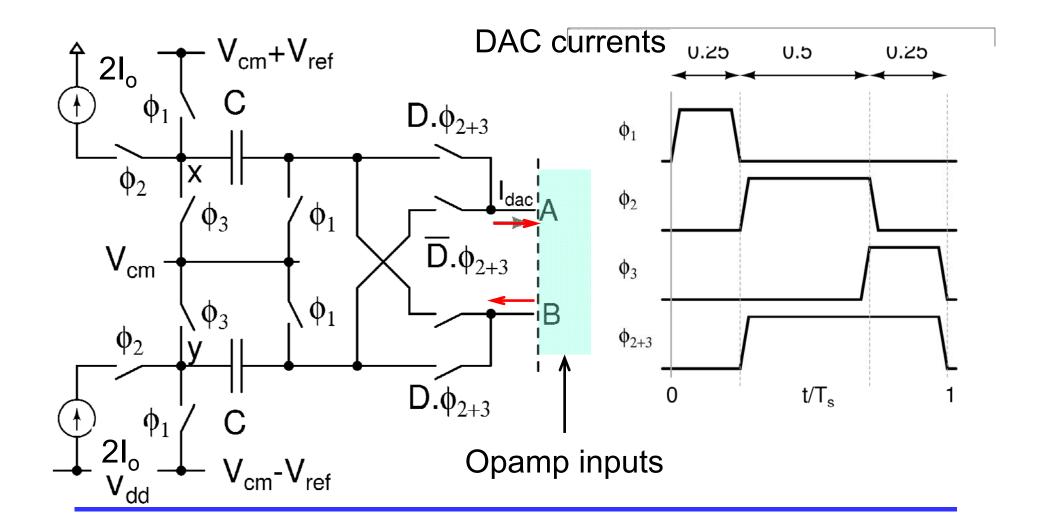

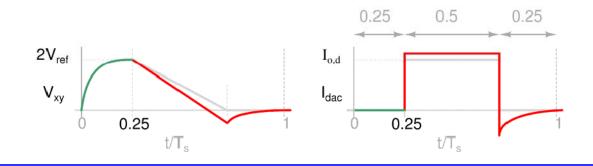

## Introducing the SCRZ DAC

### Introducing the SCRZ DAC

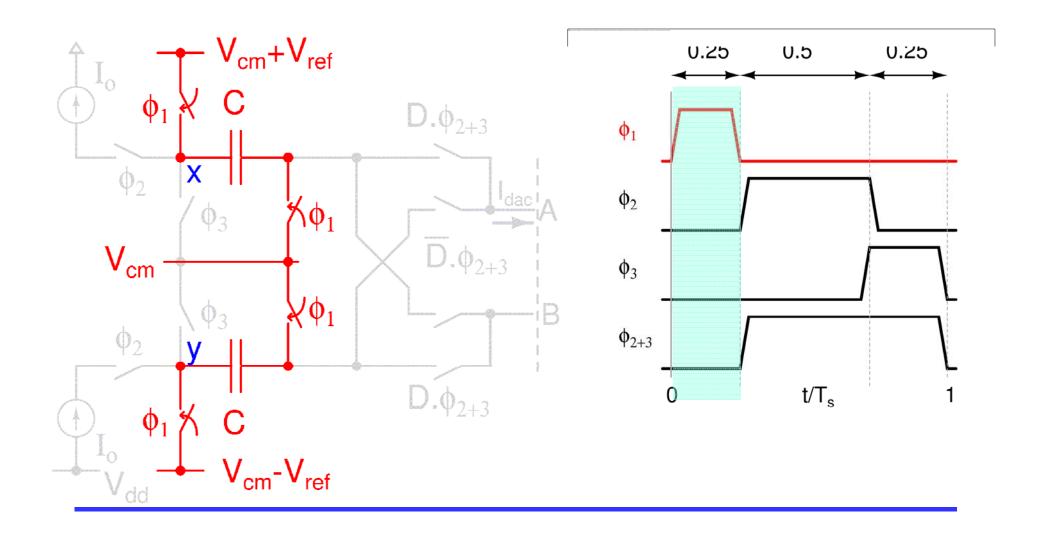

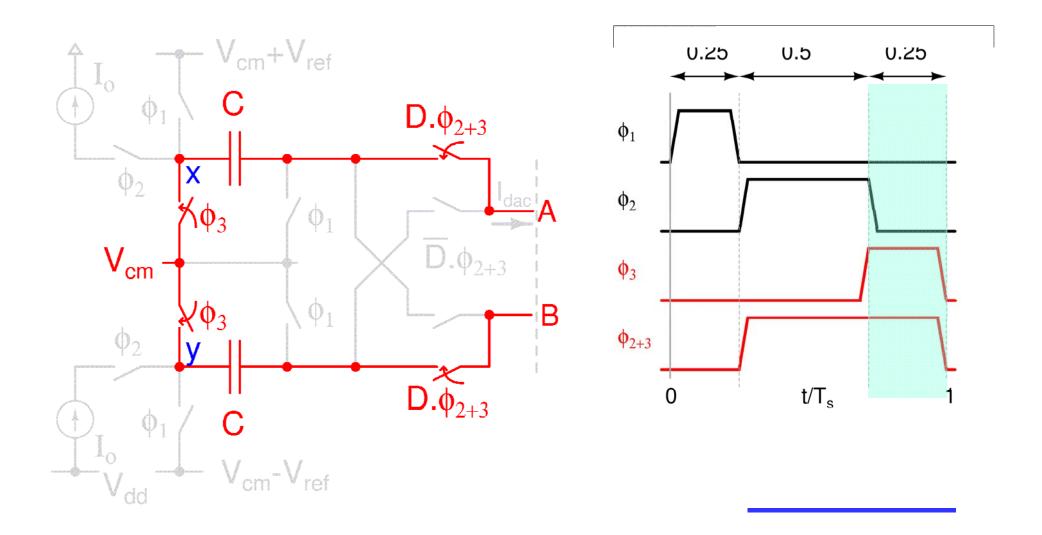

### SCRZ DAC operation ( $\Phi_1$ )

### SCRZ DAC operation ( $\Phi_1$ )

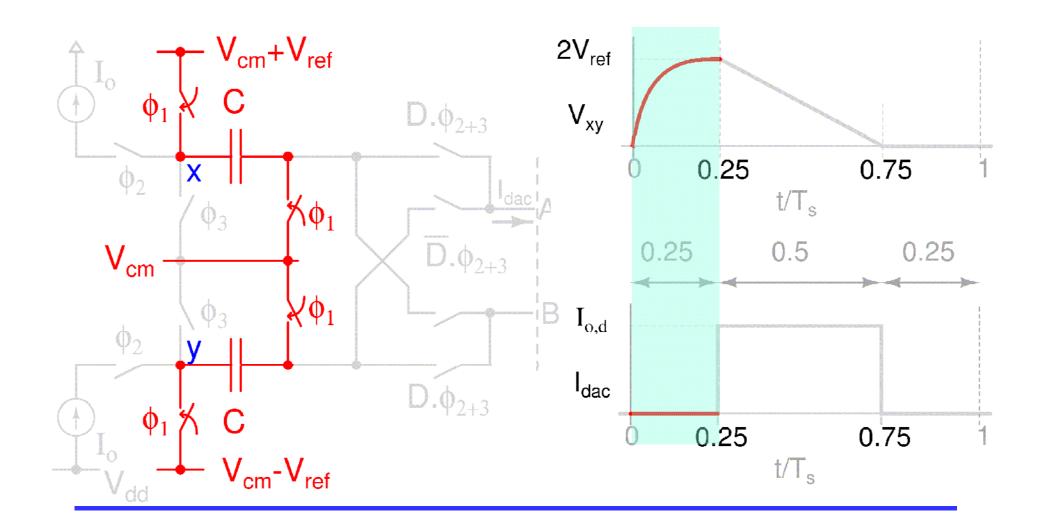

## SCRZ DAC operation ( $\Phi_2$ )

### SCRZ DAC operation ( $\Phi_2 = 0.5T_s$ )

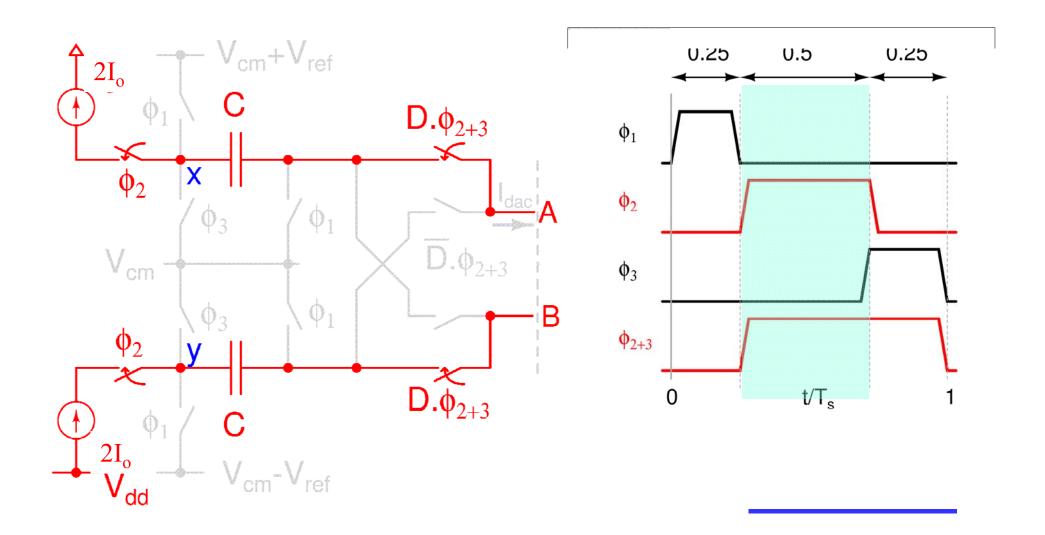

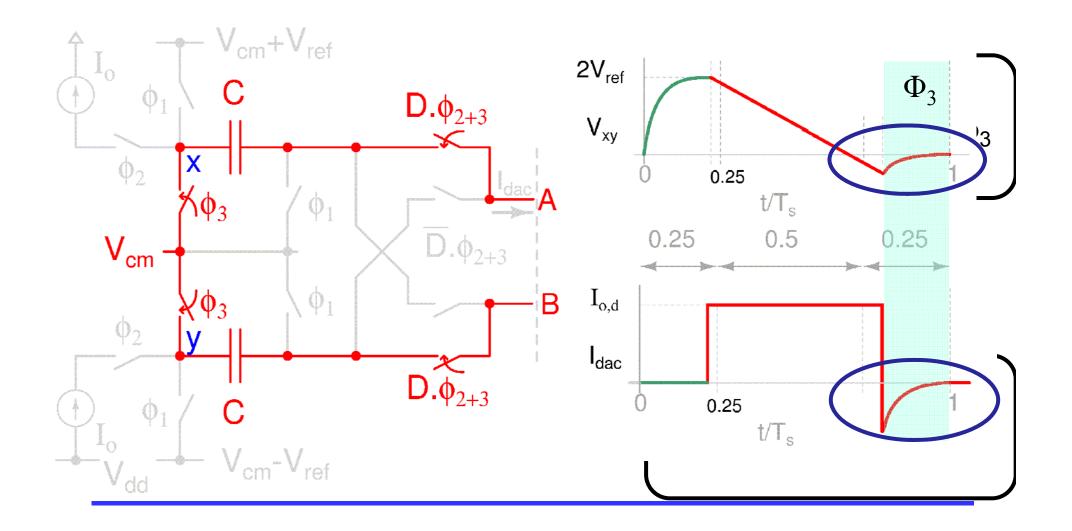

### SCRZ DAC operation ( $\Phi_3$ )

## SCRZ DAC operation ( $\Phi_3$ )

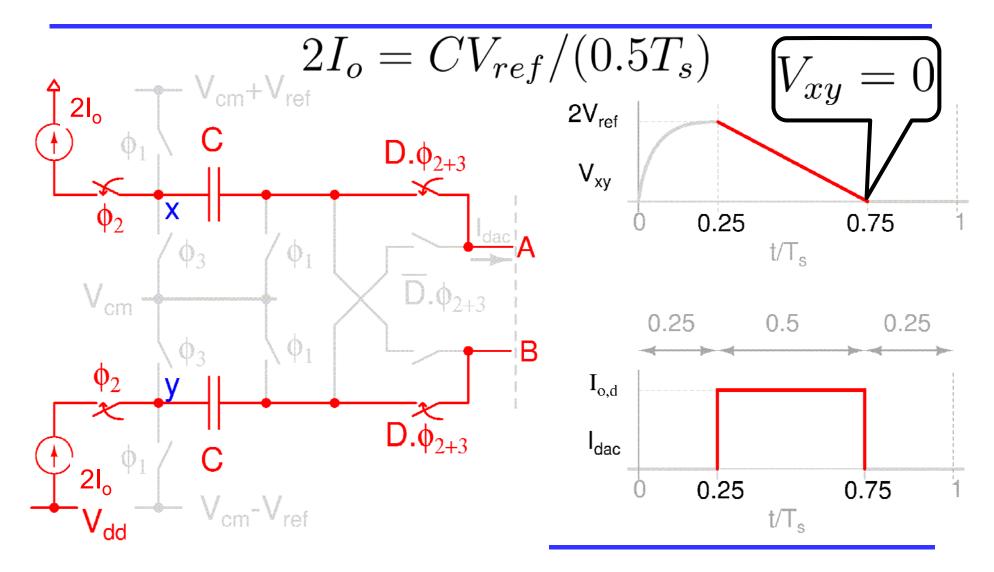

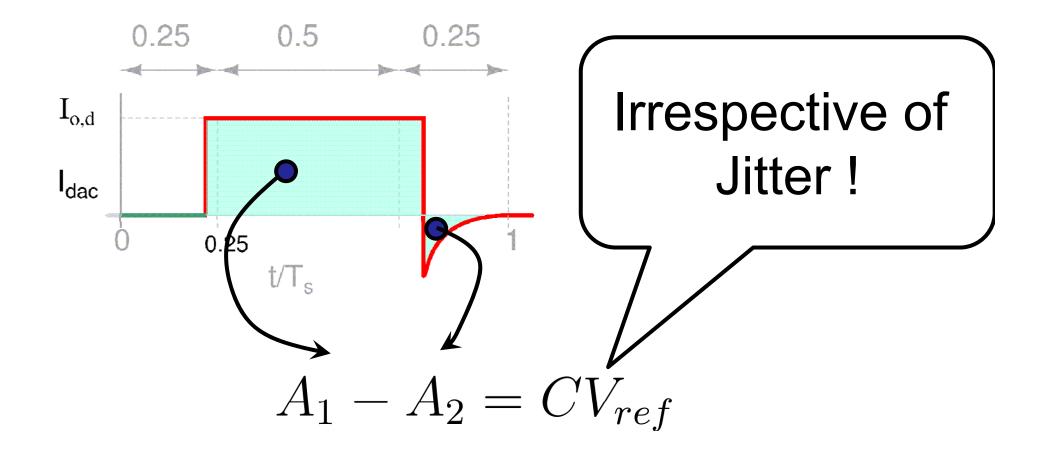

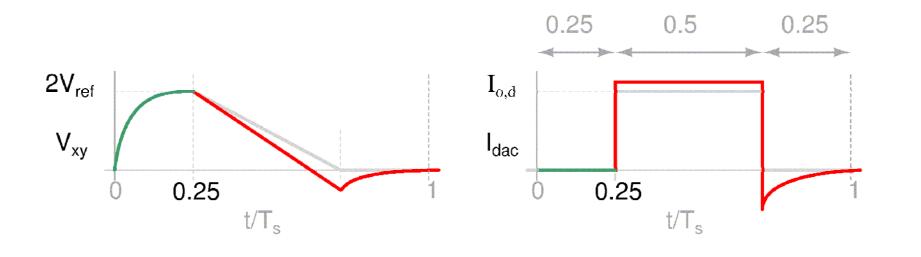

### Summary : Ideal Waveforms

- With an ideal clock

- With ideal current  $2I_o = CV_{ref}/(0.5T_s)$  $-I_{dac}$  has an RZ pulse shape

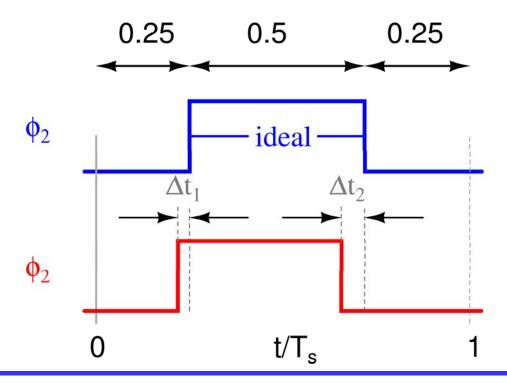

Effect of jitter

- Ideal  $\phi_2$  half clock cycle wide

- Jittered  $0.5T_s + \tau$

### Effect of jitter

# Waveforms ( $\Phi_3$ )

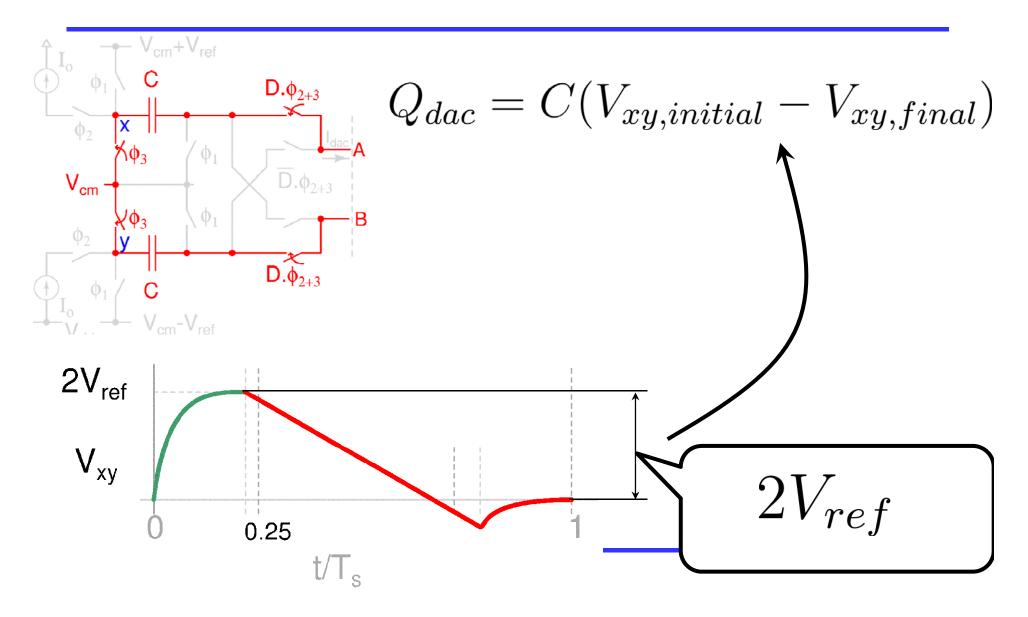

### **Total DAC Charge**

## **Total DAC Charge**

## Role of current source

- Shapes the capacitor discharge pulse

- Smaller peak current

- Relaxed requirement linearity of the loop filter

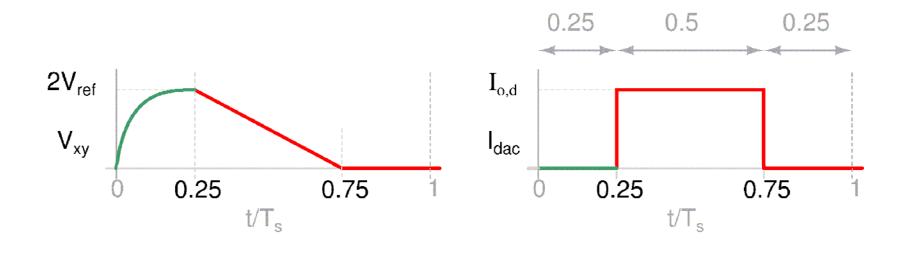

# Non ideality - Deviation of 2I<sub>o</sub>

- $2I_{o}(0.5T_{s}) = CV_{ref}$

- $I_{o,d} = 2CV_{ref}/T_s$

- Capacitors completely discharged at the end of  $\Phi_2$

- $I_{dac} = 0$  during  $\Phi_3$

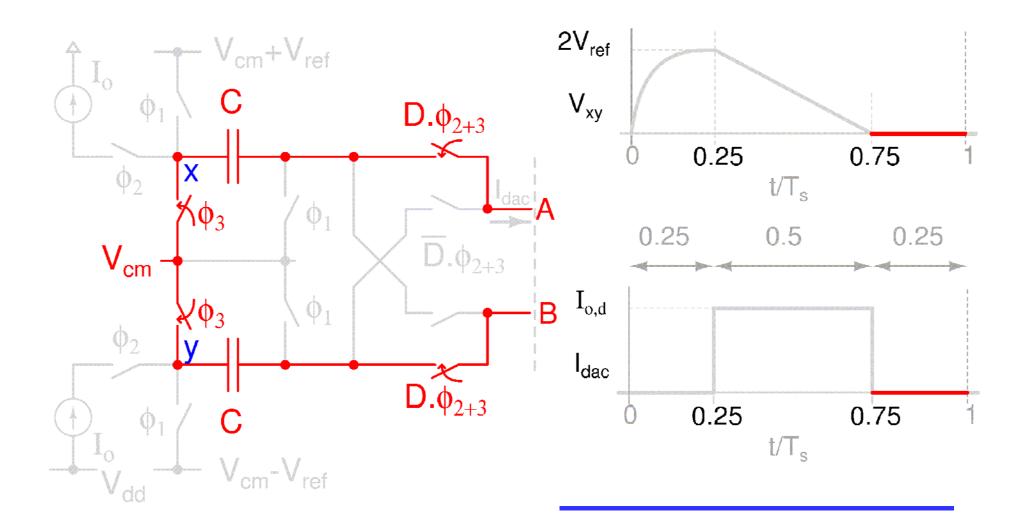

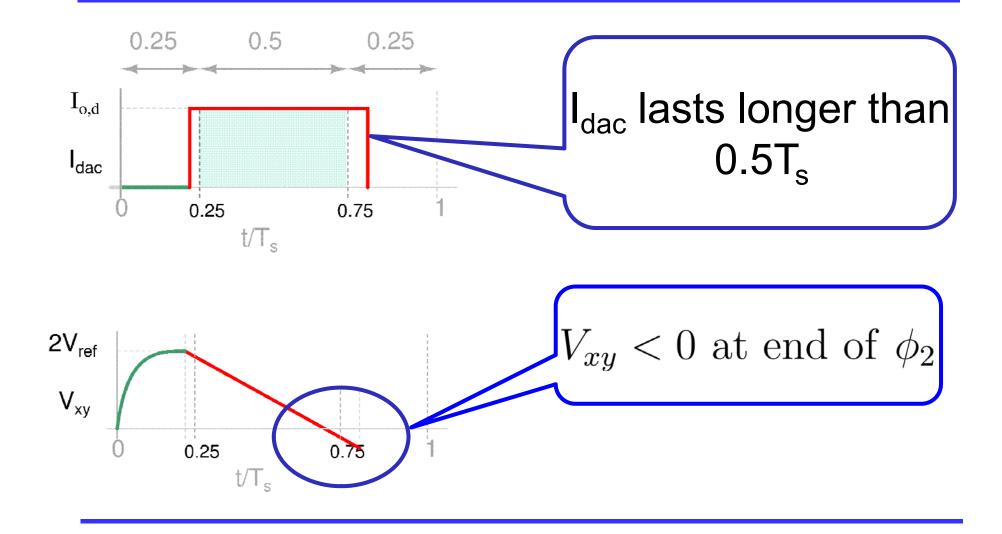

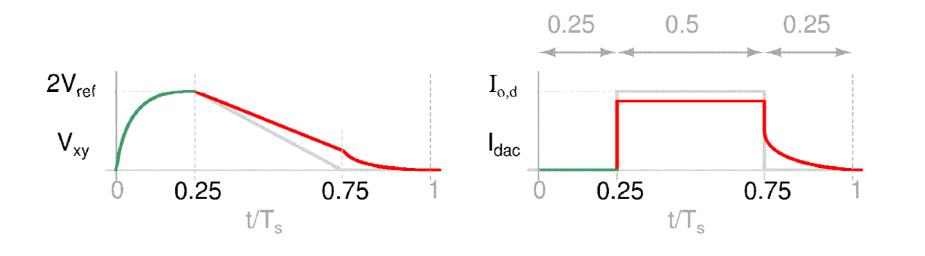

# If $2I_o < I_{o,d}$

- Capacitors are incompletely discharged

- The residual charge is discharged during  $\Phi_3$

- $I_{dac}$  is positive during  $\Phi_3$

- Net charge supplied by the DAC remains ±CV<sub>ref</sub>

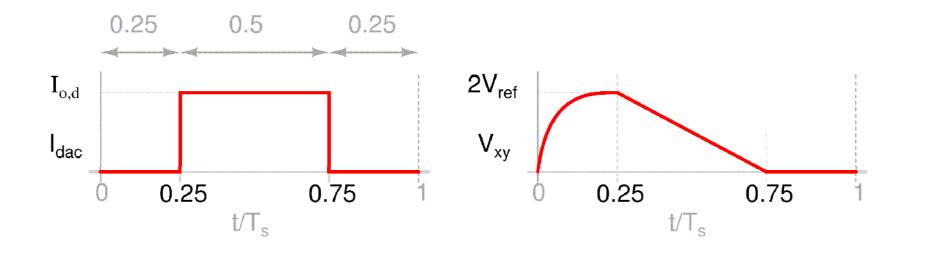

# If $2I_{o} > I_{o,d}$

- Capacitors are over discharged

- The capacitors are charged during  $\Phi_3$

- $I_{dac}$  is negative during  $\Phi_3$

- Net charge supplied by the DAC remains ±CV<sub>ref</sub>

Tune 21<sub>o</sub>

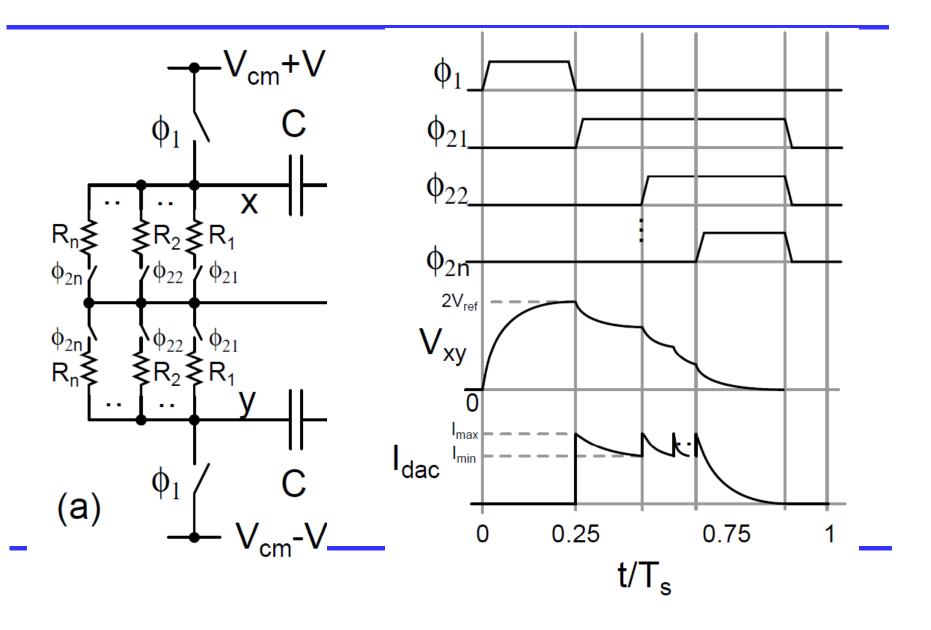

# Tune $2I_o$

- Comparator- sign of  $V_{xy}$  at the end of  $\Phi_2$

- Control I<sub>o</sub> to 6-bit accuracy

# Compare : SC versus SCRZ DAC

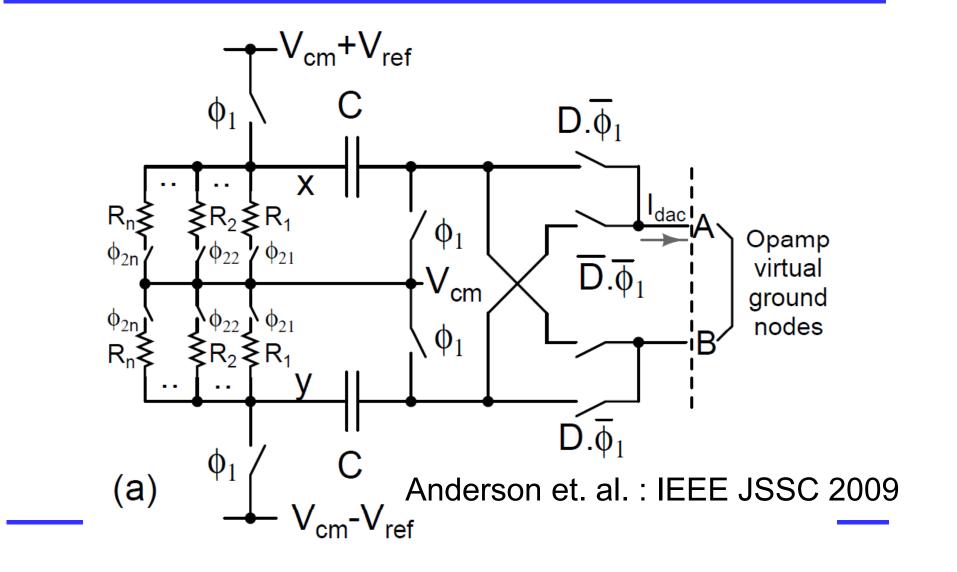

# Related Work : The SCSR DAC

# Related Work : The SCSR DAC

### **Target Modulator Specifications**

- Signal Bandwidth = 2 MHz

- Sampling frequency = 256 MHz

- Quantizer range = 3.6 V<sub>pp,d</sub>

- Target resolution = 14 Bits

- 0.18 µm CMOS process

#### **Noise Transfer Function**

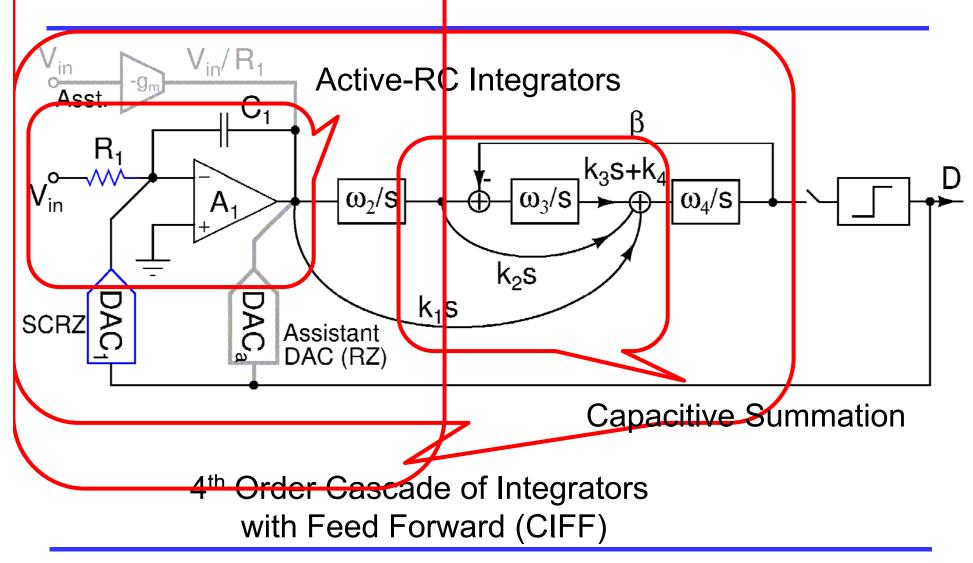

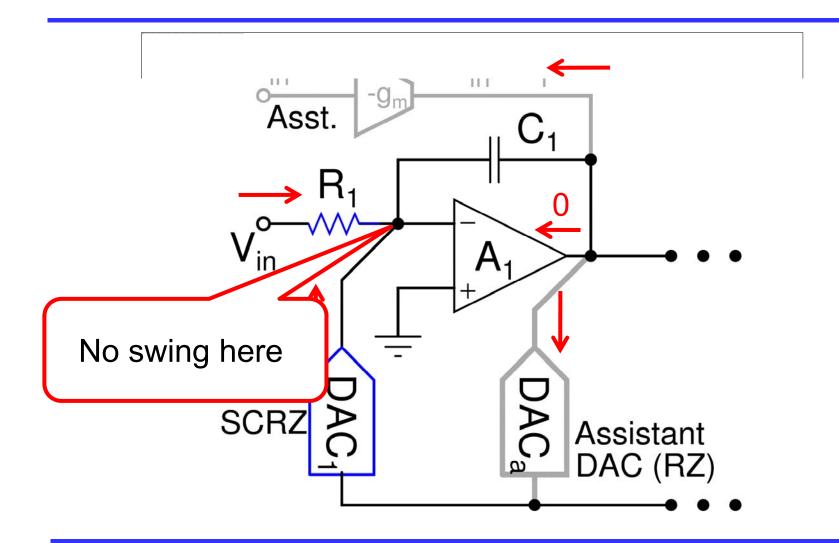

# Modulator Architecture

### **Assisted Opamp Technique**

[1] S. Pavan and P. Sankar, "Power reduction in continuous-time delta sigma modulators using the assisted opamp technique," IEEE Journal of Solid-State Circuits., vol. 45, no. 7, pp 1365-1379, July 2010

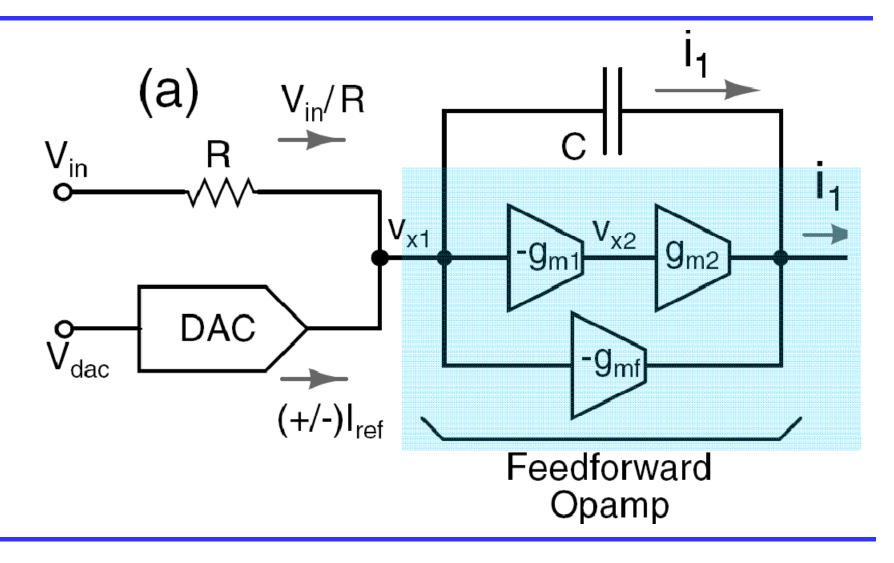

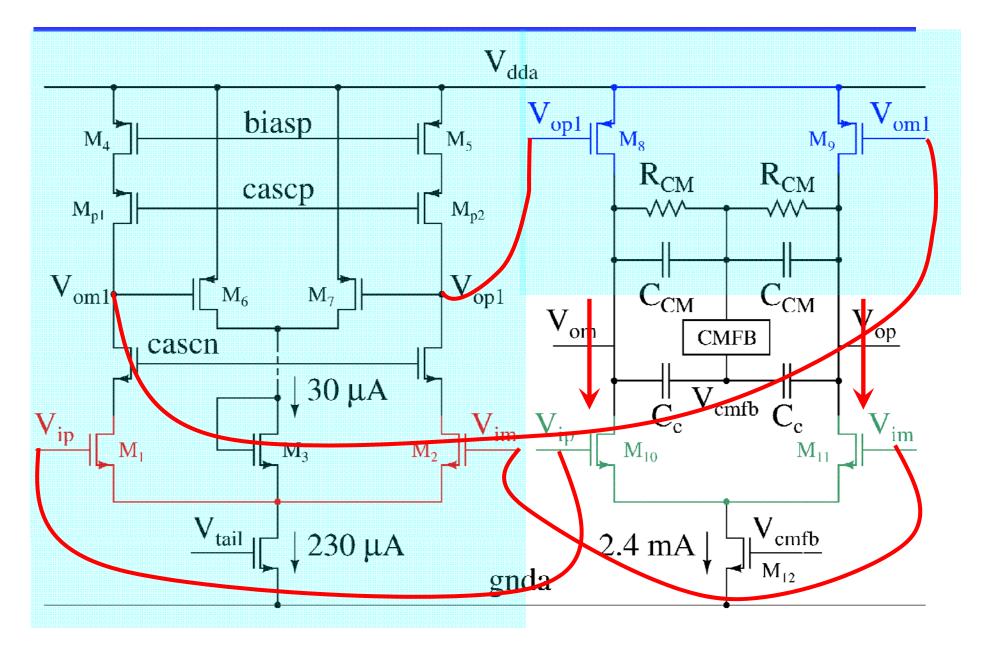

# **Opamp Design**

### **Two Stage Feedforward Compensation**

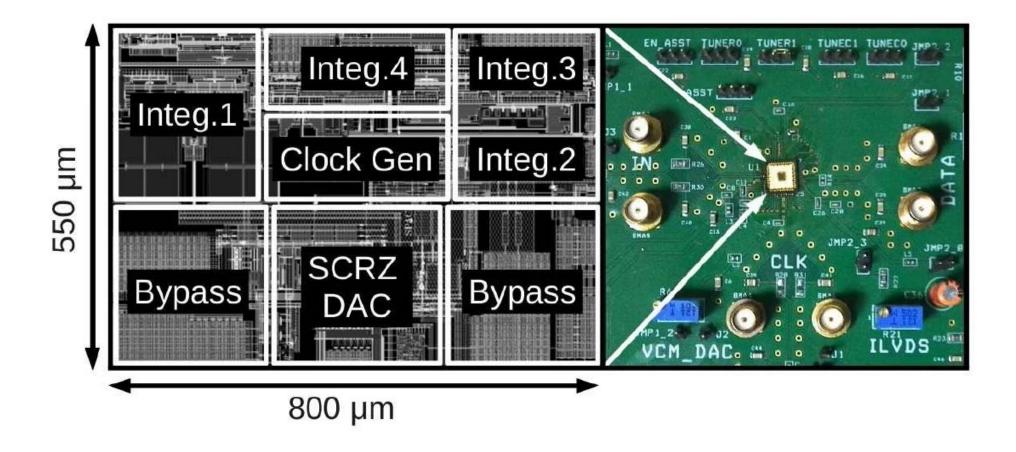

### Chip layout and test board

### Test Setup

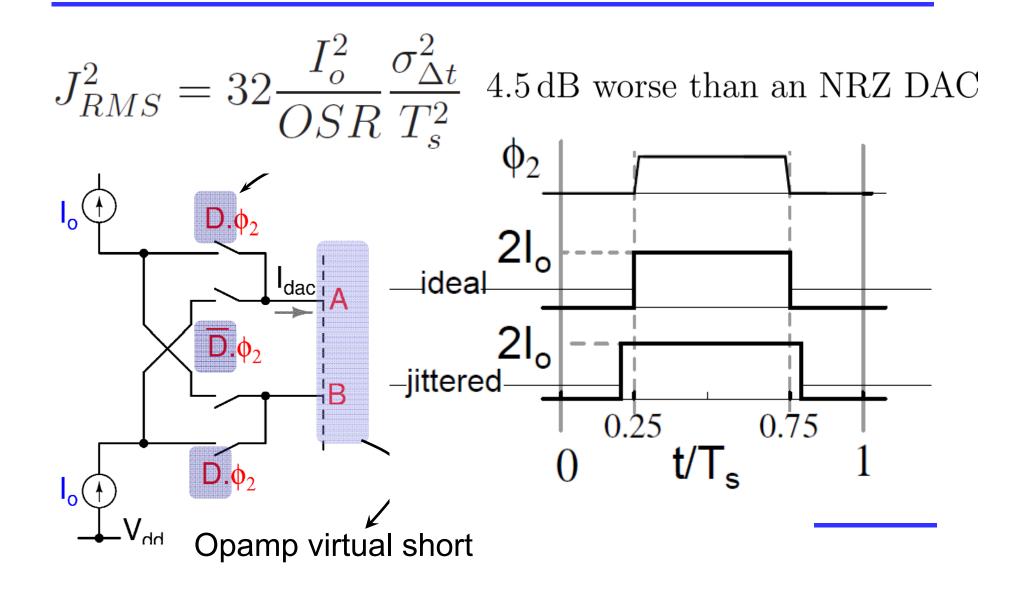

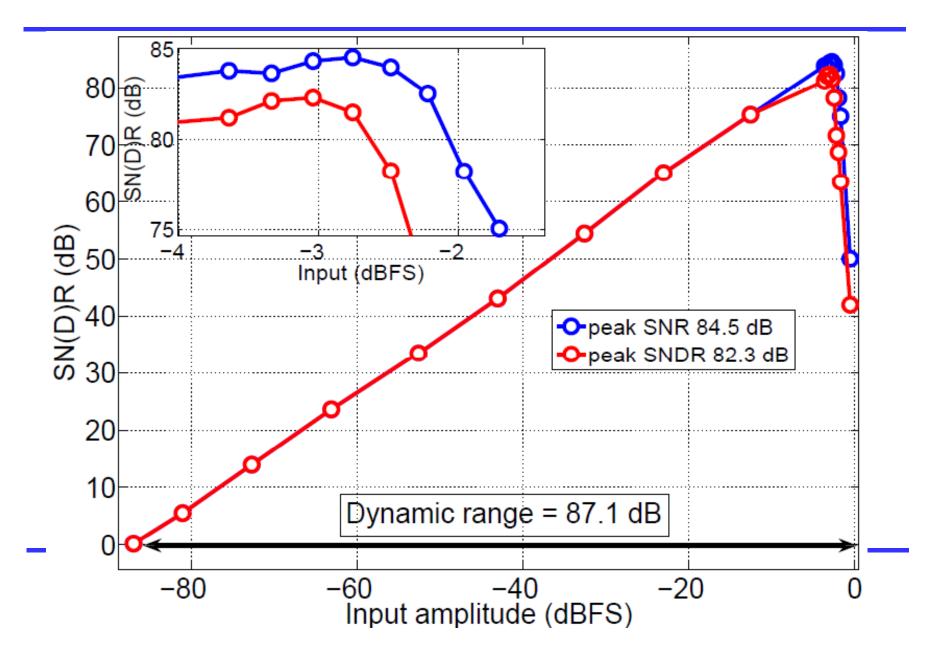

#### SN(D)R vs Input Amplitude

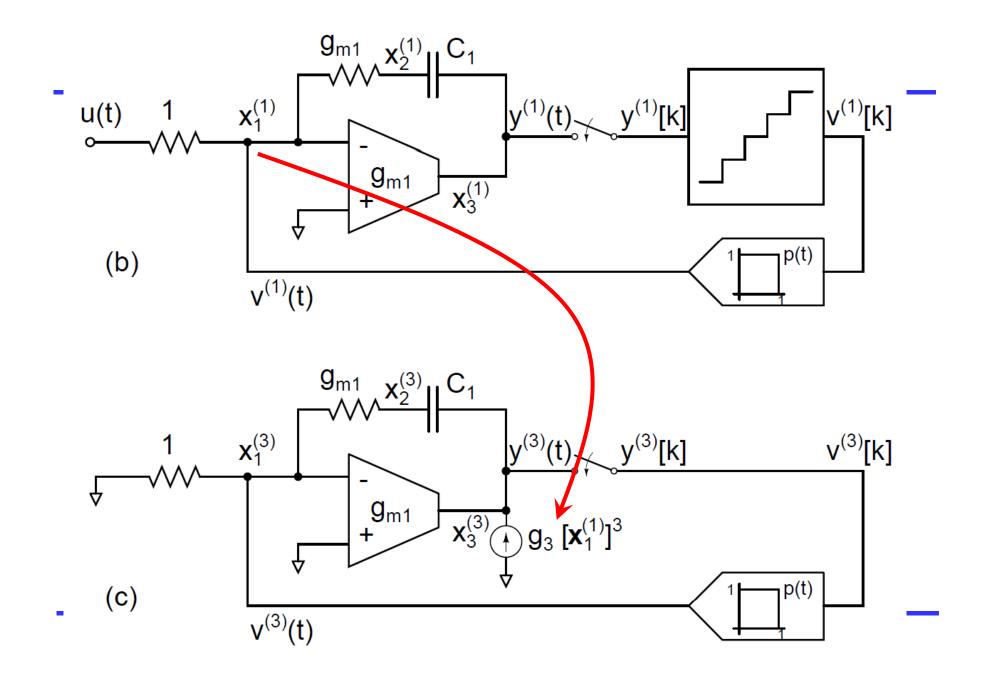

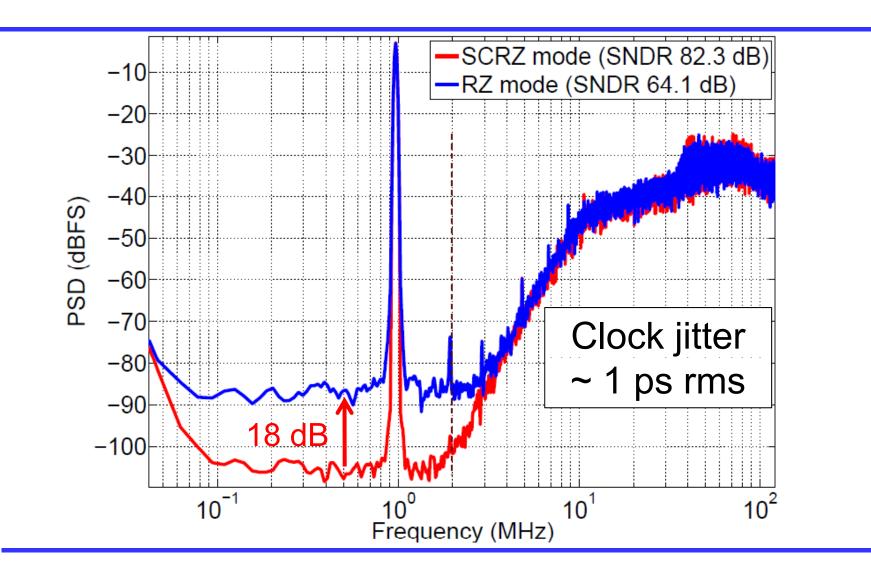

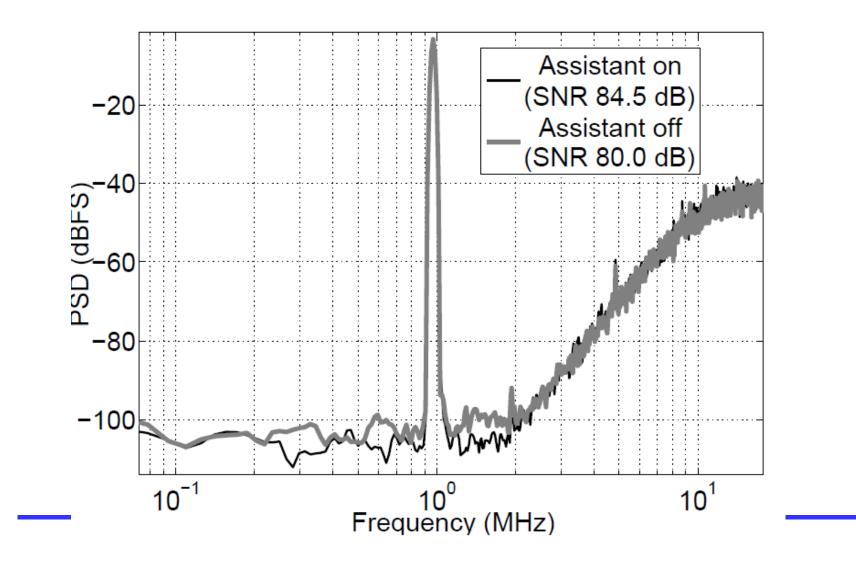

### **PSD** of modulator

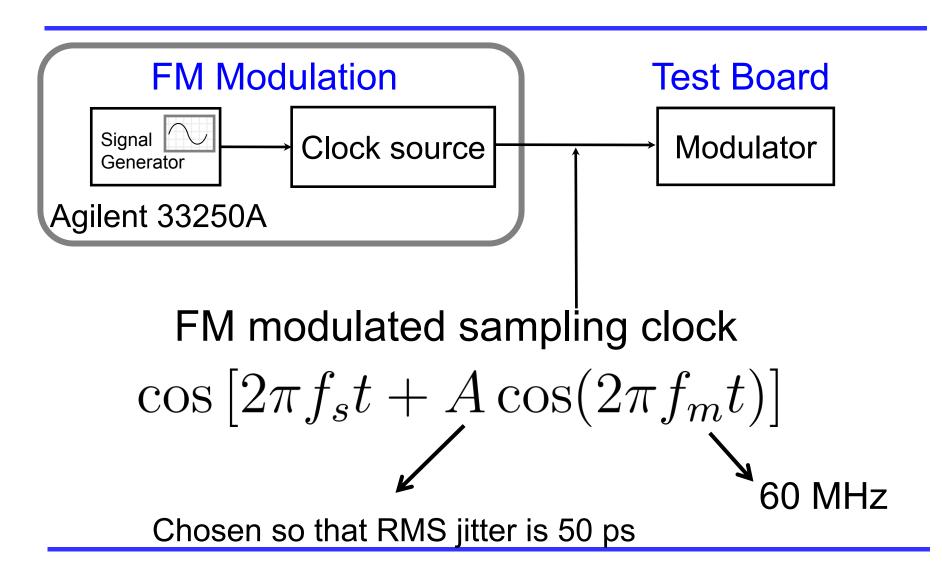

### Controlled jitter experiment

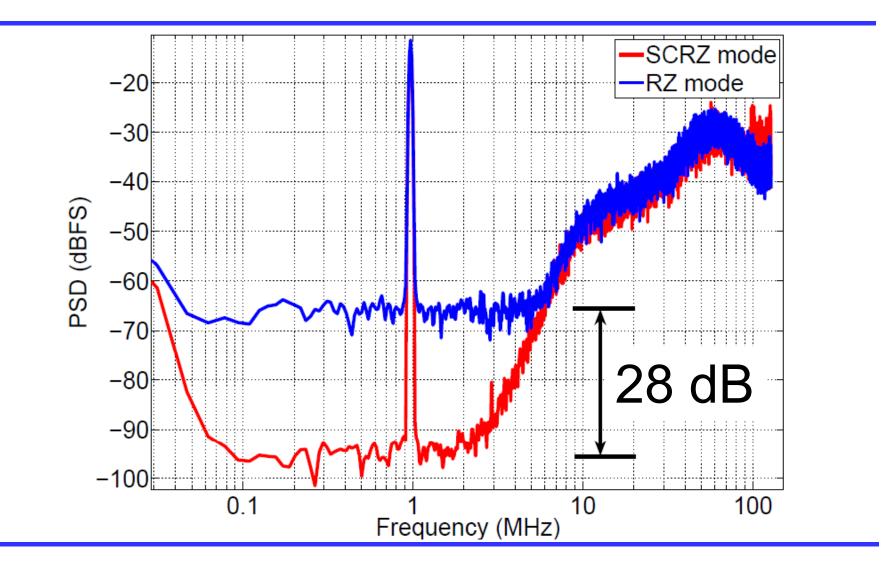

### PSD of modulator (jittery clock)

#### Effect of opamp assistance

### **Performance Summary**

| Signal Bandwidth / Clock Rate | 2 MHz / 256 MHz           |  |  |

|-------------------------------|---------------------------|--|--|

| Full Scale                    | 3.6 V <sub>pp,diff</sub>  |  |  |

| Input Swing for peak SNR      | -2.75 dBFS                |  |  |

| Dynamic Range/ SNR/ SNDR      | 87.1 dB/ 84.5 dB/ 82.3 dB |  |  |

| Active area                   | 0.38 mm <sup>2</sup>      |  |  |

| Process / Supply Voltage      | 180 nm CMOS / 1.8 V       |  |  |

| Power (including references)  | 16.5 mW                   |  |  |

| FoM (SNR)                     | 300 fJ/IvI                |  |  |

| FoM (SNDR)                    | 387 fJ/l∨l                |  |  |

| FoM (DR)                      | 168 dB                    |  |  |

## Comparison with other works

| Reference                    | This<br>Work | Anderson<br>JSSC09 | Veldho<br>JSSC03 | Gealow<br>VLSI11 | Kim<br>VLSI11 |

|------------------------------|--------------|--------------------|------------------|------------------|---------------|

| BW (MHz)                     | 2            | 1.92               | 1.23             | 1.92             | 1.95          |

| DR (dB)                      | 87           | 70                 | 83               | 83               | 79            |

| SNR (dB)                     | 84.5         | 66.4               | 83               | -                | 74.3          |

| SNDR (dB)                    | 82.3         | 62.4               | -                | 78               | 73.3          |

| Power (mW)                   | 16.5         | 5.0                | 4.1              | 2.8              | 8.55          |

| FoM <sub>DR</sub> (dB)       | 168          | 156                | 168              | 171              | 163           |

| FoM <sub>SNR</sub> (fJ/IvI)  | 300          | 768                | 145              | _                | 517           |

| FoM <sub>SNDR</sub> (fJ/lvl) | 387          | 1218               | -                | 110              | 580           |

| Tech. (nm)                   | 180          | 90                 | 180              | 40               | 65            |

| Supply (V)                   | 1.8          | 1.2                | 1.8              | 2.4/1.4          | 2.5           |

| Sampling (MHz)               | 256          | 312                | 76.8             | 245.76           | 124.8         |

| Feedback DAC                 | SCRZ         | SCSR               | SCR              | CT-SI            | CT-SC         |

## Conclusions

- Conventional feedback DACs have problems

- NRZ DAC : Rise-fall asymmetry

- RZ DAC : Jitter sensitivity

- SC DAC : Poor linearity

- The SC-RZ DAC

- Good marriage of the SC and RZ DACs

- A high performance CTDSM incorporating an SC-RZ DAC

- 87 dB DR in a 2MHz bandwidth

- 16.6mW in a 180nm CMOS process