Drew Barbier Senior Director, Product Management March 16th, 2023

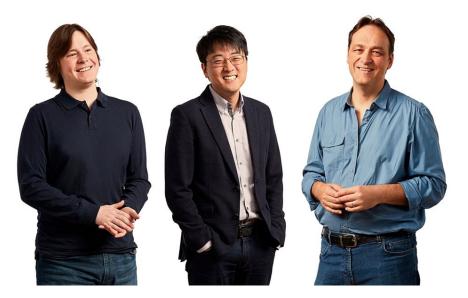

# Special Thanks - Krste Asanovic

The bulk of this presentation is from Krste Asanovic's talk:

The Past, Present, and Future of RISC-V <a href="https://www.youtube.com/watch?v=RrVRMFjYti0">https://www.youtube.com/watch?v=RrVRMFjYti0</a>

Krste Asanovic

Prof. EECS, UC Berkeley;

Chairman, RISC-V Foundation;

Co-Founder and Chief Architect,

SiFive Inc.

#### **Drew Barbier**

SiFive Inc.

Senior Director, Product Management

#### Bio

- Early joiner to SiFive (March 2017)

- ASIC Architect, Faraday

- Arm, Various

# Companies and their ISAs Come and Go

- Digital Equipment Corporation, RIP! (PDP-11, VAX, Alpha)

- Intel's dead ISAs (i960, i860, Itanium, ...)

- SPARC

## Why entrust your software investment to a proprietary ISA?

- Opened up MIPS R6 ISA in 2018, then made not open in 2019, now doing RISC-V....

- IBM POWER

- Initially proprietary, opened up in 2019 as OpenPower. Crickets...

- ARM

- Sold to Softbank in 2016

- Nvidia announced acquiring ARM 2020, deal cancelled 2022, now to IPO, ...

# Open Interfaces Are Accepted Practice!

| Field      | Open Standard    | Free, Open<br>Implementations | Proprietary<br>Implementations |  |

|------------|------------------|-------------------------------|--------------------------------|--|

| Networking | Ethernet, TCP/IP | CP/IP Many Many               |                                |  |

| OS         | Posix            | Linux, FreeBSD                | Windows                        |  |

| Compilers  | С                | gcc, LLVM                     | Intel icc, ARMcc, Xcode        |  |

| Databases  | SQL              | MySQL, PostgresSQL            | Oracle 12C, DB2 DirectX        |  |

| Graphics   | OpenGL/Vulkan    | Mesa3D                        |                                |  |

| ISA        | 555555           |                               | x86, ARM, IBM360               |  |

Why not successful open standards and multiple open-source & proprietary implementations, like other fields?

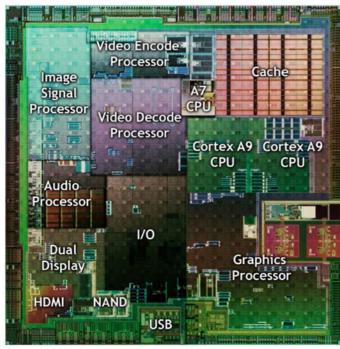

# Many ISAs on one SoC

- Applications processor (usually ARM)

- Graphics processors

- Image processors

- Radio DSPs

- Audio DSPs

- Security processors

- Power-management processor

- dozen ISAs on some SoCs each with unique software stack

#### Why?

- Apps processor ISA too big, inflexible for accelerators

- IP bought from different places, each proprietary ISA

- Engineers build home-grown ISA cores

**NVIDIA Tegra SoC**

Do we need all these different ISAs?

Must they be proprietary?

Must they keep disappearing?

What if there was one stable free and open ISA everyone could use for everything?

#### SiFive

# **RISC-V Background**

- In 2010, after many years and many research projects using MIPS, SPARC, and x86, time for architecture group at UC Berkeley to choose ISA for next set of projects

- Obvious choices: x86 and ARM

- x86 impossible too complex, IP issues

- ARM mostly impossible complex, no 64-bit in 2010, IP issues

- Began a "3-month project" during summer 2010 to develop clean-slate ISA

- Principal designers: Andrew Waterman, Yunsup Lee, David Patterson, Krste Asanovic

- Four years later, May 2014, released frozen base user spec

- many tapeouts and several research publications along the way

- Name RISC-V (pronounced "risk-five") represents fifth major Berkeley RISC ISA

# RISC-V International (RVI)

- RISC-V is a free and open Instruction Set Architecture (ISA)

- Frozen base user spec released in 2014, contributed, ratified, and openly published by RISC-V International

# RISC-V International is a non-profit entity serving members and the industry

Our mission is to accelerate RISC-V adoption with shared benefit to the entire community of stakeholders.

- Drive progression of ratified specs, compliance suite, and other technical deliverables

- ✓ **Grow the overall ecosystem / membership,** promoting diversity while preventing fragmentation

- Deepen community engagement and visibility

This alcon UEC The University of Electro-Communications UBILITE UC TECH IP Ultra Soc Unispund

# **RISC-V Ecosystem**

#### **Open-source software:**

Gcc, binutils, glibc, Linux, BSD, LLVM, QEMU, FreeRTOS, ZephyrOS, LiteOS, SylixOS, ...

#### **Commercial software:**

Lauterbach, Segger, IAR, Greenhills, WindRiver, Micrium, ExpressLogic, Ashling, Imperas, AntMicro, ...

#### Software

ISA specification Golden Model

Compatibility

#### **Hardware**

#### **Open-source cores:**

Rocket, BOOM, RI5CY, Ariane, PicoRV32, Piccolo, SCR1, Swerv, Hummingbird, WARP-V, XiangShan, BlackParrot, ...

#### **Commercial core providers:**

Alibaba, Andes, Bluespec, Cloudbear, Cobham, Codasip, Cortus, Imagination, InCore, MIPS, Nuclei, Semidynamics, **SiFive**, StarFive, Syntacore ...

#### Inhouse cores:

Nvidia, WDC, Seagate, Alibaba, +others

# RISC-V (Modest) Project Goal

# Become the industry-standard ISA for all computing devices

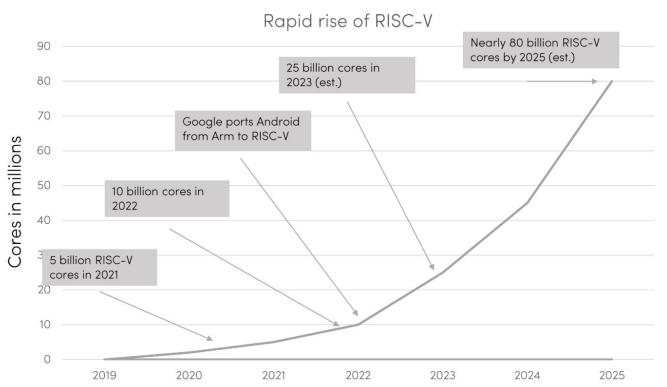

# This is happening!

Far faster, more domains, than anyone predicted Demand at every performance level (low to ludicrous) Demand for all features of all other ISAs ever built!

Using a new community ISA spec development model

©2023 SiFive

# Chip industry rapidly adopting RISC-V

### **RISC-V** in Education

RISC-V spreading quickly throughout curricula of top schools (>>10,000s undergrads/year)

# Why is RISC-V So Popular?

- Engineers sometimes "don't see forest for the trees"

- The movement is not happening because some benchmark ran 10% faster, or some implementation was 30% lower power (though that might be true)

- The movement is happening because new business model changes everything

- Pick ISA first, then pick vendor or build own core

- Add your own extension without getting permission

- Commercial, academic, and open-source ecosystems can coalesce around a single open standard

# **Comparing ISA Business Models**

|   | ISA         | Chips?                    | Architecture License? | Commercial Core IP?      | Add Own Instructions? | Open-Source<br>Core IP? |

|---|-------------|---------------------------|-----------------------|--------------------------|-----------------------|-------------------------|

| > | <b>k</b> 86 | Yes, <i>three</i> vendors | No                    | No                       | No                    | No                      |

| • | ARM         | Yes, <i>many</i> vendors  | Yes, expensive        | Yes, <i>one</i> vendor   | No (Mostly)           | No                      |

| F | RISC-V      | Yes, <i>many</i> vendors  | Yes, <b>free</b>      | Yes, <i>many</i> vendors | Yes                   | Yes, many available     |

RISC-V: The ISA that likes to say "Yes"

## **RISC-V Completeness**

- Large number of extensions ratified in 2021

- Vectors

- Full application vectors ("V") + subsets for embedded ("Zve\*")

- Hypervisor

- supports Type-1 and Type-2

- Scalar Crypto

- NIST and Shang-Mi cipher suites

- Cache Management Operations

- Block prefetch, zero, clean/flush/discard

- Virtual Memory Enhancements

- Larger pages (64KiB), PTE-based memory attributes, faster invalidate

- More extensions in flight for 2022 and beyond

- IOMMU, Advanced scalable interrupts, vector crypto, FP16, BF16, pointer masking, ...

# **Fragmentation Versus Diversity**

Fragmentation:

Same thing done different

ways

**Diversity:**Solving different problems

# How is RISC-V Avoiding Fragmentation?

Two powerful forces keep fragmentation at bay:

- Users: No one wants a repeat of vendor lock-in.

- Software: No one, not even nation state, can afford their own software stack.

Upstream open-source projects only accept frozen/ratified Foundation standards.

# **Managing Diversity**

#### Raw extensions

- Base + standard extensions + custom extensions

- Full suite of options available for experimentation and specialized uses

- Massive combinatorial space of options

#### **ISA Profiles**

- Packages of ISA extensions for given domain

- Initial set: RVI20 (basic), RVA20/22/23 (application processor)

- Factor out common ISA combinations for use in platform standards

#### **Platform standards**

- Hardware/software standards for platforms (much more than just ISA)

- Initial focus OS-A platform for Unix-like OS (includes IOMMU, AIA, etc)

### SiFive: The RISC-V Founder and Brand Standard

#### The Inventors of RISC-V

SiFive's founders are the same UC Berkeley professor and PhDs who invented the RISC-V Instruction Set Architecture (ISA) in 2010

The Most Respected Private Semiconductor Company 2022

©2023 SiFive 23

300+

Design Wins

100+

Customers

8 of 10

Top semiconductor companies work with us 500+

Employees

\$2.5B+

Valuation

# SiFive broad IP portfolio

64-bit high-performance feature-rich OS capable application processors

32/64-bit real time scalable performance deeply embedded processors

#### SiFive Automotive

#### X280-A

Al acceleration instructions 512b vector length ASIL B, D and B/D

#### **S7-A**

64-bit, High performance embedded ASIL D

#### E6-A

32-bit, Balanced performance and efficiency ASIL B, D

#### SiFive Intelligence

#### X200-Series

Al processor for Edge and Data Center ML applications Al acceleration instructions 512b vector length

#### SiFive Performance

#### P200-Series

>4.6 SpecINT2k6/GHz 2-wide in-order core 256b vector length RVA20 WorldGuard

#### P400-Series

>8 SpecINT2k6/GHz

3-wide OoO core

128b vector length

Hypervisor extension

Vector crypto

IOMMU & AIA

RVA22

WorldGuard

#### P500-Series

>8.6 SpecINT2k6/GHz 3-wide OoO core Hypervisor extension RVA20 WorldGuard

#### P600-Series

>12 SpecINT2k6/GHz 4-wide OoO core 128b vector length Hypervisor extension Vector crypto IOMMU & AIA RVA22 WorldGuard

#### SiFive Essential

S2-Series

**E2-Series**

64-bit, Area optimized

Smallest, most efficient

#### **U6-Series**

64-bit, High performance

#### **S6-Series**

64-bit, Power efficiency

#### E6-Series

Balanced performance and efficiency

#### **U7-Series**

64-bit, Superscalar performance

#### **S7-Series**

64-bit, High performance, embedded

#### **E7-Series**

32-bit, Optimized performance

25

# SiFive Performance<sup>TM</sup> Family

Market leading RISC-V

Application Processors

- ◆ Performance density leadership

- First with latest RISC-V features,

standards, and technology

- High performance with optimized power efficiency

- SiFive momentum with NASA, Google,

and Intel Horse Creek

22023 SiFive

# SiFive Performance Family

**2023 Product Lineup**

# SiFive® Intelligence™ X280 Processor

Optimized for the modern workload

- Highly optimized for AI models and software frameworks

- Enables highly efficient, simple system design

- Ideal companion to custom NN hardware accelerators

- RISC-V Vectors brings market leading performance and power efficiency

- Performance scalability with multi-cluster, multi-core configurability

- Strong momentum in image processing and data center compute applications 28

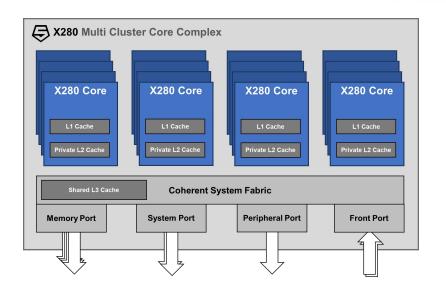

# Scaling Performance with Multi-core

#### **Extended Performance, Simple Software**

- Flexibility to configure number of clusters and cores to meet performance at minimal area, power

- Full data Coherency across all cores in the multi-core system

- Support of Linux OS to simplify multi-core software usage model, data management

- Multiple SoC connectivity ports offering coherent memory mapped accesses across all cores

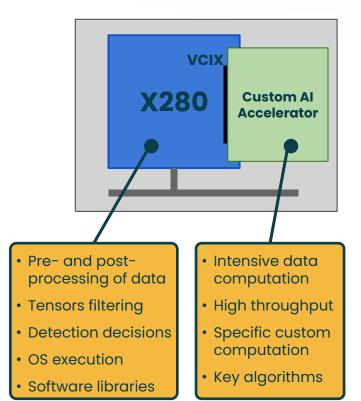

# Al dataflow optimization

#### **Workload and task management**

- Simplify AI accelerator design for required use cases

- Provide comprehensive data management, dataflow and housekeeping reducing latency, power and area

- Vector Coprocessor Interface Extension (VCIX) enables tightly coupled connectivity to an AI accelerator for optimized performance

- Linux OS with single toolchain for complete application control

2023 SiFive

# SiFive Thank you

#### SIFIVE.COM

©2023 SiFive, Inc. All rights reserved. All trademarks referenced herein belong to their respective companies. This presentation is intended for informational purposes only and does not form any type of warranty.

Certain information in this presentation may outline SiFive's general product direction. The presentation shall not serve to amend or affect the rights or obligations of SiFive or its licensees under any license or service agreement or documentation relating to any SiFive product. The development, release, and timing of any products, features, and functionality remains at SiFive's sole discretion.