|

|

|

|

Technical

Seminar Distinguished

Lecturer Series |

|

|

|

|

|

A Basic Property of MOS Transistors and its Circuit

Implications

|

|

|

DATE/TIME

Wednesday, March 24, 2004 (4:30pm to 6:30pm) |

|

PLACE

Bldg. 1 Room WLL2/3 (Agilent Technologies,

Fort Collins, CO) |

|

Non-Agilent

Attendees: Please arrive punctually at 4:15-4:30pm as you will

need to be escorted to the seminar

room. |

|

DIRECTIONS

From I-25, take Harmony Road Exit (Exit

265) westbound, and enter Agilent/HP campus on right. Agilent/HP

campus is on the NE corner of Harmony Road and Ziegler Road.

Proceed to Bldg. 1 Lobby to sign-in and meet host for escort to Room

WLL2/3. |

|

|

ABSTRACT

The MOS transistor drain current is the

(linear) superposition of independent and symmetrical effects of

source and drain voltages. This basic property is not affected

by the geometry or symmetry of the transistor, by the level of gate

voltage or by narrow channel effects. However, it progressively

deteriorates when the channel is shortened. Except in weak

inversion, it is also degraded by structural non-homogeneities along

the channel. This property can be exploited by means of the

concept of pseudo-resistors to implement transistor-only linear

circuits in the current domain. |

|

PRESENTATION SLIDES

pdf |

|

REFERENCES |

- E. Vittoz, C. Enz, and F. Krummenacher,

"A basic property of MOS transistors and its circuit implications,"

Nanotech 2003 Workshop on Compact Modeling (San

Francisco, CA), Feb. 2003. pdf

- E. Vittoz, "Pseudo-resistive networks

and their applications to analog collective computation," Proc.

MicroNeuro (Dresden, Germany), Sep. 1997.

pdf

|

|

|

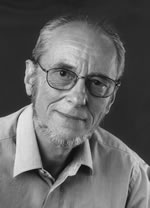

PROF.

ERIC

VITTOZ (Centre

Suisse d Électronique et de Microtechnique SA, Neuchatel, Switzerland)

|

|

Eric Vittoz

received his E.E. degree from Polytechnical School University of

Lausanne in 1961 and his Ph.D. from EPFL (Swiss Institute of Technology

Lausanne) in 1969. He joined the Centre Electronique Horloger (CEH) in

May 1962, became head of the Advanced Circuits Department at CEH in 1967

and was appointed Vice Director and head of the Applications Division of

CEH in 1971. In 1984, he took the responsibility for the Circuits

and Systems Research Division of the newly founded CSEM (Swiss Center for

Electronics and Microtechnology), where he was appointed Executive

Vice-President in 1991, head of Integrated Circuits and Systems, then head

of Advanced Microelectronics after 1997. In 1999, he partially

retired from CSEM with the position of Chief Scientist. Since 1975, he

has been lecturing and supervising undergraduate and graduate students

who are working on projects in analog circuit design at EPFL.

|

|

In 1982 he

became a professor at EPFL. Dr. Vittoz is a

Fellow of the IEEE and served as an SSCS AdCom member from 1996 to 1999.

Vittoz was involved in the formation of the one of the IEEE Solid-State

Circuits Society. He also is a member of the steering committee of

ESSCIRC, the European Solid-State Circuits Conference, for which the

SSCS provides technical co-sponsorship. Vittoz

holds more than 25 U.S. patents and has authored more than 36 IEEE

publications. In 1994 he presented the plenary talk at the ISSCC titled

“Low-power design: Ways to approach the limits.” He also also given

numerous Short Courses at the conference over the years and is well

known for his contributions to Analog Design Courses of MEAD, Eurochip,

and Iberchip.

|

|

|

PHOTOS

Courtesy of Bob Barnes & Tin Tin Wee |

|

|

|

|

|

|