# Introduction to Deep Submicron CMOS Device Technology & Its Impact on Circuit Design

Alvin L.S. Loke, Tin Tin Wee & James R. Pfiester Agilent Technologies, Fort Collins, CO

> IEEE Solid-State Circuits Society December 8, 2004

## Outline

- CMOS Technology Trends

- MOSFET Basics

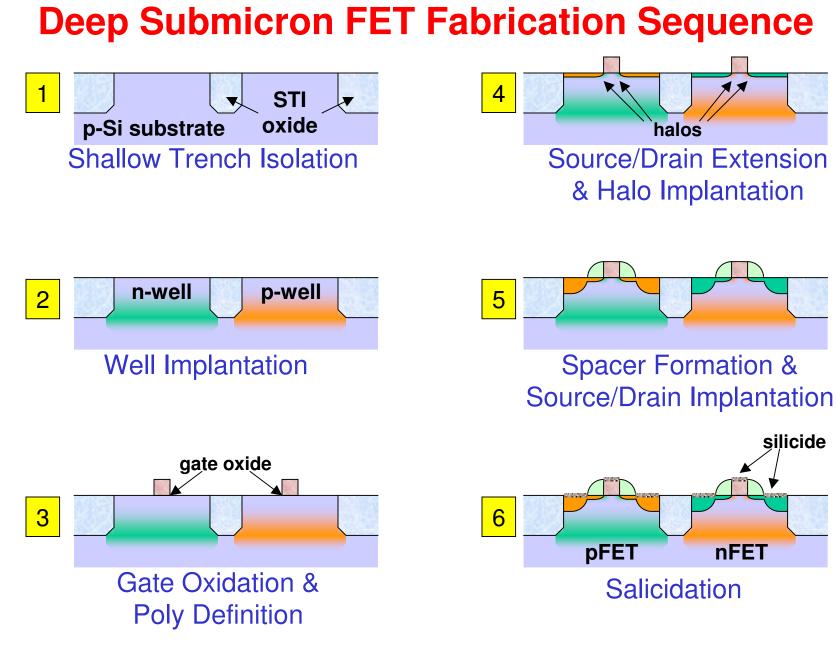

- Deep Submicron FET Fabrication Sequence

- Enabling Technologies

- Second-Order Consequences

- Dealing with Process Variations in Manufacturing

- Conclusions

#### **Disclaimer**

- A proper *introduction* alone would take weeks, let alone a whole semester

- Need to omit lots of nitty-gritty yet important process details

- Hopefully, we'll still learn lots of *cool* device physics

☺ ☺ ☺ ☺ ☺ ☺ ☺ ☺

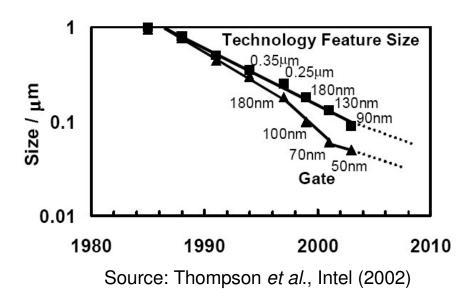

### Where is CMOS Technology Today?

- Scaling is still alive & well

- 130nm now standard fare

- 90nm already in volume manufacturing

- 65nm integration tough but not insurmountable

- Some key trends:

- Aggressive scaling of gate CD (critical dimension)

- Scaling driven by exclusively by digital circuit needs

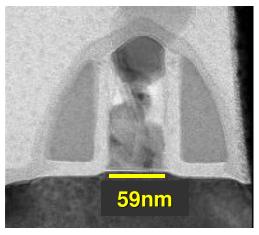

90nm Technology

Source: Wu et al., TSMC (2002)

## Why Aggressive FET Scaling?

$$t_{delay} \approx \frac{C_{load} \Delta V}{I_{FET}}$$

- The road to higher digital performance

- $C_{load} \downarrow \rightarrow$  reduce parasitics (largely dominated by interconnect now)

- $\Delta V \downarrow \rightarrow$  reduce  $V_{DD}$  or logic swing, need for core & I/O FET's

- $I_{FET} \uparrow \rightarrow$  all about moving charge quickly

- Hiccups along the way

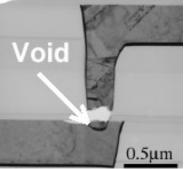

- Interconnect scaling much more difficult than anticipated, especially Cu/low-K reliability

- FET leakage doesn't go well with  $V_{\mbox{\scriptsize DD}}$  scaling

- How to beef up I<sub>FET</sub>?

- Tweak with  $\mu,\,C_{\text{ox}},\,L$  &  $V_{\text{T}}$

Stress-Induced Voiding

Got redundant vias?

- $I_{dsat} \approx \frac{1}{2} \mu C_{ox} (W/L) (V_{GS} V_T)^2$

- Technology upgrades not necessarily compatible with analog design

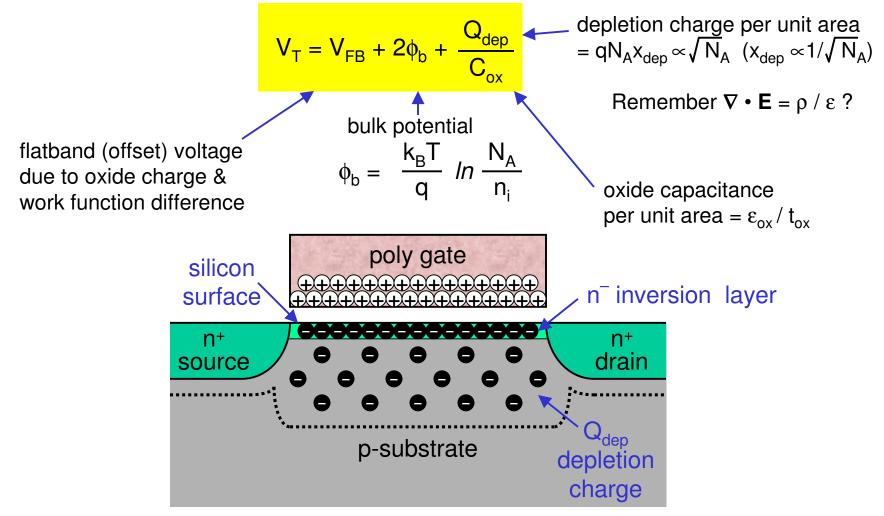

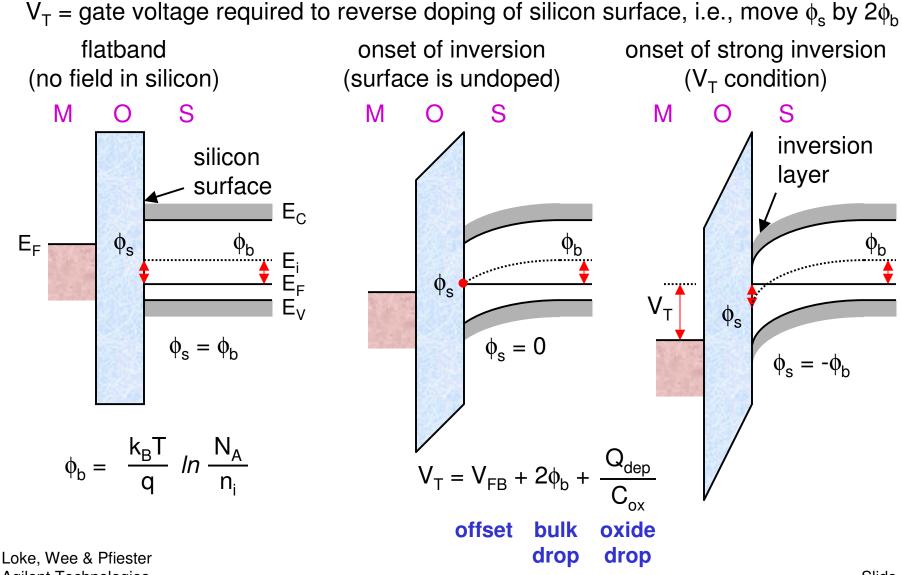

### The Most Basic MOS Concept – V<sub>T</sub>

V<sub>T</sub> = FET ON voltage, i.e., gate voltage required to form inversion layer connecting source & drain; shorts out back-to-back pn-junctions with substrate

#### More MOS Fundamentals (Energy Band Diagram) Formation of Inversion Layer

Agilent Technologies

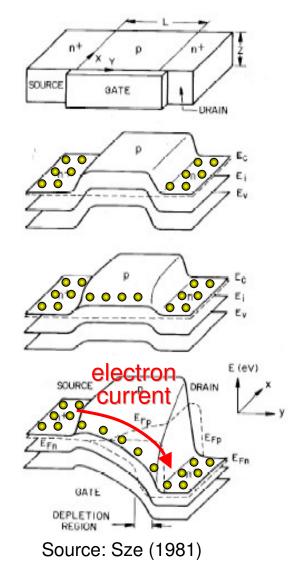

#### Reintroducing (...drum roll...) the MOSFET

Loke, Wee & Pfiester Agilent Technologies  $V_{GS} = 0$   $V_{DS} = 0$  (no net current flow) Large source barrier (back-to-back diodes)

$V_{GS} \approx V_T$   $V_{DS} = 0$  (no net current flow) Source barrier is lowered Surface is inverted

$V_{GS} > V_T$  $V_{DS} > 0$  (net source-to-drain current flow) Carriers easily overcome source barrier Surface is strongly inverted

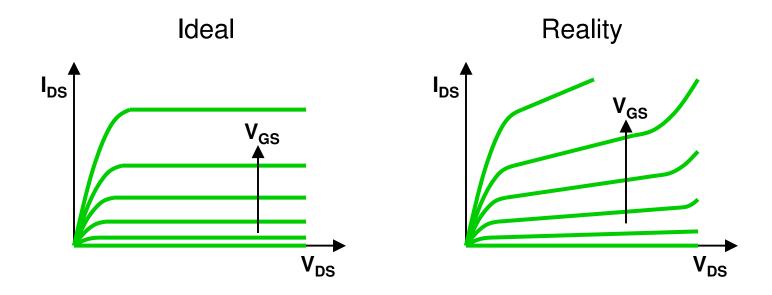

#### Life's Never So Perfect

#### *Ideal MOSFET = voltage-controlled current source*

Now plunging deep into a lot of interesting second-order effects...

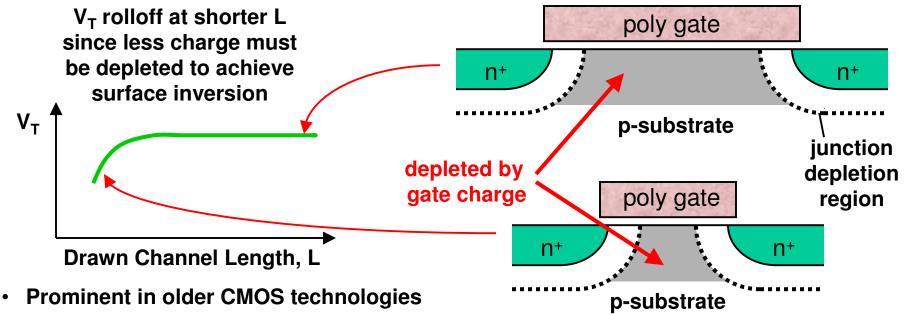

### Warp Speed Ahead → Short-Channel Effect (SCE)

- How to minimize SCE?

- Minimize volume of charge depleted by source/drain junctions

- Higher substrate doping for thinner junction depletion regions ( $x_{dep} \propto 1/\sqrt{N}$ )

- Higher V<sub>T</sub> & junction capacitance → not consistent with scaling

- Shallower source/drain junctions

- Higher source/drain resistance → smaller drive currents

- Tighter gate coupling to surface potential

- Thinner gate oxide of surface potential  $\rightarrow$  direct tunneling leakage

- Higher K gate dielectrics

- Other SCE problems: large electric fields  $\rightarrow$  carrier v<sub>sat</sub> &  $\mu$  degradation

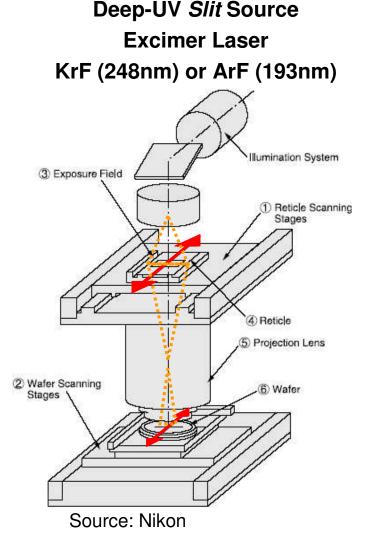

#### **Step-and-Scan Projection Lithography**

#### Rayleigh's Equation: Resolution $\propto \lambda$ / NA

- Previous generations used G-line (436nm) & I-line (365nm) steppers (refractive 4X-projection optics)

- Technology trends

- More aggressive CD's  $\rightarrow$  shorter  $\lambda$

- Higher NA lenses  $\rightarrow$  \$\$\$

- Larger reticle field sizes → \$\$\$

- Step-and-scan enabled resolution & CD control for critical layers beyond 0.35µm node

- Slide reticle & wafer across narrow slit of light

- Aberration-free high-NA optics only required along 1-D but now requires high-precision constant-velocity stages

- Still much cheaper than optics optimized in 2-D

- Rectangular reticle size → shorter edge limited by slit width

- Relatively weak intensity of deep-UV source required development of very sensitive *chemically-amplified* resists for throughput

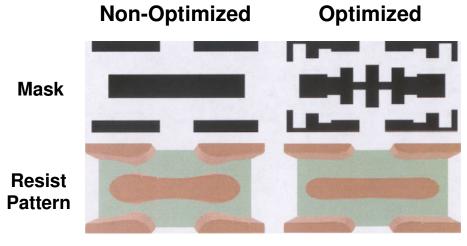

## **More Lithography Tricks**

- Sharp features (e.g., corners) are lost because diffraction attenuates & distorts higher spatial frequencies (low-pass optical filtering)

- Compensate for diffraction effects for features much smaller than exposure  $\lambda$  $\rightarrow$  manage sub- $\lambda$  constructive & destructive interference

- Software complexity during mask fabrication

#### **Optical Proximity Correction (OPC)**

- Add scattering features to sharpen corners

- Used extensively for poly gate definition

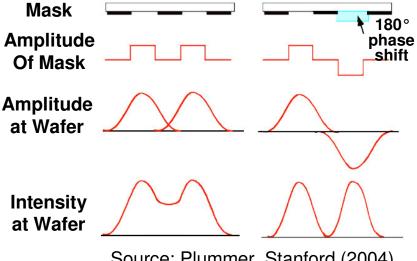

#### Phase Shift Masking (PSM)

- Modulate optical path through mask

- Used extensively for contacts & vias

- Complicated for irregular patterns

Source: Socha, ASML (2004)

Source: Plummer, Stanford (2004)

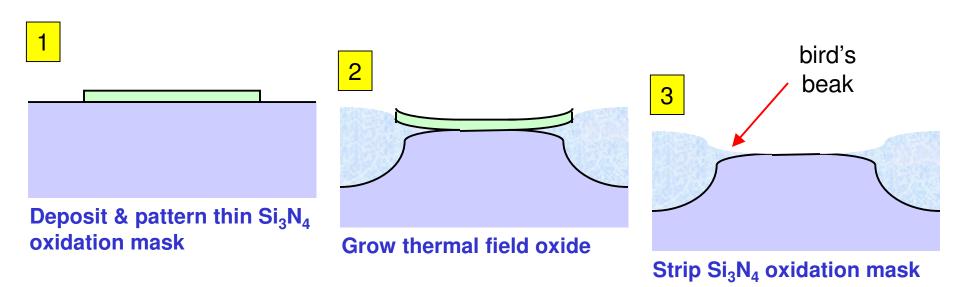

#### **Basics of LOCOS Isolation – 0.35µm & Earlier**

Industry played lots of tricks to reduce width of bird's beak & make field oxide coplanar with active areas

#### Depth of Focus $\propto$ Resolution / NA

- Required very careful understanding of visco-elastic properties of oxide during thermal oxidation

- LOCOS ran out of gas beyond 0.25um

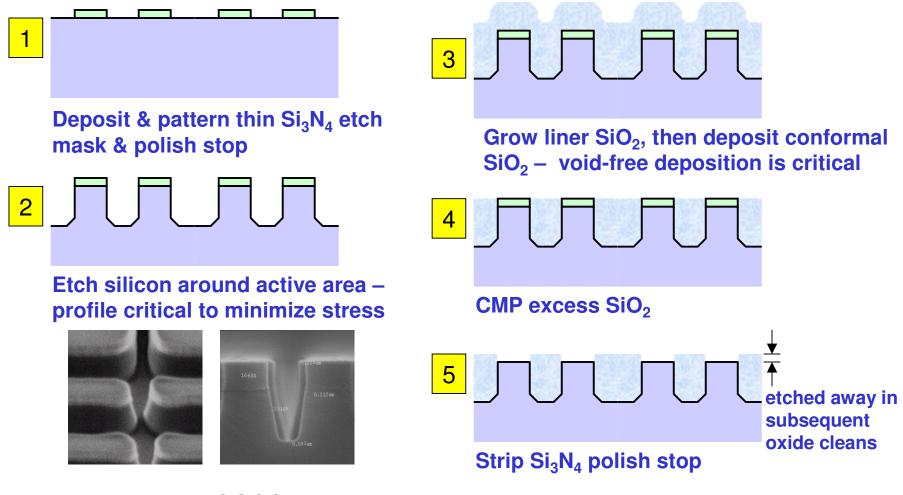

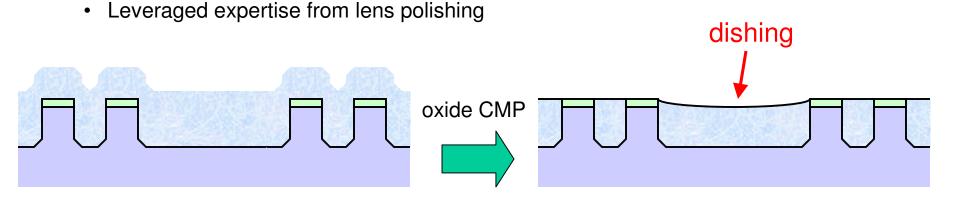

### Shallow Trench Isolation (STI) – 0.25 µm & Beyond

#### Advantages over LOCOS technologies

- Reduced active-to-active spacing (no bird's beak)

- Planar surface for gate lithography

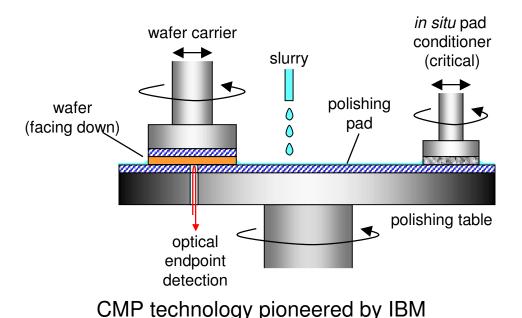

#### Let's Think a Little Bit More About CMP

- Ideal world for CMP: want *perfect* periodicity of patterns throughout wafer

- Need to throw in dummy features to minimize pattern density variations

→ optimize planarity

- Polishing pad will flex

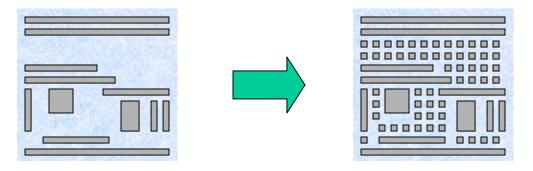

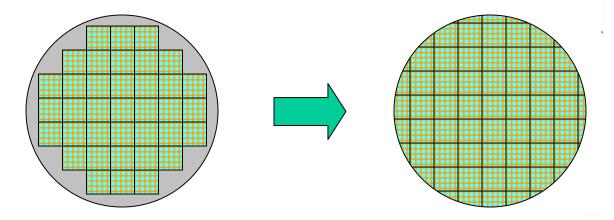

## **Always Think Dummies in Any CMP Process**

- Dummification is key to minimize topography in any CMP process

- · Add dummy patterns to open spaces to minimize layout density variations

- $\rightarrow$  Added design complexity to check layout density & insert dummy patterns

• Also critical to step dummy dies along wafer circumference

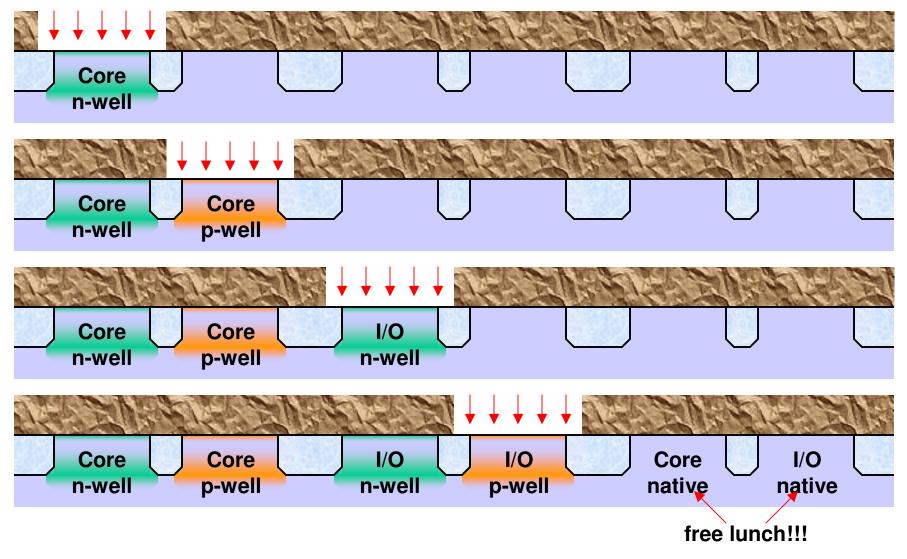

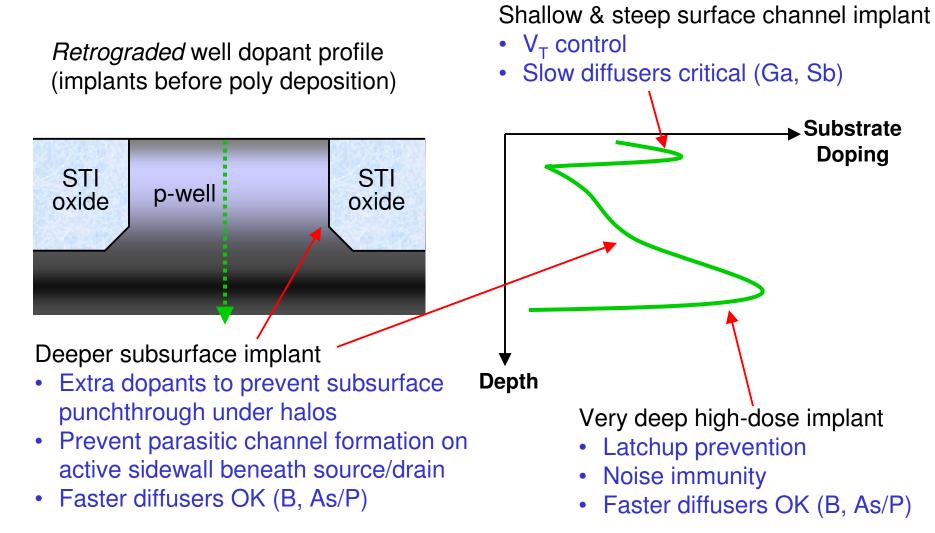

### Well Implants – Lots of Transistor Variants

- core vs. I/O FET's, core low-/nom-/high-V $_{\rm T}$  variants, native vs. implanted

## **Well Engineering**

Implant order matters to prevent ion channeling, especially for the shallow implant

## **Gate Oxidation**

- Need two gate oxide  $t_{ox}$ 's thin for core FET's & thick for I/O FET's

- Grow 1<sup>st</sup> oxide, strip oxide for core FET's, grow 2<sup>nd</sup> oxide

- Gate oxide is really made of silicon oxynitride (SiO<sub>x</sub>N<sub>y</sub>)

- N content prevents boron penetration from p+ poly to channel in pFET's

- Side benefit increased  $\epsilon_{\text{ox}}$

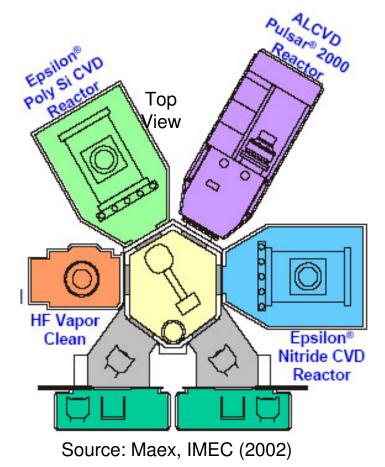

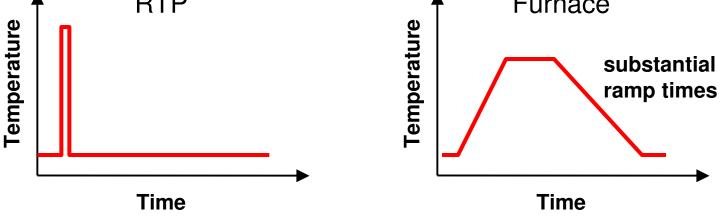

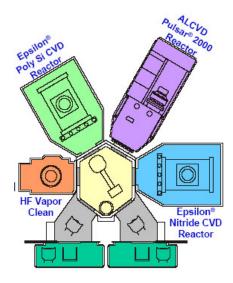

#### Subroutine on Equipment Technology

- Gate oxide no longer furnace grown

- Multi-chamber *cluster tools* now ubiquitous

- Pre-oxidation clean, gate oxidation & poly/ARL deposition performed in separate chambers without breaking vacuum

- Better thickness & film compositional control (native SiO<sub>2</sub> grows instantly when exposed to air)

- Fast minutes-seconds per wafer vs. hours per wafer batch

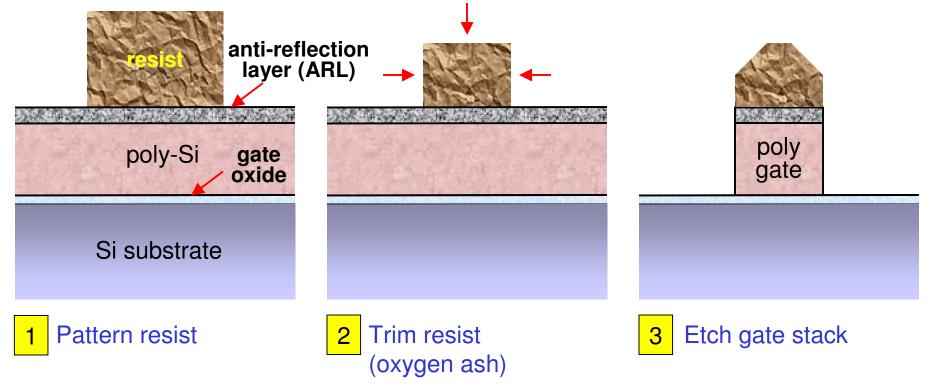

## **Poly Gate Definition**

• Gate CD way smaller than lithography capability, even with mask tricks

- *Process control is everything* resist & poly etch chamber conditioning is critical (lesson to remember: don't clean those residues in tea cups or woks)

- Way to get smaller CD's to trim more (requires tighter control)

- Dummification also necessary for poly mask

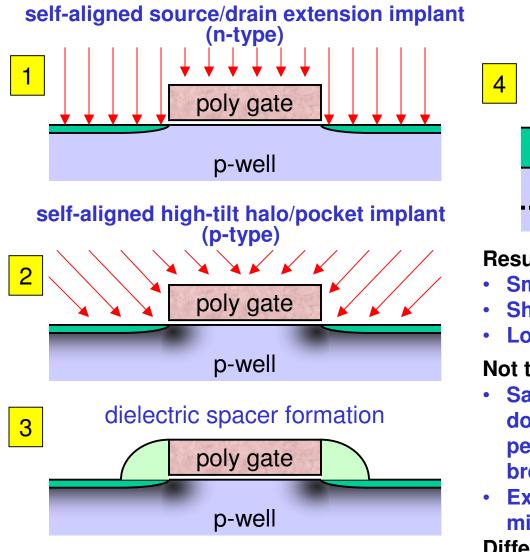

#### **Source/Drain & Channel Engineering**

Loke, Wee & Pfiester Agilent Technologies

#### **Resulting structure has:**

- Smaller SCE

- Shallow junction where needed most

- Low junction capacitance

#### Not to be confused with LDD's in I/O FET's

- Same process with spacers but lightly doped drain (LDD) is used for minimizing peak *E* fields that cause hot carriers & breakdown

- Extensions need to be heavily doped to minimize series resistance

- Different halo & extension/LDD implants for each FET variant

####

- Initially developed for short anneals

- Impossible to control short thermal cycles in furnaces

- Want minimum diffusion for shallow & abrupt junctions

- Process steps:

- Annealing  $\rightarrow$  repair implant damage

- Oxidation  $\rightarrow$  gate oxide

- Nitridation → spacers, ARL

- Poly deposition → gate

- RTP in single-wafer multi-chamber cluster tools

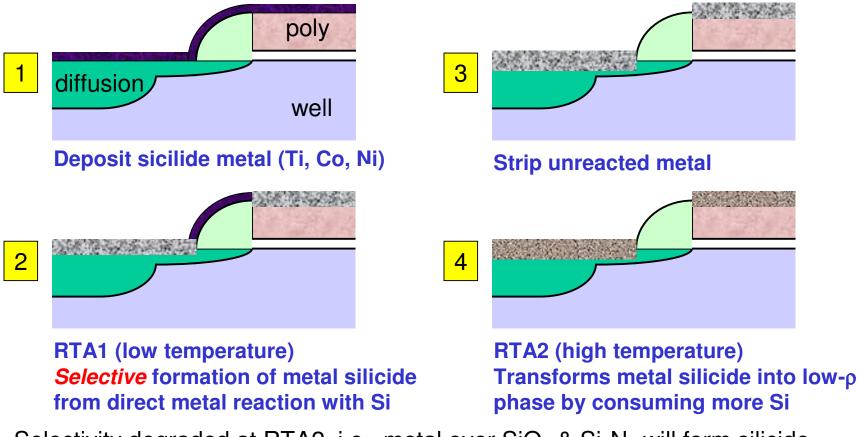

## Self-Aligned Silicidation (Salicidation)

Need to reduce poly & diffusion R<sub>s</sub>, otherwise get severe IFET degradation due to voltage drops from contacts to intrinsic FET (source degeneration)

- Selectivity degraded at RTA2, i.e., metal over SiO<sub>2</sub> & Si<sub>3</sub>N<sub>4</sub> will form silicide

- Technology progression:  $TiSi_x \rightarrow CoSi_x \rightarrow NiSi_x$

- Scaling requires smaller silicide grain size to minimize R<sub>s</sub> variations

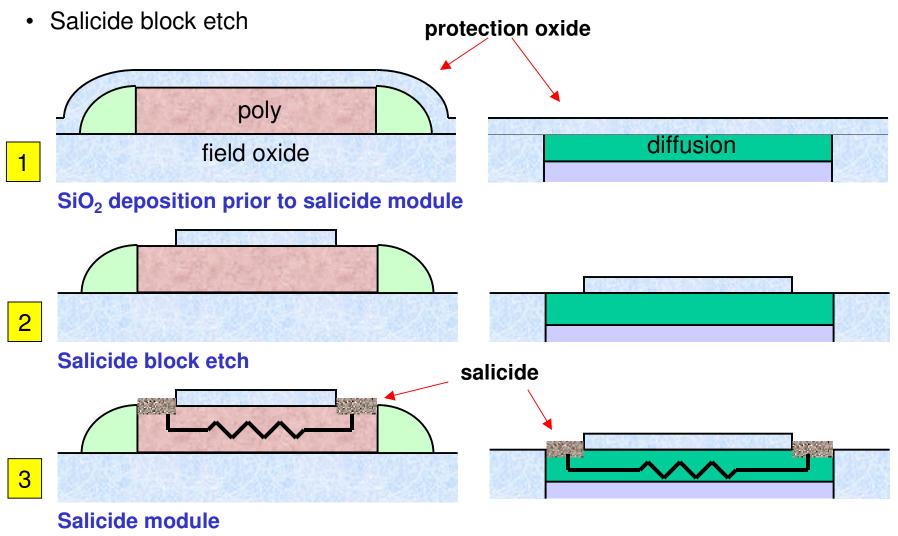

## **Making Cheap Resistors**

• Only one extra mask can buy you unsalicided poly & diffusion resistors

#### So What Do All These Cool Process Upgrades Mean To Designers?

• Short answer...

some extras but plenty more non-idealities to worry about, *especially* in analog land !!!

- We'll look at:

- Poly depletion & charge centroid effects

- $V_T$  effects

- Reverse short- & narrow-channel effects

- Well proximity effect

- Active area mechanical stress effect

- Leakage current mechanisms

- Multiple V<sub>T</sub> devices

- Impact of halos

- Manufacturability

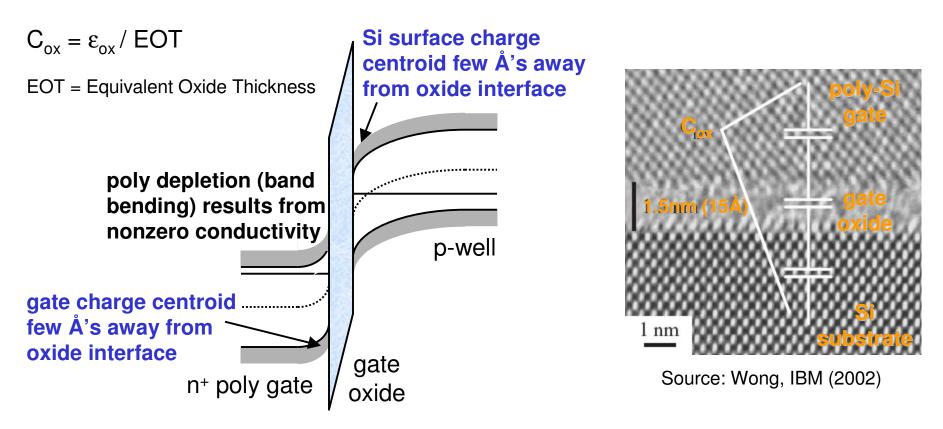

#### **Poly Depletion & Surface Charge Centroid Effects**

- Increasing discrepancy between electrical & physical gate oxide thicknesses since charges are not intimately in contact with oxide interface  $\rightarrow C_{ox}$  not as small

- + C<sub>ox</sub> must account for gate & Si surface charge centroids as well as  $\epsilon_{Si}$

- Modeled in BSIM4 → more accurate I-V & C-V calculations

- Motivation for high-K gate dielectrics & metal/silicided gate technology

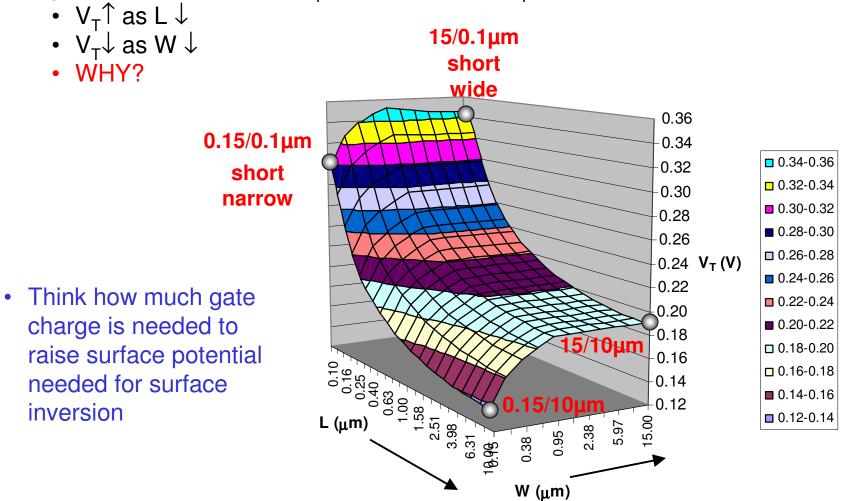

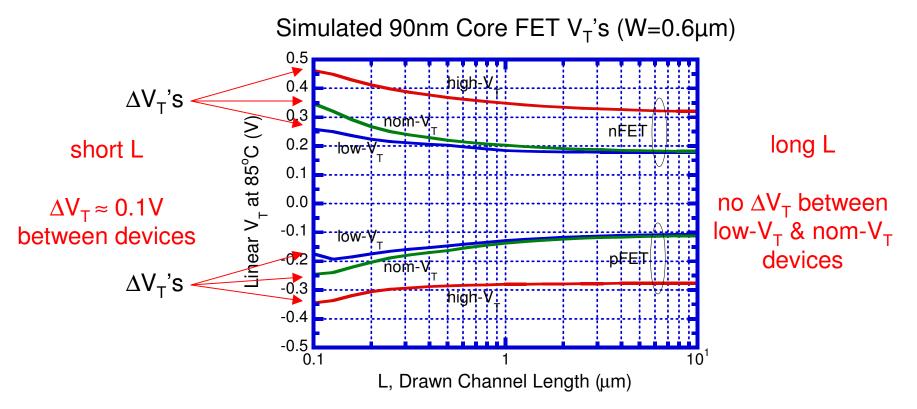

### **V<sub>T</sub> Variations Across FET L & W in 90nm**

- Wondered why so many transistor L & W bins in SPICE models?

- e.g., SPICE model linear  $V_{\tau}$ 's for 90nm nom- $V_{\tau}$  core nFET @ 85 °C

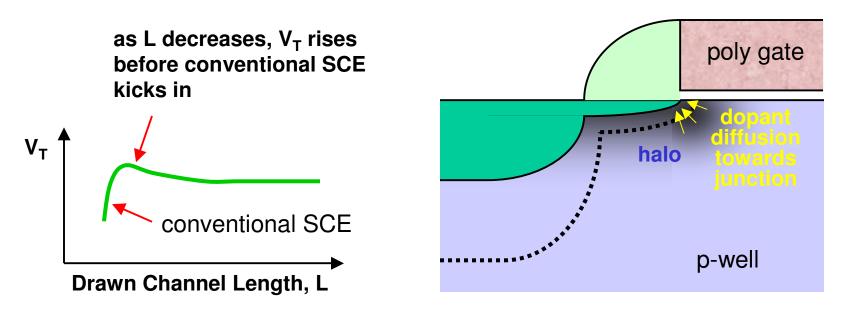

#### **Reverse Short-Channel Effect (RSCE)**

- Mechanism Transient Enhanced Diffusion (TED)

- Damage from halo implant creates crystalline defects that accelerate diffusion of dopants in subsequent anneals where damage is eventually repaired

- Dopants migrate to source-to-substrate junction & raise source-to-channel barrier height

- V<sub>T</sub> increases

- Target  $L_{min}$  at  $V_T$  peak for good process margin, i.e., minimize  $V_T$  sensitivity to poly-CD variations

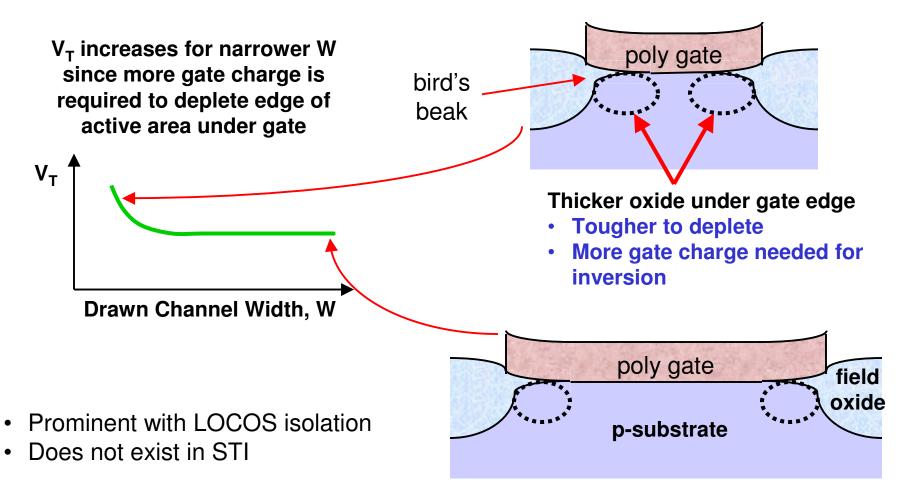

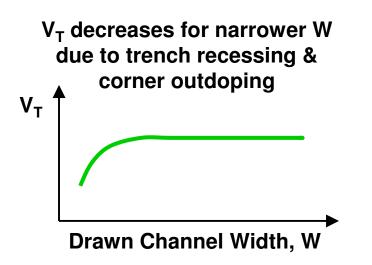

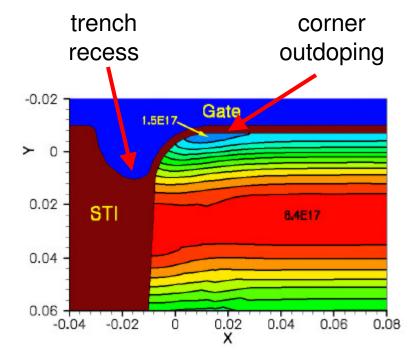

#### **Narrow-Channel Effect (NCE)**

## **Reverse Narrow Channel Effect (RNCE)**

- Prominent in STI technologies

- Concentration of electric field

lines terminating at corner

- Trench recess results from faster oxide etch rate at STI edge during pre-oxidation HF wet-cleans

Source: Burenkov & Lorenz, Fraunhofer Institut (2003)

Edge device turns on before center device

→ I-V kink in very narrow devices

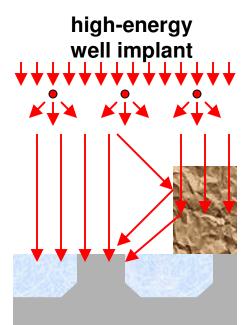

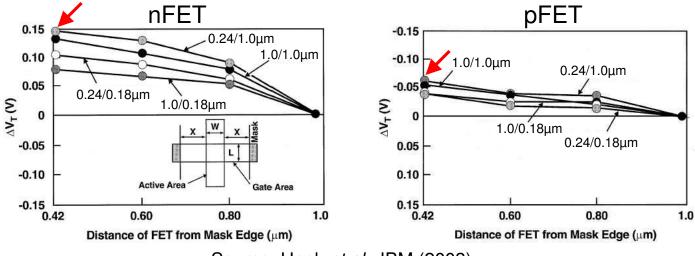

## **Well Proximity Effect**

- |V<sub>T</sub>| ↑ if FET is too close to edge of well resist mask due to extra channel dopants from lateral scattering off resist sidewall into active area during well implants

- $|\Delta V_T|$  depends on:

- FET distance to well mask edge

- FET orientation

- implanted ion species/energy

- Most impact on narrow- & long-channel devices

- No impact on native FET's

- Well mask matching critical especially in analog layout

- Not modeled in BSIM4

Source: Hook et al., IBM (2003)

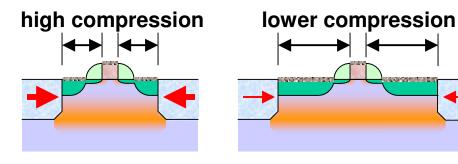

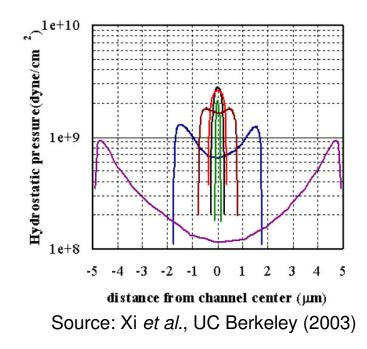

#### **Active Area Mechanical Stress Effect**

- Silicon is *piezoresistive* electrical properties depends on mechanical stress state

- Stress affects m<sup>\*</sup>, μ, E<sub>g</sub>, V<sub>T</sub>, body effect, DIBL, ...

- Compression → slower nFET, faster pFET

- Tension → faster nFET, slower pFET

- STI  $\rightarrow$  compression in Si channel due to 10x CTE mismatch between Si & SiO<sub>2</sub>

- $I_{dsat}$ 's can change by as much as 10-15%  $\rightarrow$  affects digital device ratios

- Channel stress is strong function of distance from poly to active edge

- Known for some time

- Can play tricks with tensile spacer & silicide films to relieve channel stress

- Basis of high-µ<sub>n</sub> strained-Si technology

- Modeled in BSIM4 not BSIM3 (SA, SB)

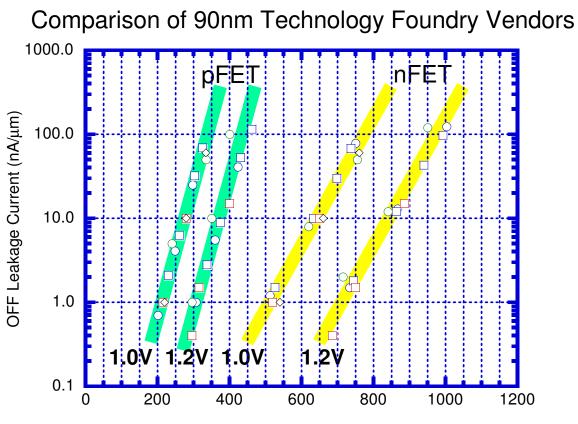

## **ON vs. OFF Current Benchmark**

ON Drive Current ( $\mu$ A/ $\mu$ m)

- "No free lunch" principle prevails again: high I<sub>ON</sub>  $\rightarrow$  high I<sub>OFF</sub>

- $V_T$ 's not scaling as aggressively as  $V_{DD}$

- Technology providers offer variety of V<sub>T</sub>'s on same die to concurrently meet high-speed vs. low-leakage needs

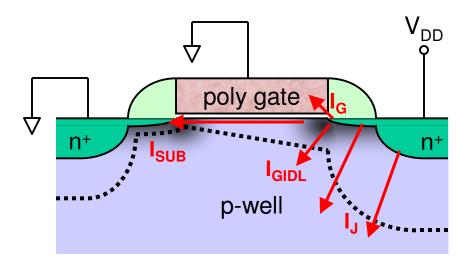

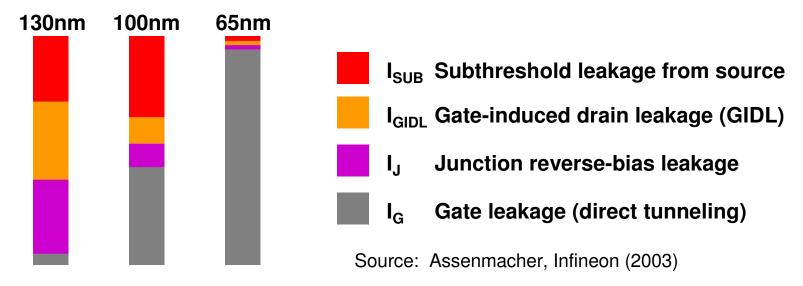

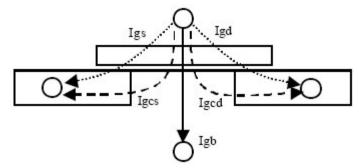

#### **Leakage Current Contributions**

• Relative contributions of OFF-state leakage

#### Subthreshold Conduction

- ON vs. OFF current big issue with V<sub>DD</sub> & V<sub>T</sub> scaling

- FET does not abruptly turn on: large  $I_{ON} \rightarrow Iow V_T \rightarrow Iarge I_{OFF}$  leakage

- Diffusion current due to carriers from source spilling over source barrier into channel • due to application of V<sub>G</sub> to lower  $\phi_s$  (weak dependence on V<sub>DS</sub> in long-channel FET)

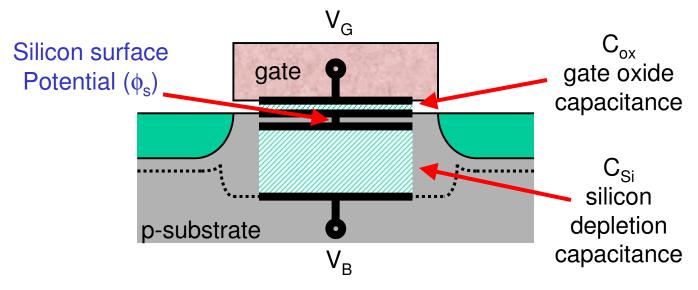

- Want to maximize coupling of V<sub>G</sub> to  $\phi_s$  but have capacitive sharing with substrate

- Large  $C_{ox} \rightarrow$  high-K gate dielectrics, thinner gate oxides

- Small  $C_{Si} \rightarrow$  low substrate doping, fully-depleted SOI

- Inverse subthreshold slope (S) ≈ 100mV/decade at 300K (ideally 60mV/decade)

- e.g.,  $V_T=0.2V \& I_{ON}=100\mu A \rightarrow I_{OFF}=1\mu A !!!$

#### **Basic Intuition on Body Effect**

- Body or backgate effect

- Applying reverse bias between substrate (body) & source increases |V<sub>T</sub>|

- Basic equation:  $V_T = V_{T0} + \gamma \left(\sqrt{2\phi_b + V_{SB}} \sqrt{2\phi_b}\right)$

- Tug-o-war between  $V_G \& V_B$  to control surface potential through  $C_{ox} \& C_{si}$

- Inversion layer forms when  $\phi_s$  is lowered sufficiently with respect to source (that's where carriers come from)

- +  $C_{si}$  decreases with increasing  $|V_B|$

- Steeper subthreshold slope with body effect only valid for long channel

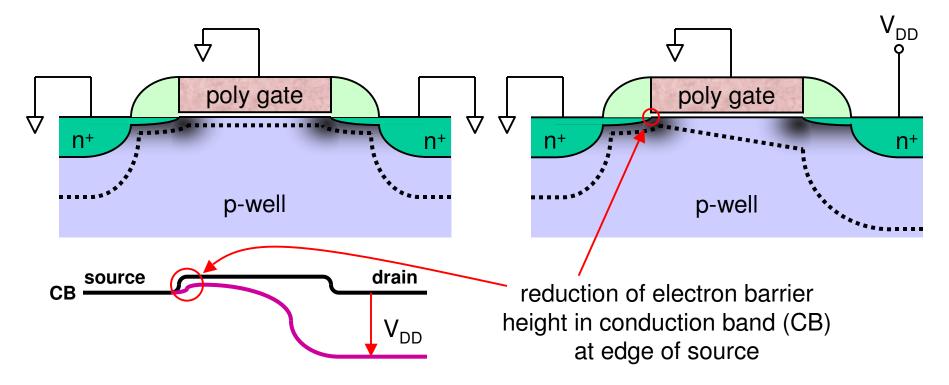

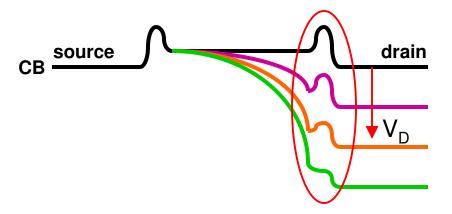

## **Drain-Induced Barrier Lowering (DIBL)**

- Soft punchthrough induced by drain-to-substrate depletion region

- $|V_T| \downarrow$  as  $V_D \uparrow$  (drain-induced SCE)

- $V_D^{\uparrow\uparrow}$   $\rightarrow$  drain-to-substrate depletion region grows with more reverse bias

- Lateral electric fields in drain-induced depletion region lowers source-tochannel barrier, allowing more carriers to diffuse from source to channel

- Typical DIBL magnitude:  $\Delta V_T = -0.12V$  for  $\Delta V_D = +1.2V$  in 90nm

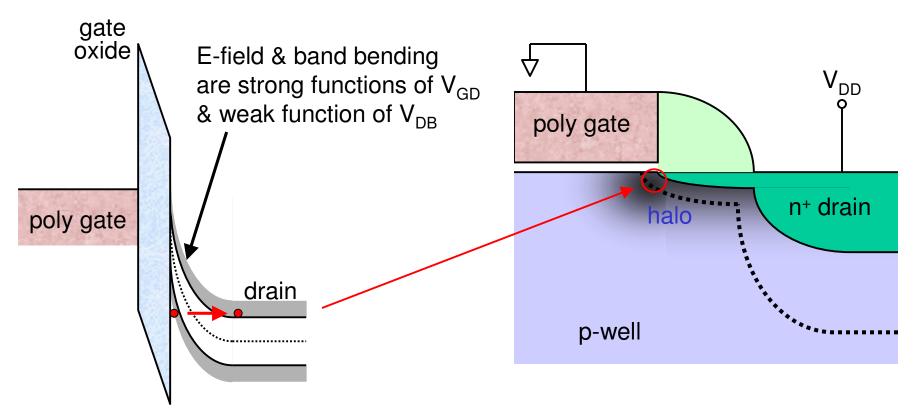

# **Gate-Induced Drain Leakage (GIDL)**

Drain-to-substrate leakage due to band-to-band tunneling current in very high-field depletion region in drain overlap region

- Similar gate-induced source leakage (GISL) mechanism exists when source is raised above gate potential

- Modeled in BSIM4 not BSIM3

# Gate Leakage (Direct Tunneling)

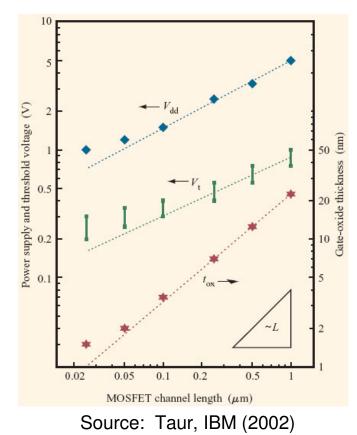

- t<sub>ox</sub> has been scaling aggressively with L<sub>min</sub>

- higher  $I_{FET}$

- tighter gate control  $\rightarrow$  less SCE

- Significant direct tunneling for  $t_{ox} < 2nm$

- Gate leakage =  $f(t_{ox}, V_G)$

- Tunneling probability  $\propto \exp(-\alpha t_{ox})$

- V<sub>G</sub> dependence from Fermi-Dirac statistics & density-of-states considerations

- Hole & electron tunneling in CB & VB

- High-K gate dielectric achieves same C<sub>OX</sub> with much thicker t<sub>ox</sub>

- Modeled in BSIM4 not BSIM3

**Historical Trends**

Loke, Wee & Pfiester Agilent Technologies

## Using FET's with Multiple $V_T$ 's

- Be very careful when using multiple- $V_T$  FET's, especially in analog land

- $V_T$  separation typically advertised only for  $L \approx L_{min}$

- Different mechanisms for setting  $V_T$  in low- $V_T$  vs. high- $V_T$  devices

- Want to share as many implant masks as possible to save \$\$\$

- $V_T$  adjustment: channel implant vs. halo implant

Loke, Wee & Pfiester Agilent Technologies

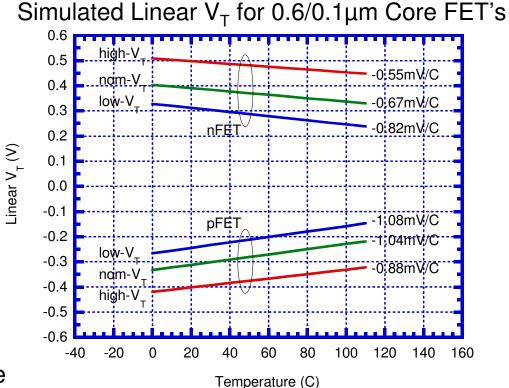

### V<sub>T</sub> vs. Temperature

•  $|V_T| \downarrow \text{ as } T \uparrow$ •  $T \uparrow$   $\rightarrow E_g \downarrow$   $\rightarrow n_i \uparrow$   $\rightarrow \phi_b \downarrow \text{ for constant } N_A$  $\rightarrow |V_T| \downarrow$

$$\phi_{b} = \frac{k_{B}T}{q} \ln \frac{N_{A}}{n_{i}}$$

- $V_T$  can vary a lot with temperature

- Worse  $\mathrm{I}_{\mathrm{OFF}}$  due to  $|\mathrm{V_T}|\downarrow$  & S  $\uparrow$

- Temperature sensitivity depends on W & L

- Analog implication: With V<sub>T</sub> becoming increasing % V<sub>GS</sub> given reduced V<sub>DD</sub>, cold temperatures may yield worst headroom

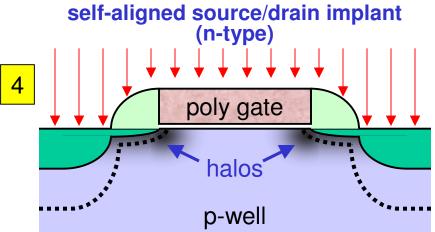

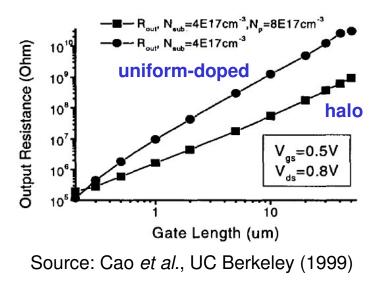

### Impact of Halos on Analog Design

- Halo at source side suppresses SCE & DIBL in *short-channel devices*

- Halo at drain side creates Drain-Induced Threshold Shift (DITS) in Iong-channel devices

- Drain bias very effective in modulating drain halo barrier  $\rightarrow$  V<sub>T</sub>  $\downarrow$   $\rightarrow$  I<sub>ds</sub>  $\uparrow$

- Worse DIBL compared to uniform-doped FET

- Can degrade FET r<sub>out</sub> by 10-100x!!!

- Critical limitation for building current sources (cascoding difficult with low V<sub>DD</sub>)

- Asymmetric FET's with only source-side halo shown to improve r<sub>out</sub> significantly

- Halos increase  $C_{gb}$  when FET is not in inversion

- Modeled in BSIM4 not BSIM3, but still need improvement

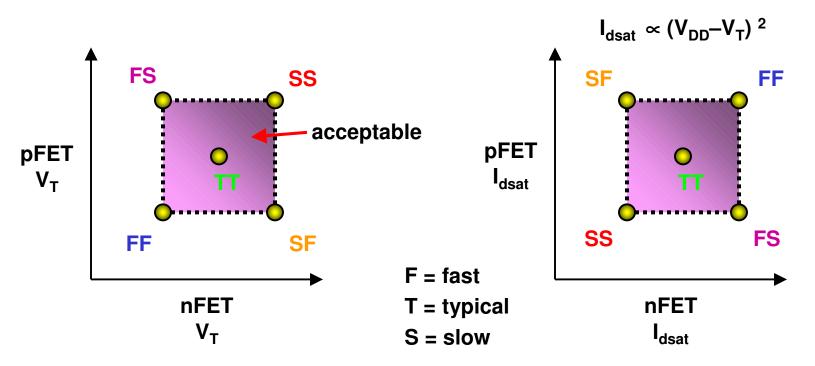

### **Characterizing Process Variations**

- Statistical variations in IC manufacturing  $\rightarrow$  variations in FET characteristics

- Circuits must function across operating V<sub>DD</sub> & temperature but also across statistically acceptable process tolerances

- Statistical variations summarized by spread in nFET & pFET V<sub>T</sub>'s, or in I<sub>dsat</sub>'s, i.e., use V<sub>T</sub> or I<sub>dsat</sub> to summarize cumulative effect of ALL process variances

- Consider die-to-die, wafer-to-wafer & lot-to-lot variations

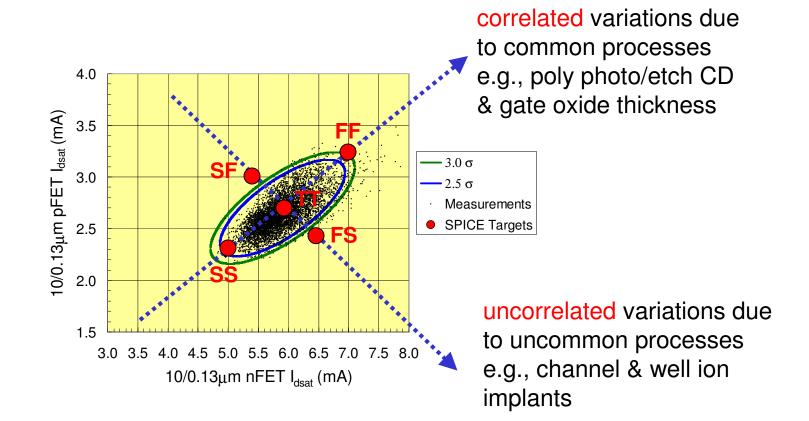

### **Correlated vs. Uncorrelated Process Variations**

• Elliptical 2-D Gaussian distribution from natural variations with no deliberate retargetting of process parameters

• Tougher to control poly CD than implant doses

## **Skew Process for Design Margin Verification**

- Process wafers with I<sub>dsat</sub>'s that target SPICE corners of acceptable distribution

- Statistical distribution is cumulative result of ALL variations for processes targetted as NOMINAL

- Countless possibilities of tweaks to achieve skew nFET/pFET I<sub>dsat</sub> combination

- Fab typically employs SIMPLE means of retargetting nFET & pFET I<sub>dsat</sub>'s with very few deliberate non-nominal process tweaks

- FF vs. SS

- Adjust poly CD, no change in gate oxide thickness

- Nominal implant doses

- FS vs. SF

- Adjust surface channel or halo implant dose

- Nominal poly CD & gate oxide thickness

- Consequences

- Nominal & skew results frequently miss intended targets since nominal (by definition) can land anywhere in distribution

- Not 100% representative of natural process corners

- Decent approximation for vanilla digital circuits

- May be bad approximation for some analog & high-speed digital circuits if they are insensitive to selected tweaks

### Additional Commentary Manufacturing Impact on Design

- Importance of poly gate orientation align FET gate along x or y?

- Preferred orientation will likely exist due to step-and-scan nature of gate lithography

- FET mismatch

- Symmetric circuits that are built asymmetric may fail

- DFM (design for manufacturability) is a big buzz word now

→ need for Monte Carlo simulations to statistically validate design

- Exposure  $\lambda$  is *not* scaling as aggressively as L<sub>min</sub>

- Roadmaps are just guidelines

- Huge industry resistance to move to 157nm

- Requires *reflective* optics  $\rightarrow$  \$\$\$

- Expect more gate resist trimming & relatively worse CD/overlay control at 65nm node

- Whole business of minimum vs. recommended design rules

- Who is willing to design let alone pay for poor yield?

- Statistical design considerations & *layout engineering* becoming more critical than ever

# Conclusions

- CMOS scaling continues to be driven by digital circuit needs

- Should expect incremental changes in 65nm CMOS technology

- Hopefully no major surprises

- Increasing mechanical engineering opportunities in IC technology

- Always a time lag for SPICE models to account for new effects

- Pressing issue since tapeout mistakes are costlier than ever

- Need to work closely with technology providers to quickly find out about these new effects

- Account for them or avoid them!!!

- Statistical design & layout considerations more critical than ever

- Analog designers have to keep living with what they get from digital

- Designers with intimate knowledge of technology constraints will be best positioned to avoid pitfalls & to turn bugs into features

- Could you think of a better time to be doing design?  $\ensuremath{\textcircled{\sc o}}$

#### References

- T. B. Hook *et al.*, "Lateral Ion Implant Straggle and Mask Proximity Effect," *IEEE Trans. Electron Devices*, vol. 50, no. 9, pp. 1946-1951, Sept. 2003.

- J. Assenmacher, "BSIM4 Modeling and Parameter Extraction," *Technical Univ. Berlin Analog Integrated Circuits Workshop*, Mar. 2003.

- X. Xi et al., BSIM4.3.0 MOSFET Model User's Manual, The Regents of the University of California at Berkeley, 2003.

- International Technology Roadmap for Semiconductors, *Front End Processes* (2003 Edition), 2003.

- H.-S. P. Wong, "Beyond the Conventional Transistor," *IBM Journal of Research & Development*, vol. 46, no. 2/3, pp. 133-168, Mar. 2002.

- Y. Taur, "CMOS Design Near the Limit of Scaling," *IBM Journal of Research & Development*, vol. 46, no. 2/3, pp. 213-222, Mar. 2002.

- C. R. Cleavelin, "Front End Manufacturing Technology," *IEEE IEDM Short Course on The Future of Semiconductor Manufacturing*, Dec. 2002.

- D. Harame, "RF Device Technologies," *IEEE IEDM Short Course on RF Circuit Design for Communication Systems*, Dec. 2002.

- S. Thompson *et al.*, "A 90nm Logic Technology Featuring 50nm Strained Silicon Channel Transistors, 7 Levels of Cu Interconnect, Low k ILD, and 1µm<sup>2</sup> SRAM Cell," *IEEE IEDM Tech. Digest*, pp. 61-64, Dec. 2002.

- C. C. Wu *et al.*, "A 90nm CMOS Device Technology with High-Speed , General-Purpose, and Low-Leakage Transistors for System on Chip Applications," *IEEE IEDM Tech. Digest*, pp. 65-68, Dec. 2002.

### **References (cont'd)**

- R. Rios *et al.*, "A Three-Transistor Threshold Voltage Model for Halo Processes," *IEEE IEDM Tech. Digest*, pp. 113-116, Dec. 2002.

- R.A. Bianchi *et al.*, "Accurate Modeling of Trench Isolation Induced Mechanical Stress Effects on MOSFET Electrical Performance," *IEEE IEDM Tech. Digest*, pp. 117-120, Dec. 2002.

- B. Razavi, *Design of Analog CMOS Integrated Circuits*, McGraw-Hill, 2001.

- J. D. Plummer *et al.*, *Silicon VLSI Technology– Fundamentals, Practice and Modeling*, Prentice-Hall, 2000.

- K. M. Cao *et al.*, "Modeling of Pocket Implanted MOSFETs for Anomalous Analog Behavior," *IEEE IEDM Tech. Digest*, pp. 171-120, Dec. 1999.

- A. Chatterjee *et al.*, "Transistor Design Issues in Integrating Analog Functions with High Performance Digital CMOS," *IEEE Symp. VLSI Technology Tech. Digest*, pp. 147-148, June 1999.

- T. H. Lee, *The Design of CMOS Radio-Frequency Integrated Circuits*, Cambridge University Press, 1998.

- D. P. Foty, *MOSFET Modeling with SPICE: Principles and Practice*, Prentice-Hall, 1996.

- A. Beiser, *Concepts in modern Physics (4<sup>th</sup> ed.)*, McGraw-Hill, 1987.

- S.M. Sze, *Physics of Semiconductor Devices (2<sup>nd</sup> ed.)*, John Wiley & Sons, 1981.

#### **Acknowledgments (My Device & Circuits Teachers)**

**Prof. Simon Wong Stanford University**

**Stanford University**

Prof. Krishna Saraswat Prof. James Plummer **Stanford University**

**Prof. Bruce Wooley Stanford University**

**Prof. Tom Lee Stanford University**

Dr. Stephen Kuehne Agere

**Dr. Gary Ray** Novellus

**Tom Cynkar** Agilent Loke, Wee & Pfiester **Agilent Technologies**

**Dr. Peter George** Agilent

Dr. Jeff Wetzel Sematech

**Mike Gilsdorf**

Agilent

**Prof. Martin Wedepohl** University of B.C.

Dr. Chintamani Palsule Agilent

**Prof. David Pulfrey** University of B.C.

**Bob Barnes** Agilent