# Front End Manufacturing Technology

C. Rinn Cleavelin Si Technology Development Texas Instruments, Inc. Dallas, Texas

# Topics

- Transistor Performance Trends

- Transistor Scaling Challenges

- New Device Architectures

- Advanced CMOS

- Non-Classical CMOS

- Memories

- New Front End Materials & Modules

- Lithographic Trends

- Summary

# Moore's Law / Productivity

The definition of "Moore's Law" has come to refer to almost anything related to the semiconductor industry that when plotted on semi-log paper approximates a straight line.

– Gordon Moore, 1995

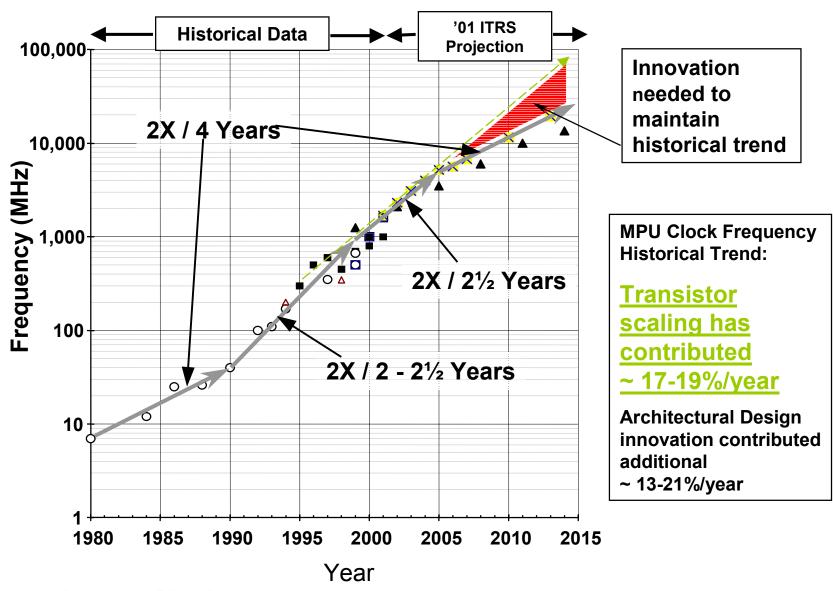

# **Transistor Performance Trend**

Sources: SEMATECH, 2001 ITRS ORTC

# Topics

- Transistor Performance Trends

- Transistor Scaling Challenges

- New Device Architectures

- Advanced CMOS

- Non-Classical CMOS

- Memories

- New Front End Materials & Modules

- Lithographic Trends

- Summary

# **Transistor Scaling Key Challenges**

- Isolation: Minimum Pitch and SOI

- Gate Dielectric: Leakage vs Speed

- Gate Electrode: polySi vs Metal (Mid-gap vs Dual Work Function)

- Ultra-Shallow Junctions (USJ)

- Low resistance contacts

- Low resistance abrupt S/D extensions

iedm

#### **2001 ITRS Scaling Projections**

iedm 🗇

| Technology Generation          | <u>130 nm</u>   | <u>90 nm</u> | <u>65 nm</u> | <u>45 nm</u> | <u>32 nm</u> | <u>22 nm</u>   |

|--------------------------------|-----------------|--------------|--------------|--------------|--------------|----------------|

| Year Production                | 2001            | 2004         | 2007         | 2010         | 2013         | 2016           |

| <i>MPU Gate Length (nm)</i>    | <mark>65</mark> | 37           | 25           | 18           | 13           | <mark>9</mark> |

| DRAM (production)              | 512M            | 1G           | 4G           | 8G           | 32G          | 64G            |

| DRAM chip (cm <sup>2</sup> )   | 1.27            | 0.93         | 1.83         | 1.81         | 2.39         | 2.38           |

| DRAM cost (µ ¢/bit)            | 7.7             | 2.7          | 0.96         | 0.34         | 0.12         | 0.042          |

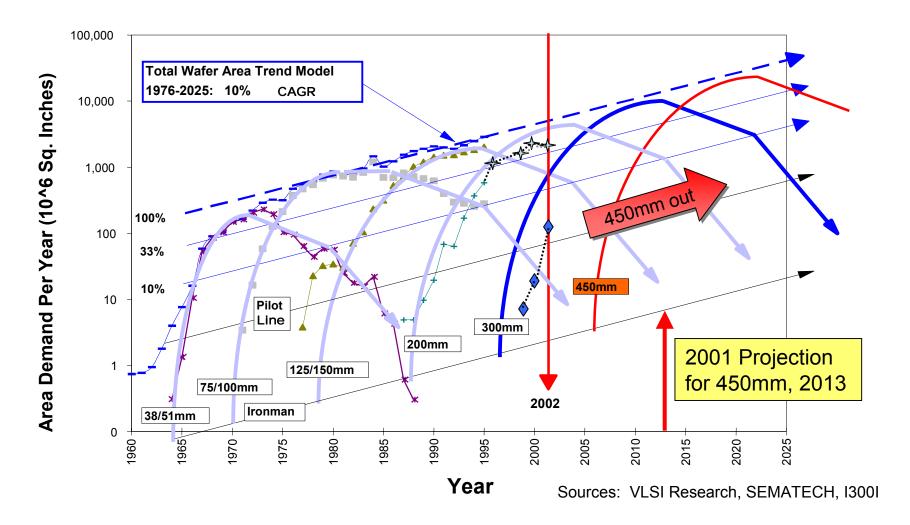

| <i>Wafer Diameter (mm)</i>     | 300             | <u>300</u>   | <u>300</u>   | 300          | <b>450</b>   | <b>450</b>     |

| Logic M gates                  | 97              | 193          | 386          | 773          | 1546         | 3092           |

| Logic M gates/cm <sup>2</sup>  | 69              | 138          | 276          | 552          | 1104         | 2209           |

| Logic chip (cm <sup>2</sup> )  | 1.4             | 1.4          | 1.4          | 1.4          | 1.4          | 1.4            |

| Frequency (GHz)                | 1.7             | 3.9          | 6.7          | 11.5         | 19.3         | 28.7           |

| μP cost (μ ¢/T)                | 97              | 34           | 12           | 4.3          | 1.5          | 0.54           |

| Power/ Chip (W)                | 130             | 160          | 190          | 218          | 251          | 288            |

| Power Supply MPU (V)           | 1.2             | 1.0          | 0.7          | 0.6          | 0.5          | 0.4            |

| Levels of Metal                | 7               | 8            | 9            | 9-10         | 9-10         | 10             |

| EOT (nm)                       | 1.3-1.6         | 0.9-1.4      | 0.6-1.1      | 0.5-0.8      | 0.4-0.6      | 0.4-0.5        |

| X <sub>j</sub> at Channel (nm) | 27-45           | <b>15-25</b> | 10-17        | 7-12         | <b>5-9</b>   | <b>4-6</b>     |

### iedm�

### **Device Scaling Issues: Beyond 65nm**

Threshold Voltage:

- $V_{DD} V_T$  decreases

- Subthreshold Slope kT/q

- CD Control

- Gate Stack

- Tunneling => high  $I_{off}$

- Inversion Layer => EOT limit

- PolySi Depletion => I<sub>on</sub> reduced

- Mobility degradation =>  $I_{on}$  reduced

- CD control

- Reliability

- Source/Drain

- Series Resistance => I<sub>on</sub> reduced

- Dopant Profile Control

- TED suppression

- USJ abrupt S/D extensions

- Contacts to S/D

- Tunneling

- Drain to body & source to drain

### iedm 🗇

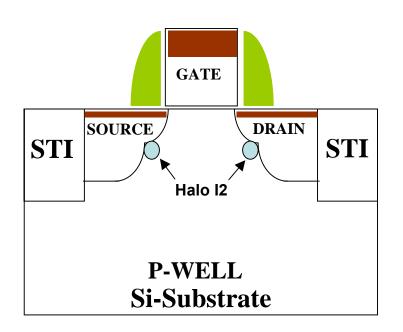

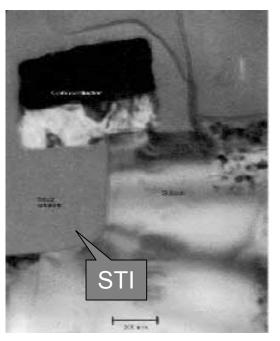

### **Isolation Roadmap**

IBM 16MB DRAM

- STI induced to resolve LOCOS Bird's Beak

- Future device scaling and alternate structures such as Double Gate Logic devices and new member elements may lead to SOI only isolation.

$$LOCOS \rightarrow$$

Shallow Trench Isolation – STI  $\rightarrow$  STI / SOI  $\rightarrow$  SOI only?

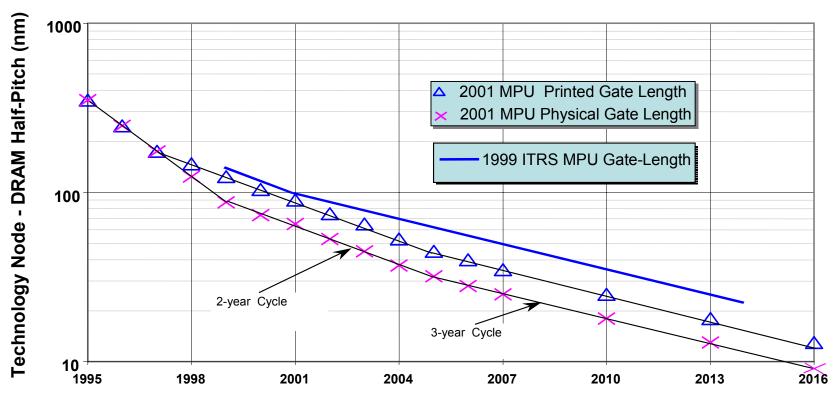

# **Gate Length Scaling: ITRS**

ITRS Roadmap Acceleration Continues...Gate Length

**Year of Production**

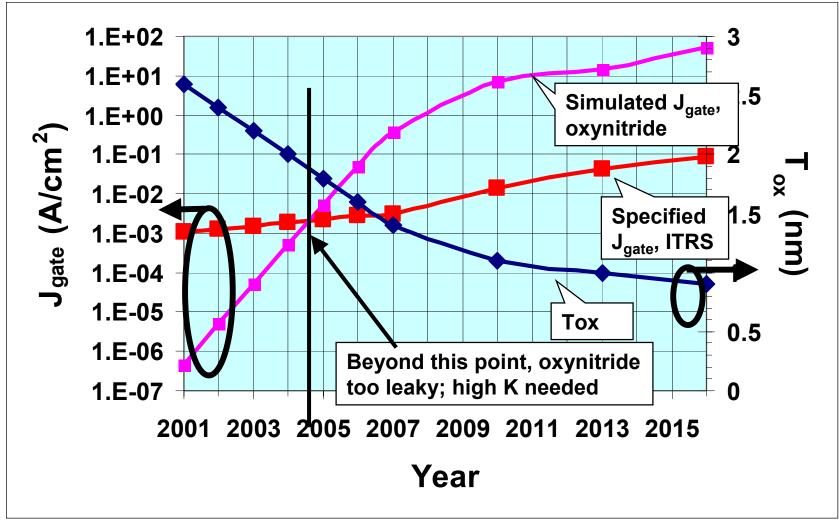

2001 ITRS Projections Versus Simulations of Direct Tunneling Gate Leakage Current Density for Low Standby Power Logic

# Topics

- Transistor Performance Trends

- Transistor Scaling Challenges

- New Device Architectures

- Advanced CMOS

- Non-Classical CMOS

- Memories

- New Front End Materials & Modules

- Lithographic Trends

- Summary

# Limits of CMOS Scaling

#### Planar Non-Planar **New Switch CMOS** CMOS **Structure** Device **Structure** HfO<sub>2</sub> Size Sub 50nm ? source PSG c-Si gate gate body PSG 1.3 nm drain 100 nm SiC 47 Agere '02 Nanotube 5 nm SiC $\overline{}$ Single nanotube 7 - 12 years 12 + Years. 0 - 7 years. TIME

### **Device Evolution**

# **New Device Architectures**

SOI

- Partially Depleted (PD)

- Fully Depleted (FD): Ultra-Thin Body

- Double Gate Structures

- FinFET

- Tri, Pi Gate

- DG-SOI

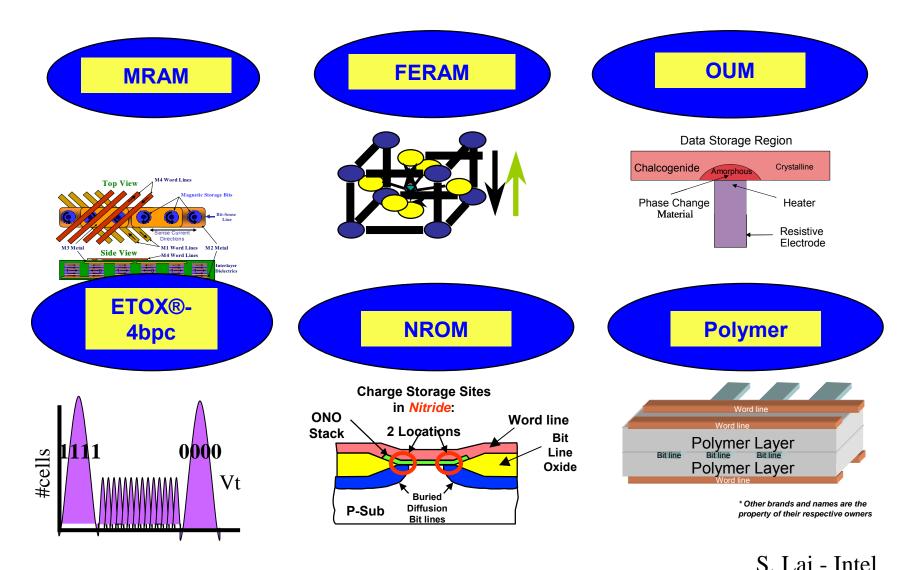

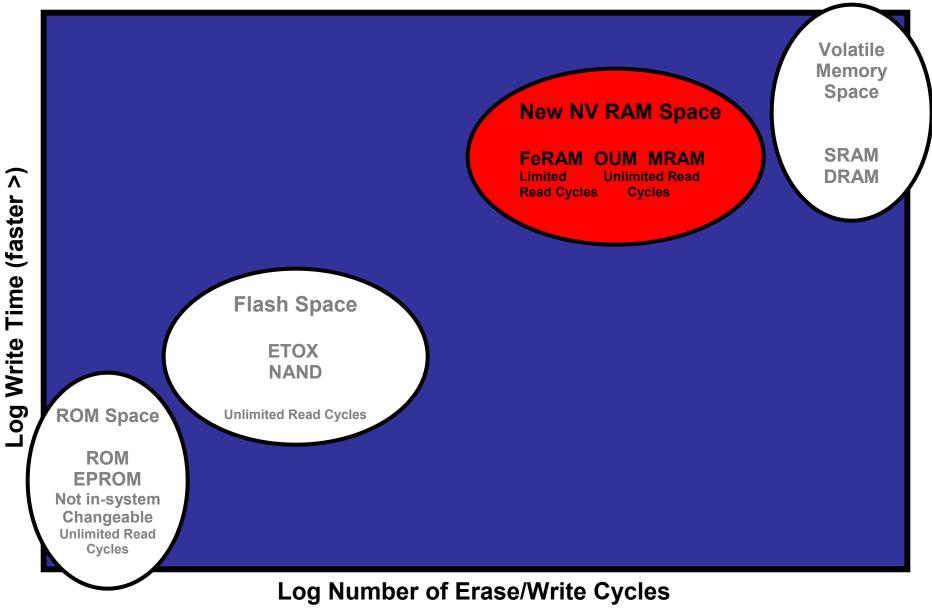

- Memory Innovations

- FeRAM, MRAM, Ovonics, etc

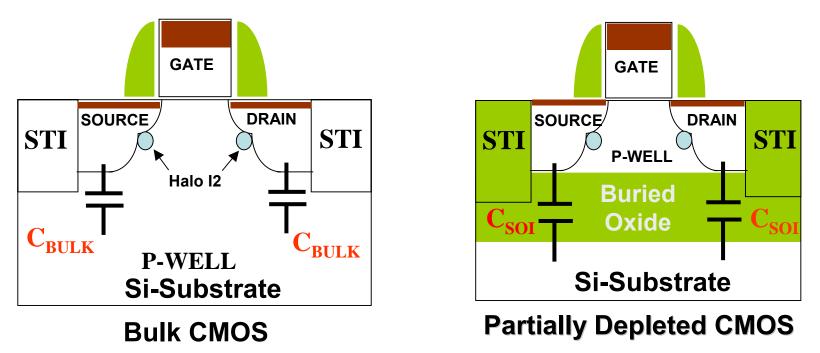

# **SOI Device Structures**

- Short Channel Effect controlled by channel doping/halo as in Bulk

- Reduced junction capacitances => faster speed, lower leakage

- Device design translation straight forward between Bulk and PD SOI

- Complete isolation between devices

- Rad-hard

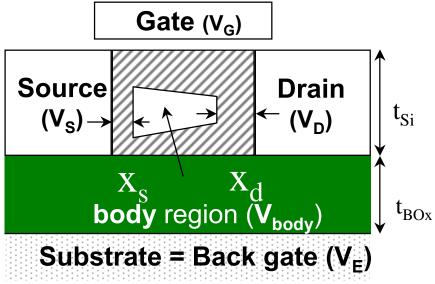

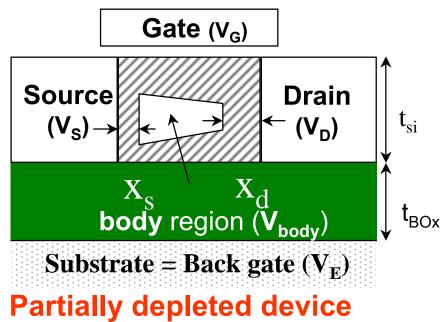

### **Partially versus Fully Depleted**

#### **Partially depleted device**

- Bulk bottom junction capacitances replaced by thick oxide capacitance

- Gate side lateral junction capacitance comparable to Bulk case. Can be smaller for PD in case of silicon film thinning

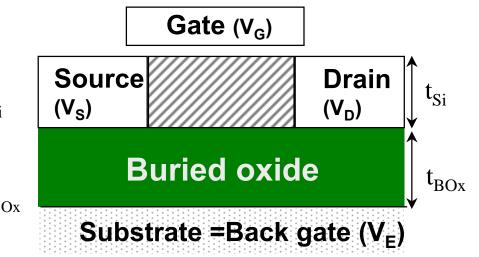

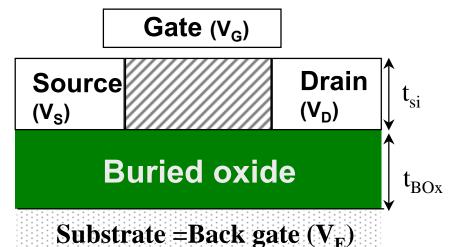

#### Fully depleted device

- Bulk bottom junction capacitances replaced by thick oxide capacitance

- Full depletion of silicon film suppress lateral junction capacitance

- Speed improvement compared to PD

- Smaller power consumption

### **Partially versus Fully Depleted**

- 4 or 5 nodes

- Front and back gate decoupledinternal floating body node

- Floating-Body effects

- $V_T = f(V_{body})$  independent of  $V_E$

#### Fully depleted device

- 4 nodes

- t<sub>si</sub><40nm (for deep sub-µm MOS)

- No neutral floating region

- independent of 'body' voltage

- subthreshold swing=60mV/decade

- Front-Back interface coupling

- V<sub>T</sub>= f (V<sub>E</sub>)

#### iedm 🗇

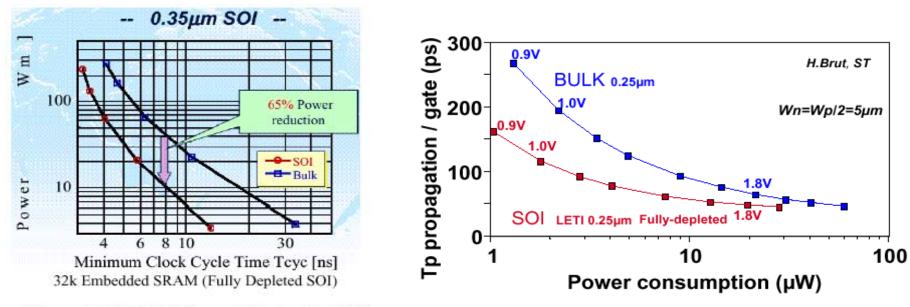

# **SOI: Power Reduction**

Ichigawa & al OKI VLSI Research Center . Sept 2000

### **Merits of Device Scaling <50nm Options**

|                            | Strengths                                                                             | Weaknesses                                                                                   |

|----------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Standard<br>FD device      | <ul> <li>Small parasitic<br/>capacitances</li> <li>Simpler FD architecture</li> </ul> | - Scalability: Ultra-thin film                                                               |

| Ground<br>Plane            | <ul> <li>Reduced SCE</li> <li>Relaxed constraint on Tsi</li> </ul>                    | <ul> <li>Parasitic capacitances<br/>increase</li> <li>Subthreshold swing increase</li> </ul> |

| Partial<br>Ground<br>Plane | <ul> <li>Reduced SCE</li> <li>Relaxed constraint on Tsi</li> </ul>                    | <ul> <li>Parasitic capacitances<br/>increase</li> </ul>                                      |

| Double<br>Gate             | <ul> <li>Best case for SCE control</li> <li>Relaxed constraint on Tsi</li> </ul>      | <ul> <li>Fabrication very difficult</li> <li>Parasitic elements?</li> </ul>                  |

# **SOI Fabrication/Process Issues**

- SOI is ~1.5 3x over bulk wafer pricing

- Etch Pit Density, typically ~600-1000/cm<sup>2</sup>

- PD and to lesser extent FD have floating body effects which must be comprehended

- FD requires Silicon body thickness control less than ~0.2 - 0.4x of Lg or for example 18nm Lg, t<sub>si</sub>~36 - 72A for 45nm node

# **New Device Architectures**

SOI

- Partially Depleted (PD)

- Fully Depleted (FD): Ultra-Thin Body

- Double Gate Structures

- FinFET

- Tri, Pi Gate

- DG-SOI

- Memory Innovations

- FeRAM, MRAM, Ovonics, etc

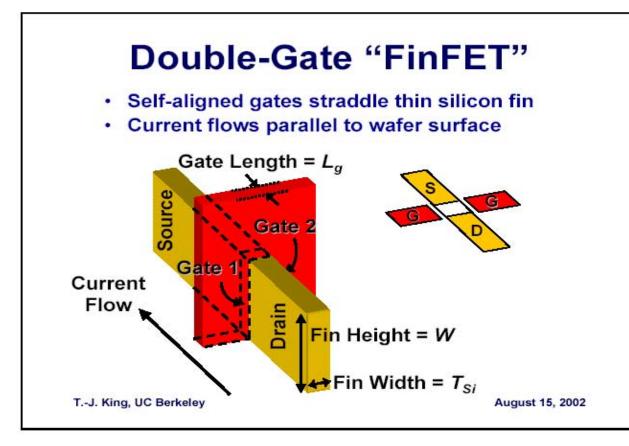

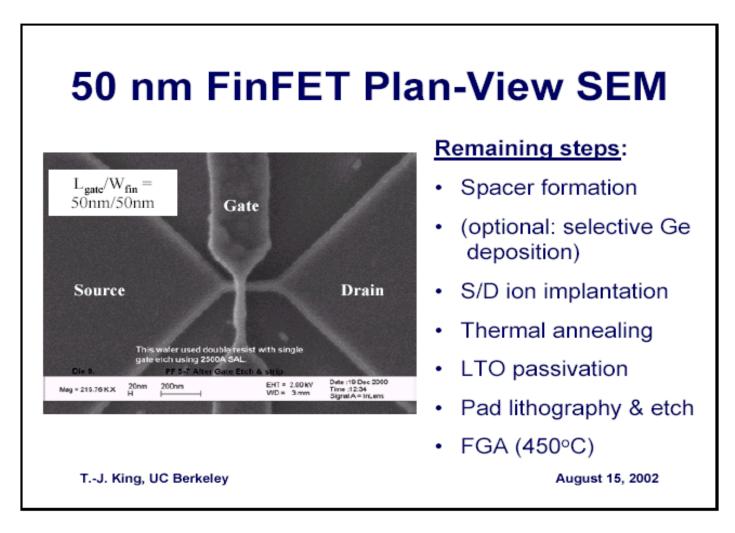

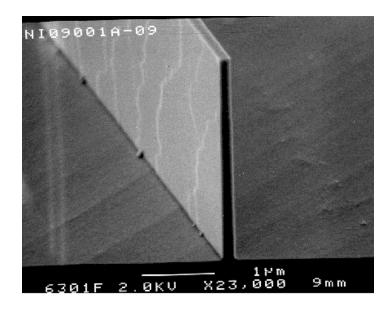

# **Double Gate Structures: FinFET**

Fin width must be less than 2/3 x L<sub>q</sub>

Formation of narrow fin is primary challenge

sub-lithographic process needed

### **Double Gate Structures: FinFET Gate**

### iedm 🗇

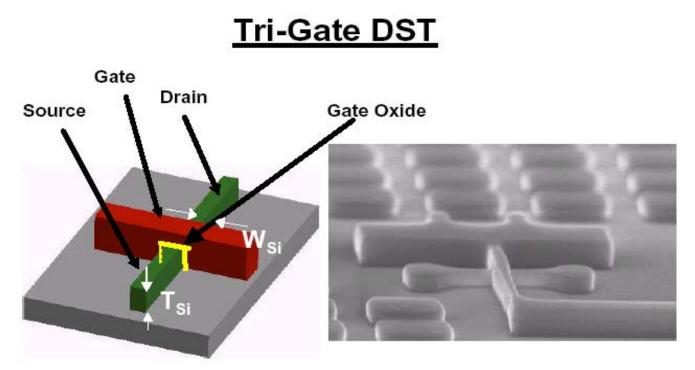

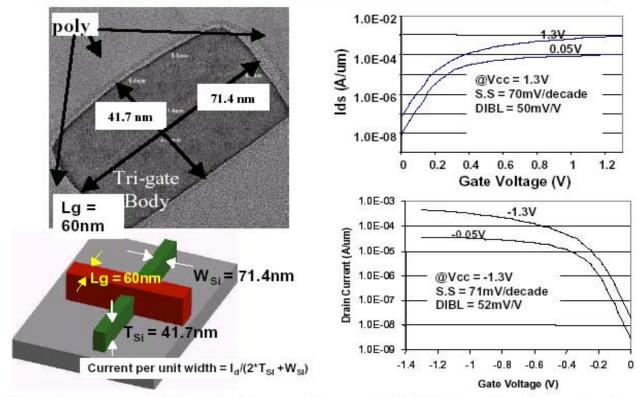

### **Double Gate Structures: Tri-Gate**

- Taller TSi than single-gate; shorter TSi than double-gate

- Wider WSi than double-gate

SSDM 2002, Nagoya, Japan

### **Double Gate Structures: Tri-Gate**

#### Tri-gate DST Relaxes Si Body Dimensions

Tri-gate relaxes Si body dimensions: 2.3X thicker T<sub>si</sub> than singlegate DST, and ~2X wider W<sub>si</sub> than double-gate FINFET

### iedm�

# **DG Fabrication/Process Issues**

### Moat etch

- Defines vertical gates

- Etch and gate dielectric interaction on vertical gate structures

- Gate dielectric (including high-K integration)

- Integrity, mobility, manufacturability

- Gate materials and etch

- Depletion issues, hence Metal gate

- Junction and Contact

- Ion Implant, PLAD, SEG

- Ground plane design

- Implant through thin BOx

### iedm 🗇

### **Options Below 50nm**

|                                          | Doping                             | Mobility | Silicon film | Parasitic<br>cap | Perf             |

|------------------------------------------|------------------------------------|----------|--------------|------------------|------------------|

| BULK                                     | 10 <sup>18</sup> -10 <sup>19</sup> | Low      | /            | -                | Ref. <b>o</b>    |

| PD                                       | 10 <sup>18</sup> -10 <sup>19</sup> | Low      | 50-150nm     | +                | High +           |

| FD & N⁺ Poly                             | 10 <sup>18</sup> -10 <sup>19</sup> | Low      | 5-15nm       | ++               | Very High ++     |

| GP, PGP, DG &<br>N⁺ Poly                 | 10 <sup>18</sup> -10 <sup>19</sup> | Low      | 10-20nm      | +                | High +           |

| DG & N <sup>+</sup> /P <sup>+</sup> Poly | 10 <sup>17</sup> -10 <sup>18</sup> | Medium   | 10-20nm      | ++               | High ++          |

| FD & Metal gate                          | 10 <sup>15</sup> -10 <sup>16</sup> | High     | 5-15nm       | ++               | Very High<br>+++ |

| GP, PGP & Metal gate                     | 10 <sup>15</sup> -10 <sup>16</sup> | High     | 10-20nm      | +                | High ++          |

| DG & Metal gate                          | 10 <sup>15</sup> -10 <sup>16</sup> | High     | 15-30nm      | ++               | Very High<br>+++ |

# **New Device Architectures**

SOI

- Partially Depleted (PD)

- Fully Depleted (FD): Ultra-Thin Body

- Double Gate Structures

- FinFET

- Tri, Pi Gate

- DG-SOI

- Memory Innovations

- FeRAM, MRAM, Ovonics, etc

# **Memory Technologies**

iedm 🚸

Many choices in development

### Memory Technologies Comparison

S. Lai - Intel 30

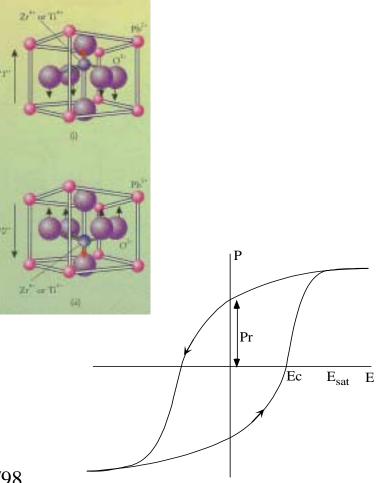

# FeRAM

### What Is FeRAM?

#### Operation

- Selected crystalline materials have spontaneous polarization

- Data is stored by applying a voltage to align the internal dipoles "Up" or "Down"

#### Attributes

- Non-Volatile

- "Fast" Random Read Access

- Fast Write with very low power consumption

- Destructive read, limited read and write cycles

Source: Physics Today 7/98

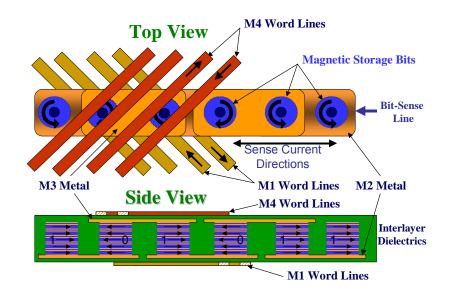

### MRAM

- Operation

- Cell is 1 MJT + 1 Transistor

- Electric current switches the magnetic polarity

- Change in magnetic polarity sensed as resistance change

- Attributes

- Non-Volatile, High Density

- Non Destructive Read

- Low Voltage & Low Power

- Write = Read Speed, < 50 nsec</p>

- Unlimited R/W Endurance

- Material compatibility with CMOS a key challenge

S. Lai - Intel

# Topics

- Transistor Performance Trends

- Transistor Scaling Challenges

- New Device Architectures

- Advanced CMOS

- Non-Classical CMOS

- Memories

- New Front End Materials & Modules

- Lithographic Trends

- Summary

### **New Front End Materials & Modules**

### Substrates:

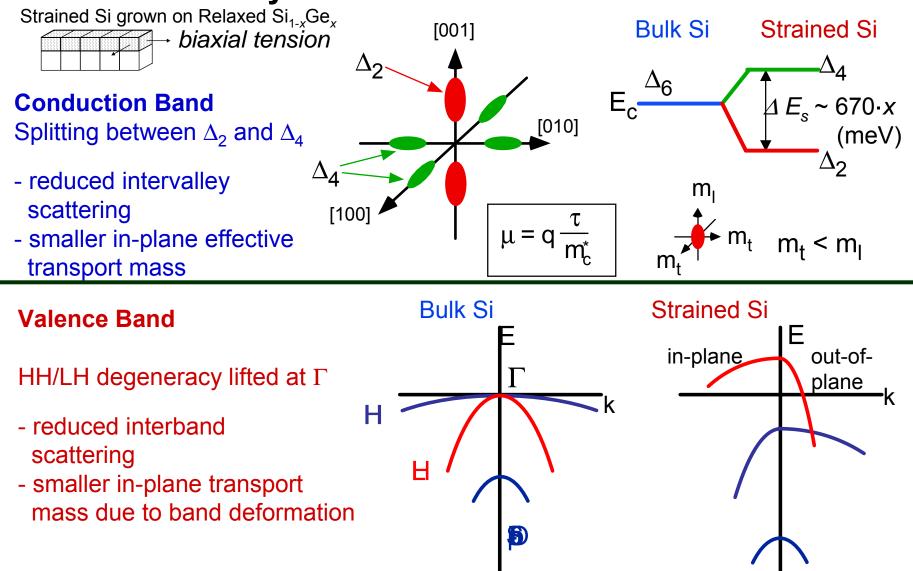

- Strained Si

- SOI; Ultra Thin Body (UTB) Si

- 450mm

- Gate Dielectrics: Oxide to High-k

- Gate Electrodes: doped polySi to metal gate

- Ultra-Shallow Junctions:

- Raised S/D

- Non-equilibrium annealing

- Gate Etch / CD Control and Clean

# **Substrates**

Progression of CMOS substrate technologies:

- ▼ Bulk Silicon

- ▼ Bulk Silicon with Backside Gettering

- ▼ Epitaxial Silicon (P/P<sup>+</sup>)

- ▼ Partially Depleted (PD-SOI)

- ▼ Strained Silicon (SiGe Relaxed Hetero-structure)

- Partially Depleted Strained Silicon

- ▼ Fully Depleted (FD-SOI)

- ▼ Fully Depleted Strained Silicon

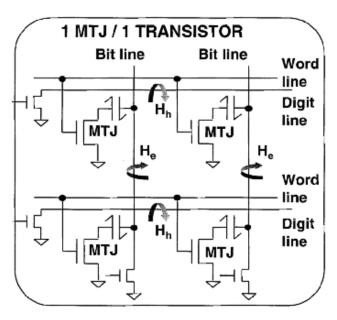

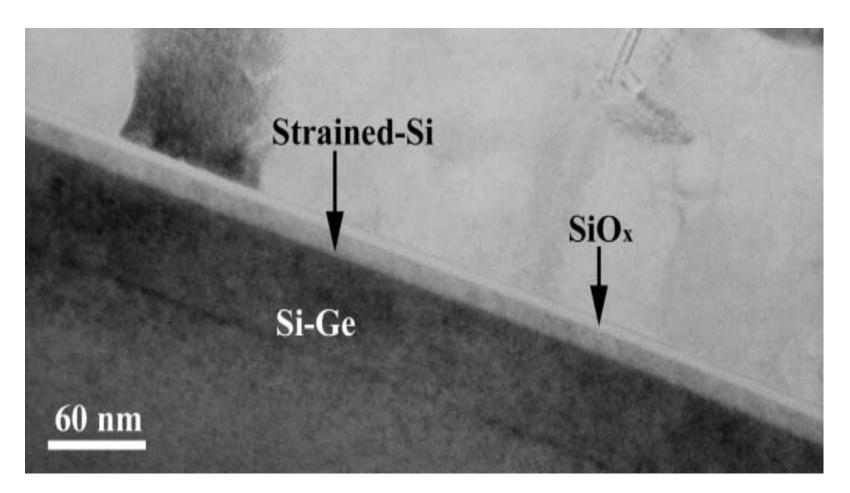

### Strained-Si MOSFET Structures

- + Increased effective mobility, increased I<sub>on</sub>

- Difficult integration issues: manufacturability

- Compatibility with ultra-thin body SOI

- Cost (~50% cost adder @300mm)

Courtesy of J. Hoyt - MIT

### **Strained Silicon CMOS**

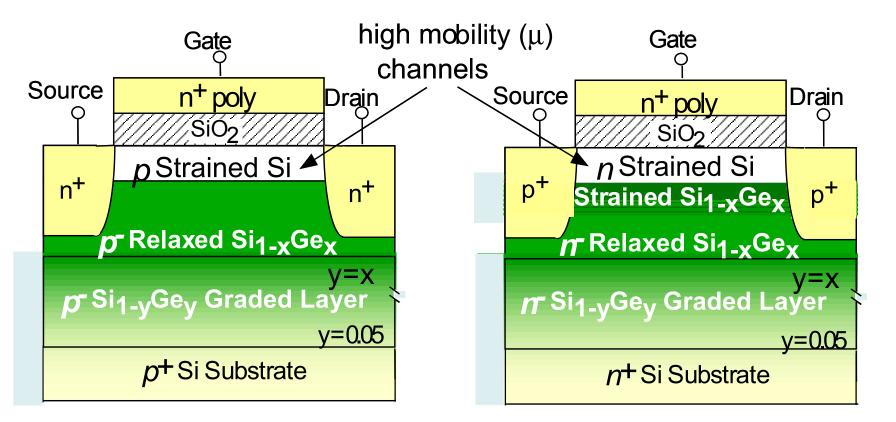

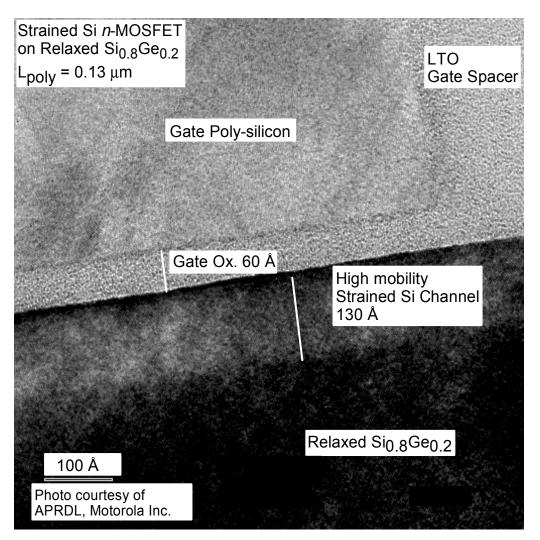

### **Cross-Section TEM of Strained Si Channel**

Rim, Hoyt, and Gibbons, IEDM 1998

iedm 🚸

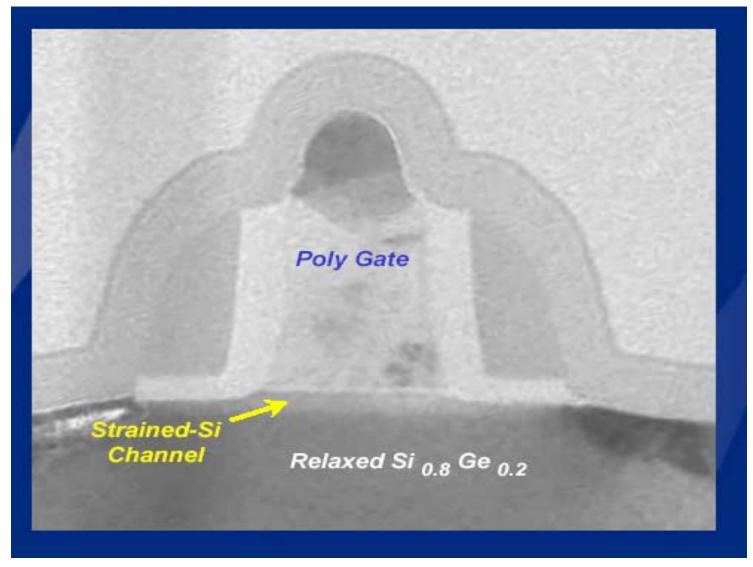

### **Cross-Section TEM of Strained Si Transistor**

Courtesy UMC/Amberwave

iedm (\*

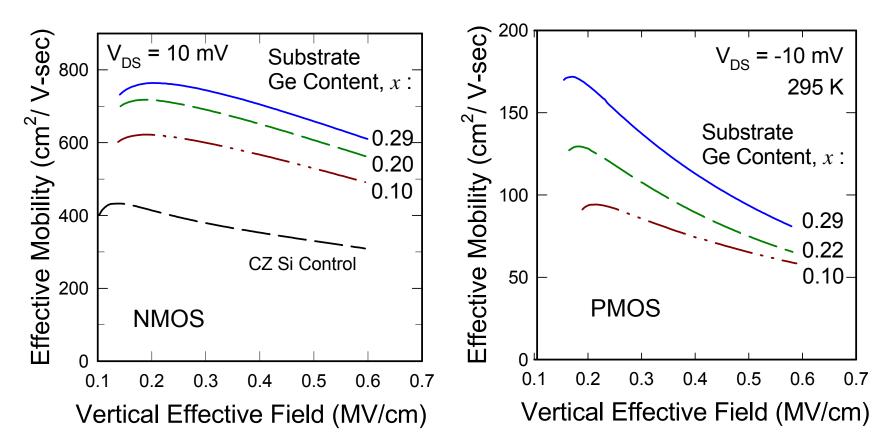

### **Strained Silicon Mobility Enhancement**

- low-field electron and hole mobilities increase with tensile strain in Si

- peak mobility enhancement ratios: ~ 1.8 for 30% Ge substrate

Courtesy Judy L. Hoyt

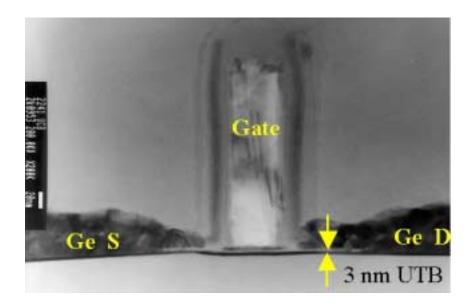

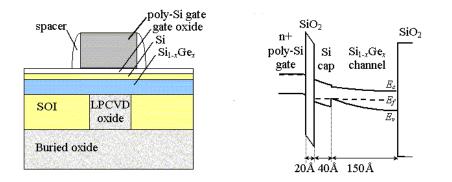

### SOI: Ultra Thin Body (UTB) Si

UTB SI with Strained Si combines advantages of SiGe/Si heterostructure with UTB low leakage

#### Yee-Chia Yeo, et. al. UTBFET for NanoCMOS

### **Wafer Area Generation Model**

### **New Front End Materials & Modules**

- Substrates:

- Strained Si

- SOI; Ultra Thin Body (UTB) Si

- 450mm

- Gate Dielectrics: Oxide to High-k

- Gate Electrodes: doped polySi to metal gate

- Ultra-Shallow Junctions:

- Raised S/D

- Non-equilibrium annealing

- Gate Etch / CD Control and Clean

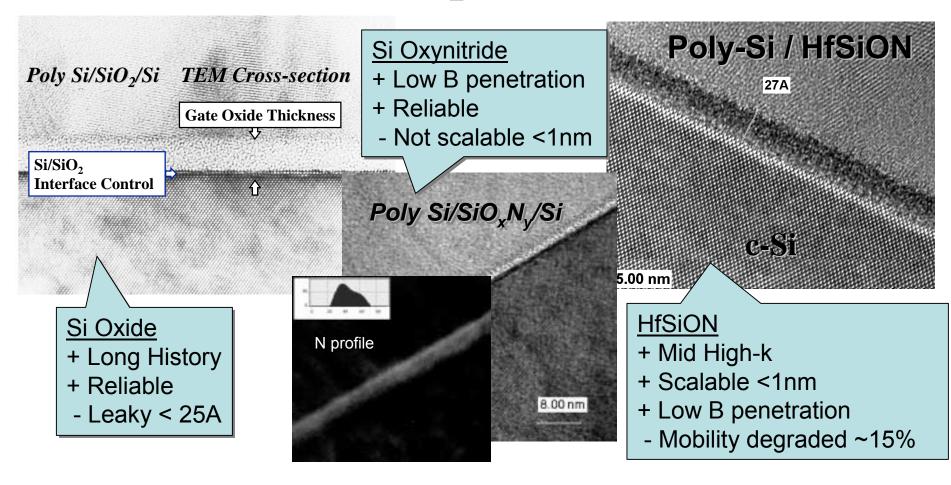

### Gate Dielectric: SiO<sub>2</sub> to High-k

Node: >/~250nm

180nm – ~65nm

#### <mark>≤65nm</mark>?

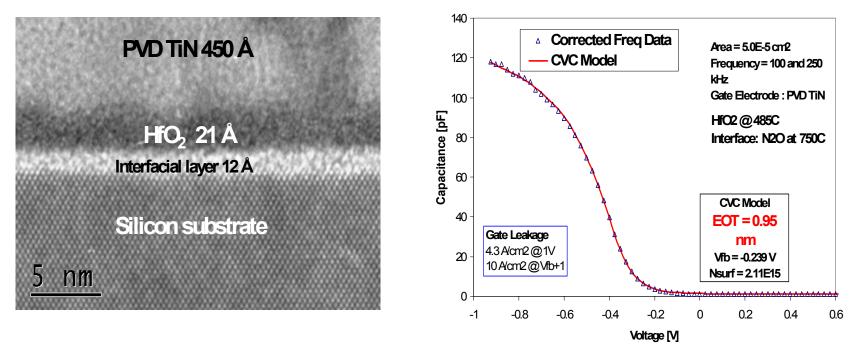

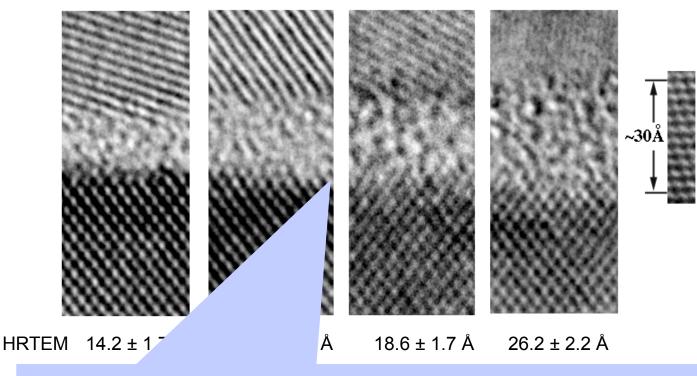

# **MOCVD HfO<sub>2</sub> High-κ Dielectric**

Effective Dielectric Constant ~ 13.5

TEM (left) for MOCVD HfO<sub>2</sub> with EOT = 0.95 nm and CV curve (right) [80] Courtesy International SEMATECH

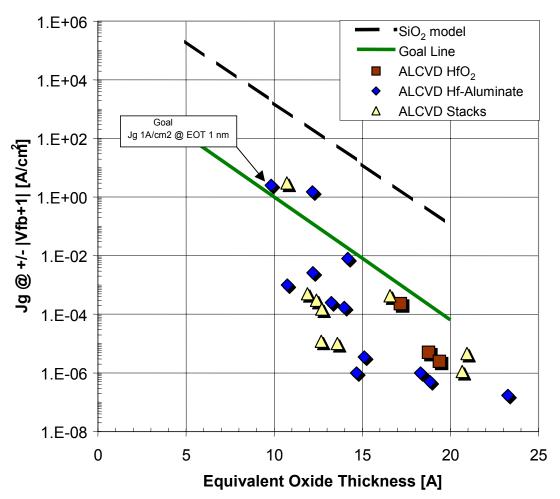

# High-k Leakage Current versus EOT iedm ♦ (trends)

# High-k Manufacturability Issues

- Interface dielectric preparation and control

- High-k dielectric amorphous phase thermal limitations

- Material etch characteristics / selectivity

- Boron penetration resistance

- High-k dielectric interactions with gate electrode

- Deposition complexities for multi-component dielectric materials

- Conformal depositions for non-planar gate structures

- Metrology of heterogeneous multilayer dielectric films

iedm

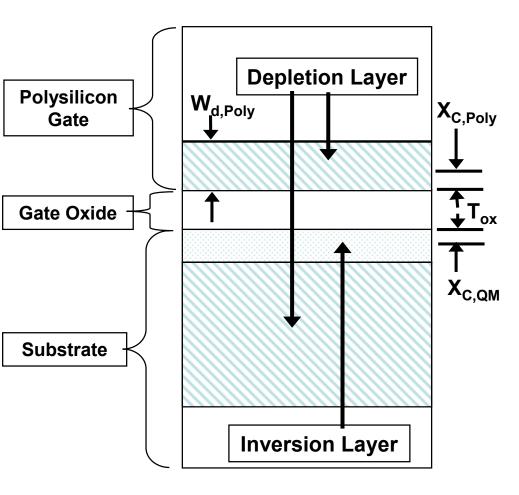

### **Gate Dielectric Scaling**

"Interface Control is critical to achieve <10A effective Gate Dielectric - To achieve 7A effective thickness:

Interface Dielectric<1A</th>High-k dielectric<1A</td>Poly Depletion<1A => Metal GateChannel Quantum Effect~4A

### **New Front End Materials & Modules**

- Substrates:

- Strained Si

- SOI; Ultra Thin Body (UTB) Si

- 450mm

- Gate Dielectrics: Oxide to High-k

- Gate Electrodes: doped polySi to metal gate

- Ultra-Shallow Junctions:

- Raised S/D

- Non-equilibrium annealing

- Gate Etch / CD Control and Clean

### Gate Electrode: Why metal gate?

- polySi depletion

- EOT reduces => Eox lower=> inversion charge lower

- For EOT scaling => polySi doping must increase

- PMOSFETs: B penetration with thin gate dielectrics

- Nitrided gates used to reduce B penetration

- Compatibility of polySi with high-k dielectrics

- Gate resistance of very thin gates even with silicide

### **Gate Electrode Options**

|                 | Pro's                                                                                                                             | Con's                                                                                                           |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| N+ Poly<br>gate | - Simpler Process                                                                                                                 | - Required doping level higher than PD/Bulk                                                                     |

| Mid-gap<br>gate | <ul> <li>No poly depletion</li> <li>Intrinsic devices:</li> <li>(high μ expected)</li> </ul>                                      | - V <sub>T</sub> can not be lower<br>than 0.4V                                                                  |

| Metal<br>gate   | <ul> <li>No poly depletion</li> <li>V<sub>T</sub> can be lower than 0.4V</li> <li>Intrinsic devices: (high μ expected)</li> </ul> | <ul> <li>Identification of Dual<br/>Metal system</li> <li>Integration difficult, esp.<br/>Dual Metal</li> </ul> |

### **New Front End Materials & Modules**

- Substrates:

- Strained Si

- SOI; Ultra Thin Body (UTB) Si

- 450mm

- Gate Dielectrics: Oxide to High-k

- Gate Electrodes: doped polySi to metal gate

- Ultra-Shallow Junctions:

- Raised S/D

- Non-equilibrium annealing

- Gate Etch / CD Control and Clean

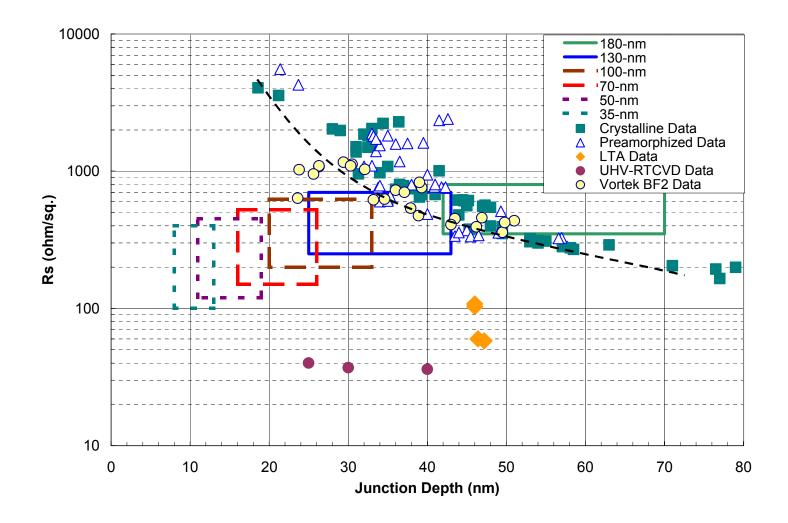

### **Ultra-Shallow Junctions - USJ**

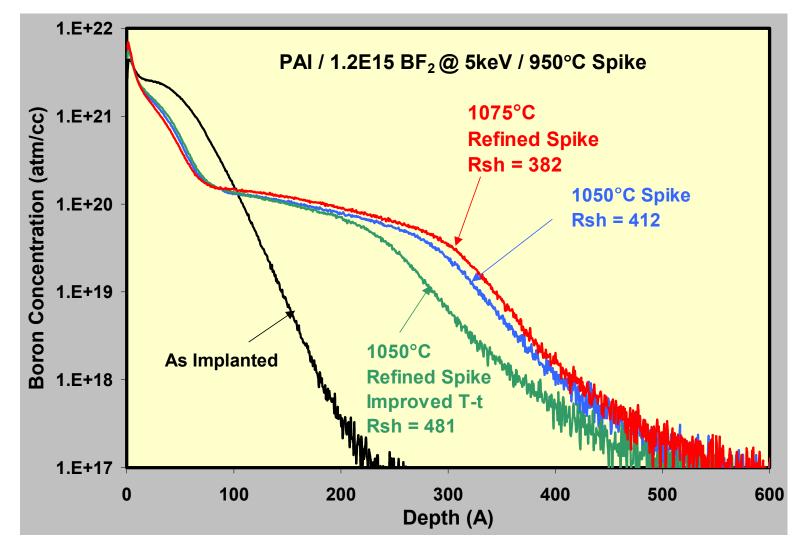

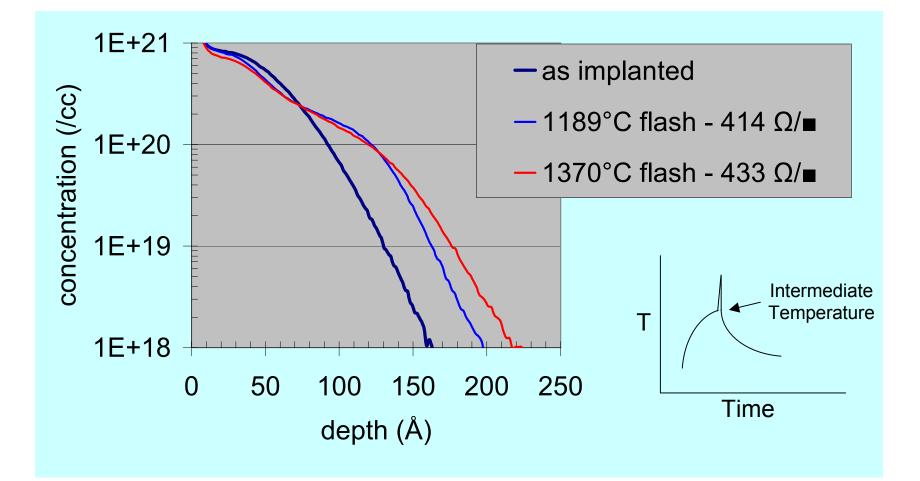

### USJ – Advanced Spike RTA

**iedm**�

### Flash assisted Impulse Anneal, 800°C Intermediate Temperature

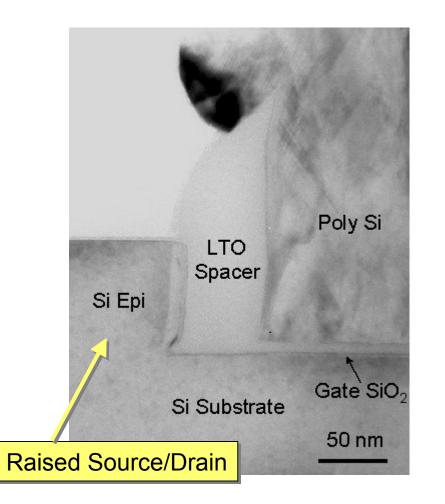

### **Raised Source/Drain**

#### Advantages

- Improves drive current

- Improves SCE

- Essential for FD-SOI with ultra-thin-body

#### Needs

- Low Temp Selective EPI process <650 C</li>

- Facet control at sidewall edge

- High doping (Ge, B, P)

- Low defects

- Good uniformity

- Low CoO

### **New Front End Materials & Modules**

- Substrates:

- Strained Si

- SOI; Ultra Thin Body (UTB) Si

- 450mm

- Gate Dielectrics: Oxide to High-k

- Gate Electrodes: doped polySi to metal gate

- Ultra-Shallow Junctions:

- Raised S/D

- Non-equilibrium annealing

- Gate Etch / CD Control and Clean

### **Gate Stack Etch**

### iedm�

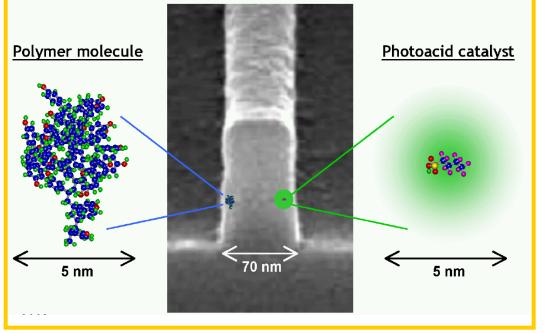

#### Line and sidewall edge roughness

The dimensions of resist features are now at a scale where the effects of individual molecules are important.

#### **Issues:**

LER of resist

- resist molecular scales (~ 5 nm)

- image contrast and flare

- mask roughness

- development effects

#### Etched gate edge roughness

- transfer of LER from resist

- does not scale with etch bias

- granularity of film stack adds

Parameters involved in Line-edge roughness add in quadrature:

$$\boldsymbol{\sigma}_{\text{LER}}^{2} = \boldsymbol{\sigma}_{\text{SHOTNOISE}}^{2} + \boldsymbol{\sigma}_{\text{DIFFUSION}}^{2} + \boldsymbol{\sigma}_{\text{AERIAL IMAGE}}^{2} + \boldsymbol{\sigma}_{\text{DEVELOPMENT}}^{2} + \boldsymbol{\sigma}_{\text{ETCH}}^{2} + \boldsymbol{\sigma}_{\text{MASK}}^{2}$$

### **Gate Stack CD Control**

293 lattice planes = 91.9nm wide

Dr. T.J. Headley, Sandia IMRL

### Atomistic Lateral Scaling of Gate Length

Gate Edge CD Control and Transistor Performance critical to etching and cleaning chemistries

## **FEOL Clean Challenges**

#### New Materials and Processes

- Cleaning and drying High Aspect Ratio (HAR) structures

- Interface control for deposited high-k dielectrics

- Post high-k gate stack etch cleans compatible with exposed materials and CD control

- Interface control for epitaxial Si and Si-Ge

#### Scaling and Defect Levels

- Removal of small particles without affecting materials and structures

- Control of contaminates (carbon, etc) for non-oxide gate dielectrics

- ESH

- Chemical, DI water, energy reduction, and hazardous chemical elimination and avoidance

iedm

### Topics

- Transistor Performance Trends

- Transistor Scaling Challenges

- New Device Architectures

- Advanced CMOS

- Non-Classical CMOS

- Memories

- New Front End Materials & Modules

- Lithographic Trends

- Summary

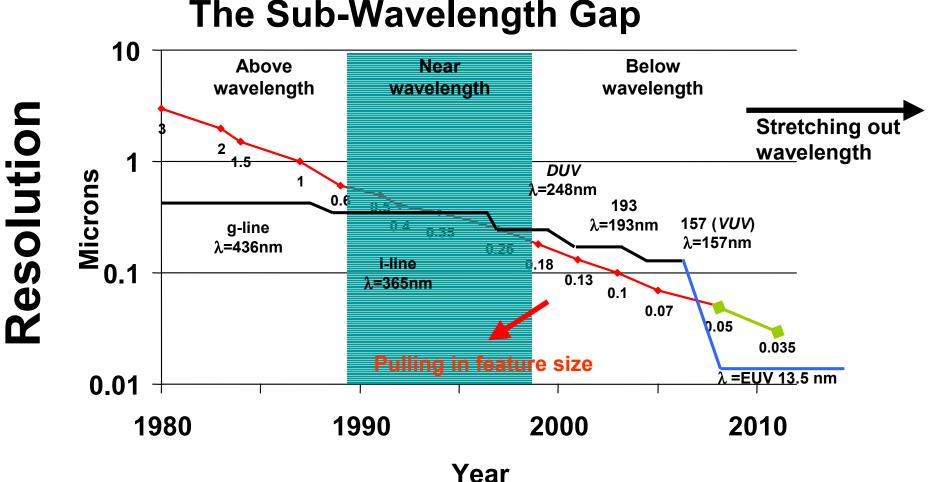

### **Lithographic Front End Trends**

**Source: Numerical Technologies**

iedm 🚸

### **Lithographic Front End Trends**

#### In Keeping Pace with Moore's Law

| Start mass production | 2001                                         | 2003                       | 2005                                         | 2007                                          |

|-----------------------|----------------------------------------------|----------------------------|----------------------------------------------|-----------------------------------------------|

| Technology            | 130 nm                                       | 90 nm                      | 65 nm                                        | 45 nm                                         |

| generation            |                                              |                            |                                              |                                               |

| Minimum               | 160 nm                                       | 115 nm                     | 80 nm                                        | 55 nm                                         |

| half-pitch            |                                              |                            |                                              |                                               |

| $k_1$ -factor         | $\lambda$ =248 nm, NA=0.7 $0.45$             | $\lambda$ =193 nm, NA=0.63 | $\lambda = 193 \text{ nm}, \text{NA} = 0.85$ | $\lambda = 157 \text{ nm}, \text{NA} = 0.95?$ |

|                       | $\lambda = 193 \text{ nm}, \text{NA} = 0.63$ | $\lambda$ =193 nm, NA=0.75 | $\lambda = 157 \text{ nm}, \text{NA} = 0.85$ | $\lambda = 157 \text{ nm}, \text{NA} = 1.25?$ |

|                       | 0.52                                         | 0.45                       | 0.43                                         | 0.44                                          |

| Respective            | 0.48                                         | 0.47                       | 0.25                                         | 0.16                                          |

| DOF in                |                                              |                            |                                              |                                               |

| micron                | 0.47                                         | 0.32                       | 0.22                                         | 0.09                                          |

| Layer-layer           | 45 nm                                        | 32 nm                      | 22 nm /                                      | 15 nm                                         |

| overlay               |                                              |                            |                                              |                                               |

Liquid immersion lithography, assuming index = 1.4 and NA = 0.9 in liquid

iedm 🚸

## Summary

- Front End Manufacturing Technology will undergo significant changes both in the near-term and long-term as new processes, materials, and structures are introduced to meet Roadmap scaling requirements.

- Material and process solutions potentially include high-k dielectrics, metal gate electrodes (mid-gap/dual), SOI (PD/FD), Strained Si, Spike and/or non-equilibrium annealing, Raised S/D, and others yet to be identified.

- Longer-term new non-classical CMOS structures such as Dual Gate, FinFET, PI/Tri-gate, may be required in combination with new materials to provide the ultimate End-of-Roadmap devices.

### iedm�

### Acknowledgements

- Allen Bowling, Texas Instruments

- Olivier Faynot, LETI

- Judy Hoyt, MIT

- Majid Mansoori, Texas Instruments

- Shane Palmer, Texas Instruments

- Walt Trybula, International SEMATECH

- Rick Wise, Texas Instruments

- Peter Zeitzoff, International SEMATECH

### **Backup Charts**

#### Effects of Biaxial Tensile Strain on Si Energy Bands and Mobility

iedm 🚸