# Channel Equalization Techniques for High-Speed Electrical Links

#### Sam Palermo Analog & Mixed-Signal Center Texas A&M University

## Outline

- Introduction

- Channel characteristics

- Equalizer circuits

- Equalizer adaptation techniques

- Optical interconnects

- Conclusion

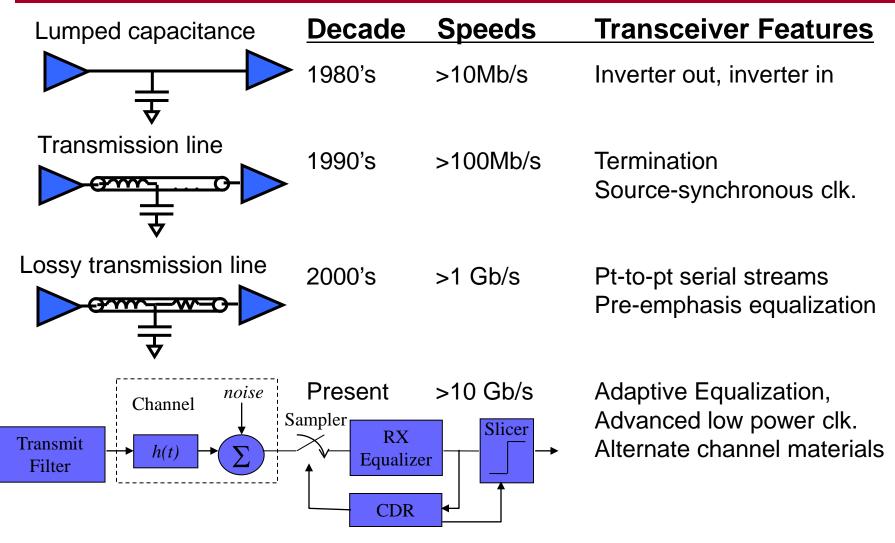

## Chip-to-Chip Signaling Trends

Slide Courtesy of Frank O'Mahony & Brian Casper, Intel

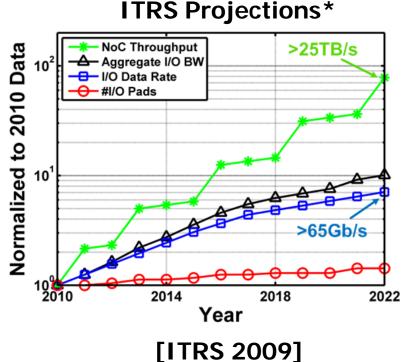

## Increasing Bandwidth Demand

- Single  $\Rightarrow$  Multi  $\Rightarrow$  Many-Core  $\mu$ Processors

- Tera-scale many-core processors will aggressively drive aggregate inter- and intra-chip bandwidth

Intel Teraflop Research Chip

- 80 processor cores

- On-die mesh interconnect network w/ >2Tb/s aggregate bandwidth

- 100 million transistors

- 275mm<sup>2</sup>

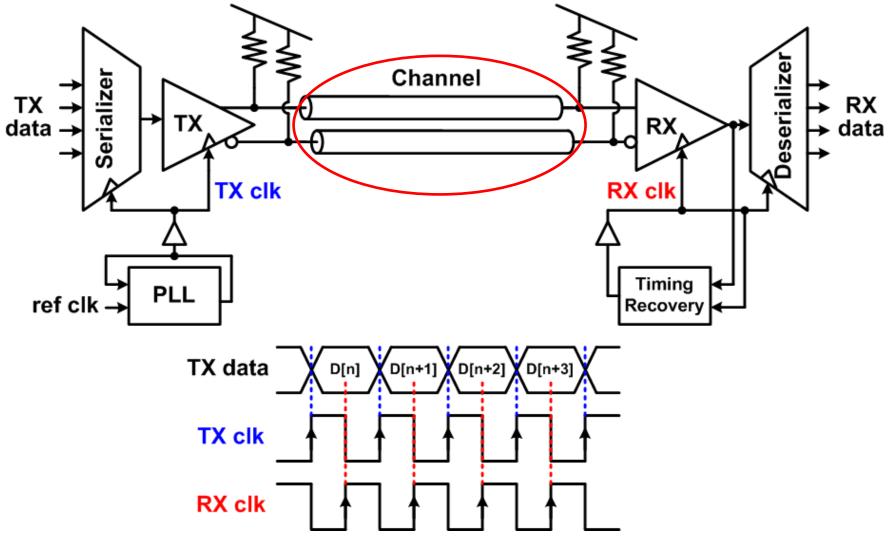

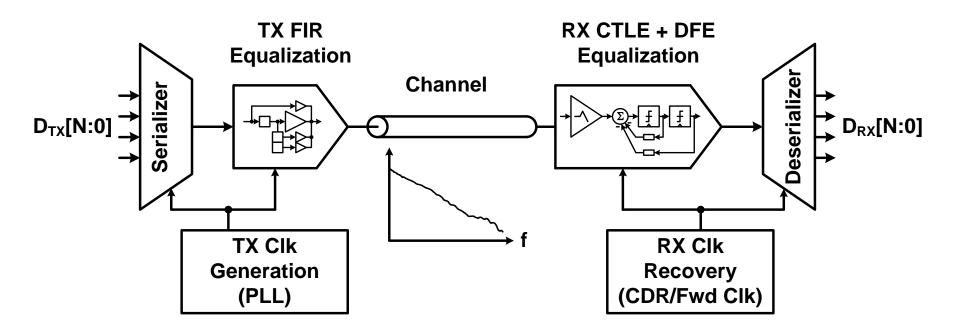

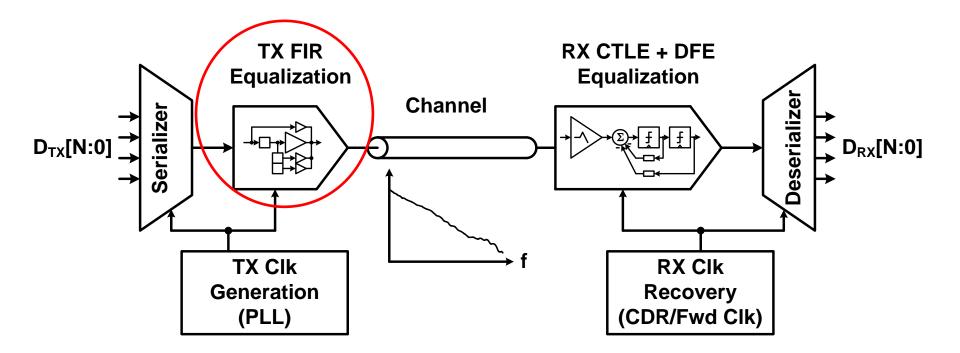

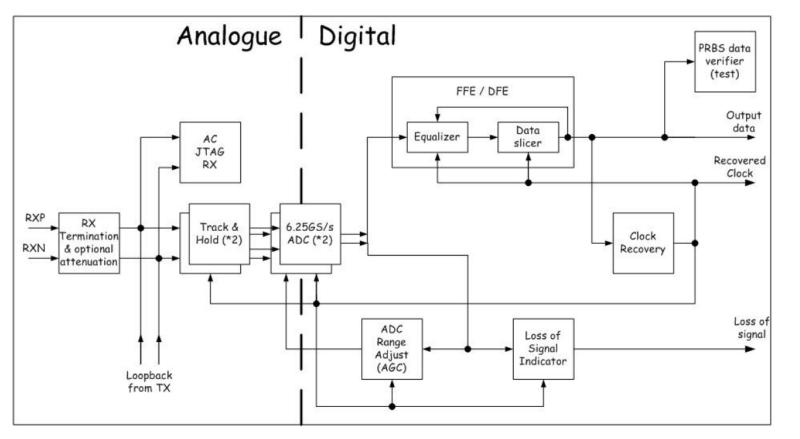

## High-Speed Electrical Link System

## Outline

- Introduction

- Channel characteristics

- Equalizer circuits

- Equalizer adaptation techniques

- Optical interconnects

- Conclusion

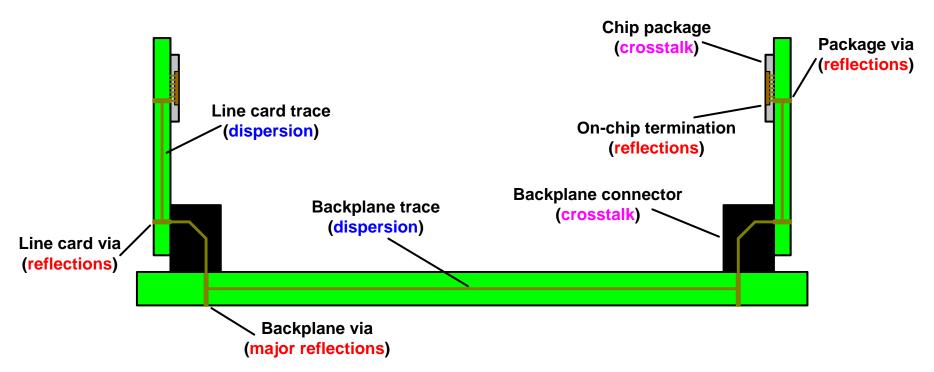

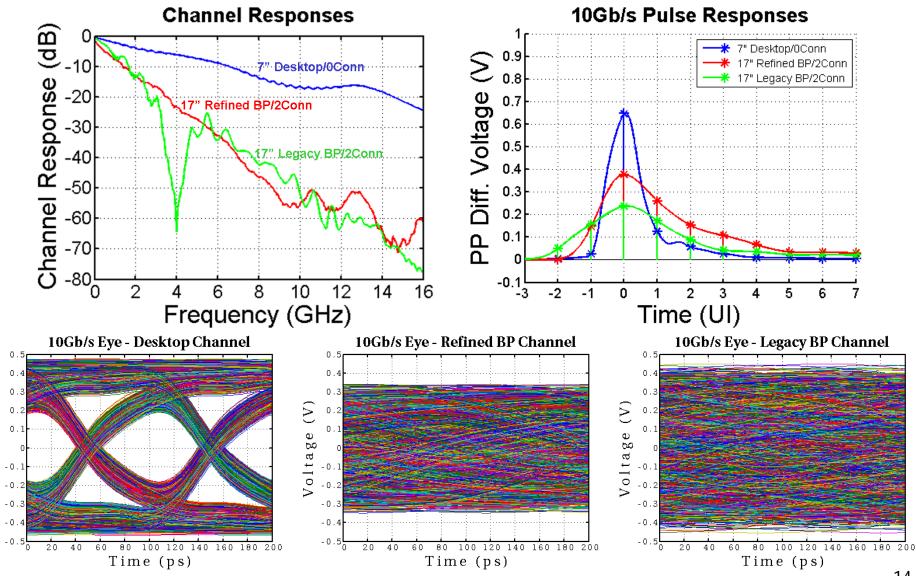

#### **Electrical Backplane Channel**

- Frequency dependent loss

- Dispersion & reflections

- Co-channel interference

- Far-end (FEXT) & near-end (NEXT) crosstalk

#### Loss Mechanisms

Dispersion V(X) ► X Z<sub>0</sub> Z<sub>0</sub> R<sub>0</sub>  $\frac{V(x)}{V(x)} = e^{-(\alpha_R + \alpha_D)x}$ - Skin effect,  $\alpha_{R}$ Skin Depth,  $\delta_{\rm sd} = \left(\frac{\rho}{\mu\pi f}\right)^{1/2}$ **Dispersion Loss** 1.0 Dielectric loss 0.8 Skin Effect  $\alpha_{R} = \frac{R_{AC}}{2Z_{0}} = \frac{\rho L}{\delta_{sd} \pi D 2Z_{0}} = \frac{2.61 \times 10^{-7}}{\pi D 2Z_{0}} \sqrt{f}$ Sum 0.6 0.4 Measured 0.2 - Dielectric loss ,  $\alpha_{D}$  $\alpha_D = \frac{\pi \sqrt{\varepsilon_r} \tan \delta_D}{c} f$ 10MHz 1MHz 100MHz 1GHz 1m 8mil 50 $\Omega$  stripguide with GETEK dielectric

B. Dally et al, "Digital Systems Engineering,"

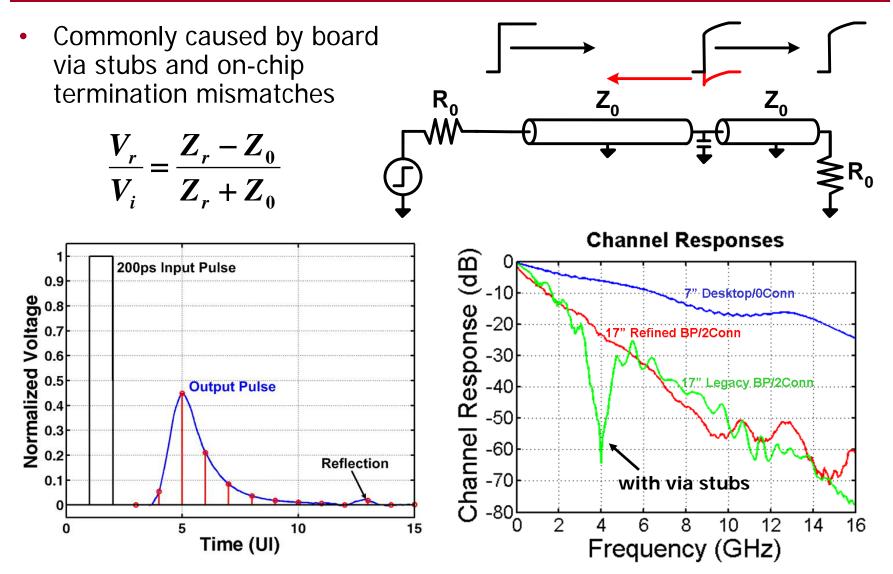

#### Reflections

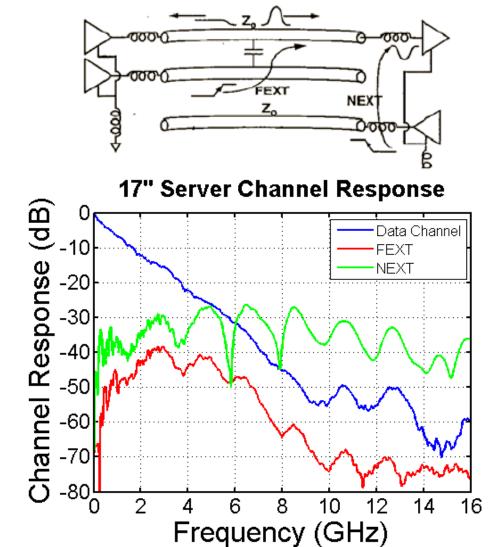

#### Crosstalk

- Occurs mostly in package and boardto-board connectors

- FEXT is attenuated by channel response and has band-pass characteristic

- NEXT directly couples into victim and has high-pass characteristic

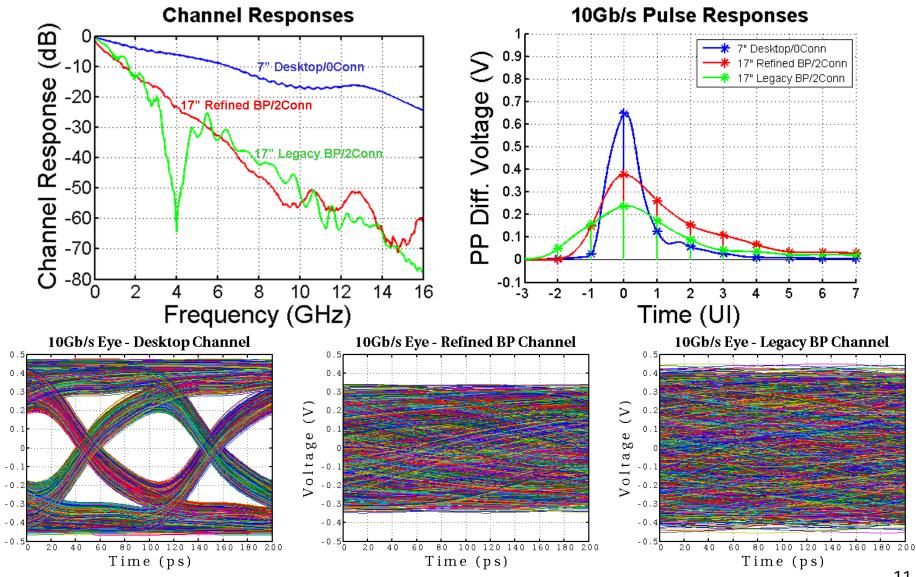

#### **Channel Performance Impact**

$(\mathbf{N})$

Voltage

## Outline

- Introduction

- Channel characteristics

- Equalizer circuits

- Equalizer adaptation techniques

- Optical interconnects

- Conclusion

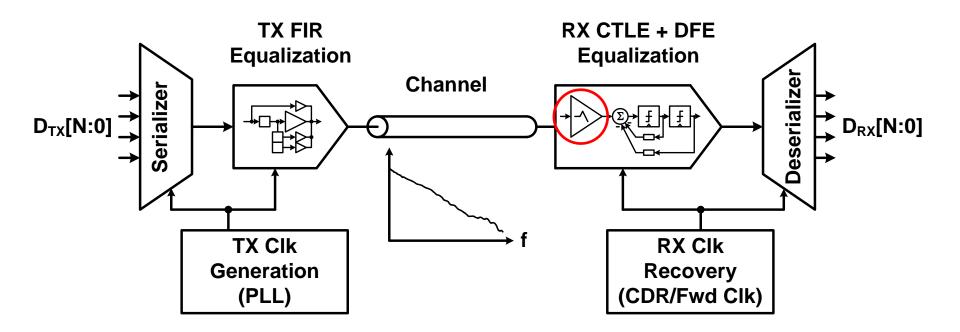

### Link with Equalization

#### **Channel Performance Impact**

$(\mathbf{N})$

Voltage

#### **Channel Performance Impact**

$\geq$

Voltage

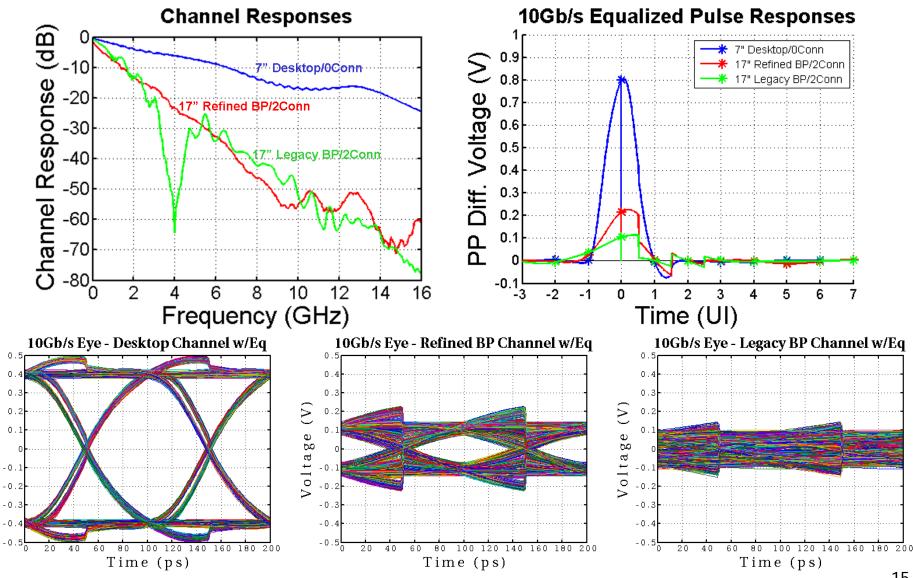

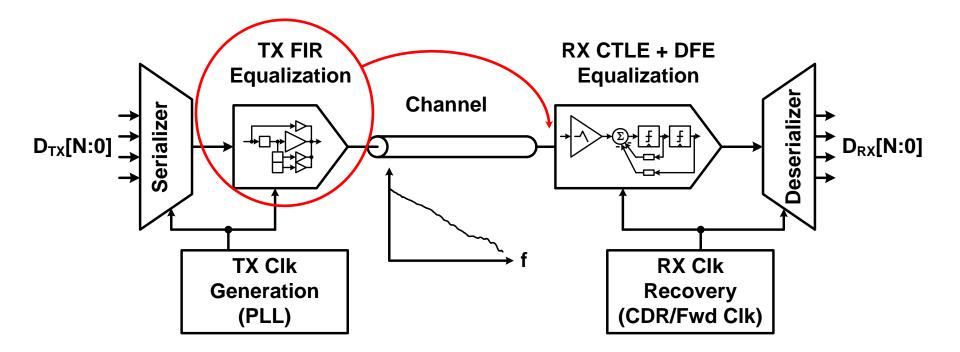

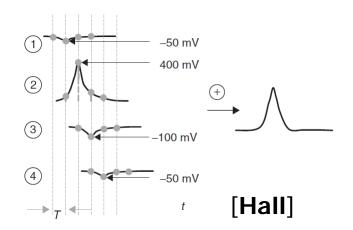

### **Channel Equalization**

Equalization goal is to flatten the frequency response out to the Nyquist Frequency and remove time-domain ISI

### Link with Equalization

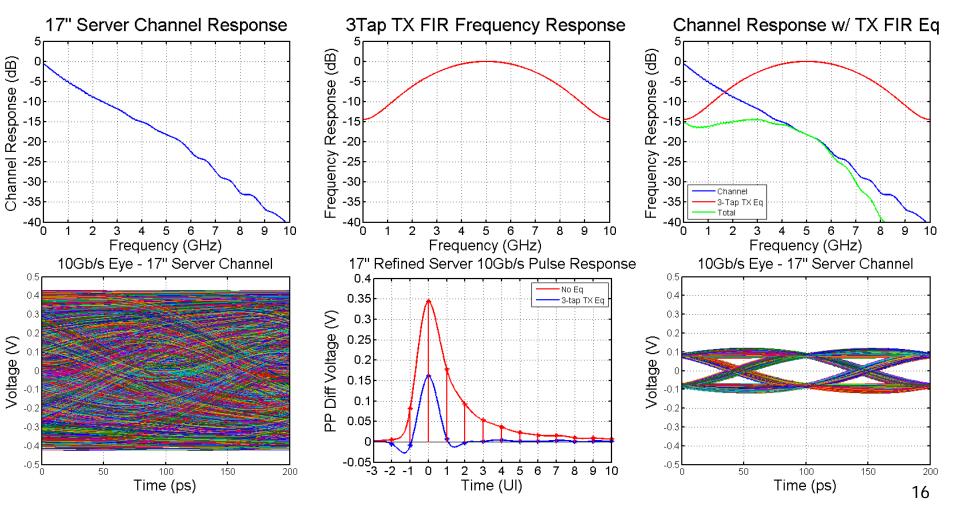

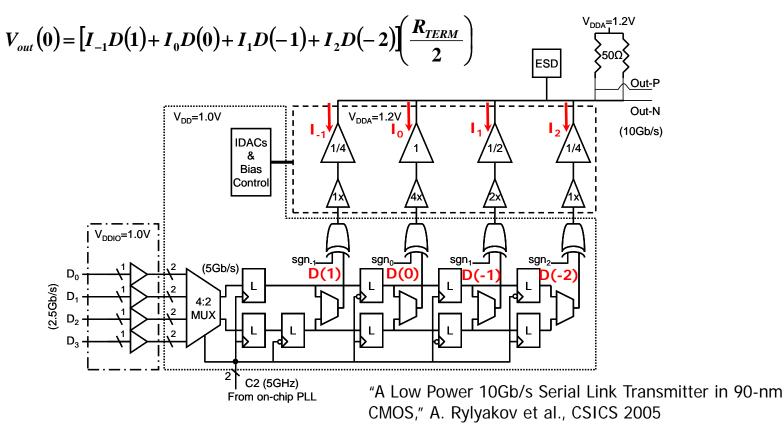

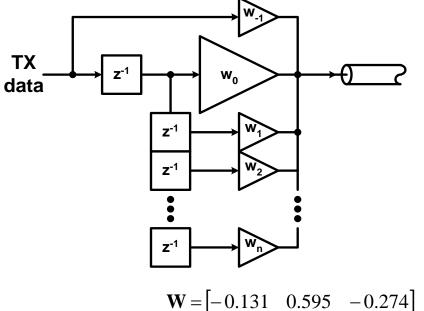

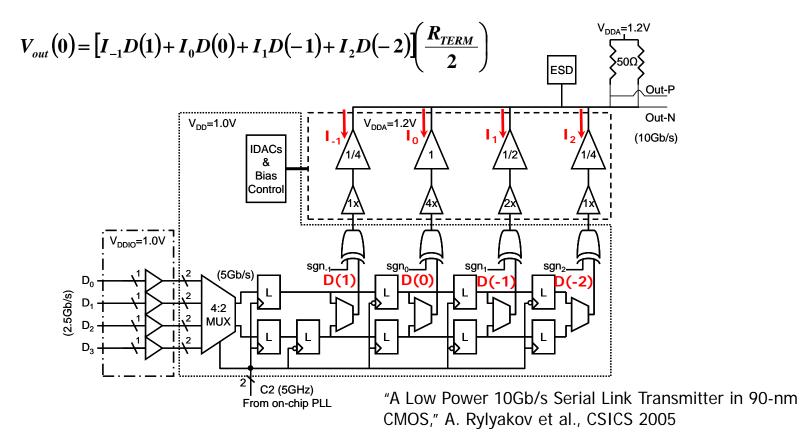

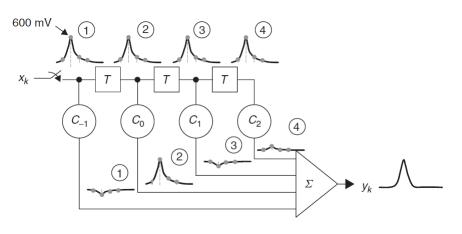

## **TX FIR Equalization**

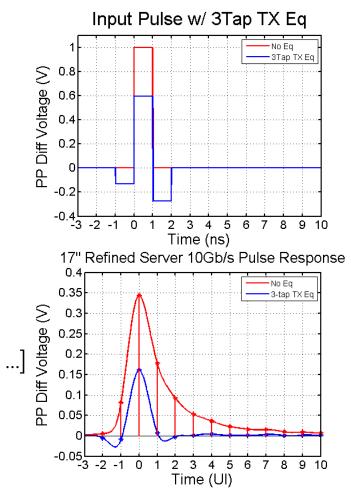

TX FIR filter pre-distorts transmitted pulse in order to invert channel distortion at the cost of attenuated transmit signal (de-emphasis)

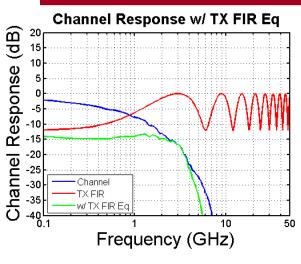

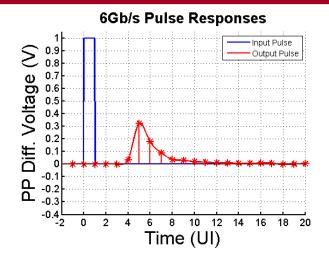

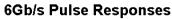

# 6Gb/s TX FIR Equalization Example

- Pros

- Simple to implement

- Can cancel ISI in precursor and beyond filter span

- Doesn't amplify noise

- Can achieve 5-6bit resolution

- Cons

- Attenuates low frequency content due to peak-power limitatior

- Need a "back-channel" to tune filter taps

#### TX FIR Equalization – Time Domain

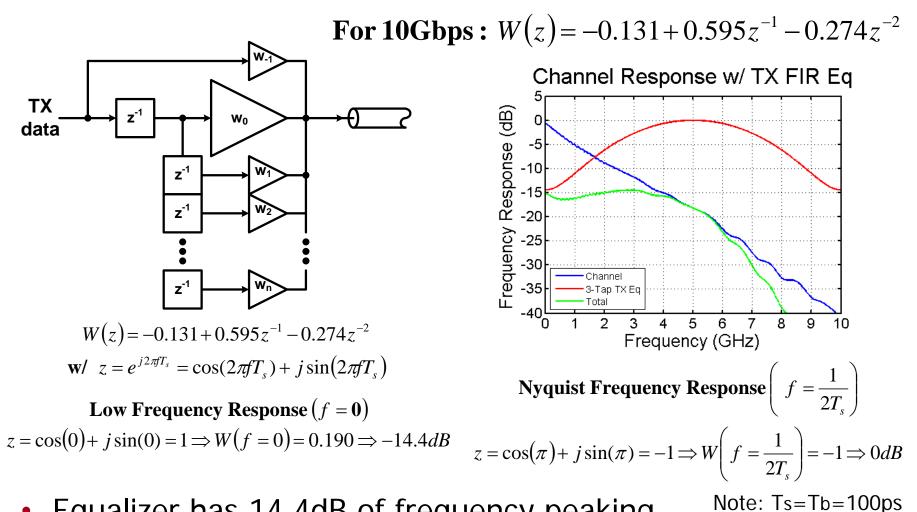

For 10Gbps:

$$W(z) = -0.131 + 0.595z^{-1} - 0.274z^{-2}$$

Low Frequency Response (Sum Taps) [... 1 1 1 ...]\*[ $-0.131 \ 0.595 \ -0.274$ ]=[... 0.190 0.190 0.190

Nyquist Frequency Response (Sum Taps w/ Alternating Polarity) [... -1 1 -1 ...]\*[-0.131 0.595 -0.274]=[... 1 -1 1 ...]

## TX FIR Equalization – Freq. Domain

- Equalizer has 14.4dB of frequency peaking

- Attenuates DC at -14.4dB and passes Nyquist frequency at 0dB

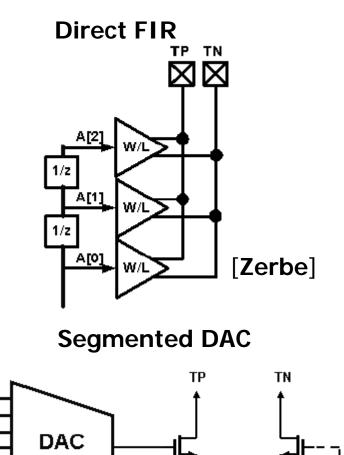

## **TX FIR Circuit Architectures**

- Direct FIR vs Segmented DAC

- Direct FIR

- Parallel output drivers for output taps

- Each parallel driver must be sized to handle its potential maximum current

- Lower power & complexity

- Higher output capacitance

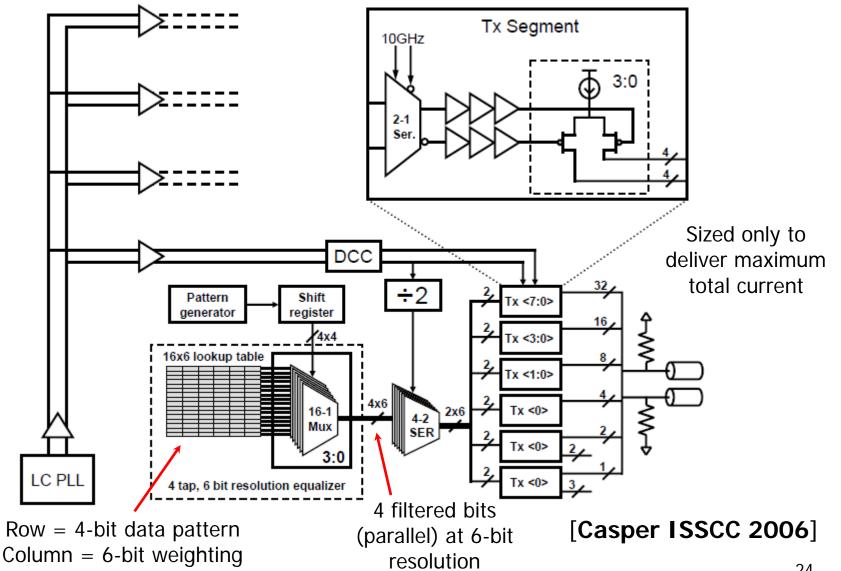

- Segmented DAC

- Minimum sized output transistors to handle peak output current

- Lowest output capacitance

- Most power & complexity

- Need mapping table (RAM)

- Very flexible in equalization

Zerbel

#### **Direct FIR Equalization**

### Segmented DAC Example

### Link with Equalization

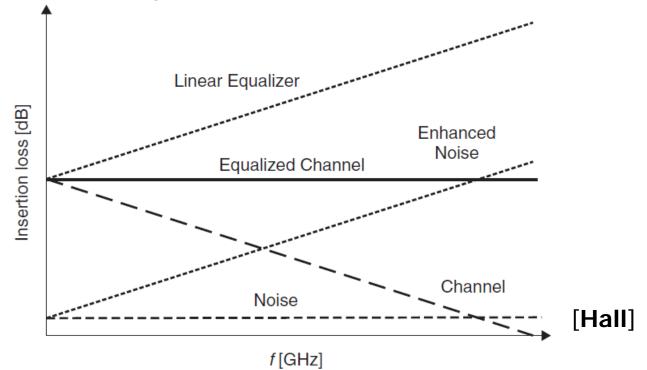

# **RX FIR Equalization**

- Delay analog input signal and multiply by equalization coefficients

- Pros

- With sufficient dynamic range, can amplify high frequency content (rather than attenuate low frequencies)

- Can cancel ISI in pre-cursor and beyond filter span

- Filter tap coefficients can be adaptively tuned without any back-channel

- Cons

- Amplifies noise/crosstalk

- Implementation of analog delays

- Tap precision

## **RX Equalization Noise Enhancement**

- Linear RX equalizers don't discriminate between signal, noise, and cross-talk

- While signal-to-distortion (ISI) ratio is improved, SNR remains unchanged

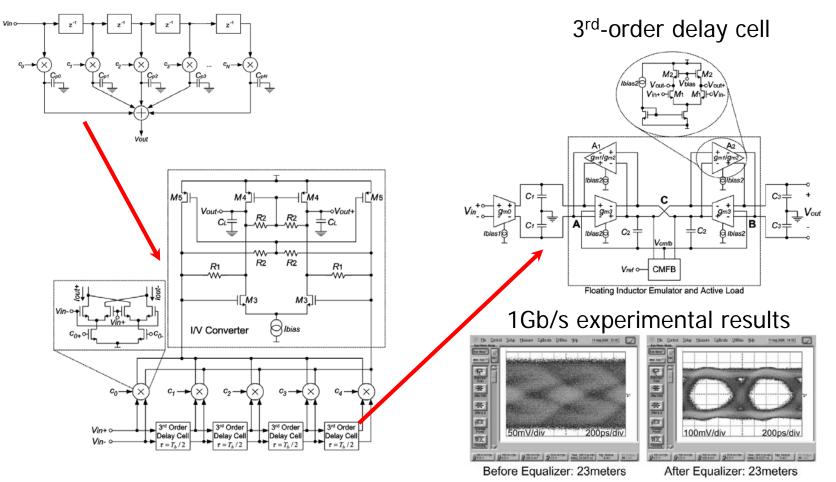

### Analog RX FIR Equalization Example

• 5-tap equalizer with tap spacing of  $T_b/2$

D. Hernandez-Garduno and J. Silva-Martinez, "A CMOS 1Gb/s 5-Tap Transversal Equalizer based on 3<sup>rd</sup>-Order Delay Cells," ISSCC, 2007.

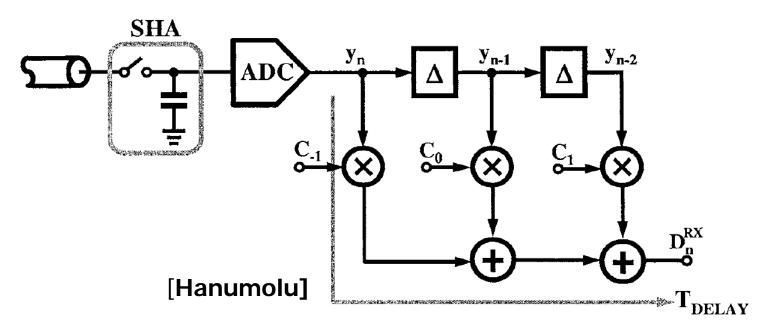

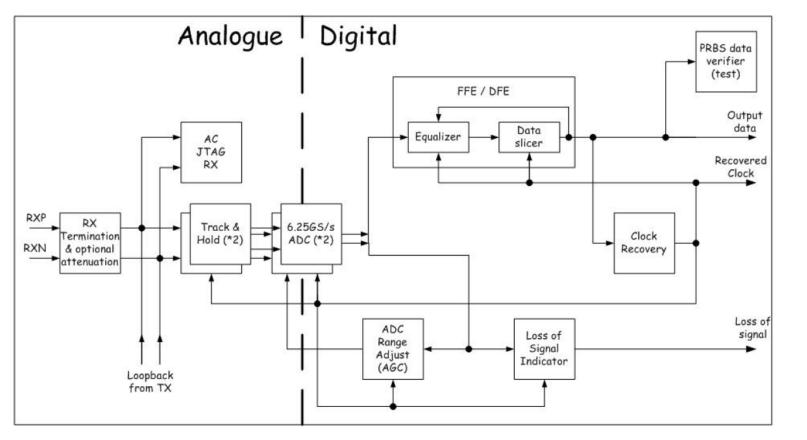

## **Digital RX FIR Equalization**

- Digitize the input signal with high-speed low/medium resolution ADC and perform equalization in digital domain

- Digital delays, multipliers, adders

- Limited to ADC resolution

- Power can be high due to very fast ADC

## Digital RX FIR Equalization Example

- 12.5GS/s 4.5-bit Flash ADC in 65nm CMOS [Ha

- [Harwood ISSCC 2007]

- 2-tap FFE & 5-tap DFE

- XCVR power (inc. TX) = 330mW, Analog = 245mW, Digital = 85mW

### Link with Equalization

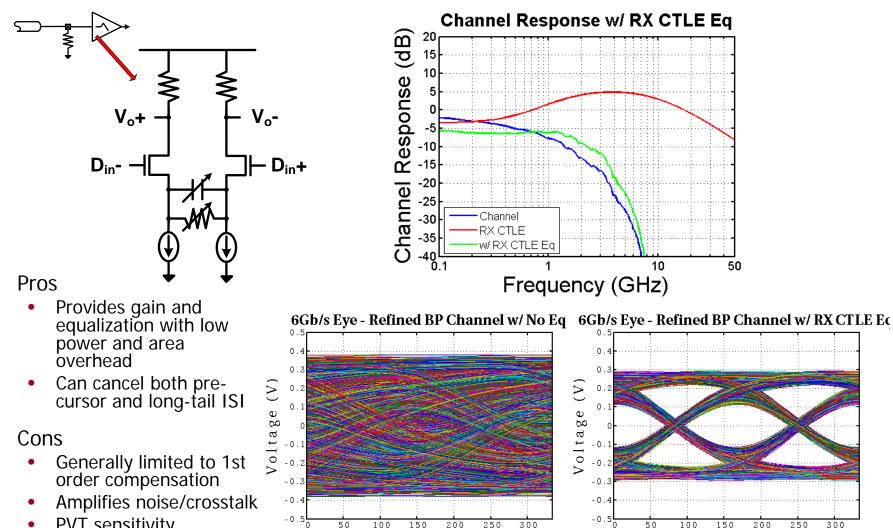

## **RX CTLE Equalization**

Time (ps)

- **PVT** sensitivity

- Can be hard to tune

Time (ps)

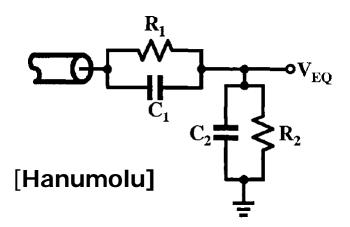

## Passive CTLE

Passive structures offer excellent linearity, but no gain at Nyquist frequency

$$H(s) = \frac{R_2}{R_1 + R_2} \frac{1 + R_1 C_1 s}{1 + \frac{R_1 R_2}{R_1 + R_2}} (C_1 + C_2) s$$

$$\omega_z = \frac{1}{R_1 C_1}, \qquad \omega_p = \frac{1}{\frac{R_1 R_2}{R_1 + R_2}} (C_1 + C_2)$$

$$DC \text{ gain} = \frac{R_2}{R_1 + R_2}, \text{ HF gain} = \frac{C_1}{C_1 + C_2}$$

$$Peaking = \frac{HF \text{ gain}}{DC \text{ gain}} = \frac{\omega_p}{\omega_z} = \frac{R_1 + R_2}{R_2} \frac{C_1}{C_1 + C_2}$$

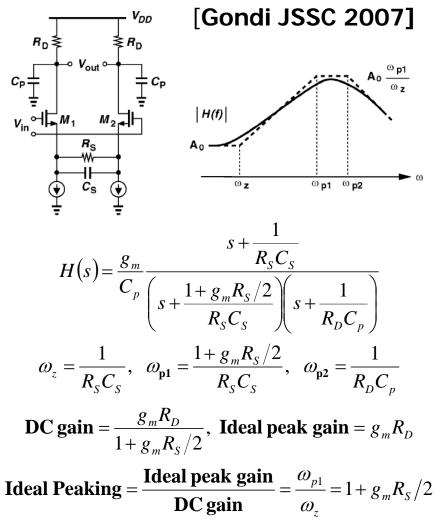

# Active CTLE

- Input amplifier with RC degeneration can provide frequency peaking with gain at Nyquist frequency

- Potentially limited by gainbandwidth of amplifier

- Amplifier must be designed for input linear range

- Often TX eq. provides some low frequency attenuation

- Sensitive to PVT variations and can be hard to tune

- Generally limited to 1<sup>st</sup>-order compensation

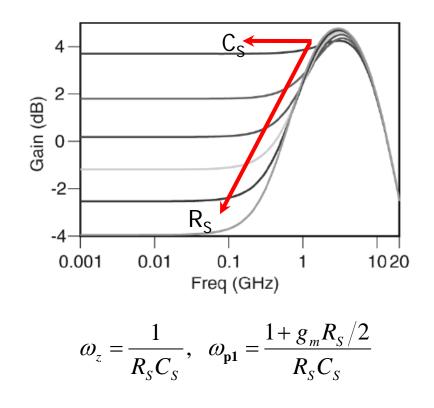

## Active CTLE Tuning

- Tune degeneration resistor and capacitor to adjust zero frequency and 1<sup>st</sup> pole which sets peaking and DC gain

- Increasing C<sub>s</sub> moves zero and 1<sup>st</sup> pole to a lower frequency w/o impacting (ideal) peaking

- Increasing R<sub>s</sub> moves zero to lower frequency and increases peaking (lowers DC gain)

- Minimal impact on 1<sup>st</sup> pole

### Link with Equalization

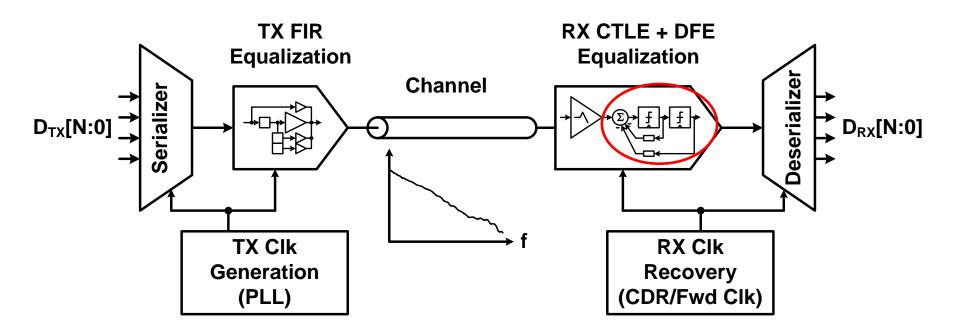

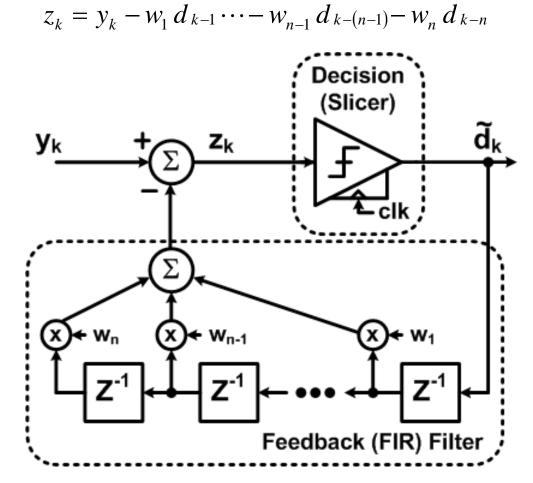

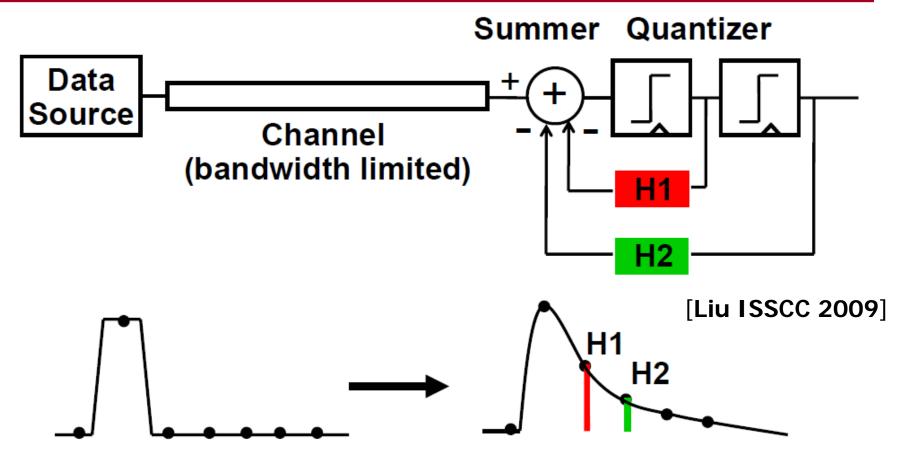

#### **RX** Decision Feedback Equalization (DFE)

- DFE is a non-linear equalizer

- Slicer makes a symbol decision, i.e. quantizes input

- ISI is then directly subtracted from the incoming signal via a feedback FIR filter

#### **RX** Decision Feedback Equalization (DFE)

- Pros

- Can boost high frequency content without noise and crosstalk amplification

- Filter tap coefficients can be adaptively tuned without any back-channel

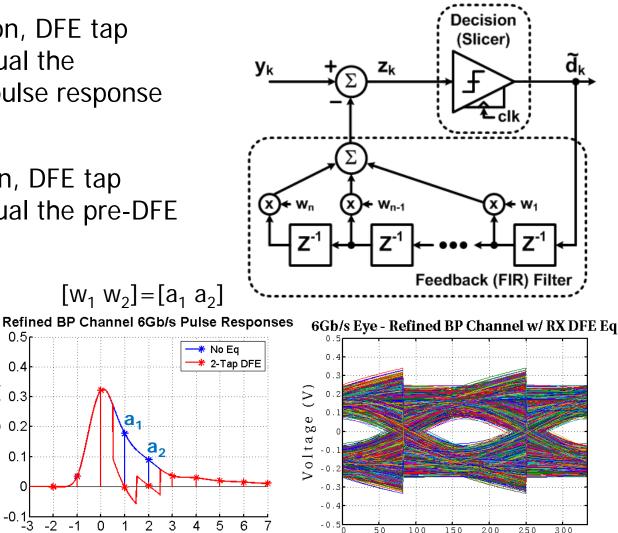

- $z_k = y_k w_1 d_{k-1} \cdots w_{n-1} d_{k-(n-1)} w_n d_{k-n}$ Decision (Slicer) **đ**<sub>k</sub> Zk ← W<sub>n-1</sub> X Feedback (FIR) Filter Pre-Cursor Post-Cursor DFE region of influence [Payne]

• Cons

- Cannot cancel pre-cursor ISI

- Chance for error propagation

- Low in practical links (BER=10<sup>-12</sup>)

- Critical feedback timing path

- Timing of ISI subtraction complicates CDR phase detection

### DFE Example

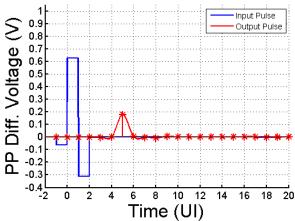

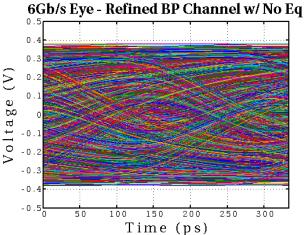

6Gb/s Eye - Refined BP Channel w/ No Eq

200

250

300

0.5

0

0.

Ο.

Ο.

-0.

-0.2 -0.3

-0.4

-0.5

50

100

150

Time (ps)

$\geq$

Voltage

- If only DFE equalization, DFE tap coefficients should equal the unequalized channel pulse response values  $[a_1 a_2 \dots a_n]$

- With other equalization, DFE tap coefficients should equal the pre-DFE pulse response values

0.5

0.4

0.2

01

-0.1∟ -3

-2

-1 0

Time (UI)

S 0.3

Voltage

Time (ps)

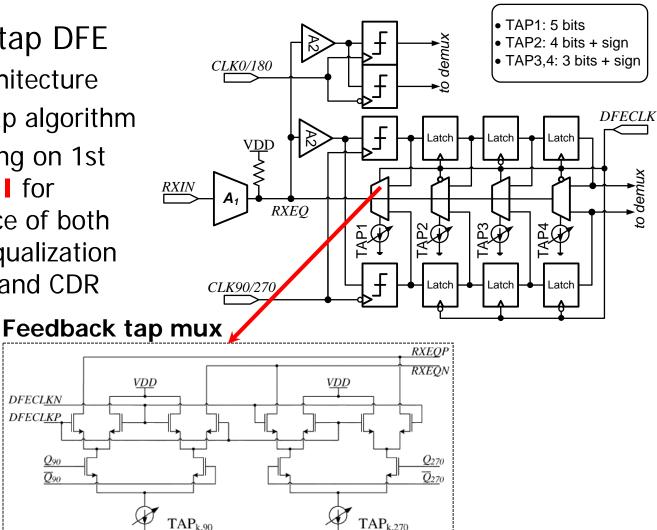

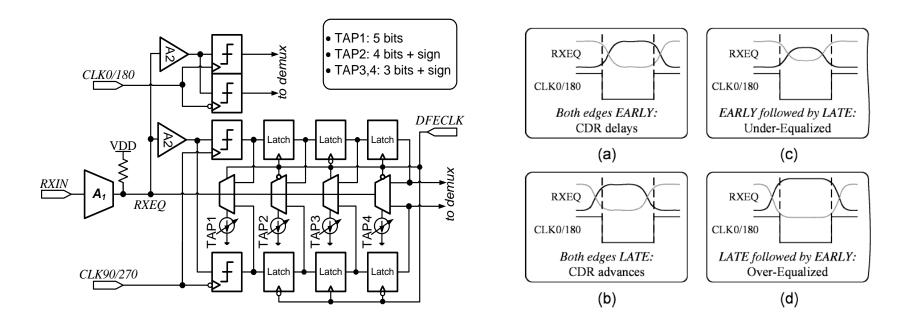

# Direct Feedback DFE Example (TI)

- 6.25Gb/s 4-tap DFE

- $\frac{1}{2}$  rate architecture

- Adaptive tap algorithm

- Closes timing on 1st tap in 1/2 UI for convergence of both adaptive equalization tap values and CDR

DFECLKN DFECL<u>KP</u>

$Q_{90}$

$\overline{Q}_{90}$

R. Payne et al, "A 6.25-Gb/s Binary Transceiver in 0.13-um CMOS for Serial Data Transmission Across High Loss Legacy Backplane Channels," JSSC, vol. 40, no. 12, Dec. 2005, pp. 2646-2657

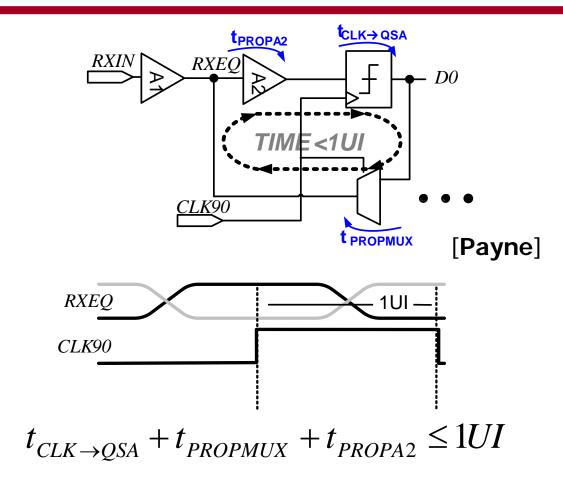

#### **Direct Feedback DFE Critical Path**

- Must resolve data and feedback in 1 bit period

- TI design actually does this in <sup>1</sup>/<sub>2</sub>UI for CDR

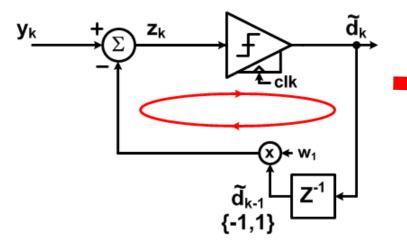

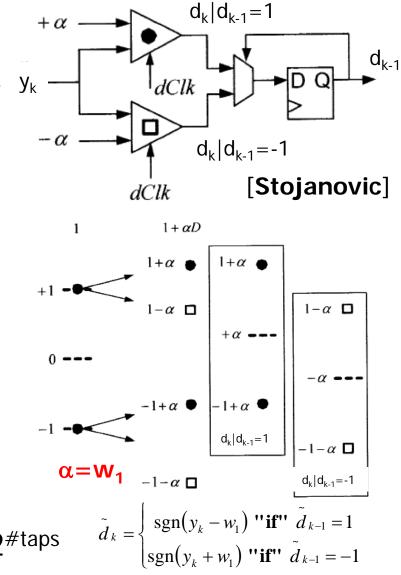

# DFE Loop Unrolling

- Instead of feeding back and subtracting ISI in 1UI

- Unroll loop and pre-compute 2 possibilities (1-tap DFE) with adjustable slicer threshold

- With increasing tap number, comparator number grows as 2<sup>#taps</sup>

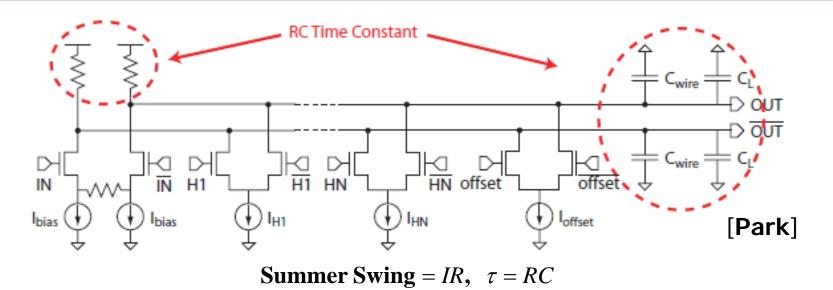

#### **DFE Resistive-Load Summer**

- Summer performance is critical for DFE operation

- Summer must settle within a certain level of accuracy (>95%) for ISI cancellation

- Trade-off between summer output swing and settling time

- Can result in large bias currents for input and taps

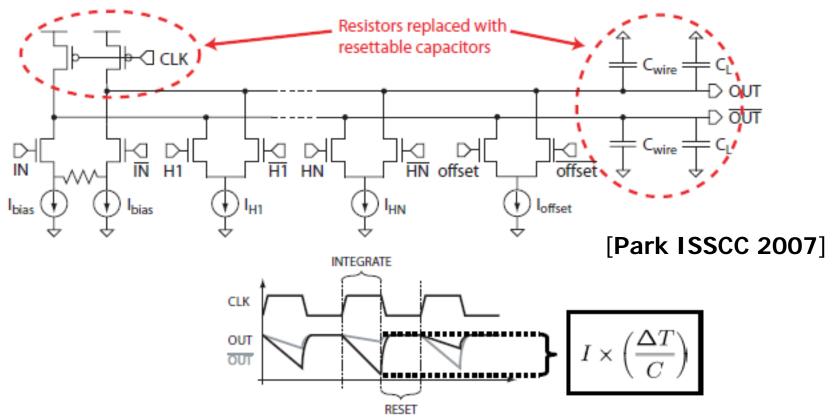

# **DFE Integrating Summer**

- Integrating current onto load capacitances eliminates RC settling time

- Since  $\Delta T/C > R$ , bias current can be reduced for a given output swing

- Typically a 3x bias current reduction

#### Digital RX FIR & DFE Equalization Example

12.5GS/s 4.5-bit Flash ADC in 65nm CMOS [Ha

[Harwood ISSCC 2007]

- 2-tap FFE & 5-tap DFE

- XCVR power (inc. TX) = 330mW, Analog = 245mW, Digital = 85mW

#### DFE with Feedback FIR Filter

DFE with 2-tap FIR filter in feedback will only cancel ISI of the first two post-cursors

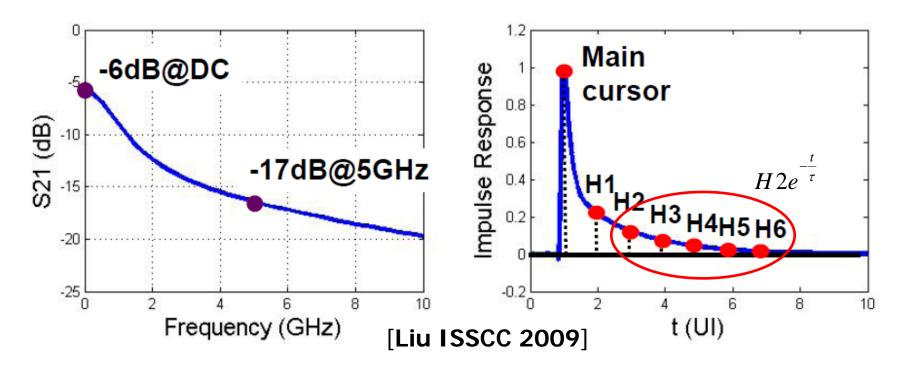

#### "Smooth" Channel

- A DFE with FIR feedback requires many taps to cancel ISI

- Smooth channel long-tail ISI can be approximated as exponentially decaying

- Examples include on-chip wires and silicon carrier wires

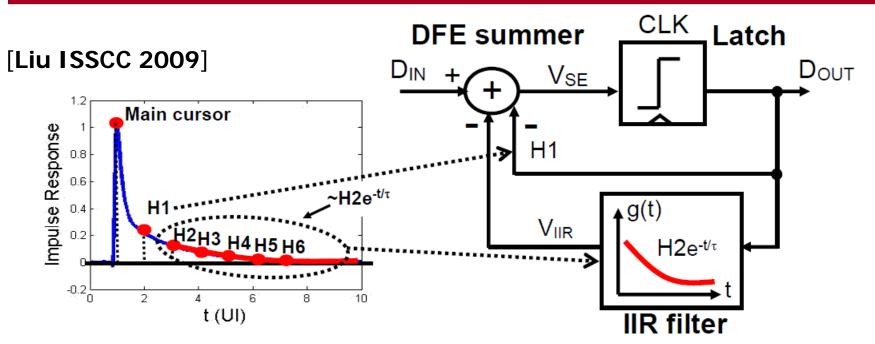

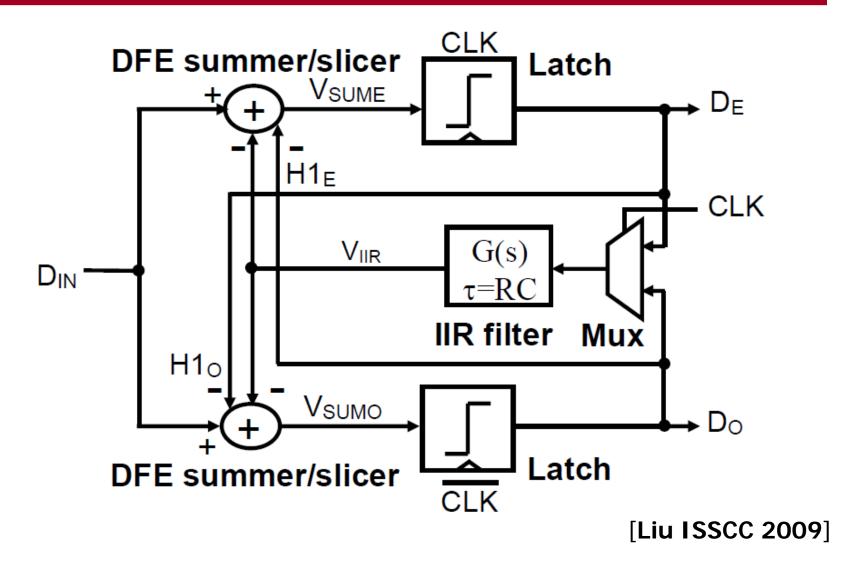

## DFE with IIR Feedback

- Large 1<sup>st</sup> post-cursor H1 is canceled with normal FIR feedback tap

- Smooth long tail ISI from 2<sup>nd</sup> post-cursor and beyond is canceled with low-pass IIR feedback filter

- Note: channel needs to be smooth (not many reflections) in order for this approach to work well 48

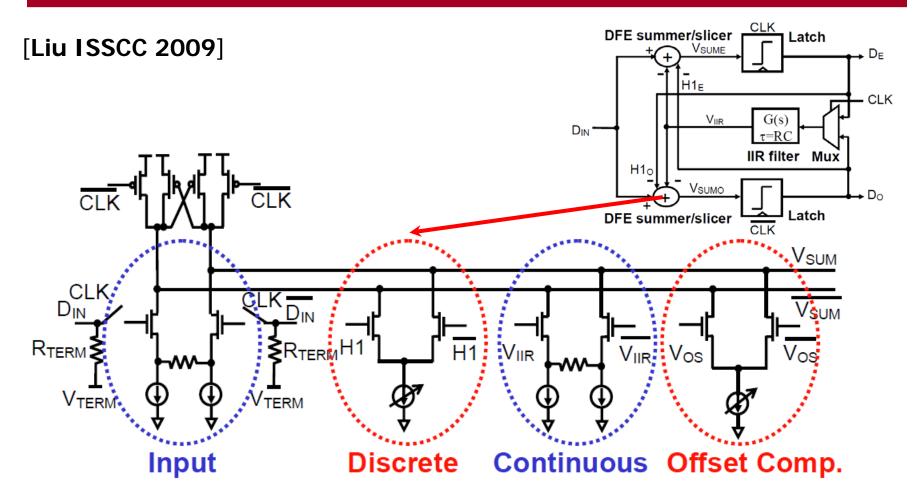

#### DFE with IIR Feedback RX Architecture

### Merged Summer & Partial Slicer

Integrating summer with regeneration PMOS devices to realize partial slicer operation

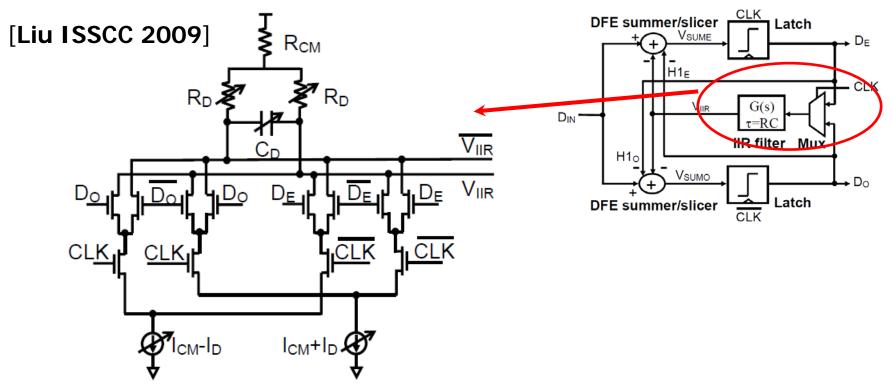

# Merged Mux & IIR Filter

- Low-pass response (time constant) implemented by R<sub>D</sub> and C<sub>D</sub>

- Amplitude controlled by R<sub>D</sub> and I<sub>D</sub>

- 2 UI delay implemented through mux to begin cancellation at 2<sup>nd</sup> post-cursor

## Outline

- Introduction

- Channel characteristics

- Equalizer circuits

- Equalizer adaptation techniques

- Optical interconnects

- Conclusion

# Setting Equalizer Values

- Simplest approach to setting equalizer values (tap weights, poles, zeros) is to fix them for a specific system

- Choose optimal values based on lab measurements

- Sensitive to manufacturing and environment variations

- An adaptive tuning approach allows the optimization of the equalizers for varying channels, environmental conditions, and data rates

- Important issues with adaptive equalization

- Extracting equalization correction (error) signals

- Adaptation algorithm and hardware overhead

- Communicating the correction information to the equalizer circuit

## **TX FIR Adaptation Error Extraction**

- While we are adapting the TX FIR, we need to measure the response at the receiver input

- Equalizer adaptation (error) information is often obtained by comparing the receiver input versus the desired symbol levels, dLev

- This necessitates additional samplers at the receiver with programmable threshold levels

## **TX FIR Adaptation Algorithm**

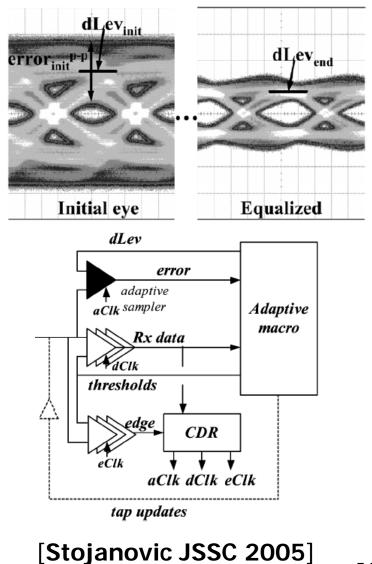

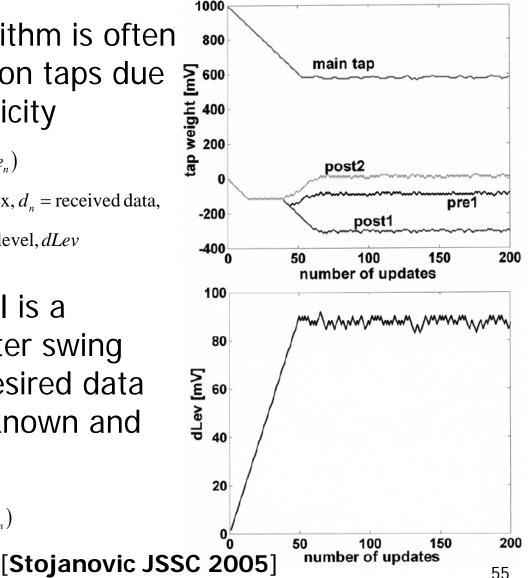

The sign-sign LMS algorithm is often used to adapt equalization taps due to implementation simplicity

$w_{n+1}^k = w_n^k + \Delta_w \operatorname{sign}(d_{n-k})\operatorname{sign}(e_n)$

$$w =$$

tap coefficients,  $n =$  time instant,  $k =$  tap index,  $d_n =$  received data,

$e_n$  = error with respect to desired data level, dLev

As the desired data level is a function of the transmitter swing and channel loss, the desired data level is not necessarily known and should also be adapted

$$dLev_{n+1} = dLev_n - \Delta_{dLev} \operatorname{sign}(e_n)$$

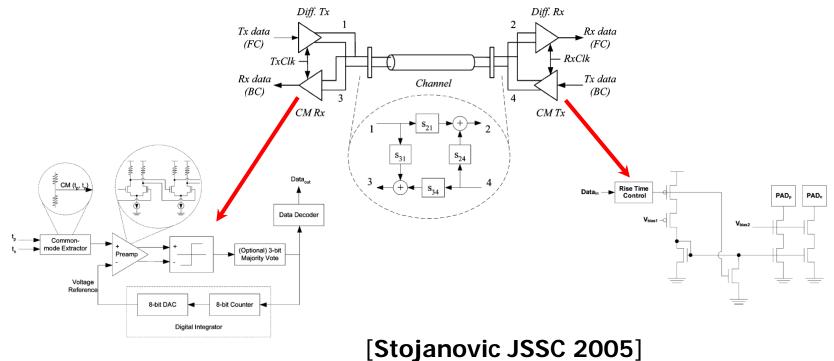

### TX FIR Common-Mode Back-Channel

- In order to communicate FIR tap update information back to the TX, a back-channel is necessary

- One option is to use low data rate (~10Mb/s) commonmode signaling from the RX to TX on the same differential channel

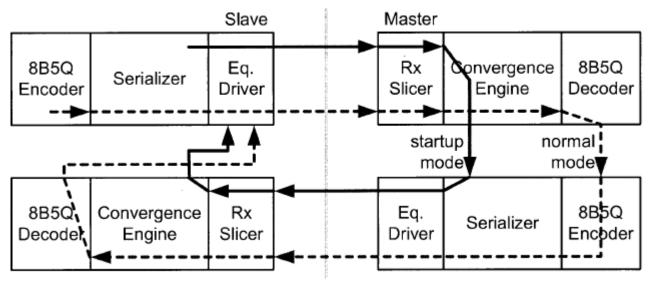

## TX FIR Data Encoder Back-Channel

- Another option is to use a high-speed TX channel on the RX side that communicates data back to the TX under adaptation

- Flexibility in data encoding (8B10B/Q) allows low data rate tap adaptation information to be transmitted back without data rate overhead

[Stonick JSSC 2003]

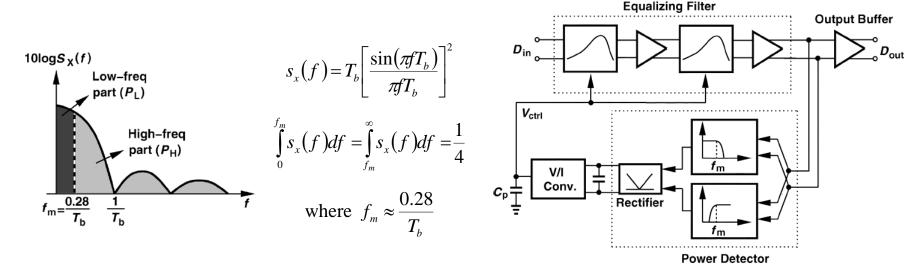

# CTLE Tuning with PSD Measurement

- One approach to CTLE tuning is to compare low-frequency and high-frequency spectrum content of random data

- For ideal random data, there is a predictable ratio between the low-frequency power and high-frequency power

- The error between these power components can be used in a servo loop to tune the CTLE

[Lee JSSC 2006]

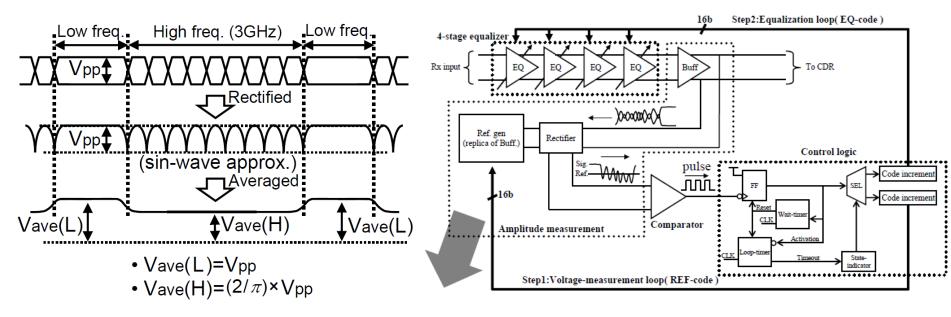

#### CTLE Tuning w/ Output Amplitude Measurement

- CTLE tuning can also be done by comparing low-frequency and highfrequency average amplitude

- Approximating the equalized data as a sine wave, a predictable ratio exists between the low frequency average and high-frequency average

- Equalizer settings are adjusted until the high frequency peak-to-peak swing matches the low-frequency peak-to-peak swing

[Uchiki ISSCC 2008]

# DFE Tuning

- 2x oversampling the equalized signal at the edges can be used to extract information to adapt a DFE and drive a CDR loop

- Sign-sign LMS algorithm used to adapt DFE tap values

## Outline

- Introduction

- Channel characteristics

- Equalizer circuits

- Equalizer adaptation techniques

- Optical interconnects

- Conclusion

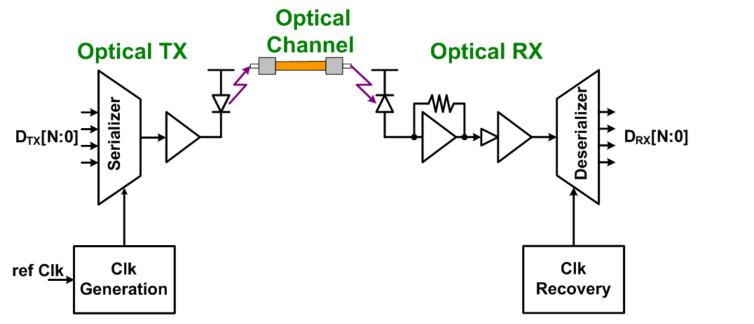

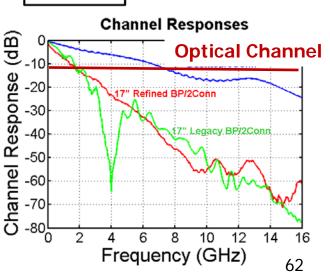

# High-Speed Optical Link System

- Optical interconnects remove many channel limitations

- Reduced complexity and power consumption

- Potential for high information density with wavelength-division multiplexing (WDM)

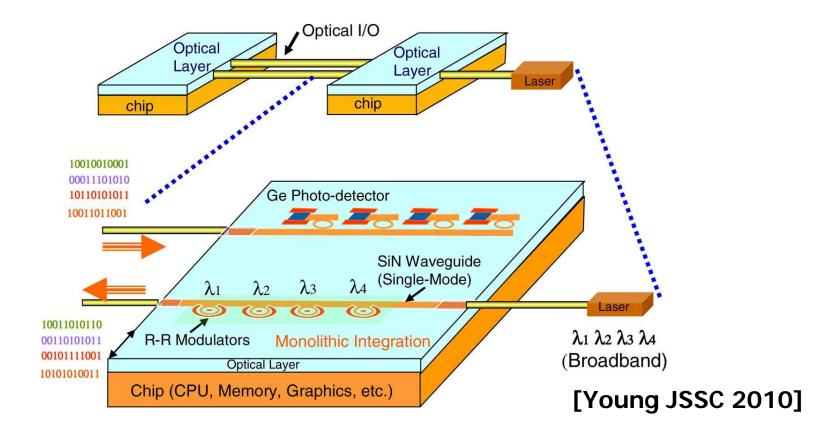

# Wavelength-Division Multiplexing

WDM allows for multiple high-bandwidth (10+Gb/s) signals to be packed onto one optical channel

### **Conclusion & Future Trends**

- Data rates are scaling faster than electrical channel bandwidths, necessitating higher complexity, adaptive, and more efficient equalization circuits

- Nanometer CMOS scaling also provides the potential for more advanced systems to deal with ISI

- ADC front-ends with complex digital equalization

- Error-correction coding

- On the horizon are optical interconnect systems which provide the potential for distance-independent bandwidth which scales with the number of wavelengths/channel