#### RF Harmonic Oscillators Integrated in Silicon Technologies

Pietro Andreani Dept. of Electrical and Information Technology (EIT) Lund University, Sweden

SSCS Distinguished Lecture

Qualcomm, S. Diego, California Friday, 15 Feb. 2019

#### Overview

- Popular harmonic oscillators

- Phase noise

- Architectures for low 1/f<sup>2</sup> and/or 1/f<sup>3</sup> phase noise

- □ Series-resonance oscillator

- Design techniques for very wide frequency tuning range RF CMOS VCOs

SSCS

SSCS

P. Andreani, SSCS DL, Qualcomm, 15 Feb. 2019

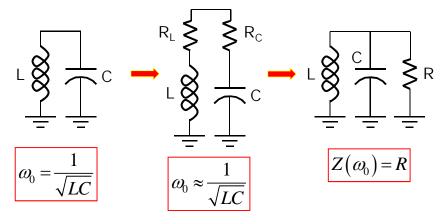

# LC resonator

We begin with an inductor-capacitor resonator

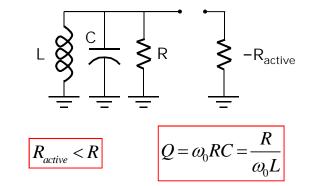

# Building a harmonic oscillator

Tank losses are compensated by an active negative resistance in parallel to the tank

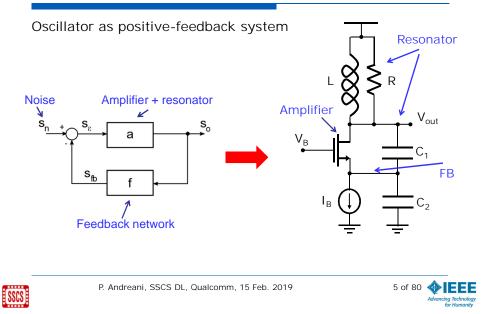

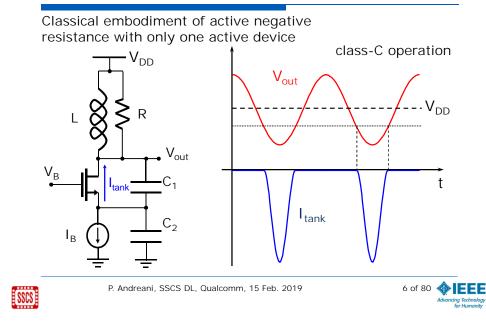

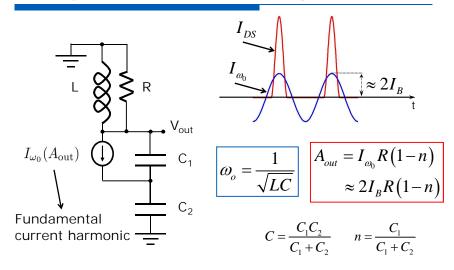

# Colpitts oscillator

# Colpitts oscillator

Analysis with Describing Function

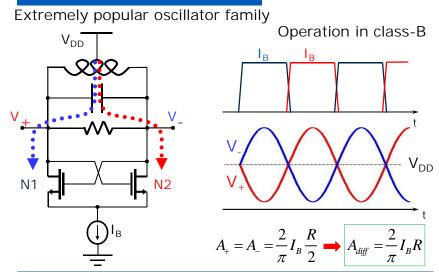

#### Cross-coupled differential-pair oscillator

SSCS

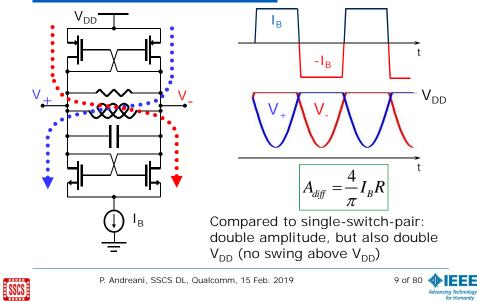

# Class-B with double switch pair

P. Andreani, SSCS DL. Qualcomm, 15 Feb. 2019

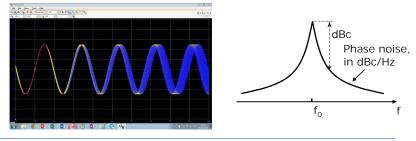

Real oscillations

- $\Box$  Phase uncertainty grows with time  $\rightarrow$  jitter

- Caused by various noise sources

- □ Jitter increases without bound in a free-running oscillator

- □ In the frequency domain, the oscillator displays phase noise

#### **Overview**

- Popular harmonic oscillators

- Phase noise

- □ Architectures for low 1/f<sup>2</sup> and/or 1/f<sup>3</sup> phase

- Series-resonance oscillator

- Design techniques for very wide frequency

SSCS

P. Andreani, SSCS DL. Qualcomm, 15 Feb, 2019

# Why bother?

- Phase noise in transceiver is important for at least three reasons:

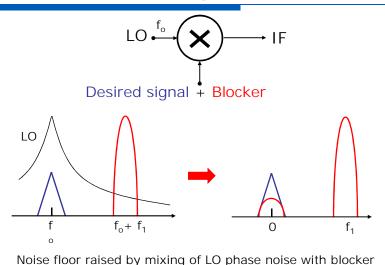

- In a receiver, it can downconvert large nearby signals on top of the desired signal

- □ In a transmitter, it can increase the noise floor in the receive band

- In both, it can directly corrupt the phase information in the signal

- Not seldom, the phase noise of the VCO is the bottleneck for the whole radio performance

# Reciprocal mixing

P. Andreani, SSCS DL, Qualcomm, 15 Feb. 2019

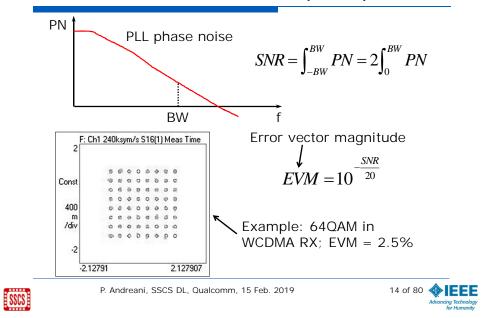

Phase noise and SNR (EVM)

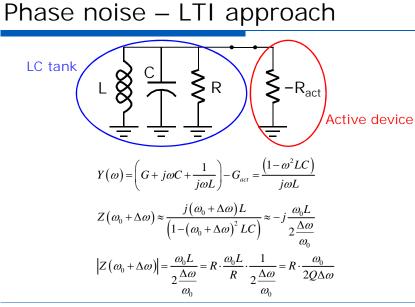

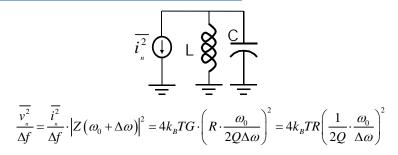

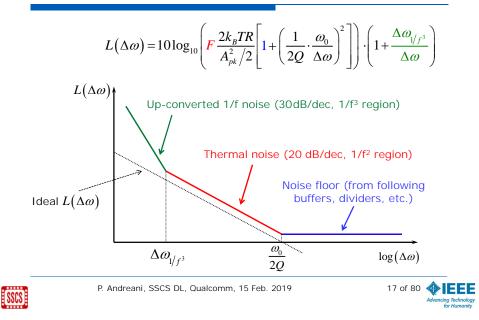

#### Phase noise from tank losses

- Both amplitude and phase noise, but amplitude noise is rejected

- Thus, phase noise is defined as half the above expression, normalized to the output signal power (in dB below the carrier per Hertz, dBc/Hz):

$$L(\Delta\omega) = 10\log_{10}\left(\frac{\overline{v_{n}^{2}}/2}{A_{pk}^{2}/2}\right) = 10\log_{10}\left(\frac{2k_{B}TR}{A_{pk}^{2}/2}\left(\frac{1}{2Q}\cdot\frac{\omega_{0}}{\Delta\omega}\right)^{2}\right)$$

[SSCS]

13 of 80 🚸 EEE

# Leeson's equation

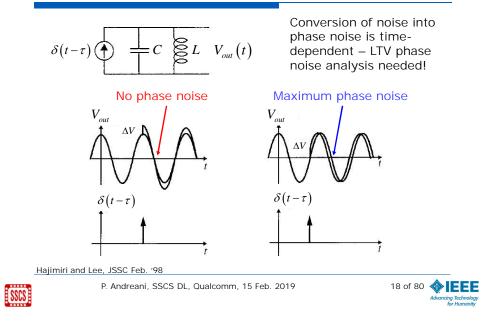

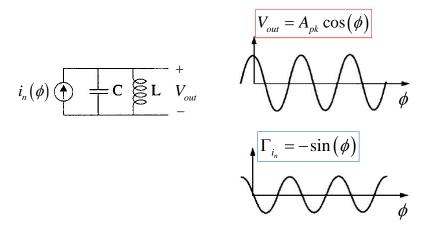

Impulse sensitivity function (ISF,  $\Gamma$ )

- Current noise source  $i_n(\phi)$  is weighed by associated  $\Gamma_{i_n}(\phi)$

- → effective current noise  $i_{n,eff}(\phi) = i_n(\phi) \cdot \Gamma_{i_n}(\phi)$   $(\phi = \omega_0 t)$

- ISF is dimensionless, frequency- and amplitude independent, with period 2π:

$$\Gamma\left(\phi\right) = \frac{c_0}{2} + \sum_{n=1}^{\infty} c_n \cos\left(n\phi + \phi_n\right)$$

# Hajimiri and Lee's theory of phase noise

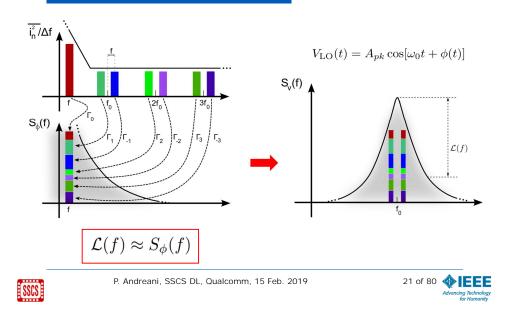

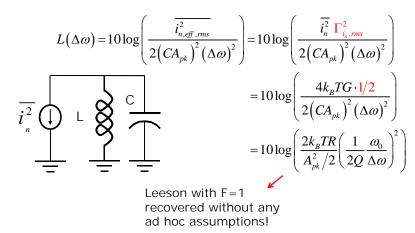

#### Phase noise expression

If  $i_n(\phi)$  is a (cyclo)stationary white current noise source, its contribution to  $1/f^2$  phase noise is

$$L(\Delta \omega) = 10 \log \left( \frac{\overline{i_{n,eff,rms}^2}}{2(CA_{pk})^2 (\Delta \omega)^2} \right)$$

$$i_n(\phi) + C + A_{pk} \cos(\omega t + \phi(t))$$

# Graphical interpretation

# Example of ISF – LC oscillators

Hajimiri and Lee, JSSC Feb. '98; Andreani and Wang, JSSC Nov. '04

SSCS

P. Andreani, SSCS DL, Qualcomm, 15 Feb. 2019

# A particularly simple case

Parallel RLC resonator again – phase noise from tank losses:

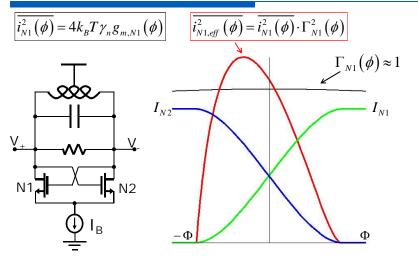

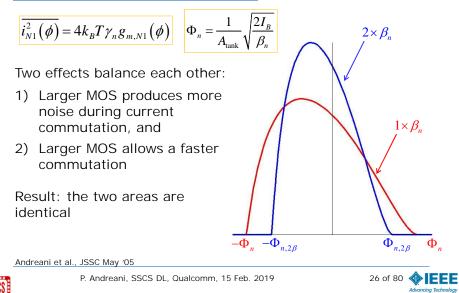

#### Phase noise from MOS pair

Two commutations in one oscillation period

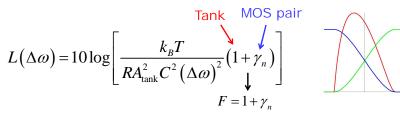

## Total phase noise

- $\blacksquare$  Transistors appear only through channel noise factor  $\gamma_n$

- $\blacksquare$  Transistor phase noise always proportional to tank noise (60% from tank, 40% from MOS pair, if  $\gamma_{\rm n}$  = 2/3)

- This is because: 1) transistor noise is proportional to commutation time, 2) which is inversely proportional to the oscillation amplitude, 3) which is proportional to the tank parallel resistance

- A simple-minded LTI analysis would yield very wrong predictions (i.e., MOS phase noise increases with MOS g<sub>m</sub>)

P. Andreani, SSCS DL, Qualcomm, 15 Feb. 2019

#### MOS phase noise - invariance

Noise injected into tank when ISF is near zero  $\rightarrow$  excellent!

Hajimiri and Lee, JSSC Feb. '98; Andreani et al., JSSC May '05

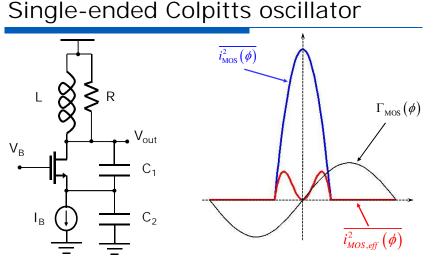

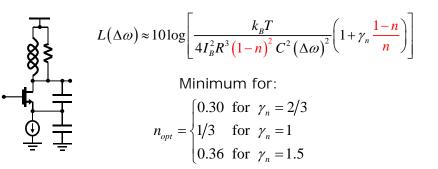

# Phase noise in Colpitts oscillator

However, contrary to what was once (justifiably) believed, Colpitts is <u>more</u> noisy than the differential-pair LC oscillator!

Andreani et al., JSSC May '05

### Harmonic oscillators - a general result

- 1)  $\Gamma$  sinusoidal and in quadrature with tank voltage

- 2) Active devices work as transistors

- 3) Transistor current noise proportional to  ${\rm g}_{\rm m}$

#### Transistor effective noise depends only on tank loss and topology

J. Bank, "A harmonic oscillator design methodology based on describing functions", PhD thesis, Gothenburg, Sweden, 2006 Mazzanti and Andreani, JSSC Dec. '08; Murphy et al, TCAS-I June '10

P. Andreani, SSCS DL, Qualcomm, 15 Feb. 2019

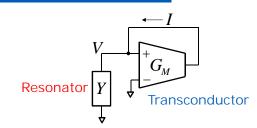

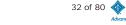

# Alternative phase noise analysis

Matrix-based Fourier-series LTV approach, starting from

- $\vec{I} = \mathbf{Y}\vec{V}$  and  $\vec{dI} = \mathbf{G}_{\mathbf{M}}\vec{dV}$

- All quantities are functions of  $\mathit{w}_{\!0}\text{,}~2\mathit{w}_{\!0}\text{,}~\dots$  ,  $n\mathit{w}_{\!0}$

Pepe and Andreani, TCAS-I Feb. 2017

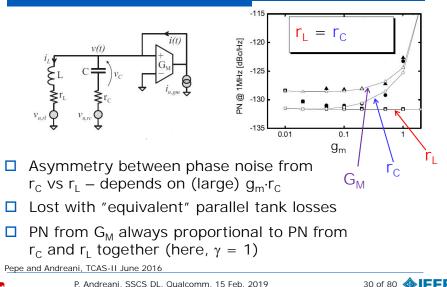

#### More on inductive vs capacitive losses

comm, 15 Feb. 2019

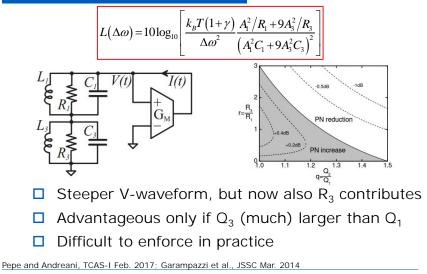

### Results of new phase noise analysis

- □ Rigorous analysis under very broad hypotheses

- $G_M$  pure transconductance; Y linear;  $G_M$  noise proportional to  $G_M$  via  $\gamma$

- Phase noise from G<sub>M</sub> always in proportion of γ:1 to phase noise from Y, independently of resonator and transconductor nature

- D Phase noise expressions as functions of V and Y

- Closed-form, explicit phase noise expressions if Q is high

- General case of Y resonating at multiples of *a*<sub>0</sub>

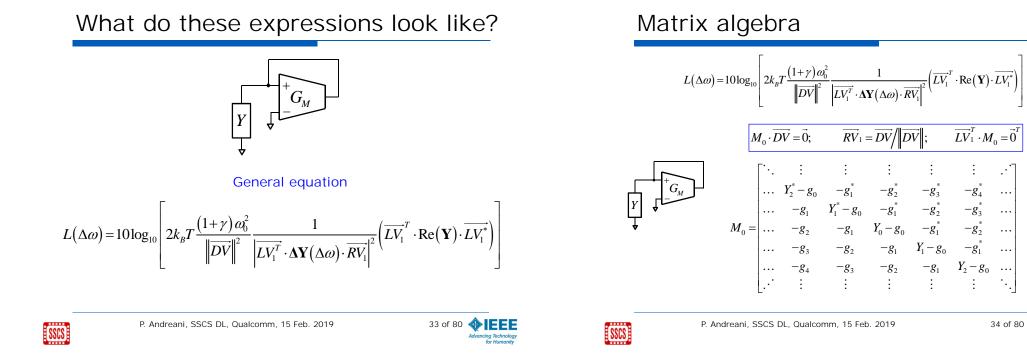

# Tank with multiple resonances

# Tank resonating at $\omega_0$ and $3\omega_0$

SSCS

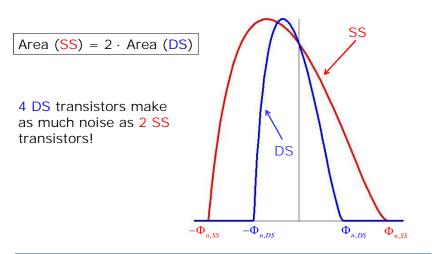

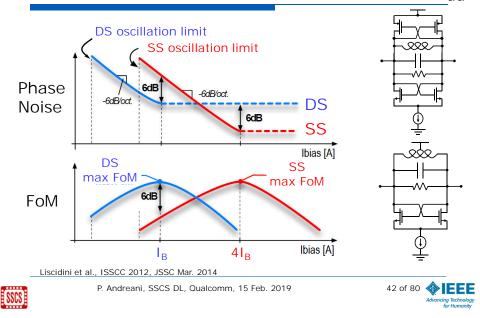

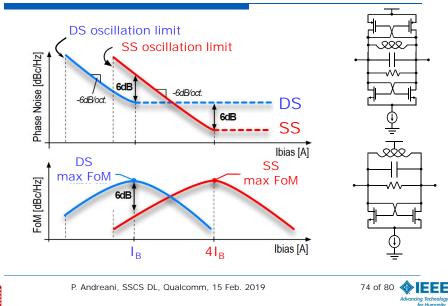

#### An aside – CMOS ring oscillator Double-switch pair vs. single-switch pair Single-switch (SS) Double-switch (DS) pair oscillator [dBc/Hz] -35 @ 1 kHz $A_{DS} = \frac{4}{I_B}R$ $A_{\rm SS} = \frac{2}{-}I_{\rm B}R$ -145 --- spectreRF -o- theory -150 π 222 -155 $V_{\underline{+}}$ $V_{\pm}$ V\_ -160 L 0.2 0.4 0.6 0.8 1.0 1.2 1.4 V, [V] ∽∕∕∕v What phase $\gamma_n + \gamma_p$ noise difference $2k_BT$ $L_{1/f^2}(\Delta\omega) = 10\log_{10}$ should we $V_{thr}$ $I_{DD}V_{DD}$ $\Lambda \omega$ expect? $V_{DD}$ Pepe and Andreani, to appear in TCAS-II (available on ieeexplore) 37 of 80 🚸 EEE P. Andreani, SSCS DL, Qualcomm, 15 Feb. 2019 P. Andreani, SSCS DL, Qualcomm, 15 Feb. 2019 SSCS SSCS

DS pair vs. SS pair – phase noise

$$L_{DS}(\Delta\omega) = 10\log\left(\frac{2k_BTR}{A_{DS}^2/2}\left(\frac{1}{2Q}\frac{\omega_0}{\Delta\omega}\right)^2\left(1+\frac{\gamma_n+\gamma_p}{2}\right)\right)$$

$$L_{SS}(\Delta\omega) = 10\log\left(\frac{2k_BTR}{A_{SS}^2/2}\left(\frac{1}{2Q}\frac{\omega_0}{\Delta\omega}\right)^2\left(1+\gamma_n\right)\right)$$

□ 60% from tank, 40% from transistors If  $\gamma_n = \gamma_p = 2/3$

□ If

$$I_{B,DS} = I_{B,SS}$$

and  $\gamma_n = \gamma_p \rightarrow A_{DS} = 2A_{SS} \rightarrow L_{DS} = L_{SS} - 6dB$  (!)

Andreani and Fard, JSSC Dec. 2006

[SSCS]

# DS vs. SS – MOS noise

38 of 80 🚸 EEE

pair oscillator

$\mathcal{M}$

# SS vs DS – PN and FoM with fixed $V_{dd}$

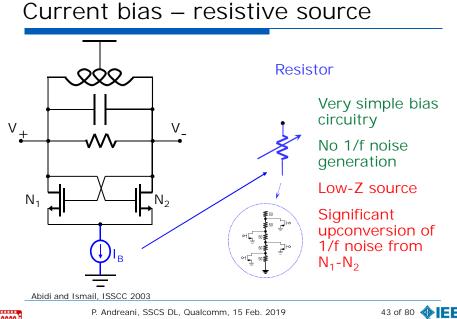

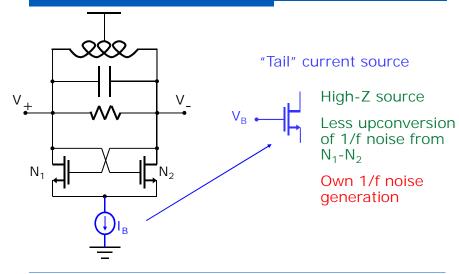

#### Current bias - MOS source

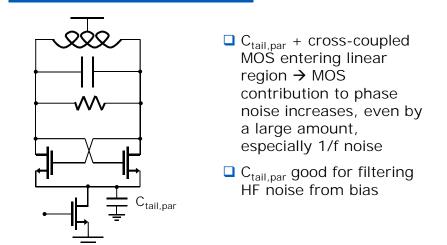

# Impact of parasitic tail capacitance

#### **Overview**

- Popular harmonic oscillators

- Phase noise

- □ Architectures for low 1/f<sup>2</sup> and/or 1/f<sup>3</sup> phase noise

- Series-resonance oscillator

- Design techniques for very wide frequency

P. Andreani, SSCS DL, Qualcomm, 15 Feb. 2019

SSCS

SSCS

P. Andreani, SSCS DL. Qualcomm, 15 Feb, 2019

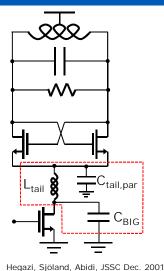

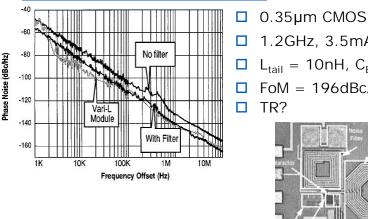

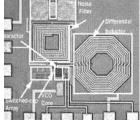

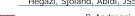

### Possible solution – noise filter

- □ Noise filter:  $C_{tail,par}$  resonates with  $L_{tail}$  at  $2\omega_0 \rightarrow MOS$ switches see high-Z at  $2\omega_0$

- □ C<sub>BIG</sub> filters tail noise and acgrounds L<sub>tail</sub>

- □  $C_{BIG}$  includes  $C_{DB}$  of MOS tail → long and large MOS, low 1/f noise

- Drawbacks: narrow-band. C<sub>tail,par</sub> must be known with some precision, extra L<sub>tail</sub>

### Dramatic performance improvement

# More on tail filter

# A recent variation

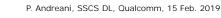

Class- $F_2$  (or, here,  $F_{2,3}$ ) oscillator

1/f<sup>3</sup> pha

a 400

€ 30

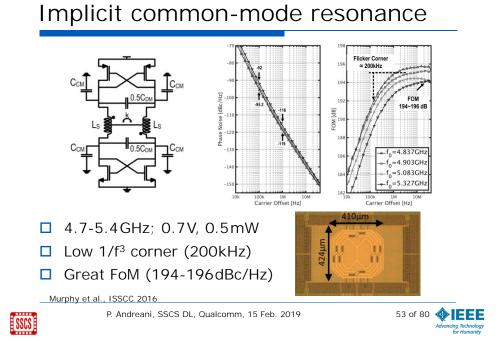

#### Alternative to tail resonance

51 of 80

- $\Box$  Design tank for differential resonance at  $\omega_0$  and common-mode resonance at  $2\omega_0$

- Also here, the  $2\omega_0$  resonance must track the  $\omega_0$ resonance - two capacitor banks

Babaie et al., RFIC 2013, JSSC Mar. 2015; Shahmohammadi et al., ISSCC 2015; Murphy et al., ISSCC 2015

P. Andreani, SSCS DL, Qualcomm, 15 Feb. 2019

SSCS

□ Very low PN (-124dBc/Hz @ 1MHz)

□ 5.4-7.0GHz; 1V, 10-12mW

□ Low 1/f<sup>3</sup> corner (60-130kHz)

□ Very good FoM (~191dBc/Hz)

Shahmohammadi et al., ISSCC 2015

**E**SSCS

25 Frequency (GHz)

Class-F<sub>2</sub>

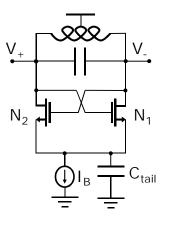

# A totally different approach – class-C

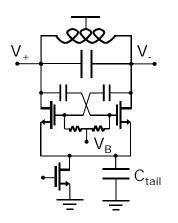

- C<sub>tail</sub> turns class-B into class-C: optimal differential "Colpitts" oscillator

- Ideally, 3.9dB lower phase noise for the same bias current

- □ Also here, C<sub>tail</sub> filters off highfrequency noise from tail, and includes tail C<sub>DB</sub> → long and large MOS, low 1/f noise

#### Mazzanti and Andreani, JSSC Dec. 2008

# Single-ended, 2<sup>nd</sup>-harmonic resonance

### Original prototype

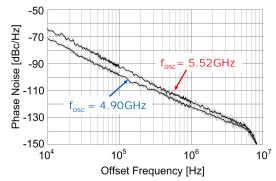

- $\Box \quad 4.90 \text{GHz} < f_c < 5.65 \text{GHz}$

- □ 1V, 1.4mW

SSCS

$\Box$  193.5dBc/Hz < FoM < 196dBc/Hz

#### Design issues in class-C CMOS oscillator

- Diff-pair must avoid linear region (otherwise, large PN boost)  $\rightarrow$  low V<sub>B</sub> for MOS gate bias via feedback loop

- XFMR feedback also possible

- □ Ideally, no 1/f noise upconversion from MOS pair

- Lower maximum oscillation amplitude than in ideal class-B CMOS oscillator

- Very attractive for BJT VCOs

Mazzanti and Andreani, JSSC Dec. 2008; Fanori and Andreani, JSSC July 2013; Bevilacqua and Andreani, TCAS-I May 2012; Bevilacqua and Andreani, unpublished work

SSCS

SSCS

P. Andreani, SSCS DL. Qualcomm, 15 Feb. 2019

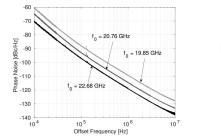

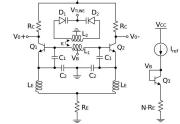

# Colpitts VCO in SiGe BiCMOS process

- □ 18.8-23.1GHz; 4.0V, 17.5mA

- PN = -119 dBc/Hz @ 1MHz (best)п  $\Box$  FoM = 188dBc/Hz

SSCS

58 of 80

Overview

- Popular harmonic oscillators

- Phase noise

- □ Architectures for low 1/f<sup>2</sup> and/or 1/f<sup>3</sup> phase

- Series-resonance oscillator

- Design techniques for very wide frequency

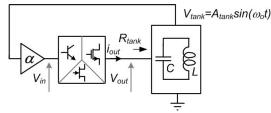

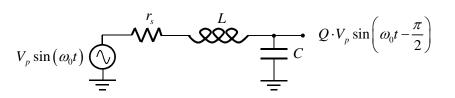

### Oscillation with series resonance

- Voltage driven

- Gain equal to guality factor  $\rightarrow$  internal oscillation may be much higher than  $V_{DD}$

- Attractive for ultra-low phase noise

- $\square$   $\pi/2$  phase shift between input and output

P. Andreani, L. Fanori, and T. Mattsson, "Series-resonance oscillator," U.S. Patent 2015 0381 157, 2015

P. Andreani, SSCS DL. Qualcomm, 15 Feb, 2019

59 of 80

# Phase shift by quadrature

- □ We disregard the (important) issue of start-up

- $\hfill\square$  Square wave between  $V_{DD}$  and GND at LC input

- MOS devices work almost exclusively as switches → channel resistance in series with the tank's

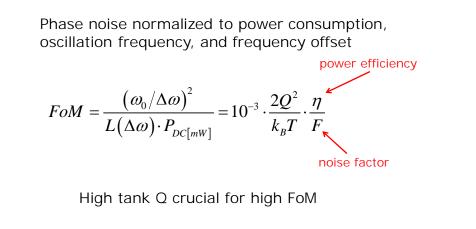

# Figure of merit

Ideally, close to 1

$$FoM = 10^{-3} \cdot \frac{2Q^2}{k_B T} \cdot \frac{\eta^{-1}}{1 + F}$$

Ideally, close to C

- □ Usual dependence on Q<sup>2</sup>

- Very large power consumption, ultra-low phase noise (plus quadrature phases for free)

- □ However, momentous issues:

- MOS resistance is critical (current-based architectures such as class-B and class-C are much more robust)

- Stray resistances of GND and power supply distribution are also critical

- Very large internal voltages make frequency tuning difficult

#### Phase noise

$$L(\Delta\omega) = 10\log_{10}\left[\frac{4k_{B}Tr_{s}}{\left(4I_{pk}L\Delta\omega\right)^{2}}\left(1+F\right)\right] = 10\log_{10}\left[\frac{4k_{B}T}{\left(4I_{pk}\Delta\omega\right)^{2}r_{s}}\left(\frac{1}{Q}\frac{\omega_{0}}{\Delta\omega}\right)^{2}\left(1+F\right)\right]$$

$$I_{pk} = \frac{2}{\pi}\frac{V_{DD}}{r_{s}}$$

- MOS work as switches → previous phase noise theorems do not apply

- F accounts for 1) MOS are non-ideal switches, and

2) they do work as transconductors for a (tiny) fraction of the oscillation period

- □ Ideally, F is negligible!

Pepe, Bevilacqua, Andreani, TCAS-I Feb. 2018

P. Andreani, SSCS DL, Qualcomm, 15 Feb. 2019 62 c

# Overview

- Popular harmonic oscillators

- Phase noise

- □ Architectures for low 1/f<sup>2</sup> and/or 1/f<sup>3</sup> phase noise

- Series-resonance oscillator

- Design techniques for very wide frequency tuning range RF CMOS VCOs

# VCOs in modern radios – I

- □ Carrier aggregation requires several harmonic VCOs

- Active at the same time

- Should not pull one another

- □ Band proliferation favors VCOs with a very wide tuning range (TR)

- Wider than 1 octave is particularly attractive

# VCOs in modern radios – II

- VCO with 8-shaped tank inductor

- Much less sensitive to external magnetic fields

- Generates itself a vanishing magnetic field

- Slightly lower Q acceptable

- Often used

M. Nilsson et al., ISSCC 2011

SSCS

P. Andreani, SSCS DL, Qualcomm, 15 Feb. 2019

66 of 80

P. Andreani, SSCS DL, Qualcomm, 15 Feb. 2019

- □ Two or more VCOs with overlapping TRs

- Saves power, costs area

- Very popular choice in real-life products

Hadiichristos et al., ISSCC 2009

65 of 80

# Very-Wide-TR VCOs – II

- □ Large switchable C in parallel to small L

- floating switches

- power wasted at low frequencies, compared to reasonable phase-noise specs

- power cannot be decreased without killing the oscillation

# Very-Wide-TR VCOs – III

#### Switchable I

- Ultra-wide TR possible

- Difficult to obtain low PN at high FoM

- Additional issue: switchable 8-shaped inductor

Sadhu et al., CICC 2009

SSCS

SSCS

P. Andreani, SSCS DL, Qualcomm, 15 Feb. 2019

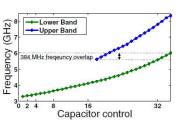

# Very-Wide-TR VCOs – IV

- Transformer-based VCOs

- Two resonances with overlapping TRs

- TR > 1 octave

- Difficult to design an 8-shaped transformer

#### Bevilacqua et al., TCAS-II Apr. 2007; Li et al., JSSC June 2012

P. Andreani, SSCS DL, Qualcomm, 15 Feb. 2019

70 of 80 🚸 EEE

Transforme

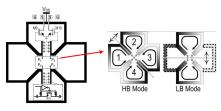

#### Mode-switching VCO

- 4 inductors, two oscillation modes

- Rejects external magnetic fields

- TR > 1 octave

- Excellent PN and FoM

- Large area

Taghivand et al., ISSCC 2014

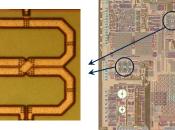

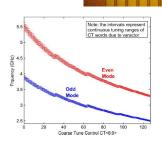

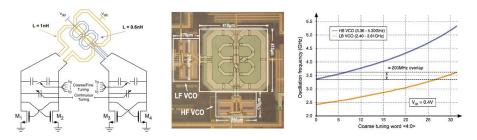

# Very-Wide-TR VCOs – VI

- Double-core VCO

- Two concentric 8-shaped coils do not interfere (much) with each other

- TR > 1 octave; saves inductor area, sub-optimal Q

#### Fanori et al., ISSCC 2014

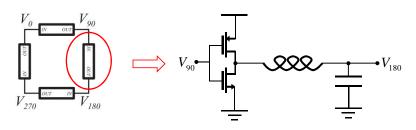

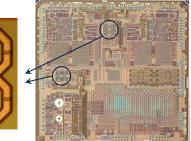

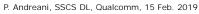

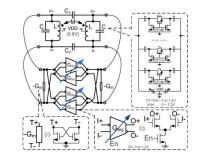

# Very-Wide-TR VCOs – VII

- Reconfigurable active core

- Standard LC tank design (i.e., with very large capacitance)

- Negative resistance: either single-switch (nMOS) pair -SS mode

- or, double (complementary nMOS-pMOS) switch pair DS mode

- DS mode avoids power waste at lower frequencies

# SS pair vs. DS pair, again

Liscidini et al., ISSCC 2012, JSSC Mar. 2014

SSCS

P. Andreani, SSCS DL. Qualcomm, 15 Feb, 2019

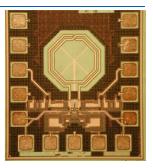

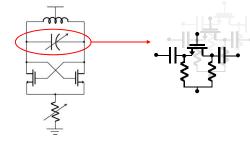

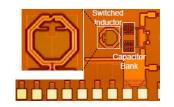

#### Very-Wide-TR reconfigurable VCO R<sub>bias,CP</sub> ∦ DS M3 $\mathsf{R}_{\mathsf{bias},\mathsf{SP}}$ V<sub>rtd</sub> = 0.9V, f<sub>0</sub> = 5.8GHz, FoM 186/189dBc/ requency Offset (MH:

- STM 28nm UTBB FD-SOI CMOS 2.8-5.8 GHz

- □ -154 < PN (dBc/Hz @ 20MHz) < -142

- 186 < FoM (dBc/Hz) < 189

- $300 \text{ kHz} < 1/\text{f}^3 \text{ corner} < 3 \text{ MHz}$

Fanori et al., RFIC 2015

# Conclusions

SSCS

SSCS

- Rigorous phase noise results For transconductor-based oscillators  $\Box$  Class-B VCOs  $\rightarrow$  simple, robust, ubiquitous Tail filter improves phase noise, even largely Recent proposals: common-mode tank resonance at  $2\omega_{0}$

- $\Box$  Class-C  $\rightarrow$  higher efficiency than standard class-B, possibly low 1/f<sup>3</sup> phase noise, but more complicated

- Class-C must be enforced for all working conditions

- Excellent for BJT VCOs

- $\Box$  Series-resonance oscillator  $\rightarrow$  great potential, but important issues to be solved

- Several techniques for very wide tuning range

- None a clear winner

Frequency

Tunina

# References – I

- 1. A. Hajimiri and T. H. Lee, A general theory of phase noise in electrical oscillators," IEEE J. Solid-State Circuits, vol. 33, no. 2, pp. 179-194, Feb. 1998

- 2. P. Andreani and X. Wang, "On the Phase-Noise and Phase-Error Performances of Multiphase LC CMOS VCOs," IEEE J. Solid-State Circuits, vol. 39, no. 11, pp. 1883-1893, Nov. 2004.

- 3. P. Andreani et al., "A study of phase noise in Colpitts and LC-tank CMOS oscillators," IEEE J. Solid-State Circuits, vol. 40, no. 5, pp. 1107-1118, May 2005.

- 4. A. Mazzanti and P. Andreani, "Class-C harmonic CMOS VCOs, with a general result on phase noise," IEEE J. Solid-State Circuits, vol. 43, no. 12, pp. 2716-2729, Dec. 2008.

- 5. J. Bank, "A harmonic oscillator design methodology based on describing functions", PhD thesis, Gothenburg, Sweden, 2006.

- D. Murphy et al., "Phase noise in LC oscillators: "A phasor-based analysis of a general result and of 6. loaded", IEEE Trans. Circuits Syst. I, vol. 57, no. 6, pp. 1187-1203, Jun. 2010.

- F. Pepe and P. Andreani, "Still More on the 1/f<sup>2</sup> Phase Noise Performance of Harmonic Oscillators," 7. IEEE Trans. Circuits Syst. - II, vol. 63, no. 6, pp. 538-542, June 2016

- 8. F. Pepe and P. Andreani, "A General Theory of Phase Noise in Transconductor-Based Harmonic Oscillators," IEEE Trans. Circuits Syst. - I, vol. 64, no. 2, pp. 432-445, Feb. 2017.

- 9. M. Garampazzi et al., "An Intuitive Analysis of Phase Noise Fundamental Limits Suitable for Benchmarking LC Oscillators", IEEE J. Solid-State Circuits, vol. 49, no. 3, pp. 635-645, Mar. 2014.

- 10. F. Pepe and P. Andreani, "An Accurate Analysis of Phase Noise in CMOS Ring Oscillators", IEEE Trans. Circuits Syst. - II (early access on ieeexplore).

- 11. P. Andreani and A. Fard, "More on the 1/f<sup>2</sup> phase noise performance of CMOS differential-pair LCtank oscillators," IEEE J. Solid-State Circuits, vol. 41, no. 12, pp. 2703–2712, Dec. 2006.

- 12. M. Garampazzi et al., "Analysis and Design of a 195.6 dBc/Hz Peak FoM P-N Class-B Oscillator With Transformer-Based Tail Filtering", IEEE J. Solid-State Circuits, vol. 50, no. 7, pp. 1657–1668, Jul. 2015

P. Andreani, SSCS DL. Qualcomm, 15 Feb, 2019

#### References – II

- 13. D. Murphy et al., "A VCO with Implicit Common-Mode Resonance", in Proc. of the IEEE ISSCC 2015, pp. 442-443, 2015.

- 14. A. Liscidini et al., "A 36mW/9mW Power-Scalable DCO in 55nm CMOS for GSM/WCDMA Frequency Synthesizers," in Proc. of the IEEE ISSCC 2012, pp. 348-350, 2012.

- 15. A. Liscidini et al., "A 36mW/9mW Power-Scalable DCO in 55nm CMOS for GSM/WCDMA Frequency Synthesizers," IEEE J. Solid-State Circuits, vol. 49, no. 3, pp. 646-656, Mar. 2014.

- 16. A. Ismail and A. Abidi, "CMOS differential LC oscillator with suppressed up-converted flicker noise," in Proc. of the IEEE ISSCC 2003, pp. 98-99, 2003.

- 17. E. Hegazi et al., "A filtering technique to lower LC oscillator phase noise," IEEE J. Solid-State Circuits, vol. 36, no. 12, pp. 1921-1930, Dec. 2001.

- 18. M. Babaie et al., "Ultra-low phase noise 7.2-8.7 GHz clip-and-restore oscillator with 191dBc/Hz FoM," in Proc. of the IEEE RFIC 2013, pp. 43-46, 2013.

- 19. M. Babaie and R. B. Staszewski, "An Ultra-Low Phase Noise Class-F<sub>2</sub> CMOS Oscillator With 191 dBc/Hz FoM and Long-Term Reliability," IEEE J. Solid-State Circuits, vol. 50, no. 3, pp. 679-692, Mar 2015

- 20. M. Shahmohammadi et al., "A 1/f Noise Upconversion Reduction Technique Applied to Class-D and Class-F Oscillators", in Proc. of the IEEE ISSCC 2015, pp. 444-445, 2015.

- 21. D. Murphy et al., "A Complementary VCO for IoE that Achieves a 195dBc/Hz FOM and Flicker Noise Corner of 200kHz", in Proc. of the IEEE ISSCC 2016, pp. 44-45, 2016.

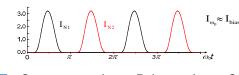

- 22. C.-C. Lim et al., "An Inverse-Class-F CMOS Oscillator With Intrinsic-High-Q First Harmonic and Second Harmonic Resonances", IEEE J. Solid-State Circuits, vol. 53, no. 12, pp. 3528-3539, Dec. 2018.

- 23. A. Mazzanti and P. Andreani, "Class-C harmonic CMOS VCOs, with a general result on phase noise," IEEE J. Solid-State Circuits, vol. 43, no. 12, pp. 2716-2729, Dec. 2008.

P. Andreani, SSCS DL. Qualcomm, 15 Feb, 2019

78 of 80

#### References – IV

- 36. M. Taghivand et al., "A 3.24-to-8.45GHz Low-Phase-Noise Mode-Switching Oscillator", in Proc. of the IEEE ISSCC 2014, pp. 368-370, 2014.

- 37. L. Fanori et al., "A 2.4-to-5.3GHz Dual-Core CMOS VCO with Concentric 8-Shaped Coils", in Proc. of the IEEE ISSCC 2014, pp. 379-372, 2014.

- 38. L. Fanori et al., "A 2.8-to-5.8 GHz Harmonic VCO in a 28 nm UTBB FD-SOI CMOS Process", in Proc. of the IEEE RFIC 2015, pp. 195-198, 2015.

SSCS

- 24. A. Bevilacqua and P. Andreani, "An Analysis of Noise to Phase Noise Conversion in CMOS Harmonic Oscillators," IEEE Trans. Circuits Syst. - I, vol. 59, no. 5, pp. 938-945, May 2012.

- 25. L. Fanori and P. Andreani, "Highly Efficient Class-C CMOS VCOs, Including a Comparison With Class-B VCOs", IEEE J. Solid-State Circuits, vol. 48, no. 7, pp. 1730-1740, July 2013.

- 26. F. Boscolo et al., "A 21GHz 20.5%-Tuning Range Colpitts VCO with -119dBc/Hz Phase Noise at 1MHz Offest", in Proc. of the IEEE ESSCIRC 2017, pp. 91-94, 2017

- 27. P. Andreani, L. Fanori, and T. Mattsson, "Series-resonance oscillator," U.S. Patent 2015 0381 157, Dec. 31, 2015. http://www.freepatentsonline.com/y2015/0381157.html

- 28. M. Tohidian et al., "A tiny quadrature oscillator using low-Q series LC tanks," IEEE Microw. Wireless Compon. Lett., vol. 25, no. 8, pp. 520-522, Aug. 2015.

- 29. F. Pepe, A. Bevilacqua, and P. Andreani, "On the Remarkable Performance of the Series-Resonance CMOS Oscillator," IEEE Trans. Circuits Syst. - I, vol. 65, no. 2, pp. 531-542, Feb. 2018.

- 30. M. Nilsson et al., "A 9-band WCDMA/EDGE transceiver supporting HSPA evolution," in Proc. of the IEEE ISSCC 2011, pp. 366-368, 2011.

- 31. A. Hadjichristos et al., "Single-chip RF CMOS UMTS/EGSM transceiver with integrated receive diversity and GPS", in Proc. of the IEEE ISSCC 2009, pp. 118-119, 2009

- 32. H. Sjöland, "Improved Switched Tuning of Differential CMOS VCOs," IEEE Trans. Circuits Syst. -II, vol. 49, no. 5, pp. 352-355, May 2002.

- 33. B. Sadhu et al., "A CMOS 3.3-8.4 GHz Wide Tuning Range, Low Phase Noise LC VCO", in Proc. of the IEEE CICC 2009, pp. 559-562, 2009.

- 34. A. Bevilacqua et al., "Transformer-based dual-mode voltage-controlled oscillators," IEEE Trans. Circuits Syst. - II, vol. 54, no. 4, pp. 293-297, Apr. 2007.

- 35. G. Li et al., "A Low-Phase-Noise Wide-Tuning-Range Oscillator Based on Resonant Mode Switching IEEE J. Solid-State Circuits, vol. 47, no. 6, pp. 1295-1308, June 2012.