### Fundamentals of EMI Chris Herrick Ansoft Applications Engineer

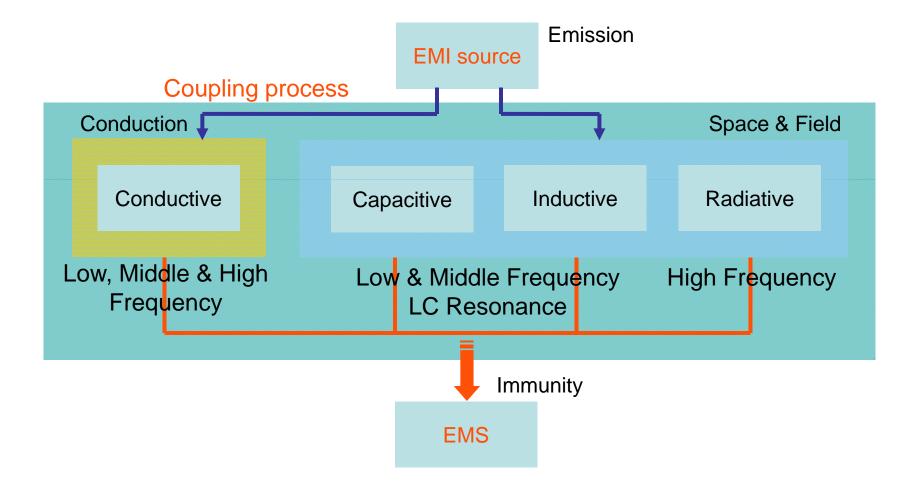

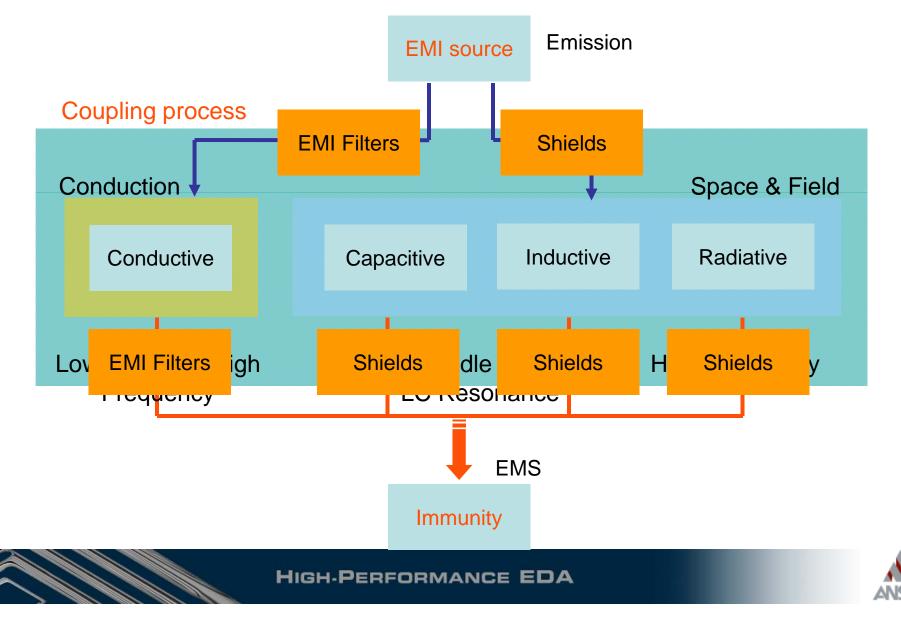

### **Three Basic Elements of EMC**

### **Controlling EMI**

# **PCB Noise Sources**

### Intentional Signals

Emissions from intentional signals include loop-mode and common-mode sources.

### • Unintentional Signals (more than 90% of EMI)

Emissions from unintentional signals include common-mode, crosstalk coupling to I/O traces (both PCB and IC level), power planes, and above board structures.

> \*Reference from "*PCB Design for Real-World EMI Control,*" Bruce Archambeault

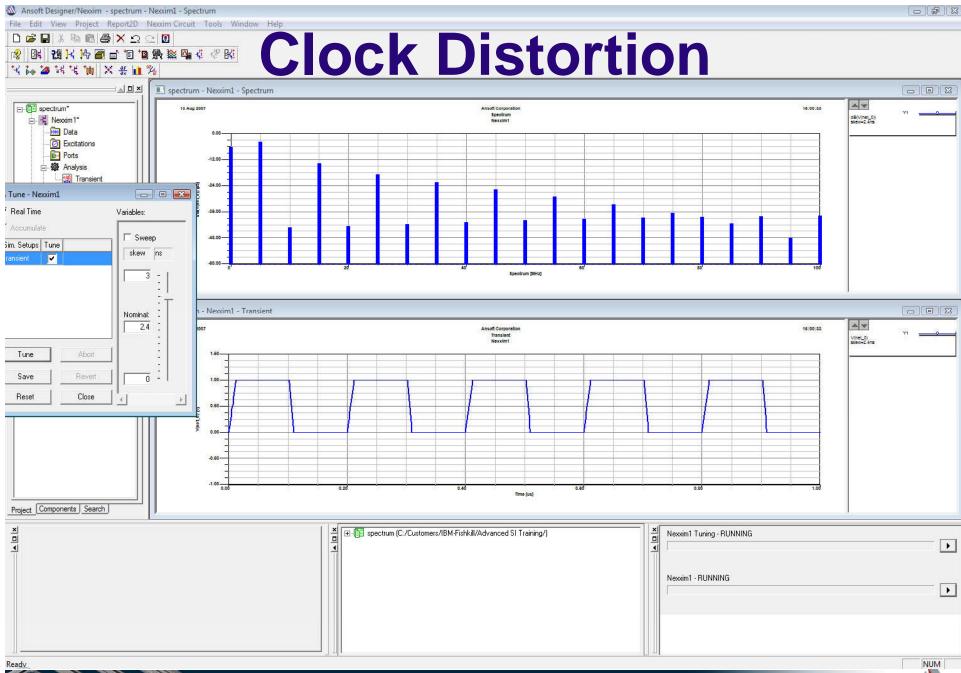

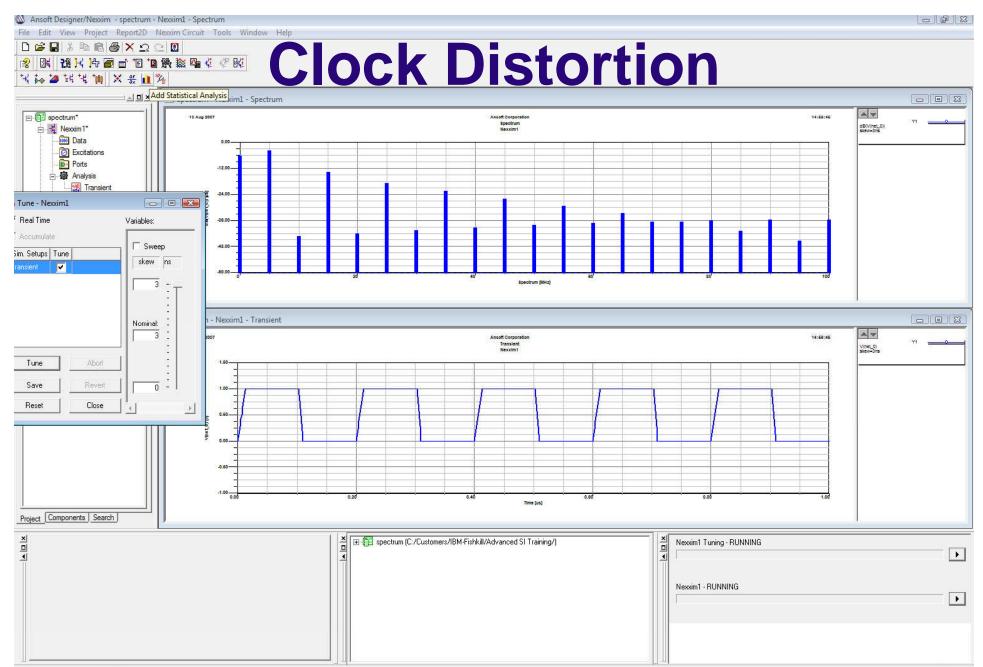

# **Intentional Signals**

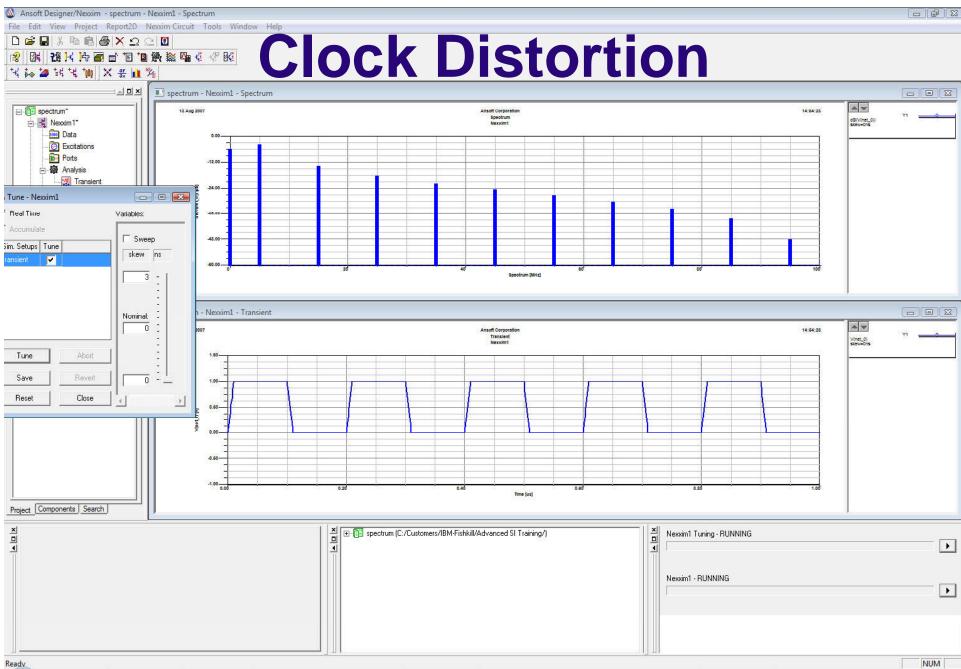

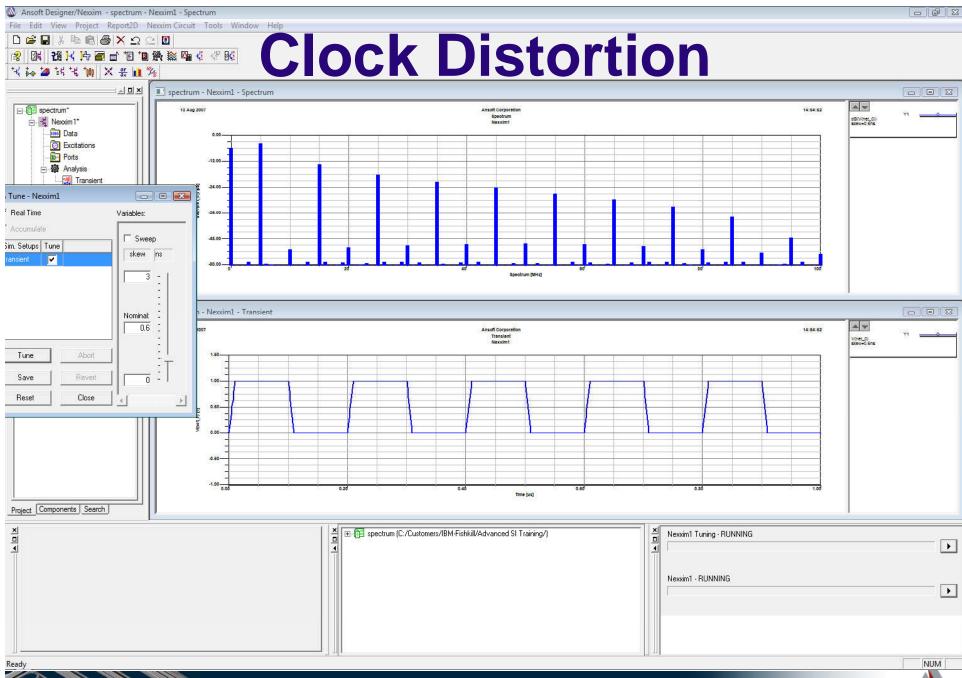

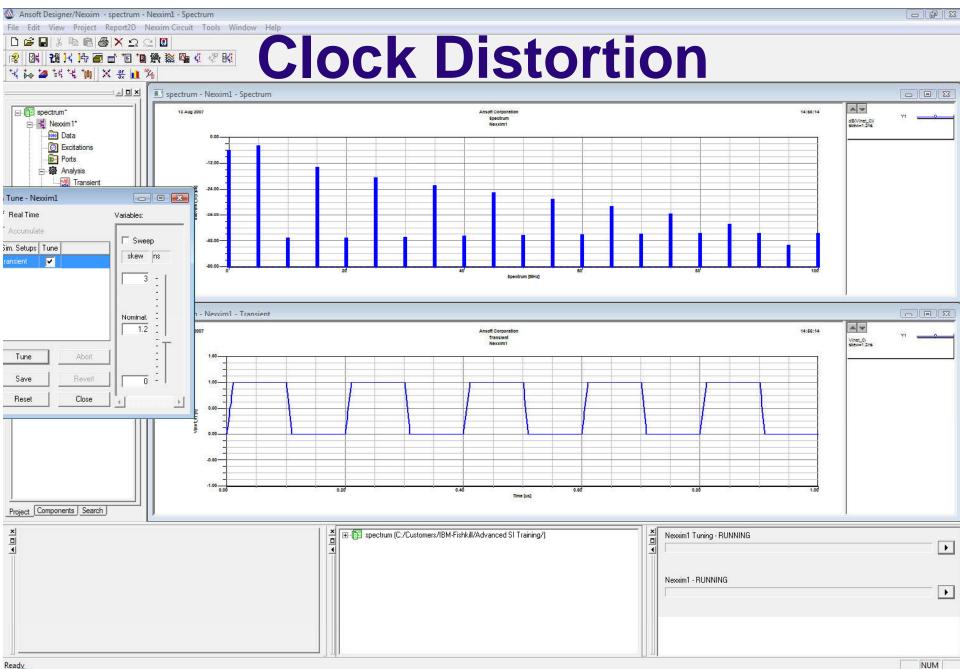

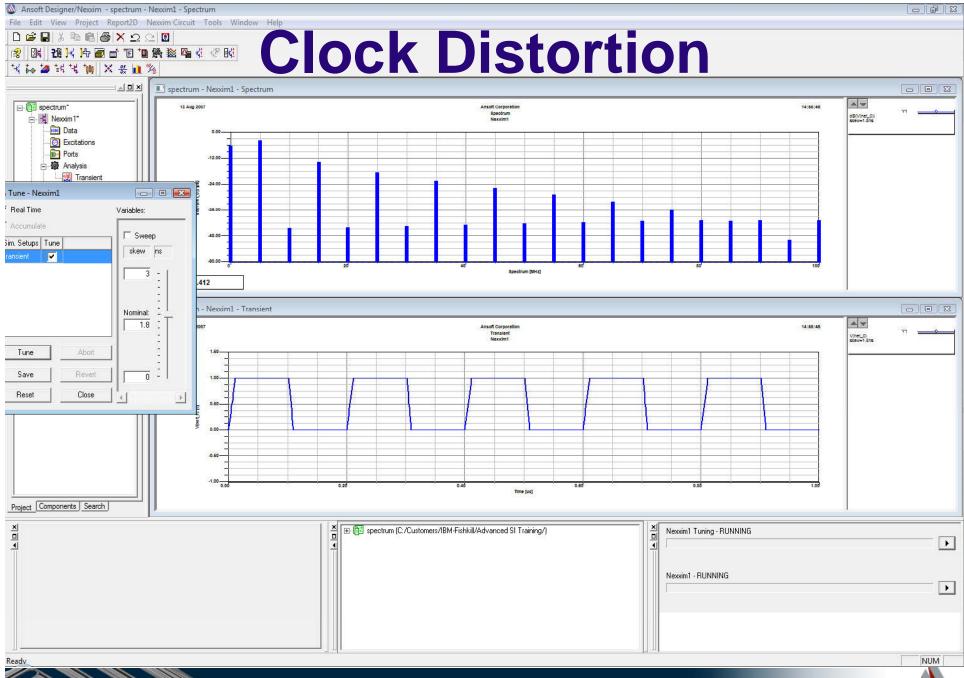

- Focus on Clock and High Speed Signals

- Stripline not necessarily better than Microstrip

- Examine Clock Harmonics

Common Mode Conversion SCD11=0.5\*(S11-S13+S31-S33) SCD21=0.5\*(S21-S23+S41-S43)

# **Unintentional Signals**

- Crosstalk is a big concern

- Beware the low speed nets; use post-layout analysis to scan for unintended coupling

- Coupling may be direct, through intermediate metal or even from plane cavities

- Common mode will always exist

- Don't neglect the overall plane impedance

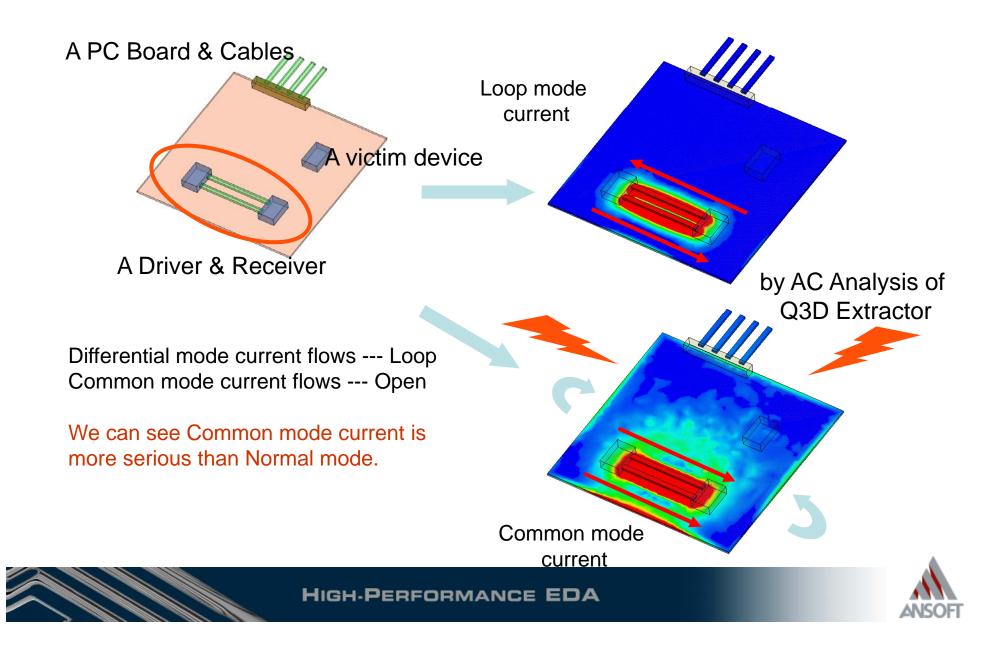

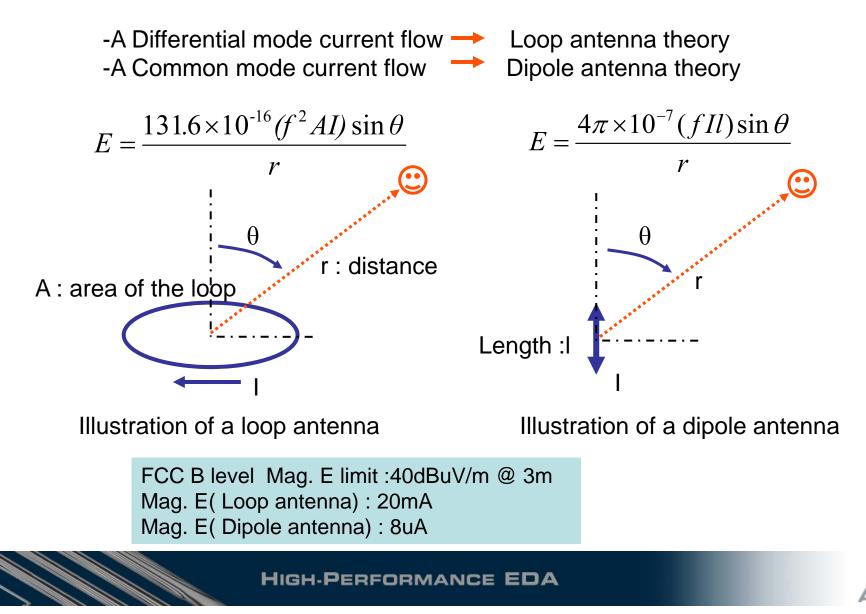

### Loop Mode & Common Mode Noise

#### **Antenna theory**

# **EMC Design Flow**

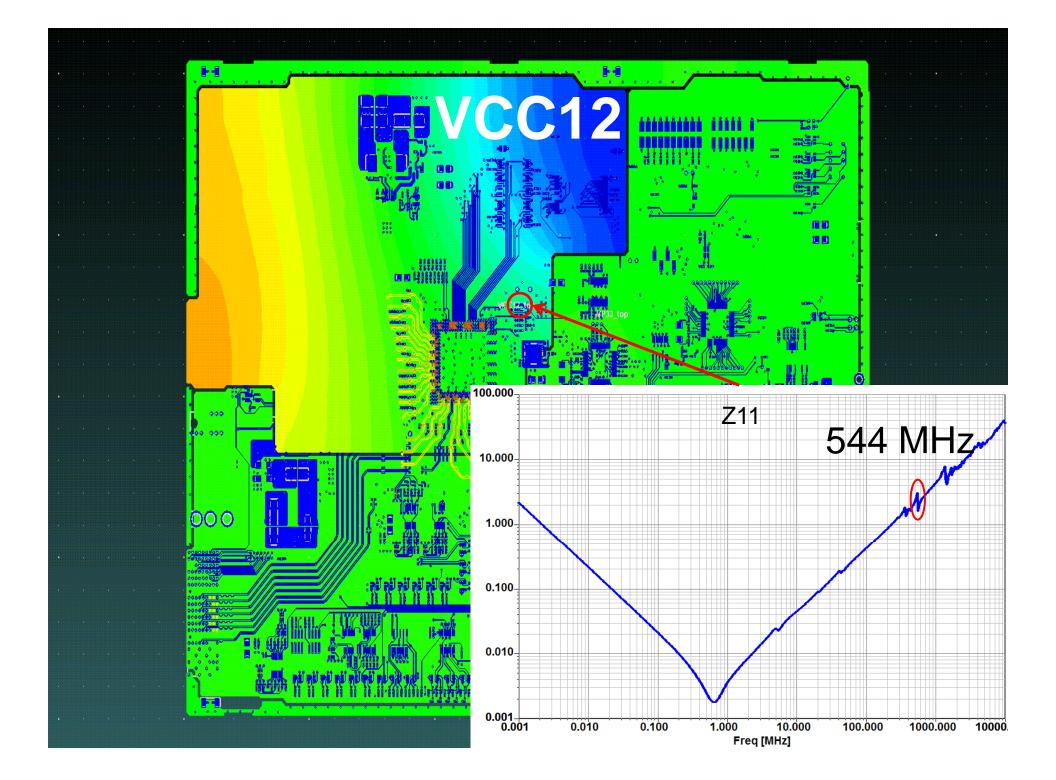

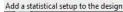

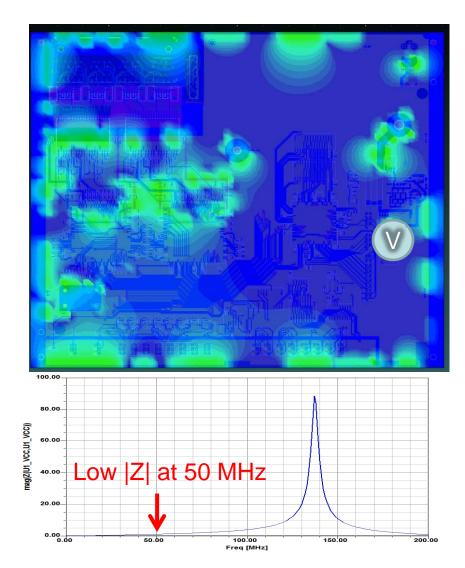

#### **Impedance Analysis**

**Resonance Analysis**

**Signal Extraction**

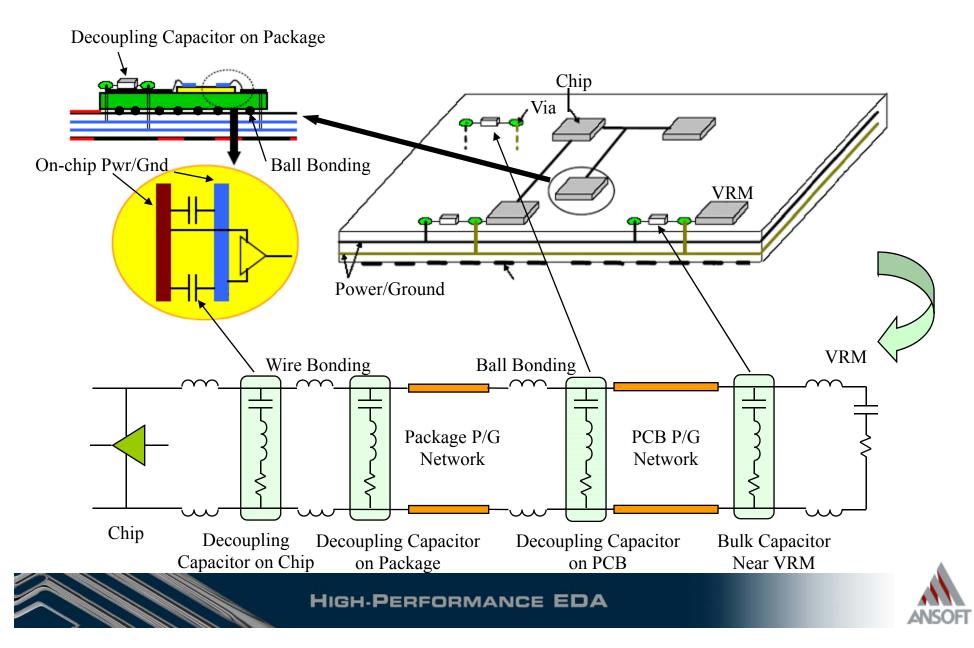

Ensure a low impedance as seen by active parts

Change stackup, plane cutouts and decoupling as necessary

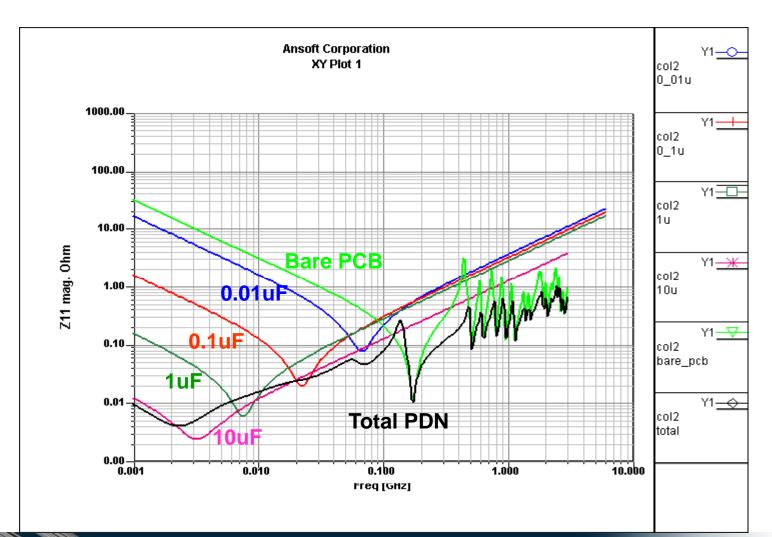

# **Decoupling Capacitor**

### **Decoupling Impedance of PDN**

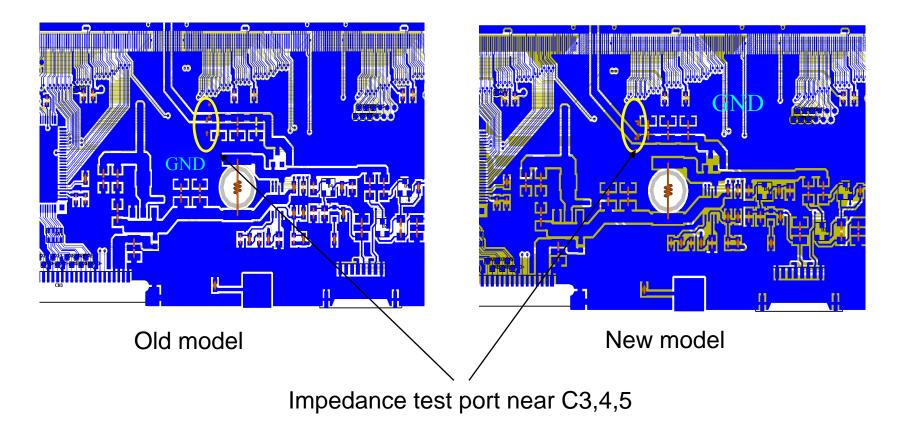

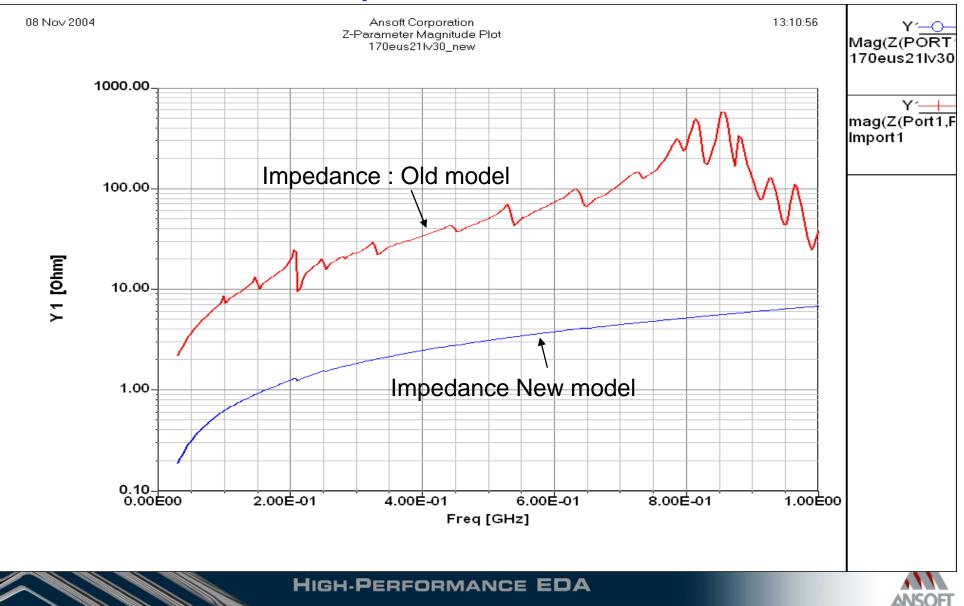

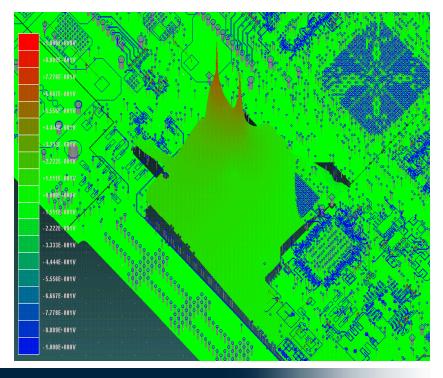

### Plasma Screen Example

Changed Return Path •Widened section of GND plane •Added decoupling Capacitors

### Impedance Plot

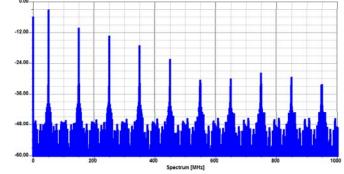

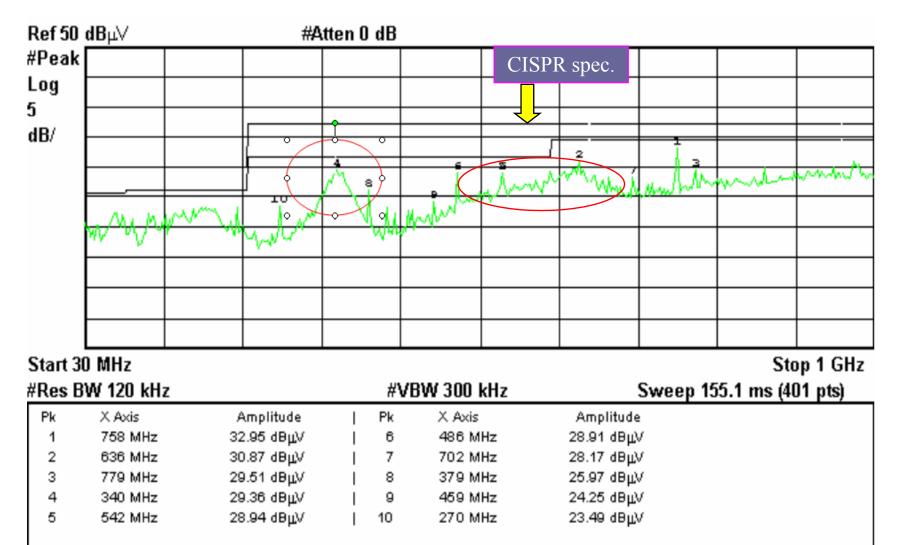

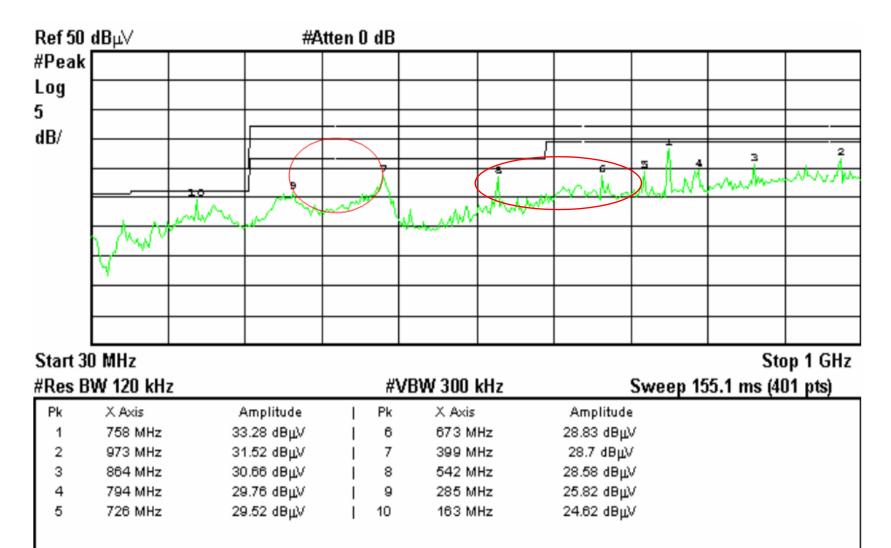

### EMI Test Results : Old model

ANSOFT

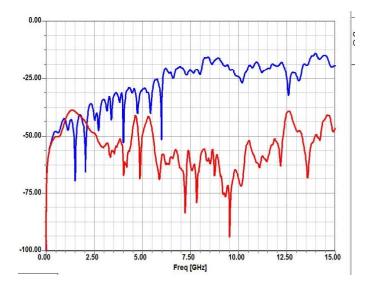

### EMI Test Results : New model

# **EMC Design Flow**

Impedance Analysis

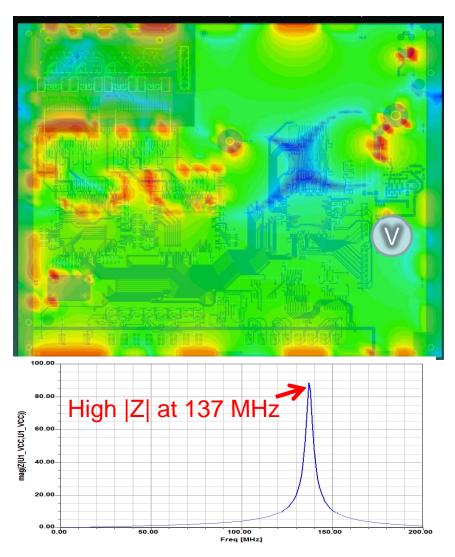

**Resonance Analysis**

**Signal Extraction**

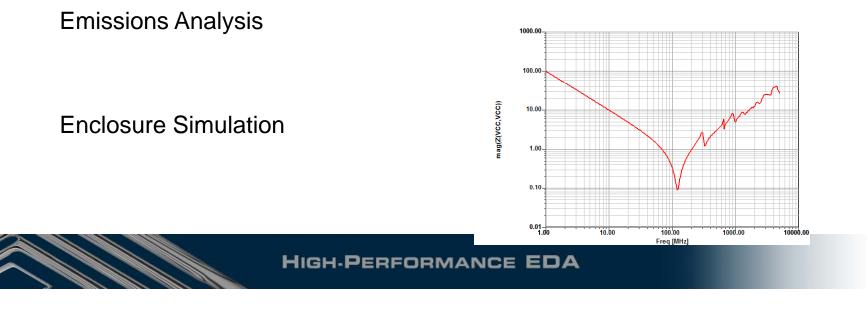

**Emissions Analysis**

**Enclosure Simulation**

Ensure power planes do not resonant in critical locations

Change stackup, plane cutouts and decoupling as necessary

# **Managing Resonances**

Even though resonances ALWAYS exist, you don't need to excite them:

- Keep them away from Clock harmonics

- Examine Via Transitions

- Avoid routing near splits

- Move discrete parts

# **EMC Design Flow**

Impedance Analysis

**Resonance Analysis**

**Signal Extraction**

**Emissions Analysis**

**Enclosure Simulation**

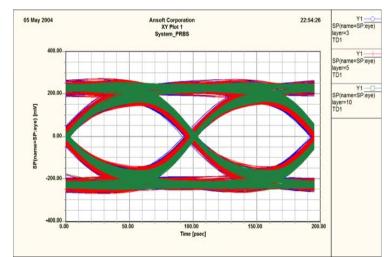

Ensure signals meet required bandwidth

Change routing as necessary

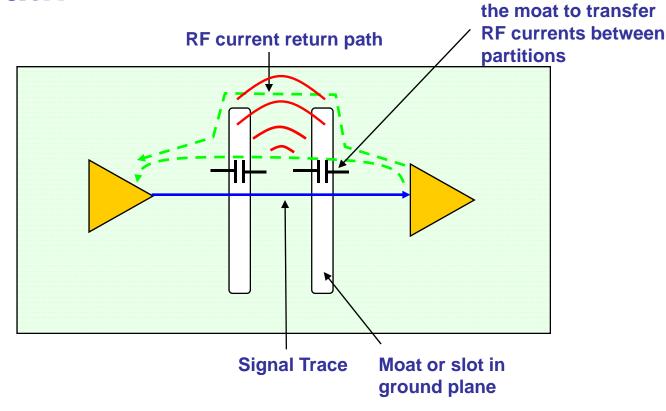

# **Image Plane Violations**

### Always Consider Return Current Path Capacitor bridging

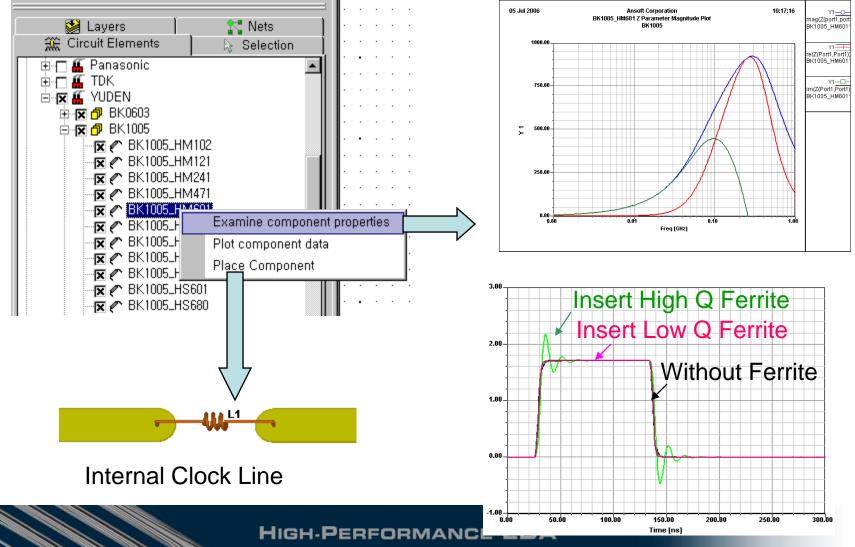

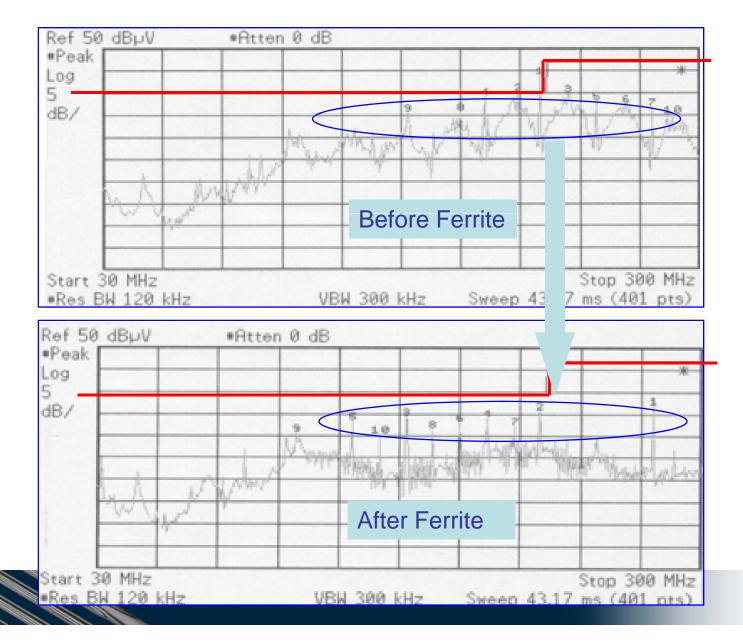

## **EMI Reduction using Ferrites**

### **EMI Test Results**

Ready

## **EMC Design Flow**

**Emissions Analysis**

Ensure EMI is at acceptable level

Optimize previous three simulations

**Enclosure Simulation**

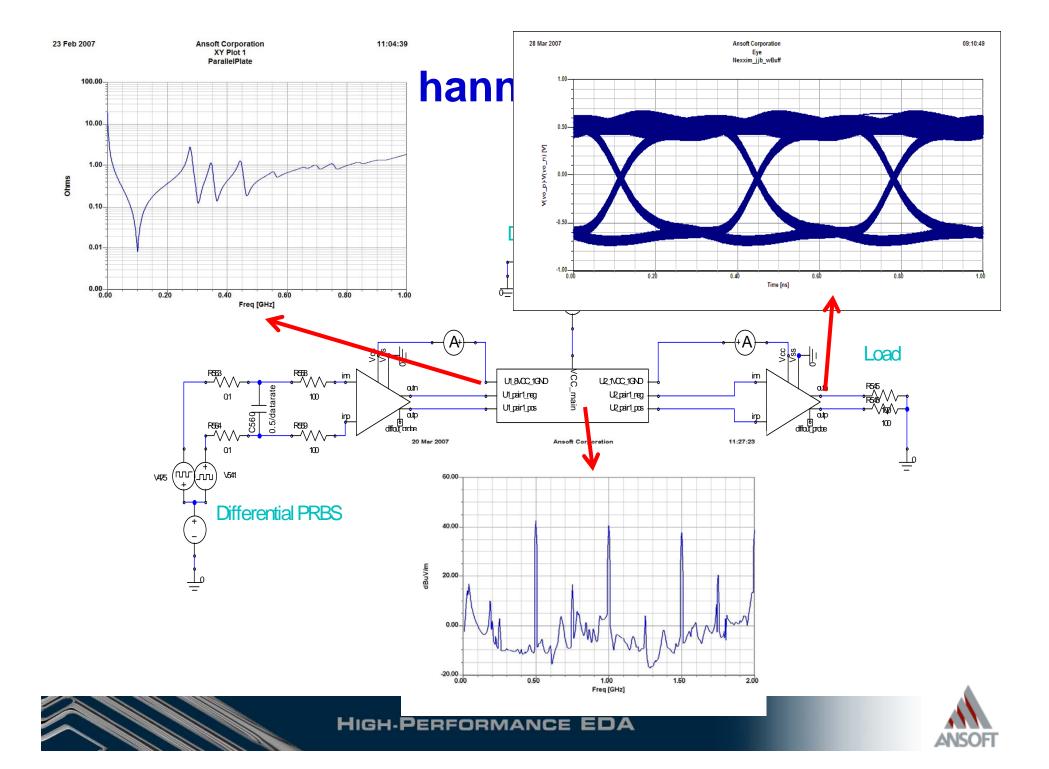

### **Real Drivers as Noise Source**

### **Near-Fields**

# **EMC Design Flow**

Impedance Analysis

**Resonance Analysis**

**Signal Extraction**

**Emissions Analysis**

**Enclosure Simulation**

Test performance of different enclosures

Iterate design as necessary

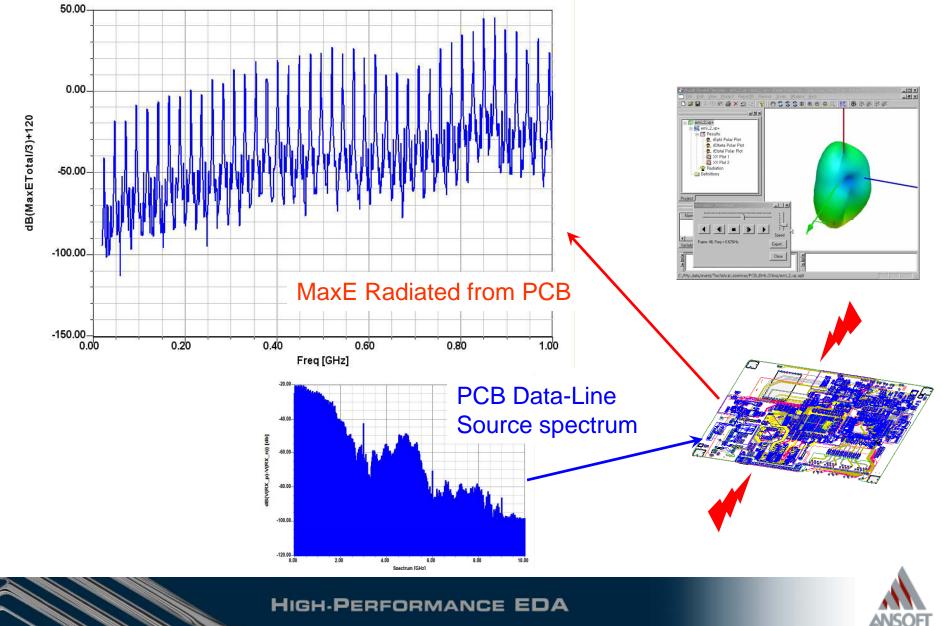

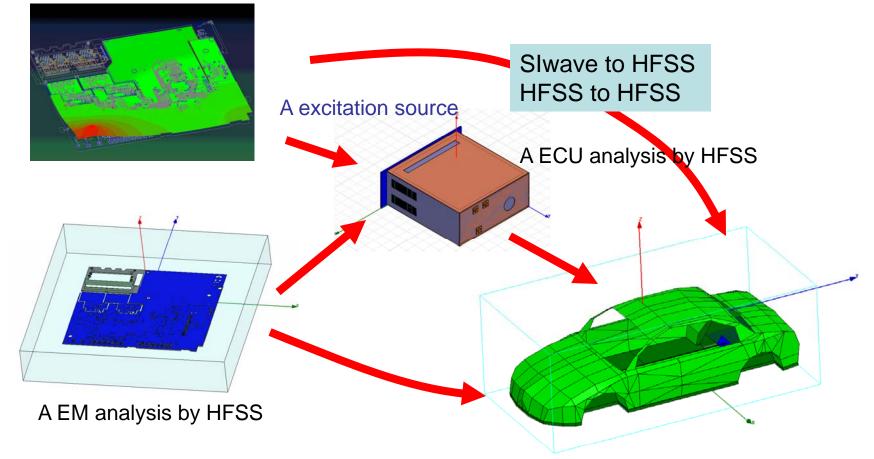

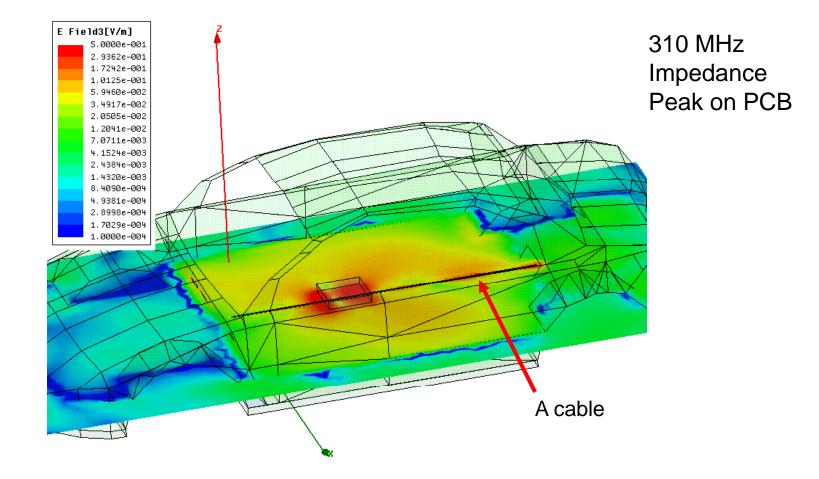

### Linking EMI Source with Shield

A noise analysis by Slwave

#### A noise source and a cable

### Conclusions

- It's easiest to control EMI at it's source

- Prevents Emission and Self Interference

- EMC is comprised of good PI and SI

- Simulating throughout the design cycle can help you avoid trouble in the chamber