## IEEE SCV-EMC 2019 Mini-Symposium October 3, 2019

Brought to you by:

#### **WELCOME!**

Thank you for attending this special one-day Mini-Symposium and exhibition brought to you by the Santa Clara Valley chapter of the IEEE Electromagnetic Compatibility Society.

We hope you enjoy our special guest speakers: Dr. James Drewniak, Doug Smith, Mark Montrose, Sandeep Chandra, Alpesh Bhode and Phillippe Sochoux.

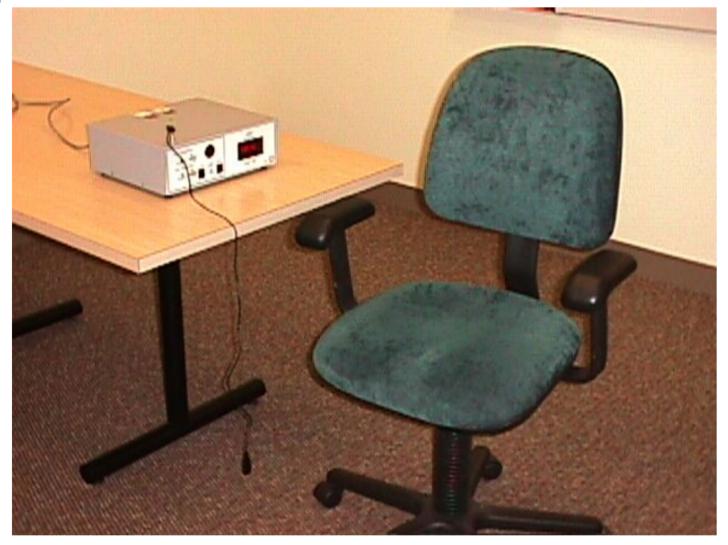

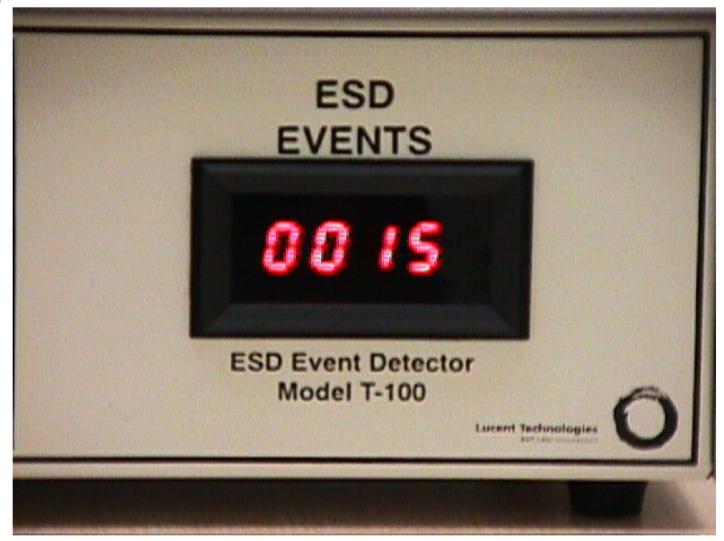

Dr. Drweniak's presentation will focus on 1) concepts and physics; 2) pre-layout method and calculations; and, 3) measurement method. In the past year, we have developed a physics-based approach that makes understanding PI straightforward, and a means for doing calculations for pre-layout design. Doug S. will have a hands-on demo on how to find the source of the ESD; Mark M. will focus on examining Maxwell's equations in a visual manner; Sandeep C. will bring us to Findings on Radiated Susceptibility ABT (Audio Breakthrough), Alpesh B. and Philippe S. will teach us about New Set of EMC Challenges in Telecommunication Equipment.

The goal of this regional event is to bring technical education to IEEE members, who do not have the opportunity to attend the annual international symposium on EMC or did not have a chance to attend the pertinent sessions during the symposium.

Quite often, travel costs and time away from the office prohibit engineers from attending these large, week long, conferences. Our hope is that you will learn practical information that you can bring back to your work place. This is also an excellent opportunity to ask ono-on-one questions directly to the speakers. There will be vendor exhibits throughout the day, so please visit the vendor booths to find out what solutions they have to offer. The exhibitors will often provide trainings on site or on their campus. Special **THANK YOU's** to those who made this event a big success, including all the vendors, companies, individuals, all volunteers and officers.

There will be vendor exhibits throughout the day so please visit vendor booths to find out what EMC solutions they have to offer. The exhibitors will often provide trainings on site or on their campus.

Special **THANK YOU's** to those who made this event a big success, including all the vendors, companies, individuals, all volunteers and officers.

Please, plan on staying for the reception with our guest speakers, and discussing specific items with Jim D., Doug S., Mark M., Sandeep C., Alpesh B. and Philippe S. after each of the technical presentations. There will be appetizers, wine and beer served during Reception hours and several raffles throughout the day. Enjoy the Mini-Symposium and Exhibition!

## Please visit us at <a href="http://ewh.ieee.org/r6/scv/emc/index.html">http://ewh.ieee.org/r6/scv/emc/index.html</a> (or scvemc.org)

Monthly meetings on the 2nd Tuesday except June/July and August. Free admission. Locations change, check website for more details.

#### **Schedule of Events**

Registration, Breakfast & Exhibits: 7:30 AM

Morning Session: 8:30 AM - 12:00 PM

Breaks & Exhibits in the Exhibit Hall + RAFFLE\*: 10:00 AM-10:30 AM

Lunch & Exhibits: 12:00 PM - 1:30 PM

Afternoon Session: 1:30 PM - 5:00 PM

Breaks & Exhibits in the Exhibit Hall + RAFFLE\*: 3:00 PM-3:30 PM

## • Reception & Exhibits in the Exhibit Hall + RAFFLE\*: 5:00 PM - 6:00 PM

\*RAFFLE: Each attendee is entered in the raffle. To earn additional tickets, fill out the Bingo Card, answer the questions and have the Vendors sign it. For each 3 vendors, you earn an extra ticket to be redeemed from any of the staff members. The more answers you get, the more winning chances you get.

## THANK YOU TO THE FOLLOWING COMPANIES FOR SUPPORTING THE IEEE SANTA CLARA VALLEY EMC CHAPTER

2019 Mini-Symposium and Exhibition

Please visit the sponsor companies' websites

#### PLATINUM - RECEPTION SPONSORS

The Knowledge. The Equipment. The Solution.

Quest for Precision

#### GOLD - LUNCH SPONSORS

rf/microwave instrumentation

### SILVER – SPONSORS

| Company                              | Description                                                                                                                                                                 | Name                                                 | Address                  | City       | State | Zip   | Phone               | E-mail                      |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------|------------|-------|-------|---------------------|-----------------------------|

| Avalon Test<br>Equipment             | Offers a complete range of electronic test and measurement equipment for immediate sales or to rent. Shop new and used test equiment, Calibration                           | Jim Burnham                                          | 1205 Activity Dr.        | Vista      | CA    | 92081 | 760-536-0191        | jburnham@avalontest.com     |

| Advanced Technical<br>Services (ATS) | Manufactures Sales Representative & Technical Consultants, Specializing in EMC/EMI & RF Testing equipment -                                                                 | David Marquez                                        | 5237 Sun Chaser<br>Way   | Sacramento | CA    | 95835 | 408-594-3064        | david@atsca.com             |

|                                      | Anechoic chamber - Shielded rooms - Materials & much more.                                                                                                                  | Jesse Marquez<br>(President of Sales &<br>Marketing) | 2566 Aspen<br>Valley Ln. | Sacramento | CA    | 95835 | 925-997-2484        | jesse-avianca@sbcglobal.net |

| Amber Precision<br>Instruments       | API is a research-oriented EMC solution provider and EMC scanner manufacturer providing measurement technologies to resolve urgent and long-sought-after industry problems. | Giorgi Muchaidze                                     | 101 Bonaventura<br>Drive | San Jose   | CA    | 95134 | 408-752-0199 ext103 | giorgi@amberpi.com          |

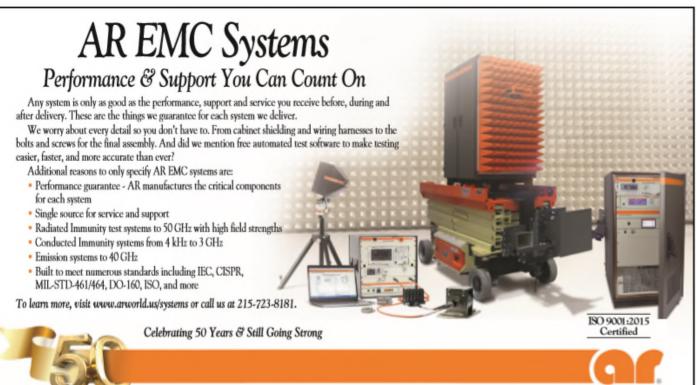

| AR/Microwave<br>Instrumentation      | Manufactures and distributes products for various EMC and wireless telecommunication req: RF and Microwave Power Amplifiers,                                                | Chuck Britten                                        | 160 School<br>House Road | Souderton  | PA    | 18964 | 215-723-8181        | cbritten@arworld.us         |

|                                      |                                                                                                                                                                             | Chuck                                                | Bishop                   |            |       |       |                     |                             |

|                                    | Hybrid Power Modules, Radiated & Conducted Immunity Test Systems, Electromagnetic Safety Products, Antennas, Test Software, accessories and more                                                          | Kevin Queen       | 160 School<br>House Road | Souderton  | РА | 18964 | 215-372-2929 | kqueen@arworld.us                 |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------|------------|----|-------|--------------|-----------------------------------|

| Advanced Test<br>Equipment Rentals | ATEC is a global leader in renting EMC & Power test equipment for meeting international standards; IEC 61000, DO-160 and MIL-STD-461, etc                                                                 | Gabriel Alcala    | 10401 Roselle<br>Street  | San Diego  | CA | 92121 | 800-404-2832 | galcala@atecorp.com               |

| скс                                | Service, Quality, Accetance,<br>EMC and Radio Testing! A2IA<br>Acredited, MIL -STD, DO-160,<br>Automotive, RS to 3,000V/m!<br>Transmitter certifications:<br>TCB for USA, CB for Canada,<br>and NB for EU | Todd Robinson     | 1120 Fulton<br>Place     | Fremont    | CA | 94539 | 209-299-3821 | todd.robinson@ckc.com             |

|                                    |                                                                                                                                                                                                           | Edward Wu         | 1120 Fulton<br>Place     | Fremont    | CA | 94539 | 209-299-3821 | edward.wu@ckc.com                 |

|                                    |                                                                                                                                                                                                           | Jennifer McMillan | 1120 Fulton<br>Place     | Fremont    | CA | 94539 | 209-299-3821 | jennifer.mcmillan@ckc.com         |

| ETS-Lindgren                       | ETS-Lindgren designs,<br>manufactures, and installs<br>EMC/EMI, RF/Microwave,<br>MIMO/OTA, and Accoustic<br>test and measurement<br>systems and components.                                               | Frans Stork       | 1301 Arrow Point<br>Dr   | Cedar Park | тх | 78613 | 512-630-9929 | frans.stork@ets-lindgren.com      |

|                                    | We also offer a full line of<br>services, including<br>calibration                                                                                                                                        | Rhonda Rodriguez  | 1301 Arrow Point<br>Dr   | Cedar Park | тх | 78613 | 512-771-8487 | rhonda.rodriguez@ets-lindgren.com |

|                          |                                                                                                                                                                                                                  | Kevin Kiersey                 | 6575 Goya Way                   | El Dorado Hills | CA           | 95762 | 916-933-2705 | kevinkiersey@outlook.com                |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------|-----------------|--------------|-------|--------------|-----------------------------------------|

|                          |                                                                                                                                                                                                                  | Tom Ellam                     |                                 |                 |              |       | 925-980-7887 | tom@atsemc.com                          |

| Fair-Rite                | Provide qualit products in all<br>markets, including EMI<br>Suppression, Power and<br>Antenna RFID.                                                                                                              | Bruce Sparrow                 | 1 Commercial<br>Row             | Wallkill        | NY           | 12589 | 845-895-2055 | kaneb@fair-rite.com                     |

|                          | Whatever you need, Fair-Rite is "your signal solution"                                                                                                                                                           | Tea Wiltse (MFS<br>Marketing) | 1 Commercial<br>Row             | Wallkill        | NY           | 12589 | 845-895-2055 | teawiltse@mfsmarketing.com              |

| Gauss                    | Ultra high performance: Best<br>RF; Lowest noisefloor;<br>Fastest FFT-based EMC<br>Receiver & the fatest<br>superheterodyne receiver on                                                                          | Anneliese Krieger             | 20 E. Thomas<br>Road Suite 2200 | Phoenix         | Az           | 85012 | 602-800-5900 | anneliese.krieger@tdemi.com             |

|                          | the planet.<br>For all your FULL<br>COMPLIANCE EMC testing<br>from DC-40GHz                                                                                                                                      | Gene Taylor                   | 20 E. Thomas<br>Road Suite 2200 | Phoenix         | Az           | 85012 | 602-800-5900 | gene@caprock.us                         |

| HV Technologies,<br>Inc. | US owned, 21 years industry experience, provide the most acurate and precise test and measurement equipment and support available to customers through strategic partnership with industry leading manufacturers | Patrick Bolliger              | 8526 Virginia<br>Meadows Dr.    | VA              | Manas<br>sas | 20109 | 703-365-2330 | patrick.bolliger@hvtechnologies.co<br>m |

| Haefely EMC               | Precision EMC transient immunity test equipment for surge, ESD, EFT and power quality testing to IEC/EN, ANSI/IEEE, UL, Bellcore, FCC, ITU standards and more            | Jon Nguyen                                  | 1650 Rt 22N                   | Brewster    | NY | 10509 | 845-230-9240 | dnguyen@hipotronics.com          |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------|-------------|----|-------|--------------|----------------------------------|

| In Compliance<br>Magazine | A monthly magazine that provides electrical engineering professionals with technical articles, news and information on compliance issues.                                | Sharon Smith                                | 531 King Street,<br>Suite 5   | Littleton   | MA | 01460 | 978-873-7722 | sharon.smith@incompliancemag.com |

| LEADER TECH INC           | Leader Tech is a world leading innovator and manufacturer of EMI shielding products for circuit boards, electronic enclosures, interconnect cables and Thermal Solutions | Brad Bowman                                 | 275 Saratoga<br>Ave Suite 260 | Santa Clara | CA | 95050 | 408-335-6700 | brad@bridgerep.com               |

|                           |                                                                                                                                                                          | Sheila Jackson                              |                               |             |    |       | 813-341-0410 | sjackson@leadertechinc.com       |

| NTS                       | Undisputed leader in<br>EMI/EMC engineering and<br>compliance services.                                                                                                  | Ciara Cunnigham                             | 2125 E. Katella<br>Ave #250   | Anaheim     | CA | 92806 | 714-732-9645 | ciara.cunningham@nts.com         |

|                           | With top EMI/EMC experts,<br>NTS is qualified to provide<br>customized services to speed<br>your product to market                                                       | James Bojorquez<br>(applications engineer)  | 2125 E. Katella<br>Ave #250   |             |    |       | 510-578-3500 | james.bojorquez@nts.com          |

|                           |                                                                                                                                                                          | Grace Nguyen (regional sales manager)       | 2125 E. Katella<br>Ave #250   |             |    |       | 510-364-1975 | grace.nguyen@nts.com             |

|                           |                                                                                                                                                                          | Ben Anderson<br>(Regional Sales<br>Manager) | 2125 E. Katella<br>Ave #250   |             |    |       | 510-946-9663 | ben.anderson@nts.com             |

| Pearson Electronics | Manufacturer of Injection and Current Probes for EMC Standards. Wide Band current probes for EMI, surge, lightning, pulse and other complex wave shapes. Powerline Ripple Detector for MIL-STD-461G CS101                                                                                                                                                                                                  | Erika Bisgard | 4009 Transport<br>St    | Palo Alto   | CA | 94303 | 650-484-6444 | erikabisgard@pearsonelectronics.com |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------|-------------|----|-------|--------------|-------------------------------------|

| RELIANT EMC         | International Distributor<br>specializing in EMC/EMI/RF<br>Test Equipment for<br>Electromagnetic compliance,<br>Self-certification and pre-<br>compliance testing for EMC<br>Standards                                                                                                                                                                                                                     | JТ            | 3311 Lewis Ave          | Signal Hill | CA | 90755 | 408-916-5750 | contact@reliantemc.com              |

| ROHDE & SCHWARZ     | we provide everything you need for development, precompliance and complaince measurements to ensure successful EMC certification. Fast EMC Receivers, Diagnostics tools for detecting EMI, EMC software packages for interfactive and fully automatic measurements, accessories for performing EMI measurements, compact and modular broadvand amplifiers, RF shielded chambers, complete EMC Test systems | Phil Parente  | 409 Dixon<br>Landing Rd | Milpitas    | CA | 95035 | 408-307-1805 | Phil.Parente@rsa.rohde-schwarz.com  |

| Stepp              | pIR | SY3-EMC Mechanically;<br>adjusted Yagi antenna is the<br>new standards-the solution<br>to MIL-STD-461G Radiated<br>Emissions, 30-200 MHz. For<br>more info, go to<br>www.steppir.com/e-series | John Mertel                       | 13406 SE 32nd<br>Street   | Bellevue  | WA | 98005 | 425-453-1910 | johnm@steppir.com           |

|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------|-----------|----|-------|--------------|-----------------------------|

| Techma<br>Electro  |     | Since 1989, Techmaster Electronics has grown to become a multi-faceted company as a global leader in electroni test equipment repair, calibration, sales and maintenance                      | Robert Tyler (VP)                 | 2453 Cades Way,<br>Bldg C | Vista     | CA | 92081 | 760-536-0227 | btyler@techmaster.us        |

|                    |     |                                                                                                                                                                                               | Neigh Krishna (Office<br>Manager) | 46782 Lakeview<br>Blvd    | Fremont   | CA | 94538 | 760-536-0234 | nkrishna@techmaster.us      |

| The E<br>Shop/ESDG |     | Solutions provoder for test<br>equipment, shielded<br>enclosures, onsite testing<br>and calibration services                                                                                  | Brendon Berg                      | 7401 Galilee<br>Road #160 | Roseville | CA | 95678 | 844-423-7435 | brendon.berg@theemcshop.com |

| TOYO Corporation | Offers "EMC Total Solutions" from EMC design to EMC test carrying TOYO EMC Test software and Systems with Keysight Accelerated Time Domain EMI receivers, OTA measurement solutions from GTS, Near Field EMI Sacnner from API and EMI Simulation Software from NEC | Nori Sugawara (VP of<br>EMC Business/Inarte<br>Certified EMC Eng) | 42840 Christy St.<br>Suite 110 | Fremont   | CA | 94538 | 510-438-9548      | nori.sugawara@toyotechus.com |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------|-----------|----|-------|-------------------|------------------------------|

| WEMS Electronics | Manufactures/supplies EMI/RFI filters and electronics and electromechanical systems for aerospace, military, commercial markets.                                                                                                                                   | Donna Miller (VP<br>President Sales &<br>Marketing)               | 4650 W<br>Rosecrans Ave.       | Hawthorne | CA | 90250 | 424-348-9932      | dmiller@wems.com             |

|                  | Provide I/O, powerline, signal<br>line filters, filter circuit<br>design, packaging and layout                                                                                                                                                                     | Manager)                                                          | 4650 W<br>Rosecrans Ave.       | Hawthorne | CA | 90250 | 310-644-0251 x105 | aifri@wems.com               |

- \$4Mil of Inventory for EMC and RFI testing (with \$4 million planned to spend)

- Chamber install, upgrades and retrofits

- RF Calibration (CI Generators, LISN's, Current Probes and more)

- Turnkey Radiated Emissions for FCC and more

- 5G and OTA Test Systems

- On-site setup and support

- Stocking of E-field probes

#### **Applications Supported**

- Automotive:

- ISO 7637-2, ISO 7637-3, ISO 10605, ISO 16750-2

- All Sections of ISO 11452

- CISPR 25 and CISPR 12

- Medical: IEC 60601-1-2 Edition 4

- All IEC/EN 61000-4-X for CE, UL, CSA Marking

- Military Standards 461G, 331, 464, 704

- Aerospace, Radar, Pulse, HIRF, DO-160 and more.

- ETSI EN 301 489 5G Telecom and other 3GPP Requirements We're also ESDguns.com

#### **Stocking Equipment From**

- Ametek (Teseq, EM Test, IFI)

- Amplifier Research

- ETS-Lindgren

- 3ctest

- Pearson Electronics

- PMM / Narda

- AH Systems

- Haefely

- Schwarzbeck

- Schloder

- Com-Power & Several more

Online Ordering Most EMC test equipment and accessories are available to order today with any major credit card.

Immediate Shipment Most EMC test equipment is in stock and available for immediate shipping.

More Information Capital B2B acquisitions aren't like online shopping. Call 800.794.0349 now for account setup, formal quotes, or technical information.

## RENT EMC TEST EQUIPMENT

## TO MEET A VARIETY OF STANDARDS

MIL-STD-461 • DO-160 • IEC 61000 IEC 60601-1-2 • ANSI C62 • ISO 7637 MIL-STD-1275 • CISPR and more...

## FROM THE LARGEST SUPPLIER OF EMC TEST EQUIPMENT

Amplifiers • ESD Guns • EMI Receivers Signal Generators • Power Meters Field Probes & Monitors • Antennas and more...

#### **Rent TODAY!**

The Knowledge. The Equipment. The Solution.

888-544-ATEC (2832)

www.atecorp.com

# ACCELERATED TIME DOMAIN SCAN

TOYO's world-renowned EMC software "EPX/RE" makes accurate and reliable EMI measurements without missing noise. None. Zero. We achieve this next-to-impossible feat by implementing an Accelerated Time Domain Scan feature and integrating it in the new Keysight Technologies' N9048B PXE EMI receiver. Engineers can now finally analyze noise behavior relative to not only frequency but also to the time sequence.

Learn more. E-mail us at <a href="mailto:info@toyotechus.com">info@toyotechus.com</a>, visit our website at www.toyotechus.com or call us at +1-510-438-9548.

EMI, ESM, Phase Measurement, Resonance Scan, NF FF, ESD Current Spreading, RF/ESD Immunity, IEC 61000–4–2 Robotic Tester

Amber Precision Instruments is the IC, module and system level EMC/EMS evaluation tool manufacturer and solution provider equipped with unique combination of IC level and system level expertise.

**TEST WITH CONFIDENCE®**

#### **Our Vision**

Avalon Test Equipment aspires to be the nationally preferred test equipment rental company by means of legendary customer service and exceptional product quality. The rental business is the foundation upon which we build our sales and service departments. Our vision and commitment to achieving excellence brings true value to our clients as a full-service provider.

Avalon Test Equipment has a reputation built on client trust and serves a great number of repeat customers. Avalon was founded in 1998, and expanded by opening a second office in Dallas, Texas. This expansion was executed to better meet the needs of our customers. CEO Steve McIlhon's philosophy, "to provide our customers with the best products and services delivered in a friendly and professional manner" forms the culture of Avalon. When you choose Avalon, we want you to feel like a part of our family.

We offer a complete range of electronic test equipment and accessories for immediate rental or sale. Whether you need a last minute rental or a quick calibration, we are ready to exceed your expectations. We value our customers and promise to provide you with the same exceptional products and legendary service we have been providing since 1998.

## **TEST WITH CONFIDENCE®**

## A HIGHER STANDARD

With the most EMI/EMC labs in the Western Hemisphere, NTS provides flexible scheduling and expedited services.

www.nts.com | 844.332.1885

ar divisions: rf/microwave instrumentation • modular rf • sunar rf motion • ar europe USA 215-723-6181. For an applications engineer, call 800-933-6181.

In Europe, call ar United Kingdom +44 1908 282766 • ar France +33147917530 • ar Deutschland +49 6101 80270 0 • ar Benelux +31 172 423000

Download the AR RE/Microscove Mobile App: sevenementLus/arApp

Copyright © 2019 AR.

The conge stripe on AR products is Reg. U.S. Par. & T.M. Oli.

#### **MIL-STD-461 TESTING**

CS114/115/116

Specifically designed for sections CS114/115/116 in MIL-STD-461 (including "G") and RTCA/D0-160 requirements

- · 3 Components

- 8700i Injection Probe

- 8705C Current Probe

- F-3 Test Fixture

- 10 kHz to 400 MHz Response

- . 100W for up to 30 minutes

- · 4 Amps RMS current

- 15 Amps max peak current

Greatly simplifies measurement of injected audio-frequency ripple on a power bus in EMI tests such as MIL-STD-461G CS101

CS101

- Measure audio frequence (CS101) injected ripple

- Separates ripple from power waveform

- . Use with spectrum analyzer

- Measure audio frequency . Max 120-240 Vac, 270 Vdc

- Selectable frequency response:

- Flat response 10 Hz ~ 150 kHz

- CS101 setting provides constant output over entire frequency range

#### pearsonelectronics.com

PHONE: +1 (650) 494-6444

#### **CAPABILITY UPGRADE:**

- FLUKE MULTI-CALIBRATORS 55XXAs\*

- EFT/BURST GENERATOR UP TO 8 KV

- SURGE GENERATOR UP TO 12 KV AND UP TO 3 KA

- VIBRATION/ACCELEROMETER UP TO 36 GPK FROM 1 HZ TO 10 KHZ

- ESD SIMULATORS UP TO 30 KV FOR 330 PF AND 150 PF NETWORK MODULES

- ANTENNA CALIBRATION:

- LOG PERIODIC

- BICONICAL

- HORN

- HYBRID ANTENNA

TECHMASTER"

Global Leader in Test Equipment Solutions

CALIBRATIONS + REPAIRS + SALES + RENTALS

www.techmastertest.com + sales@techmaster.us + 866-779-5695

NO ONSITE FEE FOR ORDERS OVER \$1K\*

FREE LOCAL PICK-UP AND DELIVERY

#### STAY CONNECTED WITH OUR APP

- ASSET MANAGEMENT: SEARCH AND DOWNLOAD YOUR CERTIFICATES

- QR READER: SCAN YOUR CALIBRATION STICKER'S

QR CODE TO OPEN A CERTIFICATE

- TICKETS: SUBMIT FOLLOW-UP TICKETS TO TECHMASTER SUPPORT TEAM

- CONTACT US: ACCESS OUR PHONE DIRECTORY AND SOCIAL MEDIA

- NOTIFICATIONS: IMPORTANT NEWS, COMMUNICATIONS AND PROMOTIONS

\*ASK FOR DETAILS

# Power Integrity for High-Speed Design on Multi-Layer PCBs

Concepts and Physics

James L. Drewniak

Clear Signal Solutions and

Missouri S&T EMC Laboratory

james.drewniak@clearsig.com

#### Contributors

- IBM B. Archambeault, S. Connor, M. Cocchini, W. Becker, M. Cracraft, A. Ruehli

- Cisco B. Achkir, S. Scearce, Q. Gaumer, M. Sapazhnikov

- Missouri S&T B. Zhao, S. Bai, S. Liang, X. Zhu, K. Shringapure, S. Pan, J. Xu, J. Fan

## PI Module Overview Part 1 – Concepts and Physics

- The PDN problem

- Noise on the PDN and an FPGA example

- PDN design considerations

- A couple of preliminary concepts

- Current and inductance physics

- A reduced order circuit model from a first principles formulation

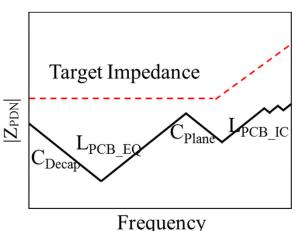

- Characteristic Z<sub>PDN</sub> and relationship to physics

- Understanding PDN physics and design through examples

- Identifying limiting physics in design

- Adding decoupling capacitors

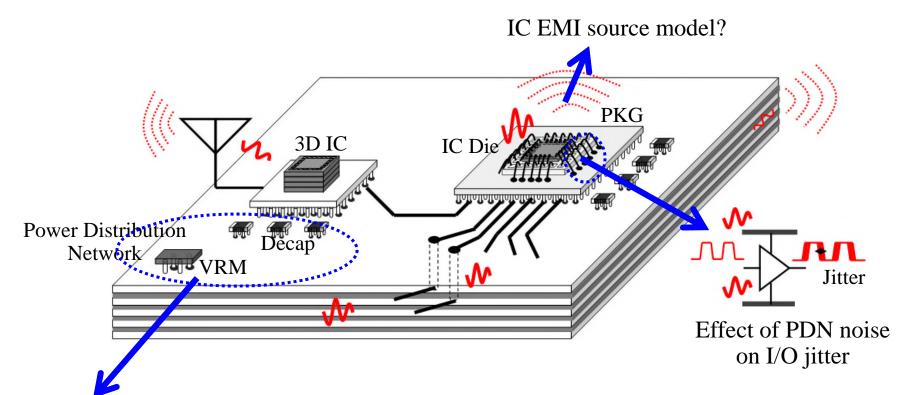

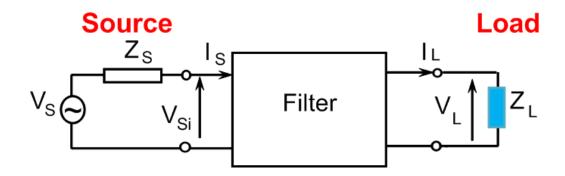

### PDN Problem

#### High-speed, integrated, and mixed electronic system

Power Distribution Network

- VRM

- Decoupling capacitors

- Power net area fills

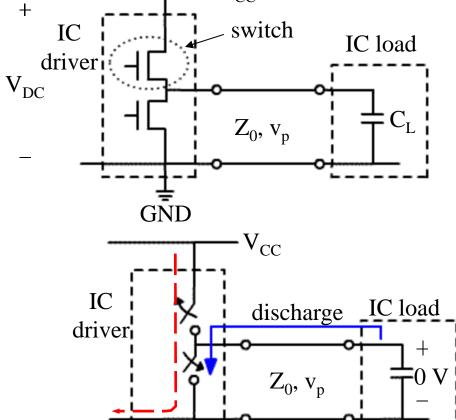

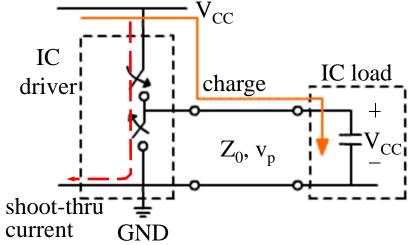

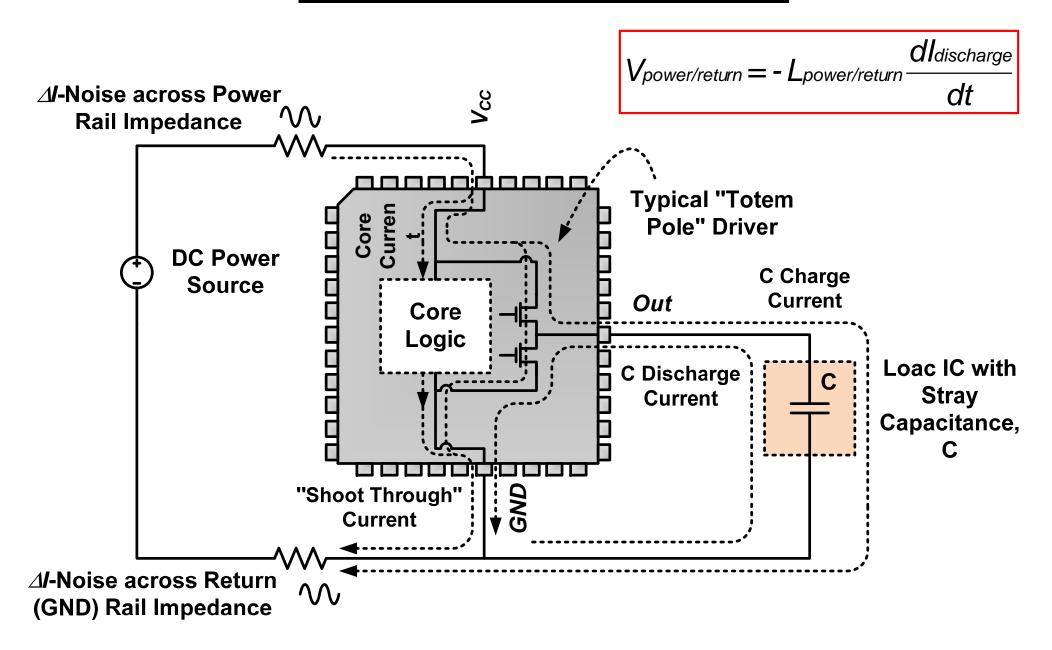

## Logic Transitions and Current Draw

Shoot-thru current (and everything else we can't account for)

Load charging current

Load discharge current

**GND**

LO to HI

HI to LO

This charge to support IC switching must be provided by the PDN – package, PCB

shoot-thru

current

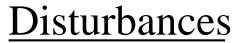

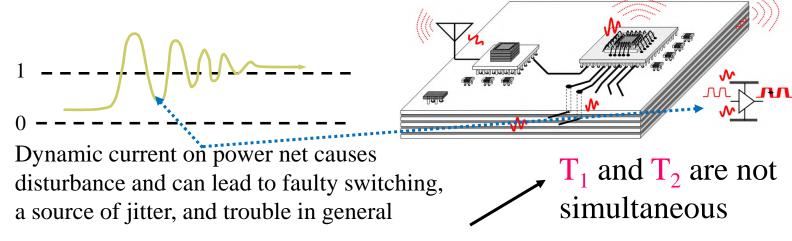

## Voltage Switching/Dynamic Current Draw

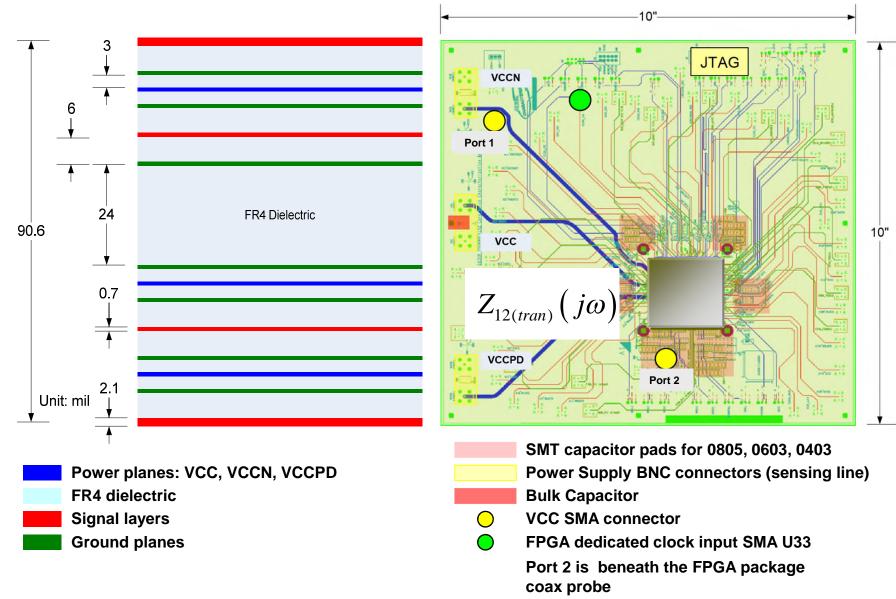

## PCB for FPGA Core PDN Noise Example

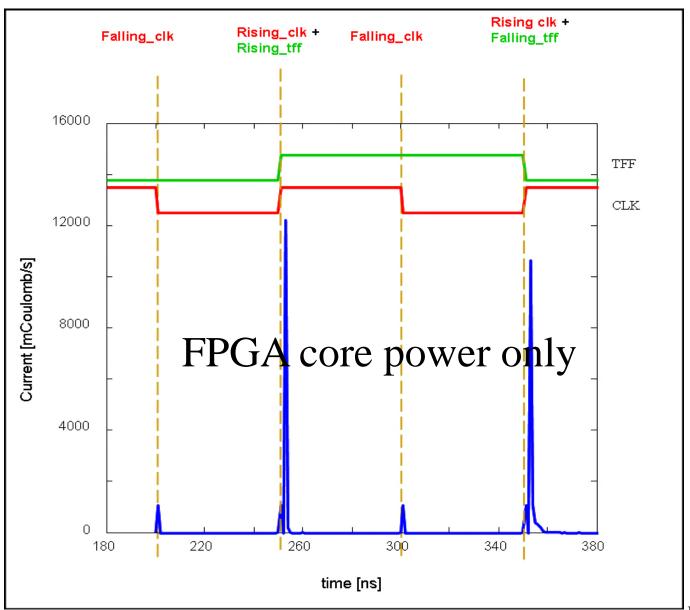

## Current Draw and the Logic Waveform

## Dynamic Current Profile (calculated)

## FPGA Core power only

Reconstructed time domain current for a large number of toggle flip-flops - 9

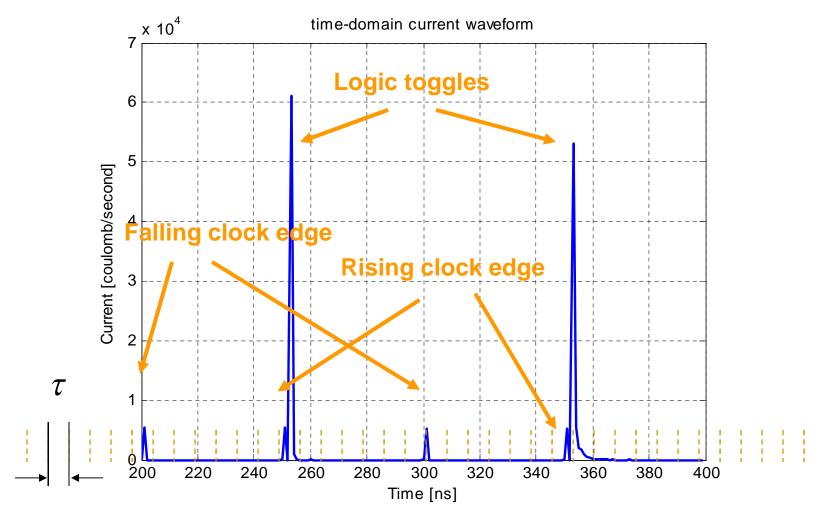

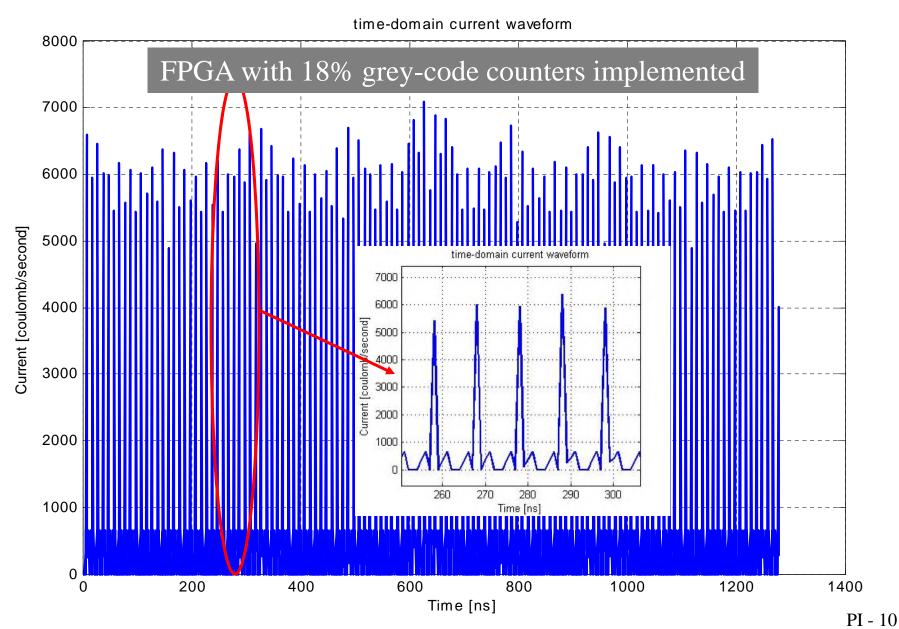

## Transient Current Waveform - Simulated

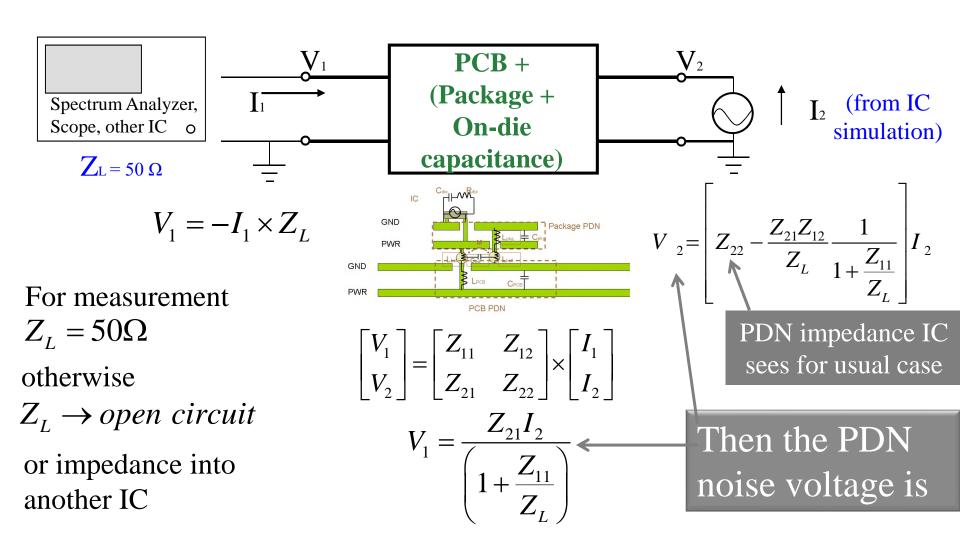

## Voltage Disturbance Calculations with Z-Parameters

$I_2$  is from IC simulation.  $Z_{21}$  and  $Z_{11}$  are both from impedance simulation (also are calculated from S-parameters from modeling or measurement).

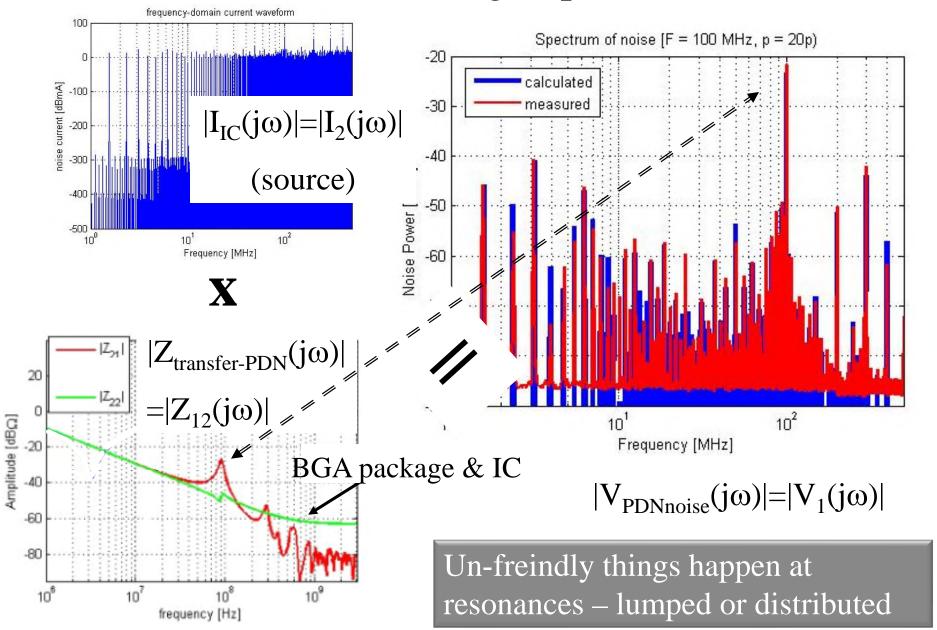

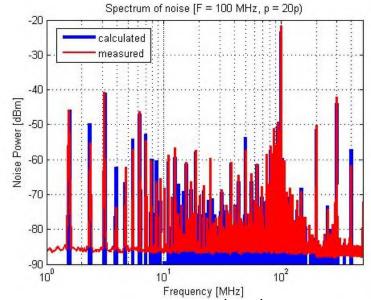

## PDN Noise Voltage Spectrum Prediction

## PDN Noise Voltage from Impedance

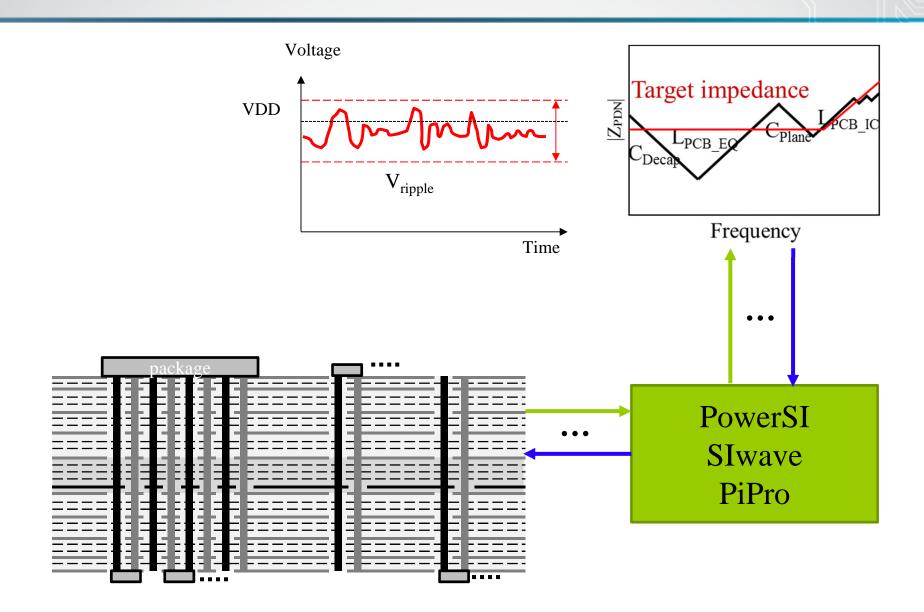

$$V_{PDN}(\omega) = Z_{PDN}(\omega) \times I_{IC}(\omega)$$

$$v_{PDN}(t) = F^{-1} \left\{ V_{PDN}(j\omega) \right\}$$

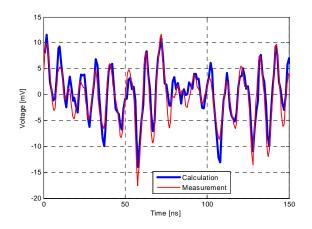

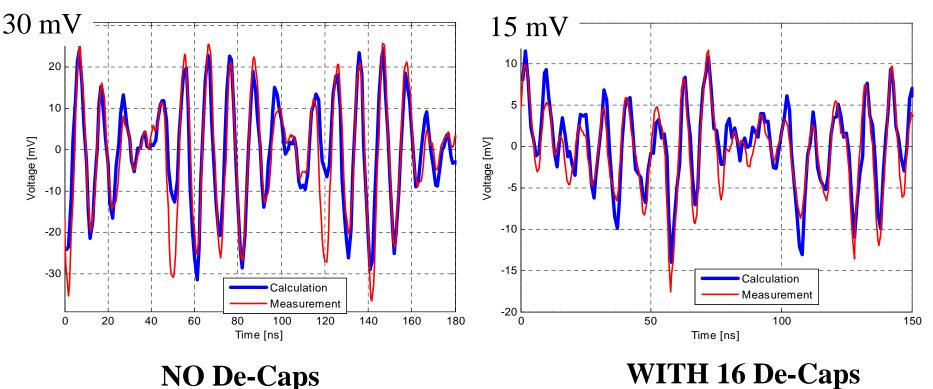

## Transient PDN Noise Voltage

Inverse Fourier Transform to get  $v_{PDN}(t)$

$$v_{PDN}(t) = F^{-1} \left\{ V_{PDN}(j\omega) \right\}$$

The estimated and measured noise voltage were compared, with a 100 MHz clock input, multi-frequency FPGA configuration, on the bare board and decoupled board.

PI - 14

## PI Module Overview Part 1 – Concepts and Physics

- The PDN problem

- Noise on the PDN and an FPGA example

- PDN design considerations

- A couple of preliminary concepts

- Current and inductance physics

- A reduced order circuit model from a first principles formulation

- Characteristic Z<sub>PDN</sub> and relationship to physics

- Understanding PDN physics and design through examples

- Identifying limiting physics in design

- Adding decoupling capacitors

## PCB PDN Design Considerations

### PI Module Overview Part 1 – Concepts and Physics

- The PDN problem

- Noise on the PDN and an FPGA example

- PDN design considerations

- A couple of preliminary concepts

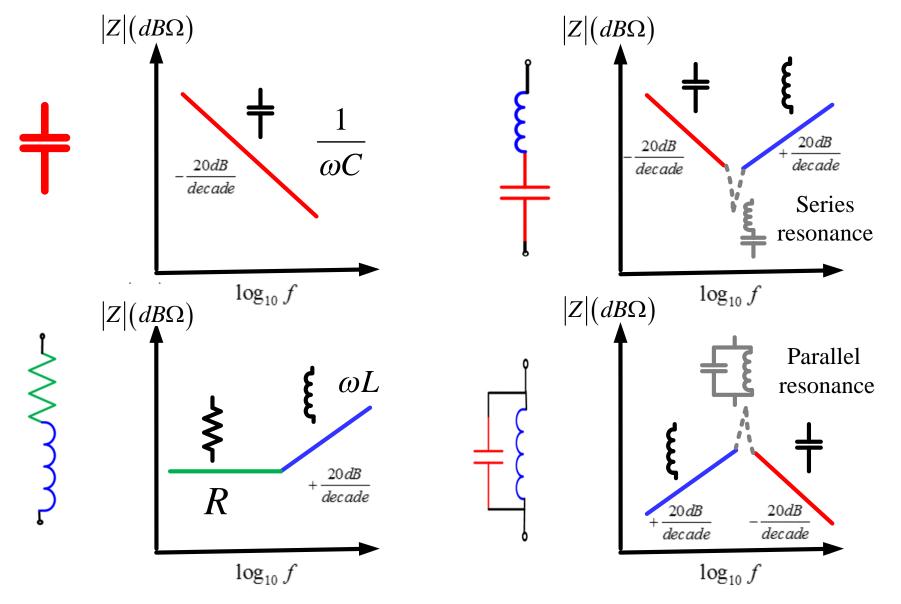

- Responses for RLC circuits

- High-frequency current path

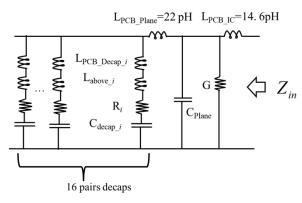

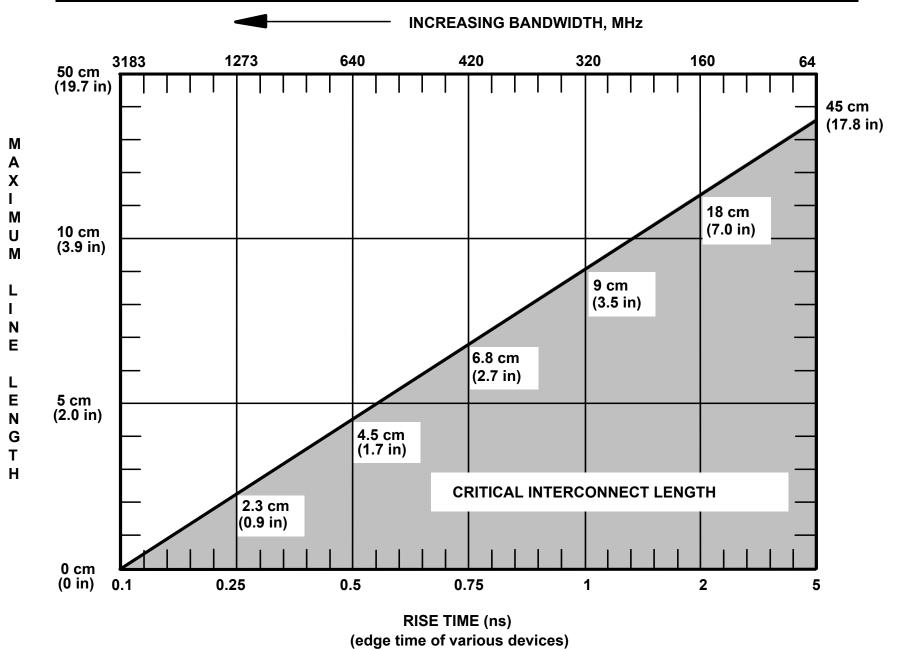

10<sup>-2</sup> [GHz]

10-1

$10^{-3}$

#### Reminder – Circuit Model Behavior with Frequency

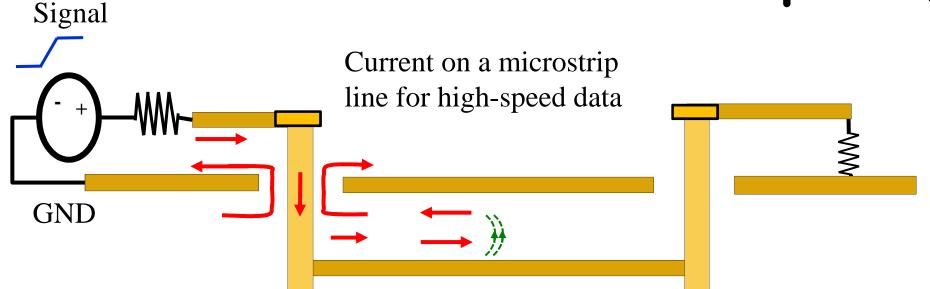

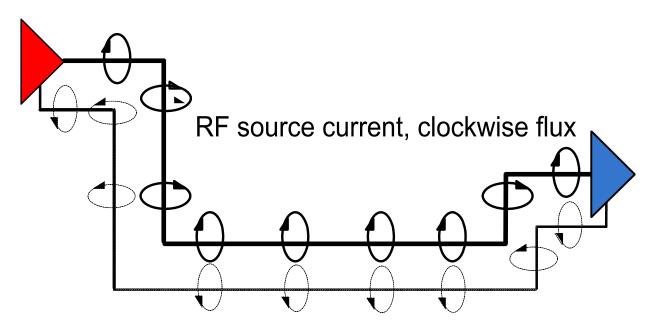

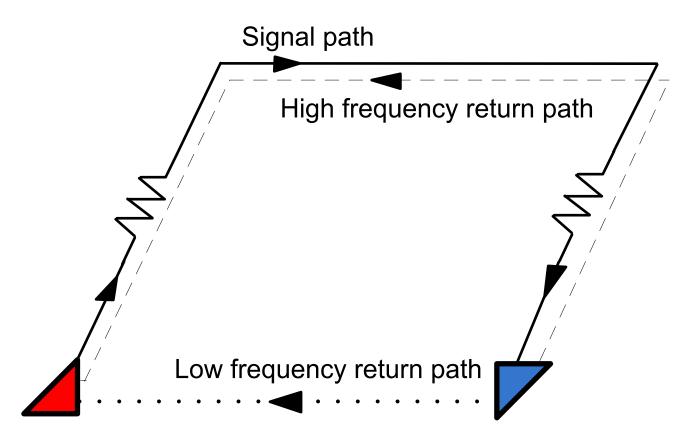

#### Reminder: Current Behavior

impeded by

- Conduction current carried by electrons  $\vec{J}_{cond} = \sigma \vec{E}$ Displacement current carried by  $\vec{J}_{displ} = \varepsilon \frac{d\vec{E}}{d\vec{E}}$

- admitted by

At high frequencies, when the copper planes/area fills that function as the signal reference conductors are several skin depths thick, no E or H fields can exist inside these planes. In order for this to be the case, currents have to "see" a partner and cannot "look through" conductors.

### PI Module Overview Part 1 – Concepts and Physics

- The PDN problem

- Noise on the PDN and an FPGA example

- PDN design considerations

- A couple of preliminary concepts

- Current and inductance physics

- Conduction current path through layers (vertical) on PCB PDN and associated inductance

- Decomposing the inductance into pieces

- Current path across the power net area fill and the ground power return current

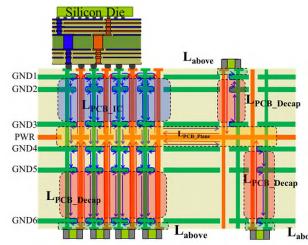

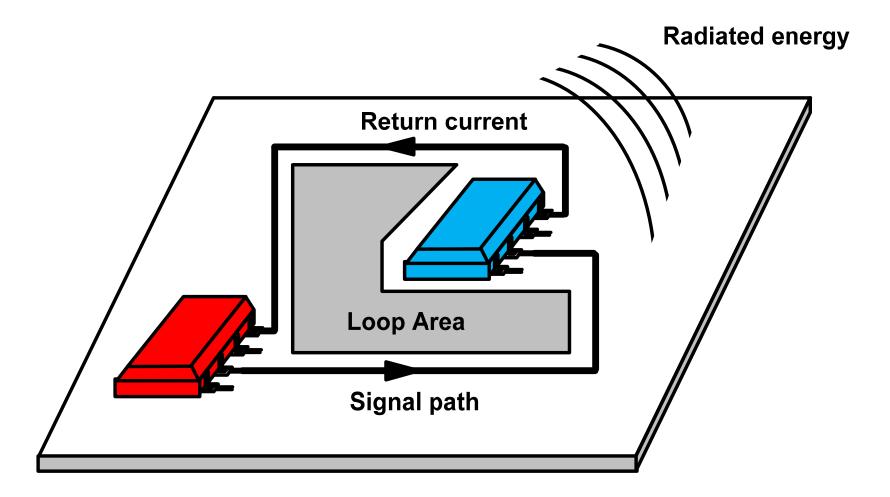

# The Objective and Guiding Physics: Conduction Current Path results in Inductance

# The Objective and Guiding Physics: Conduction Current Path results in Inductance

#### The Objective and Guiding Physics:

#### Condution Current Path results in Inductance

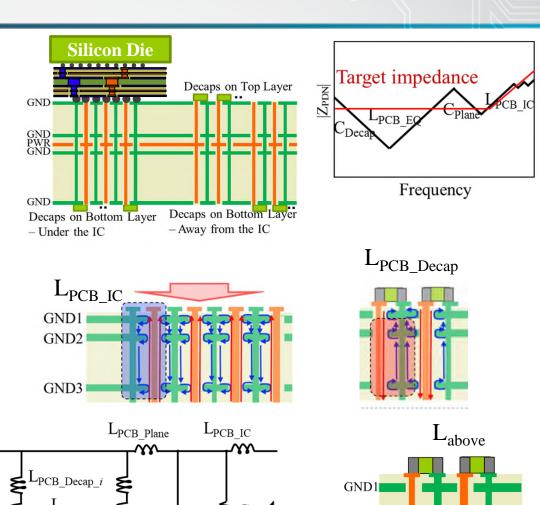

#### <u>Key Point – Current Path and Inductance</u>

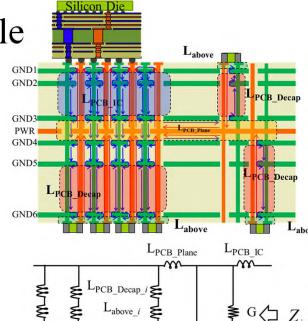

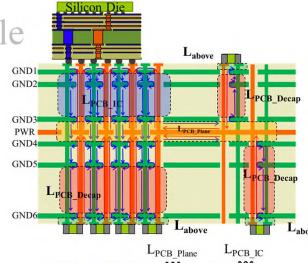

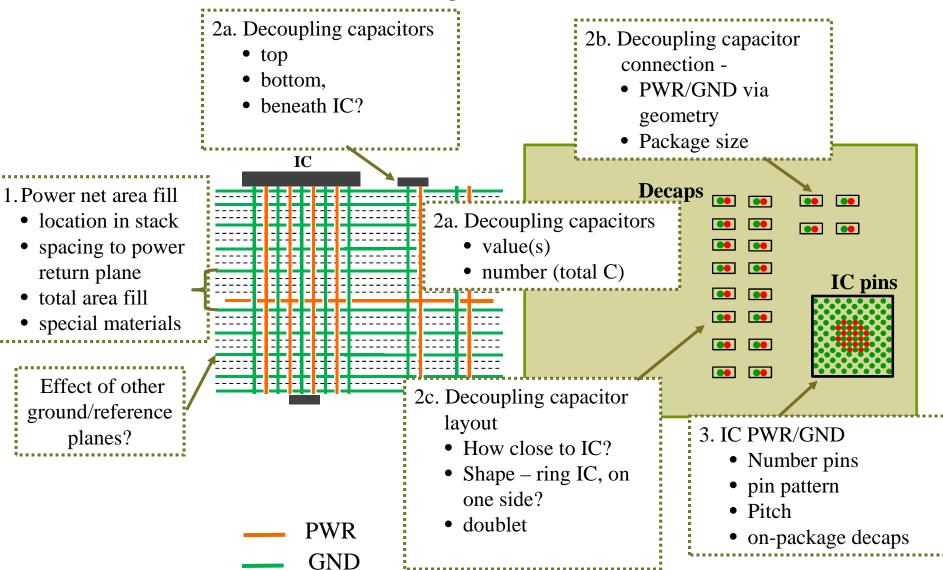

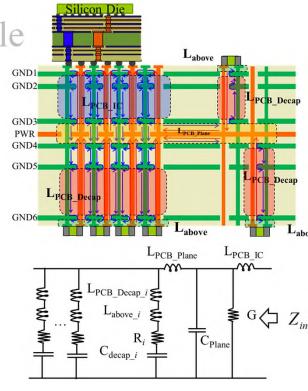

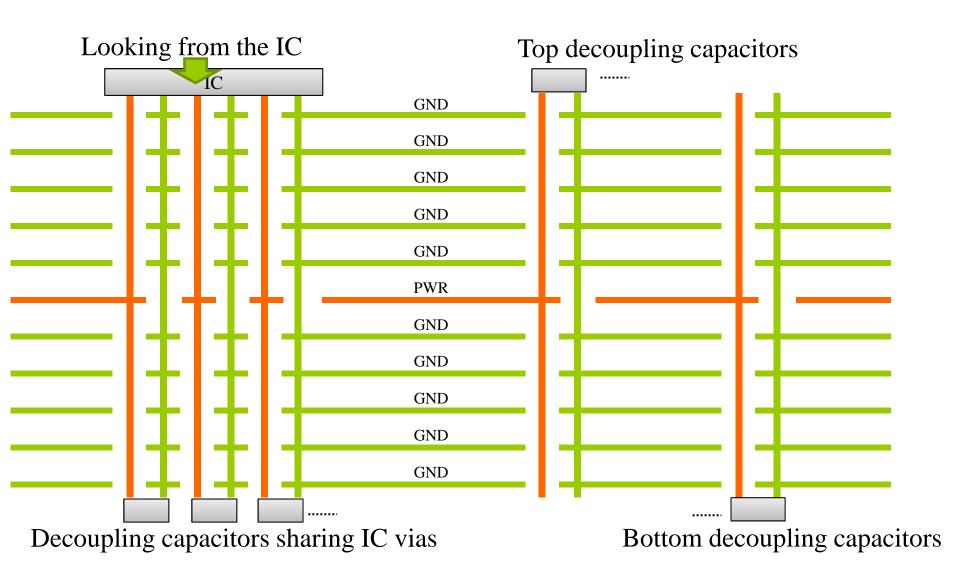

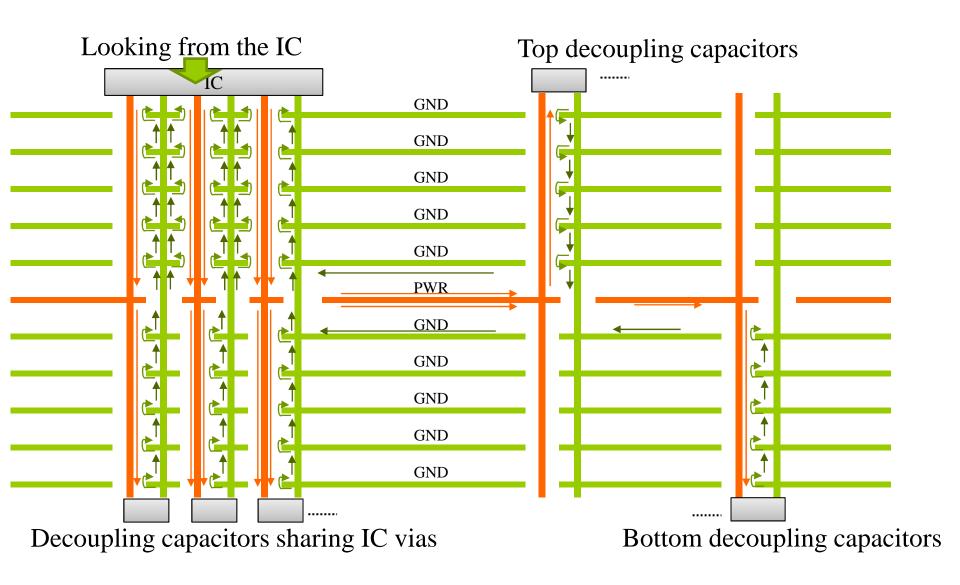

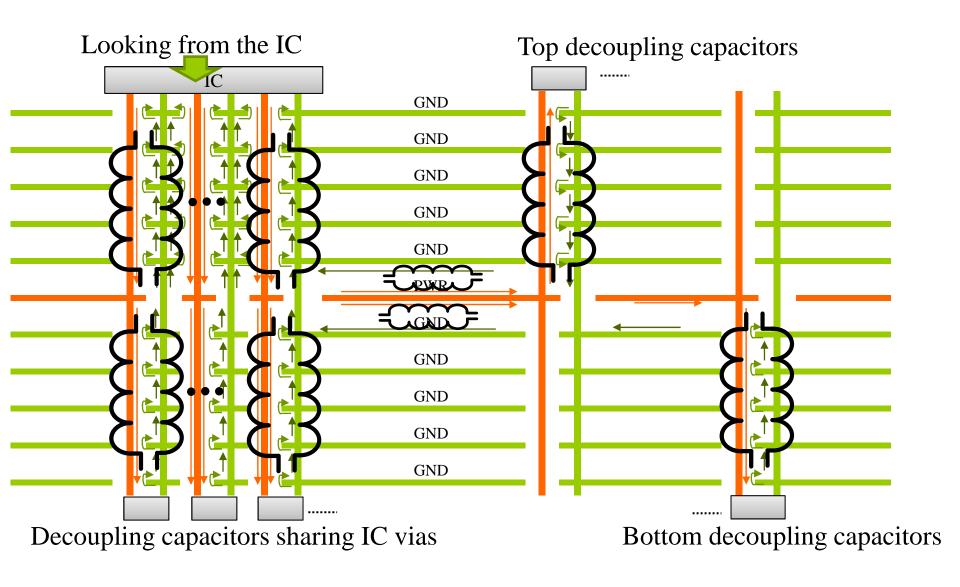

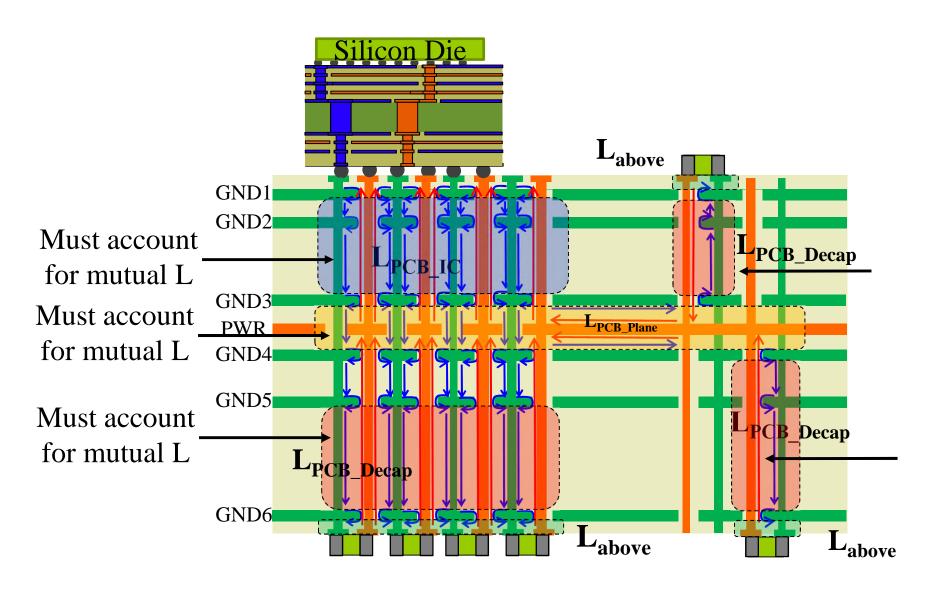

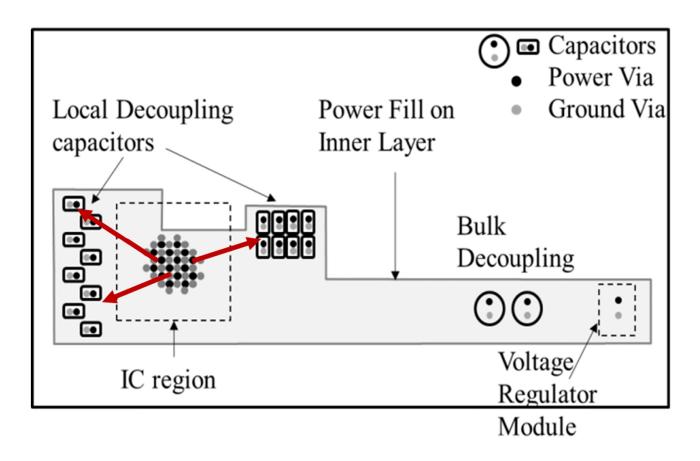

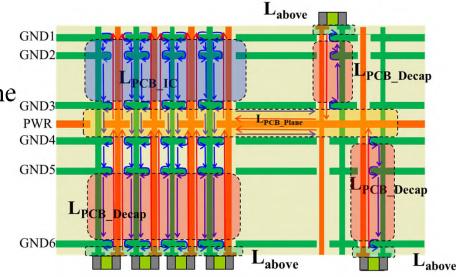

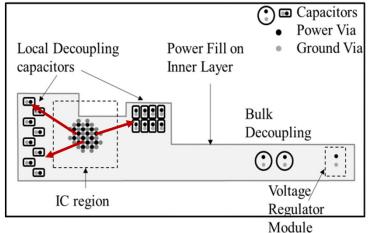

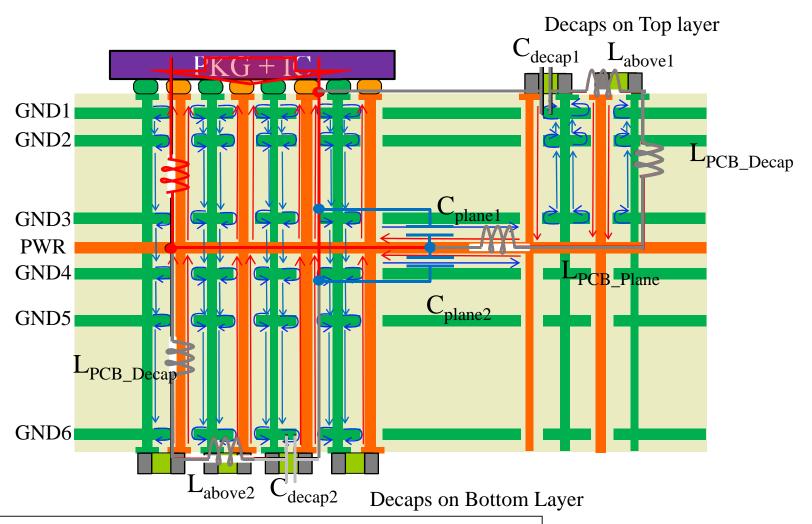

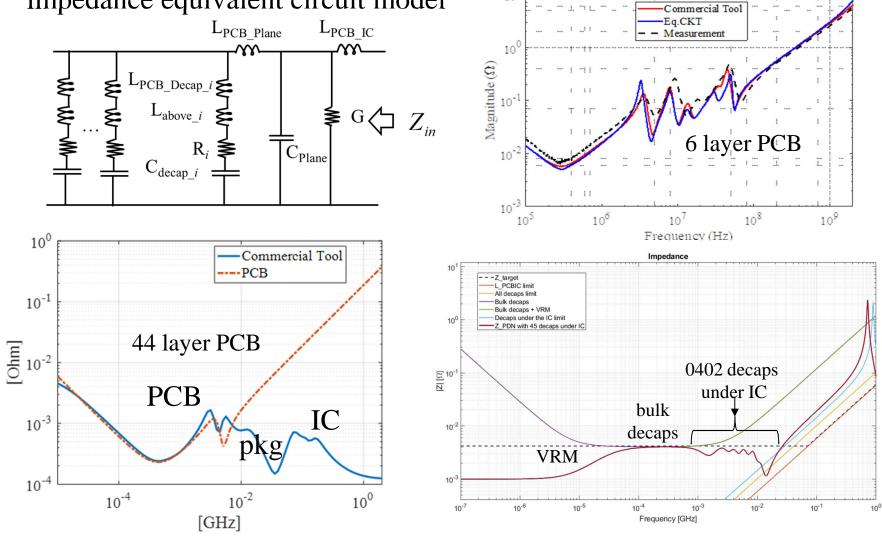

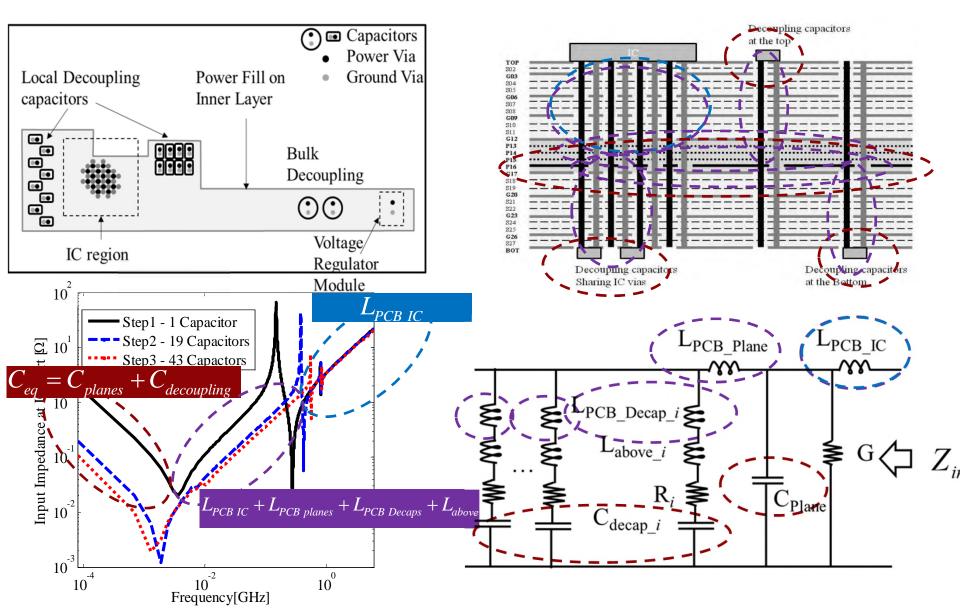

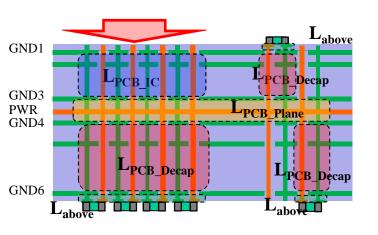

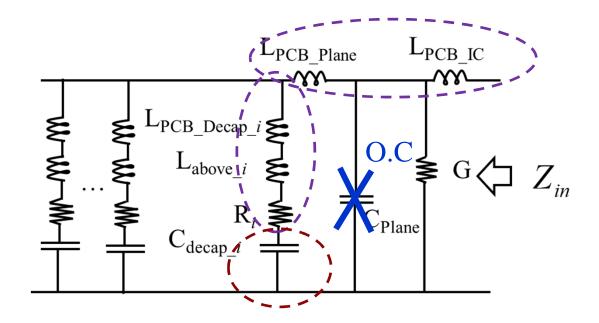

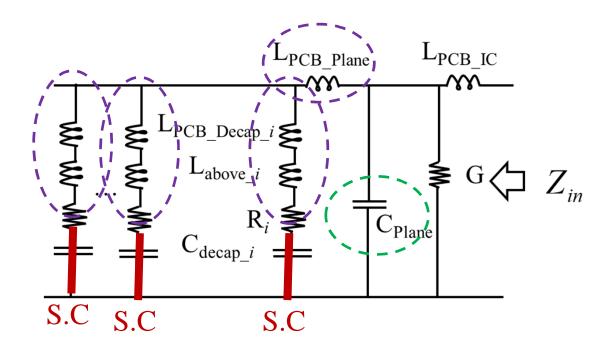

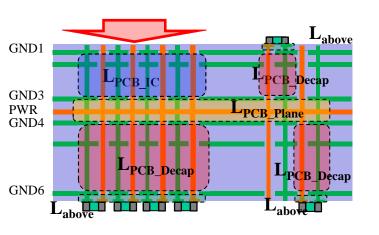

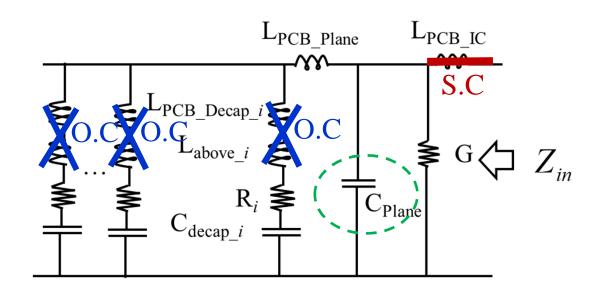

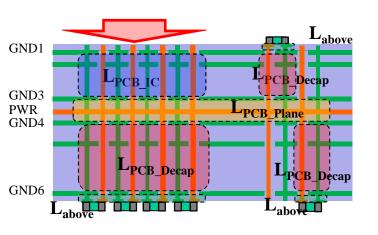

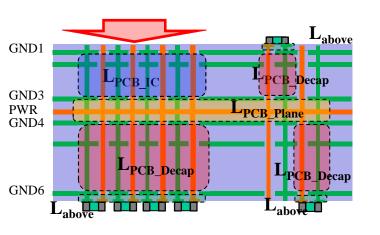

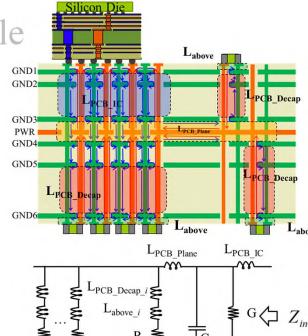

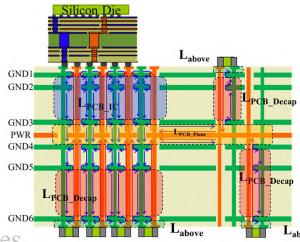

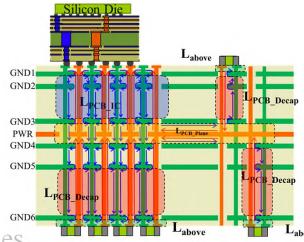

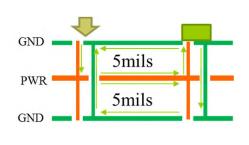

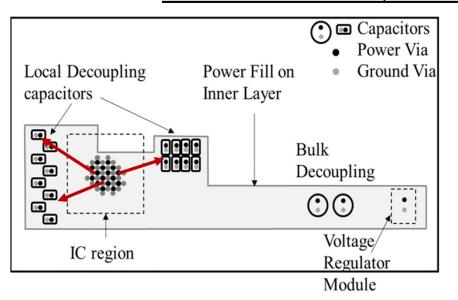

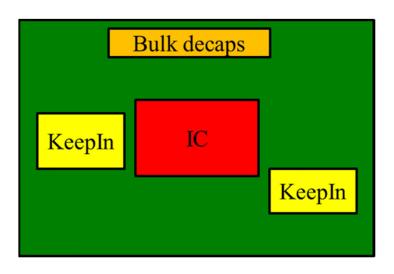

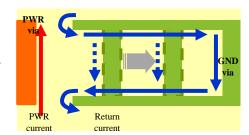

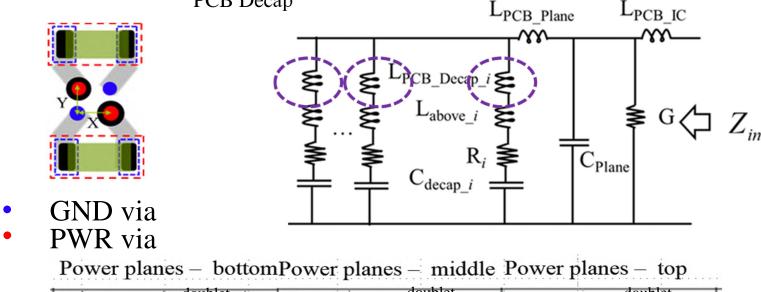

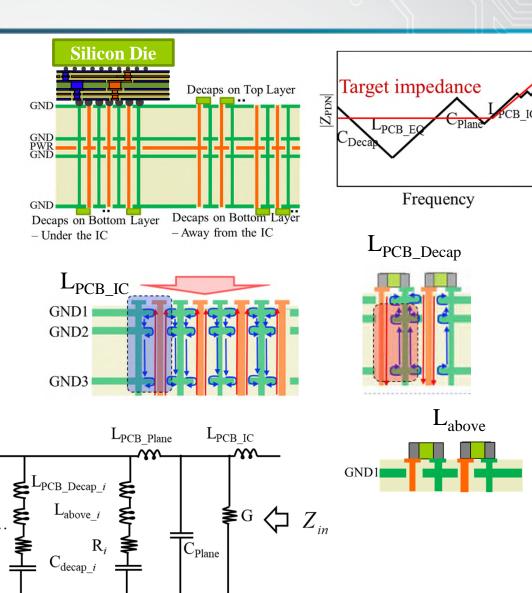

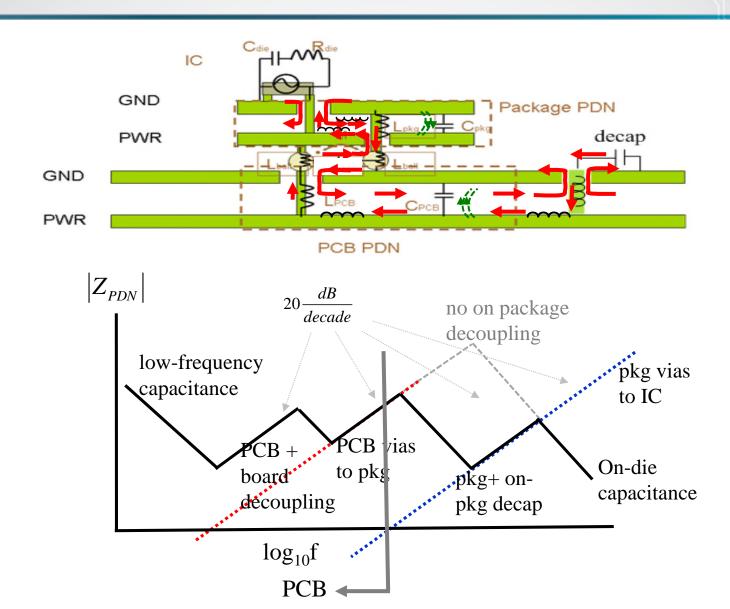

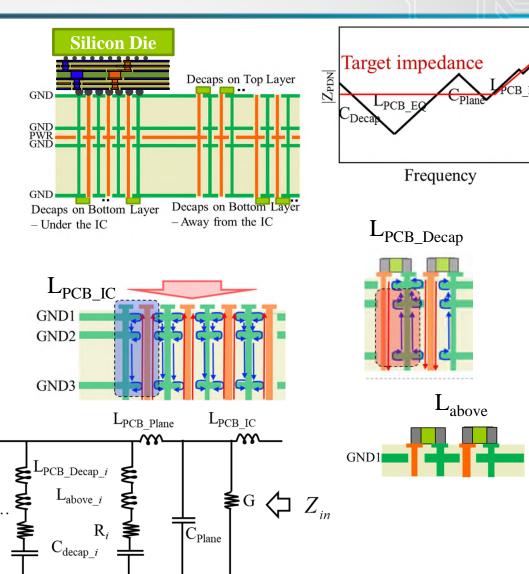

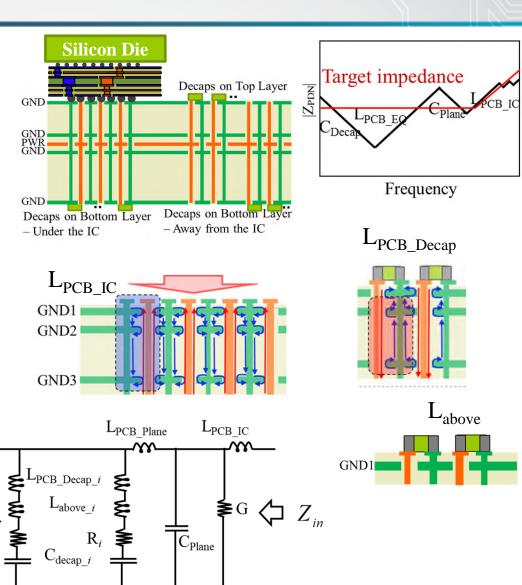

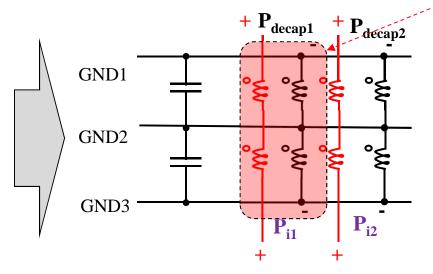

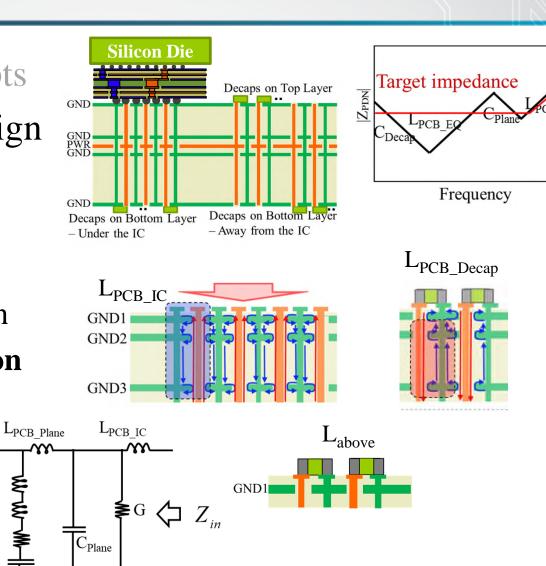

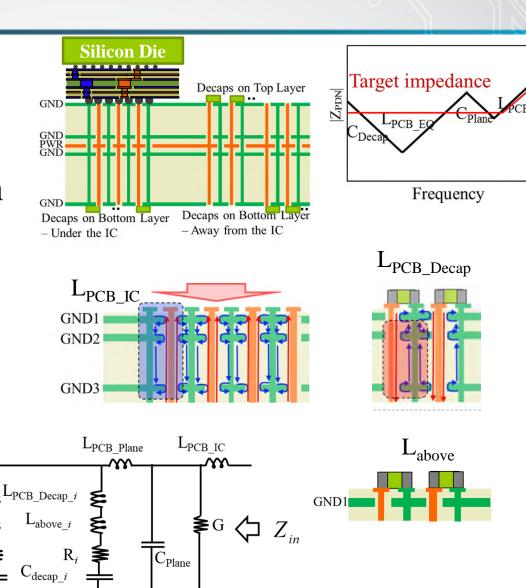

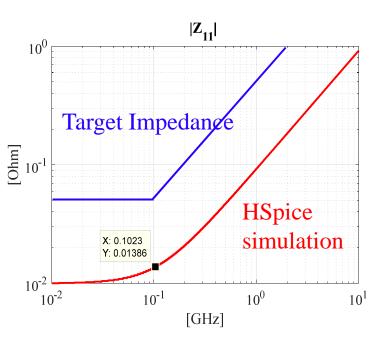

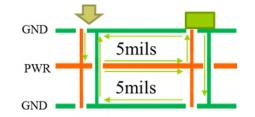

Four contributions (current path pieces) to the Z<sub>PDN</sub> inductance Top decoupling capacitors Looking from the IC Above PCB to decaps **GND** caps-to- $Z_{PCB-in}(j\omega)$ PWR net **GND** area fill **GND GND** pkg-to-PWR net area fill in PWR net area fill **GND GND GND** Decoupling capacitors Bottom decoupling sharing IC vias capacitors

### Geometry and Inductance Decomposition

#### Current Path, and Inductance

Current path from IC to decaps  $\underline{in\ the\ power\ net\ area\ fill\ layer}$  is better to be in line (and not cross cutouts, around corners, etc.).  $L_{PCB\_plane}$  is increased otherwise.

#### **Key Points**

- Production printed circuit boards that use area fills for the power net will have from 4 to over 40 layers. The IC package may have tens to hundreds of vias, and there may be tens to hundreds of decoupling capacitors. The *complexity is high*, but the *current path physics* are very *straight-forward*, though there will be many parallel paths.

- The inductance associated with a current path can be decomposed into four pieces along the path.

- Direct, "line-of-sight" current paths between the IC and the decaps will have less L<sub>PCB Plane</sub> inductance than current paths that cross cutouts, slots, go around corners, etc.

## PI Module Overview Part 1 – Concepts and Physics

- The PDN problem

- Noise on the PDN and an FPGA example

- PDN design considerations

- A couple of preliminary concepts

- Current and inductance physics

- A reduced order circuit model from a first principles formulation

- Impedance from a Maxwell's equation formulation

- A many element physics-based model to a reduced order impedance equivalent circuit with inductance related to geometry decomposition

[GHz]

10-1

10<sup>-3</sup>

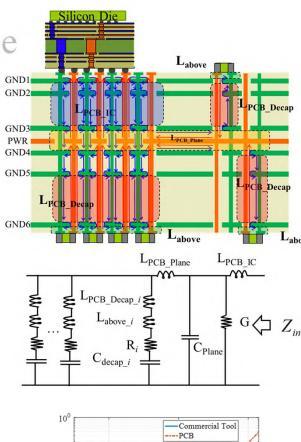

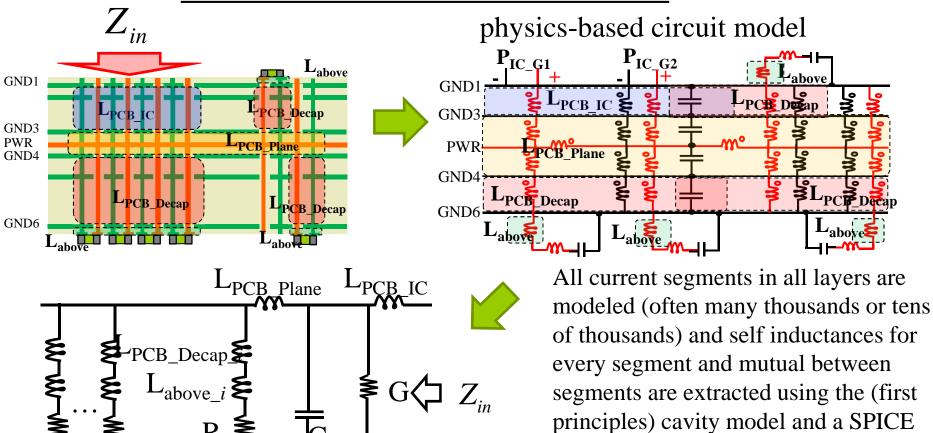

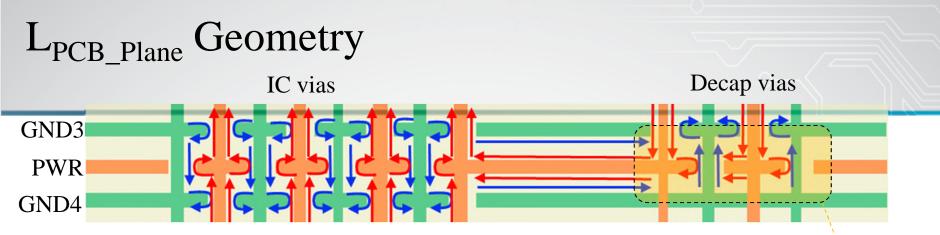

#### Calculating Inductance from Current Path Physics

- All current segments in all layers are modeled (often many thousands or tens of thousands) and self inductances for every segment and mutual between segments are extracted using the (first principles) cavity model.

- Self and mutual inductances are included.

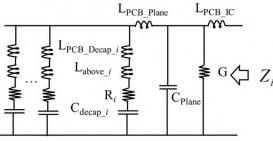

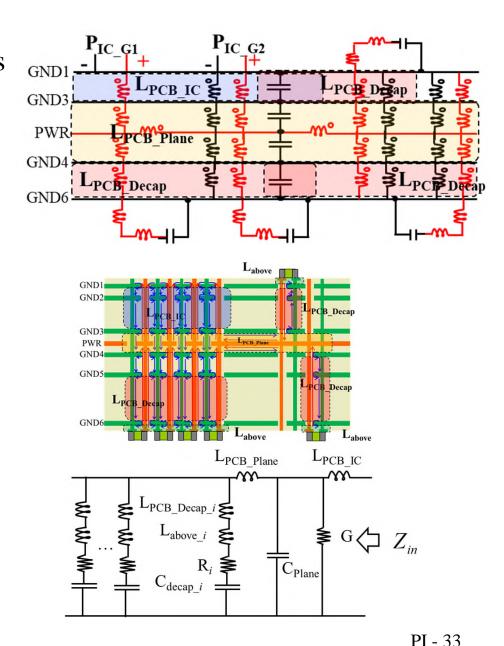

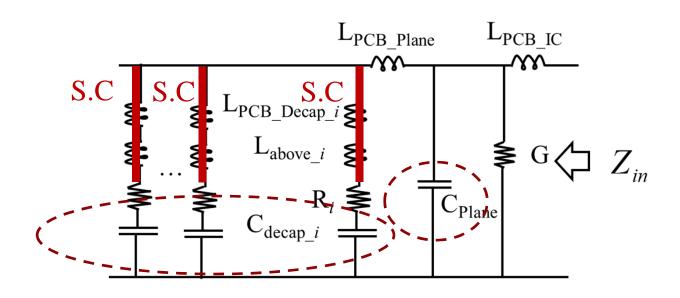

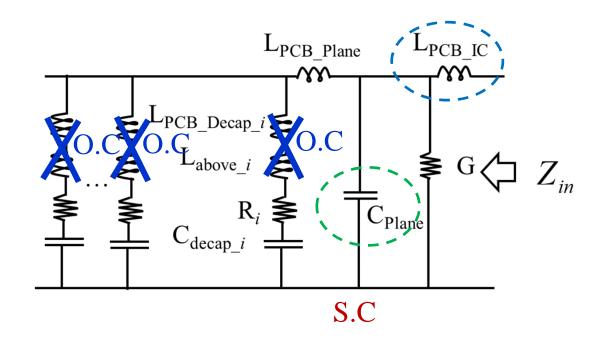

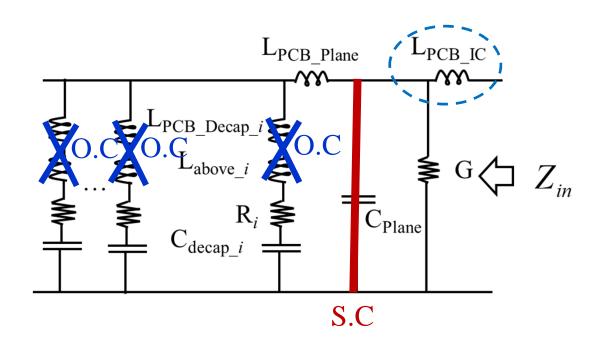

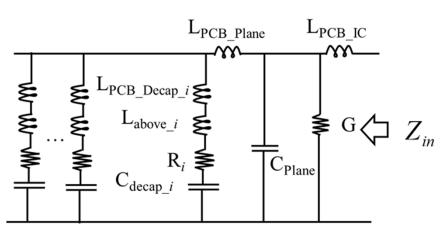

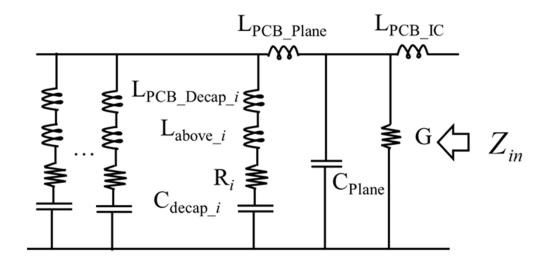

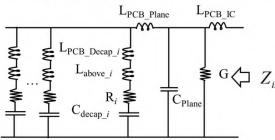

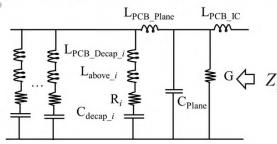

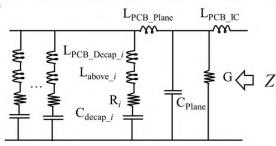

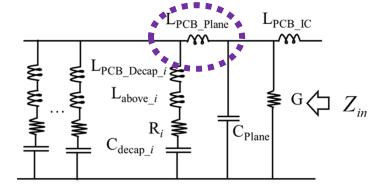

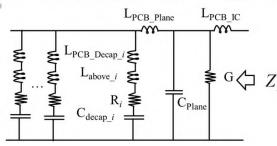

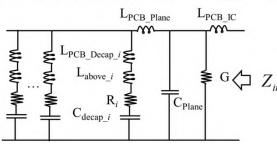

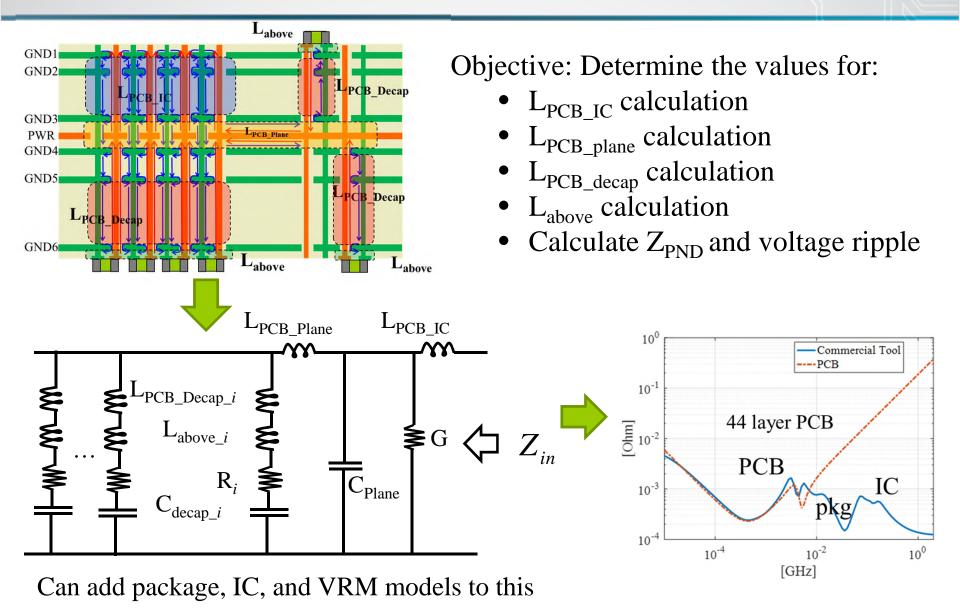

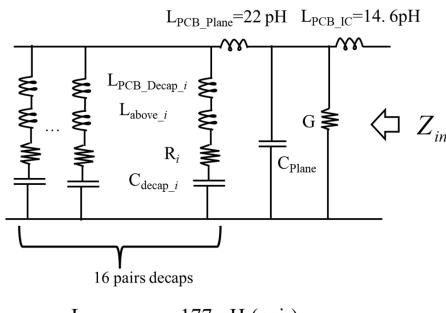

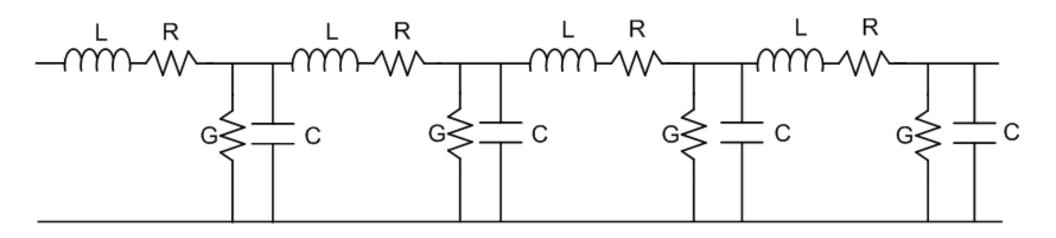

#### Circuit Model for PCB PDN

model is assembled.

Circuit reduction is used to get an impedance equivalent circuit model that coincides with the large-scale current path from IC package to decaps. Inductances are related to the current path on the geometry.

$C_{\text{decap}\_i}$

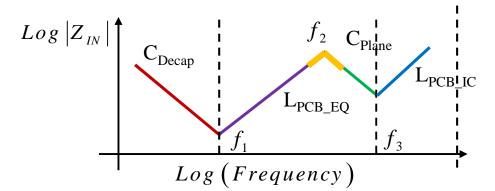

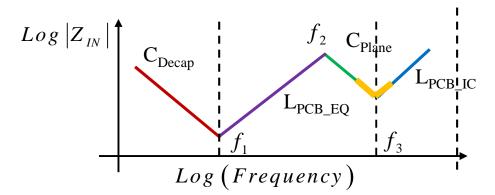

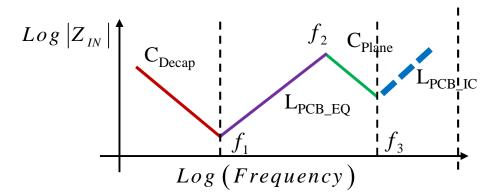

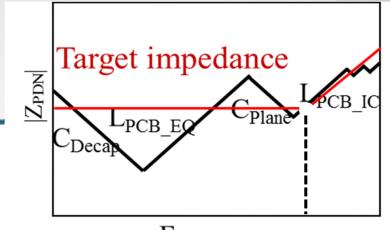

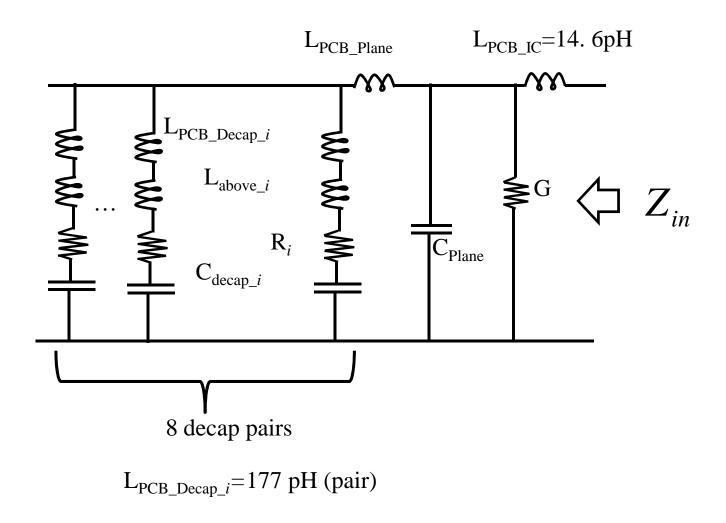

#### Impedance Equivalent Circuit

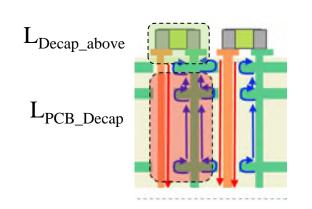

$$L_{PCB\_EQ} = L_{PCB\_Decap} + L_{PCB\_IC} + L_{PCB\_Plane} + L_{above}$$

Includes mutual inductances

#### Geometry and Impedance Equivalent Circuit

#### **Key Points**

- All current segments in all layers are modeled (often many thousands or tens of thousands) and self inductances for every segment and mutual inductance between segments are extracted using the (first principles) cavity model and a SPICE model is assembled.

- Circuit reduction can be done to produce an impedance equivalent circuit model in which the model values can be calculated. The impedance equivalent circuit model can be directly related to the geometry and current paths

## PI Module Overview Part 1 – Concepts and Physics

- The PDN problem

- Noise on the PDN and an FPGA example

- PDN design considerations

- A couple of preliminary concepts

- Current and inductance physics

- A reduced order circuit model from a first

principles formulation

- Characteristic Z<sub>PDN</sub> and relationship to physics

- Characteristic  $Z_{PDN}$  response resulting from current-path physics and associated inductance

- Relating the  $Z_{PDN}$  response to geometry and the impedance equivalent circuit model

- Z<sub>PDN</sub> frequency response related to physics

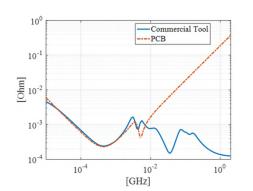

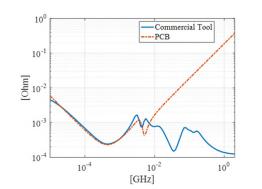

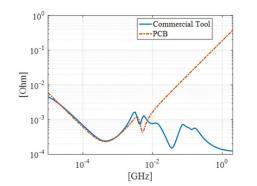

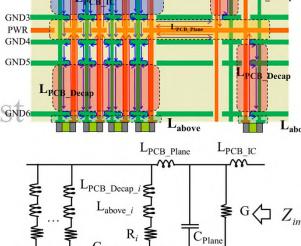

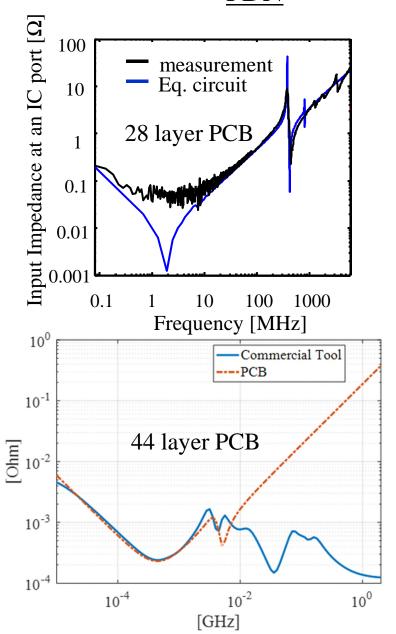

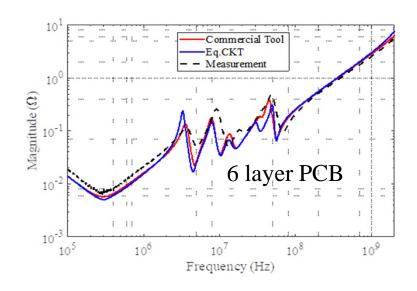

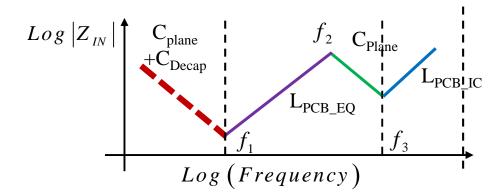

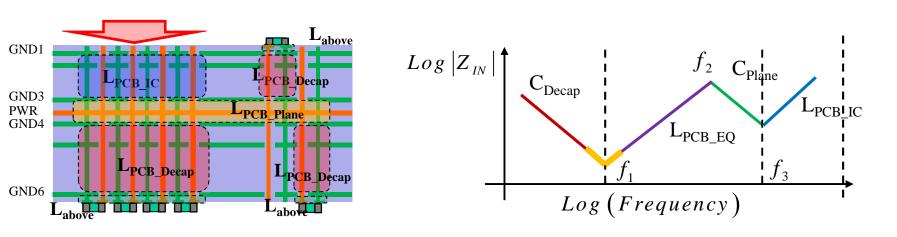

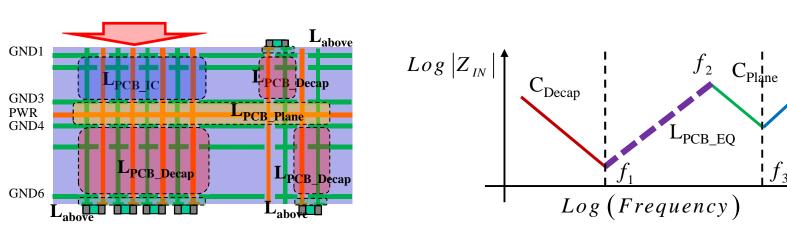

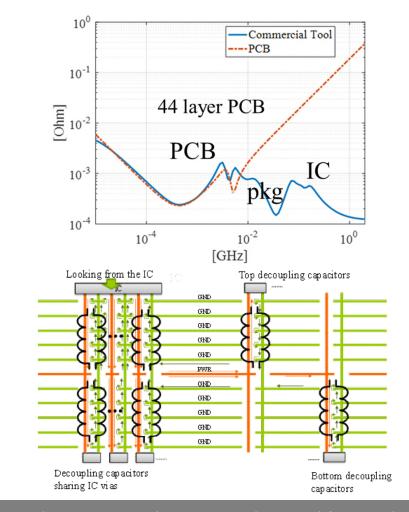

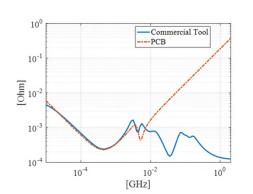

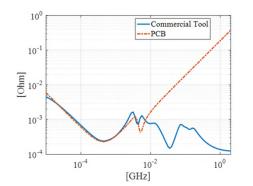

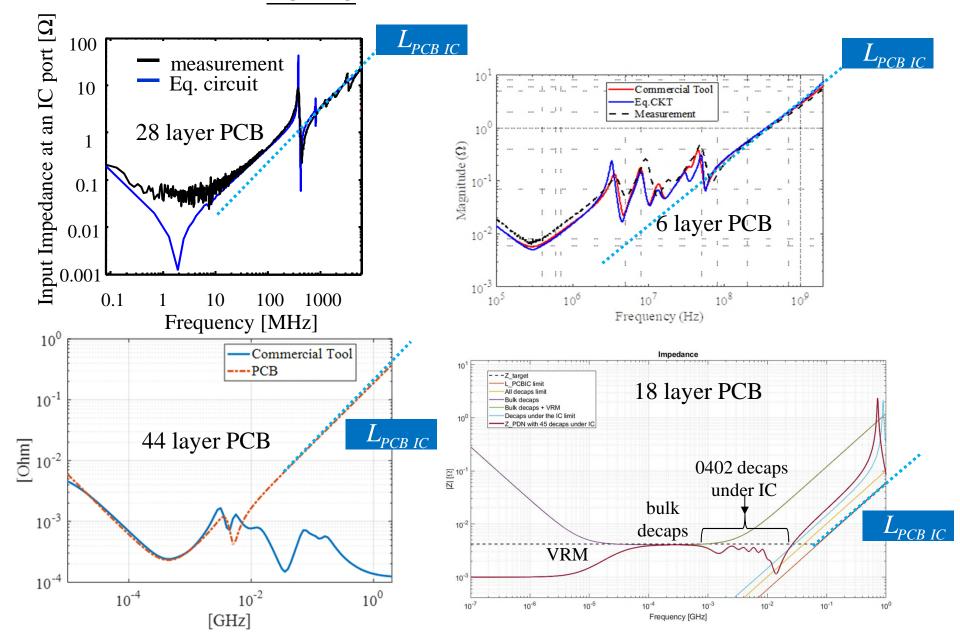

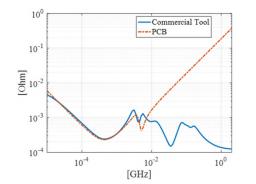

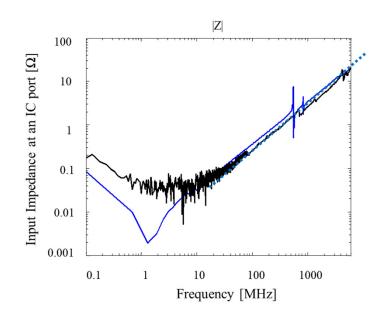

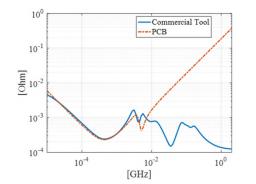

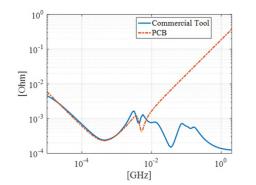

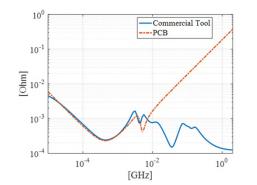

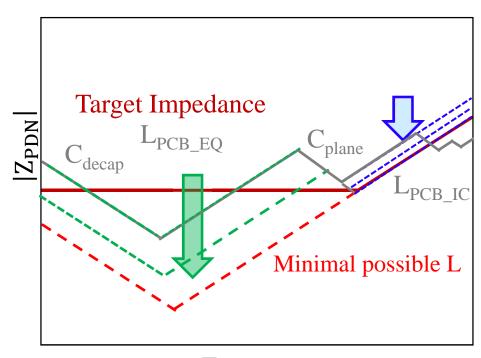

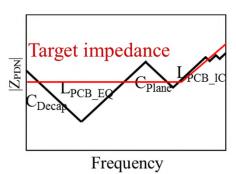

## Resulting Z<sub>PDN</sub> Response

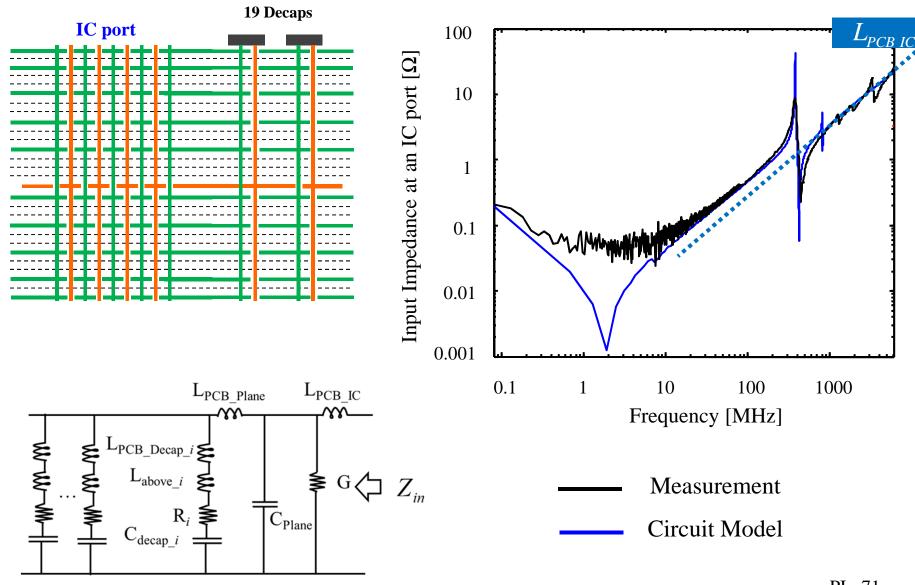

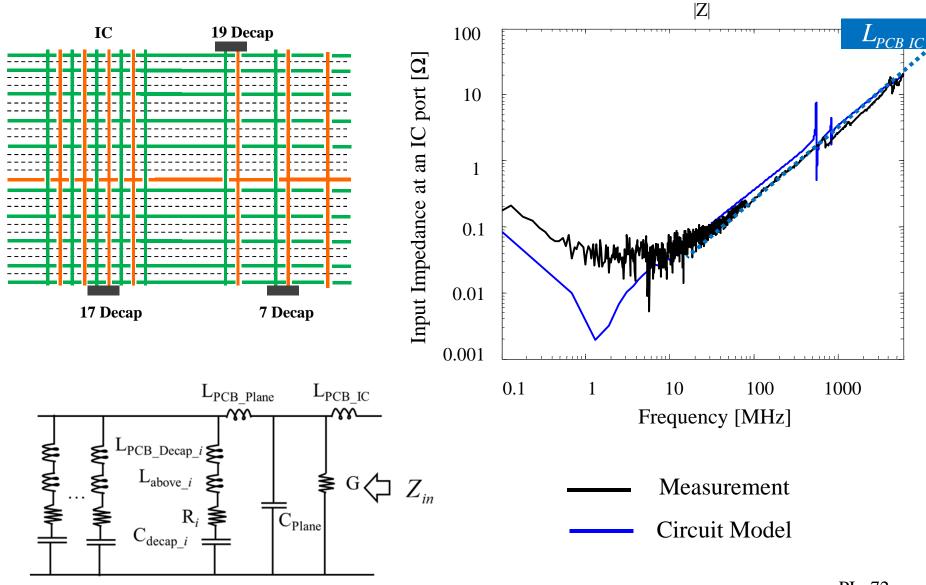

Each of these production real PCBs use only a single layer for the power net area fill (with adjacent layers for power return ground).

## Resulting Z<sub>PDN</sub> Response

$Z_{PDN}$  response is very consistent because of the current path and its associated inductance as seen from the

impedance equivalent circuit model

## Geometry, Current Path, Model, and Z<sub>PDN</sub>

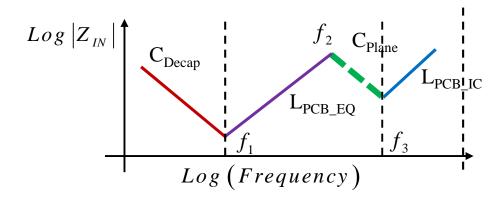

#### Frequency Response for PCB PDN - C

## Frequency Response for PCB PDN $-f_1$

# Frequency Response for PCB PDN – L<sub>PCB EQ</sub>

# Frequency Response for PCB PDN $-f_2$

# Frequency Response for PCB PDN –C<sub>Plane</sub>

# Frequency Response for PCB PDN $-f_3$

# Frequency Response for PCB PDN –L<sub>PCB IC</sub>

### **Key Points**

- The shape of the  $Z_{PDN}$  curve is very characteristic but relatively simple, even though the geometry of the PDN on a multi-layer PCB is complicated

- The current-path physics governing the impedance are dominated by inductance and lumped element resonances above approximately

1 MHz

- The inductance is dominated by the current path geometry "length/area" (series inductance), and the number of parallel paths (parallel inductance) and this will drive the design approach ("small loops and many loops")

- Where power layers are located in stackup

- Package ball pitch

- Decoupling capacitor interconnect

- Number of PWR/GND vias in package

- Number of decoupling capacitors

PI - 45

#### PI Module Overview Part 1 – Concepts and Physics

- The PDN problem

- Noise on the PDN and an FPGA example

- PDN design considerations

- A couple of preliminary concepts

- Current and inductance physics

- A reduced order circuit model from a first principles formulation

- Characteristic  $Z_{PDN}$  and relationship to physics

- Understanding PDN physics and design through examples

- Identifying limiting physics in design

- Adding decoupling capacitors

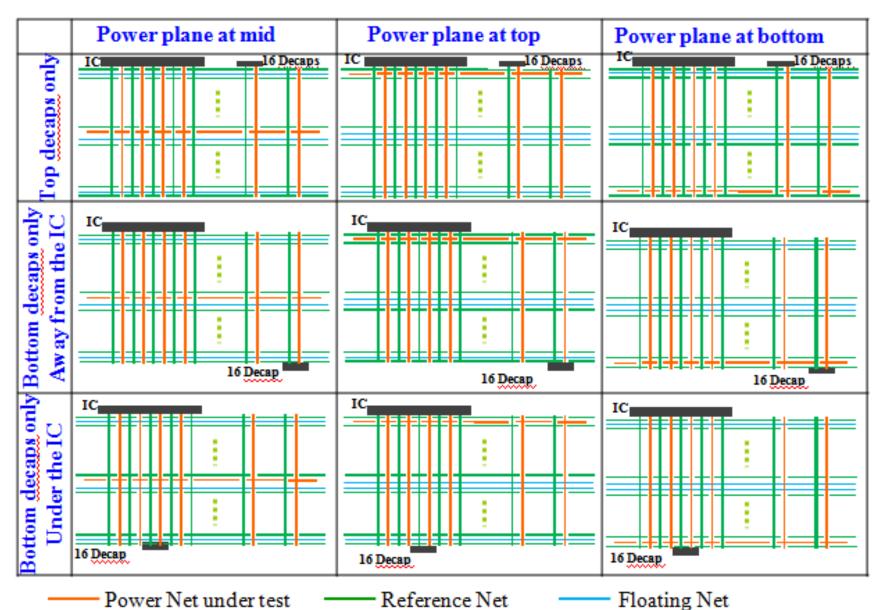

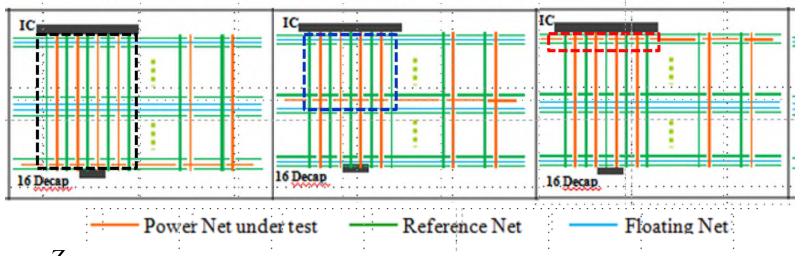

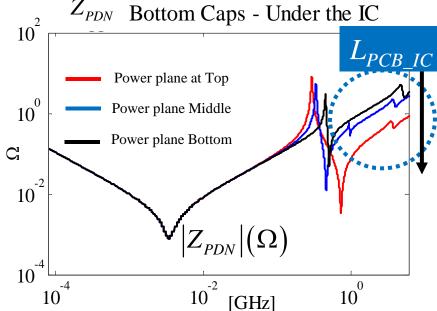

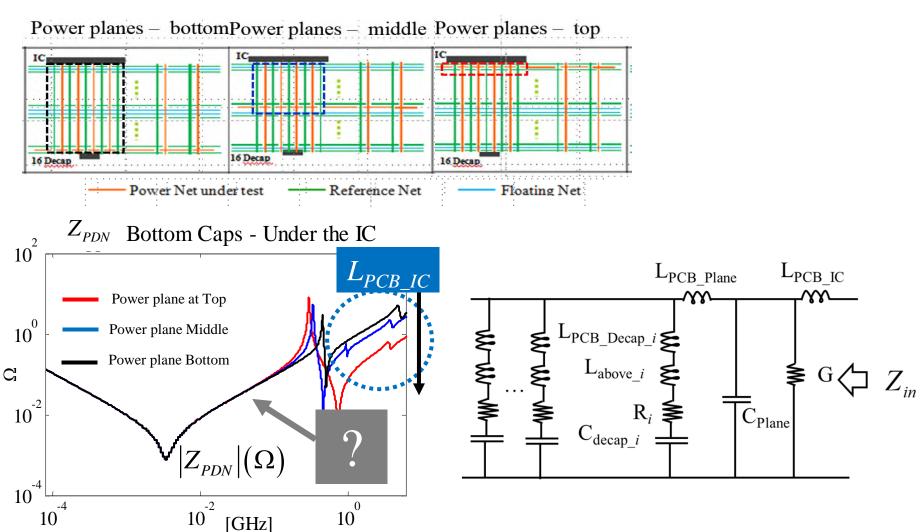

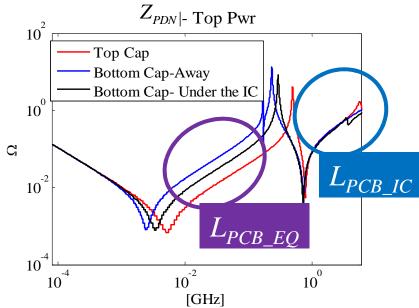

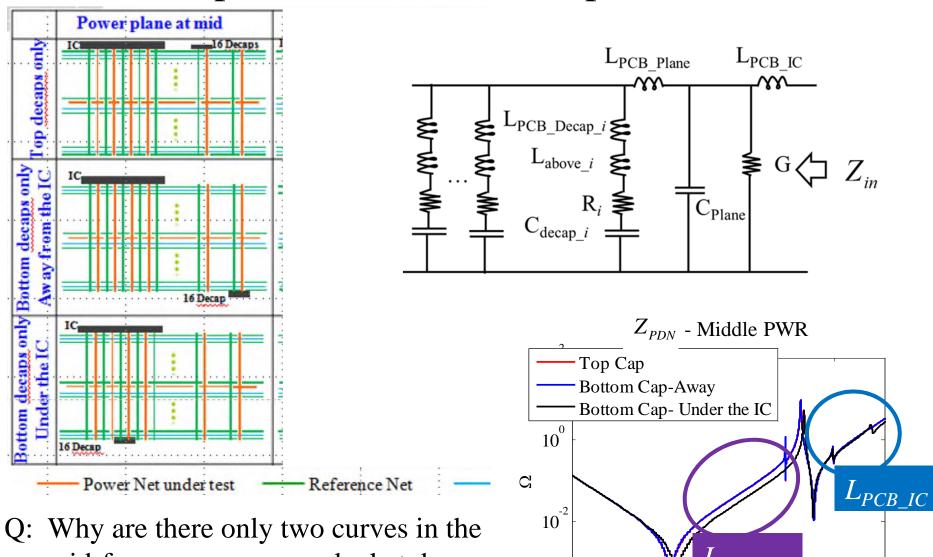

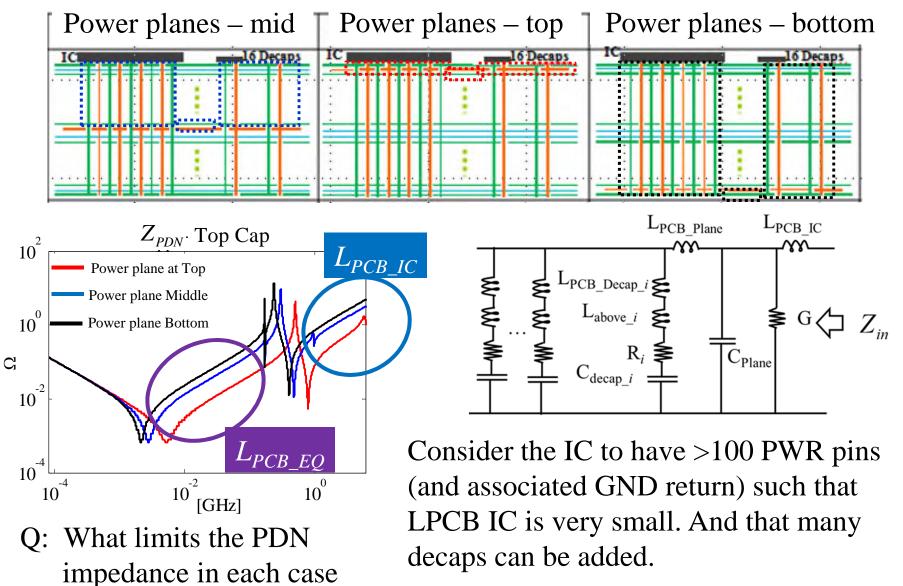

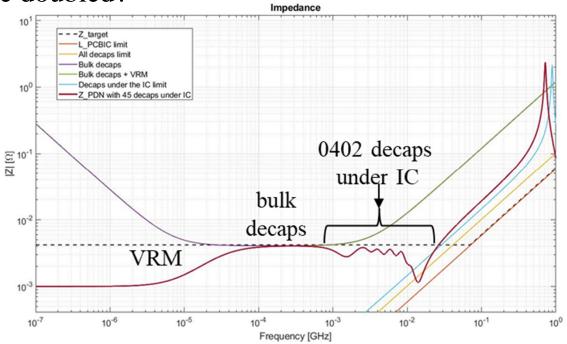

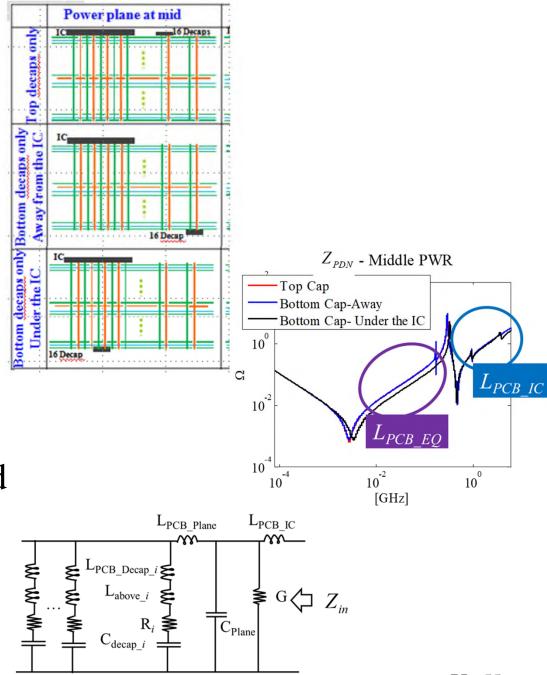

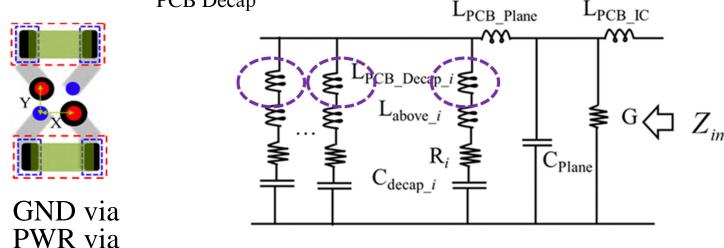

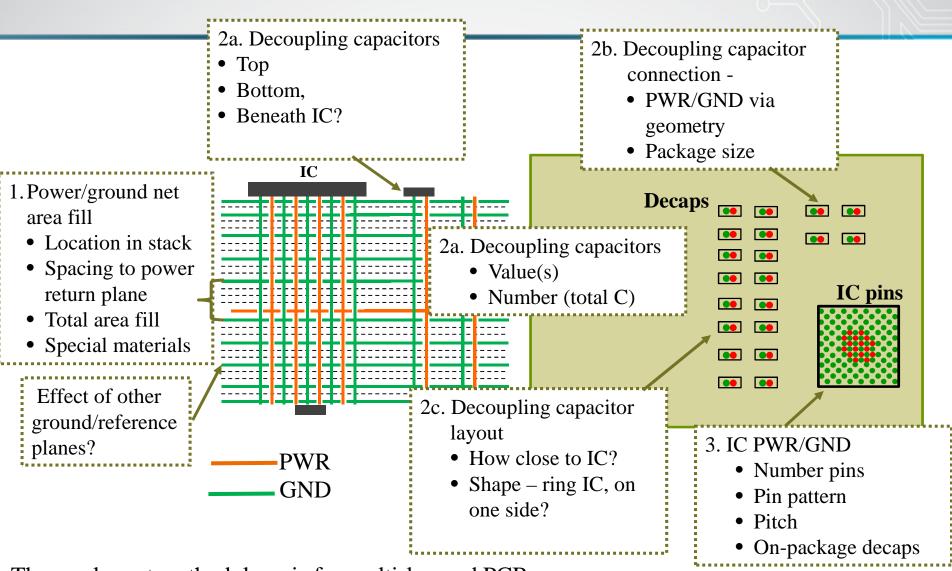

## Power Plane and Capacitor Location Matrix

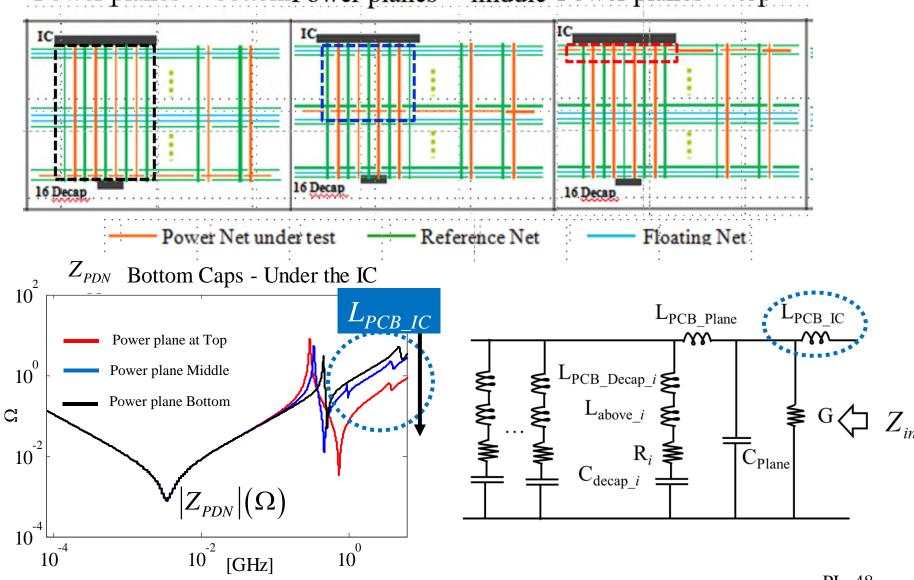

# <u>L<sub>high</sub></u> – Power Plane Location in Layer Stack

Power planes – bottomPower planes – middle Power planes – top

# <u>L<sub>high</sub></u> – Power Plane Location in Layer Stack

Power planes – bottomPower planes – middle Power planes – top

Decreasing current path and inductance from package balls to PDN power layer net

Power layer closest to the IC minimizes IC to power plane inductance. (Recall that  $j\omega L_{PCB\_IC}$  is the impedance limit above a few MHz.)

# <u>L<sub>high</sub></u> – Power Plane Location in Layer Stack

Q: How many power pins are there here?

Q: Why is the mid frequency range impedance not changing

## Capacitor Location – Top, Bottom, at IC

Capacitors placed on the side closest to the power plane reduces the inductance from the capacitor to power plane and  $L_{EQ}$ . The current path length/area is smallest.

## Capacitor Location – Top, Bottom, at IC

10<sup>-4</sup>

10

$10_{PI - 52}^{0}$

$10^{-2}$

$[GH_7]$

Q: Why are there only two curves in the mid-frequency range and what do they correspond to? Explain the differences.

## <u>L<sub>EQ</sub></u> – Power Plane Location and Decaps

above?

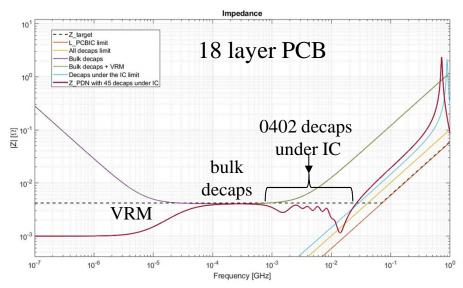

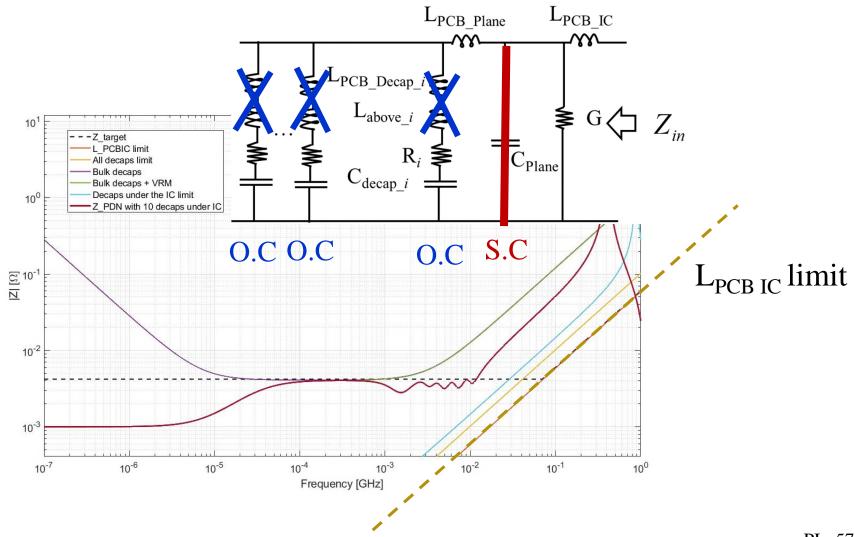

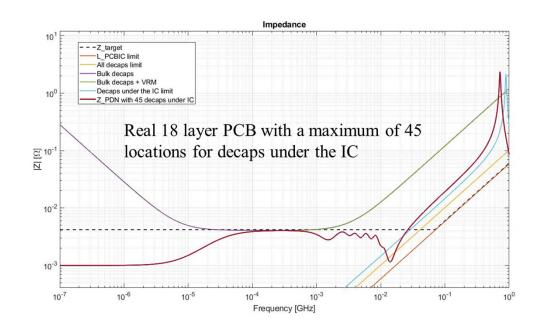

#### **Example**

- 18 layer PCB

- Layer 2 is the power layer

- 45 power pins, 109 surrounding GND

- 45 decaps under the IC

Q: What happens if the number of IC pins are doubled?

#### **Key Points**

- The Z<sub>PDN</sub> response can be related to the geometry, current path and associated inductance.

- The dominant component in the impedance equivalent circuit can be identified and used to explain the behavior of the PDN response, and to guide the PDN design.

#### PI Module Overview Part 1 – Concepts and Physics

- The PDN problem

- Noise on the PDN and an FPGA example

- PDN design considerations

- A couple of preliminary concepts

- Current and inductance physics

- A reduced order circuit model from a first principles formulation

- Characteristic  $Z_{PDN}$  and relationship to physics

- Understanding PDN physics and design through examples

- Identifying limiting physics in design

- L<sub>PCB IC</sub>

- Decaps under the IC

- All decaps

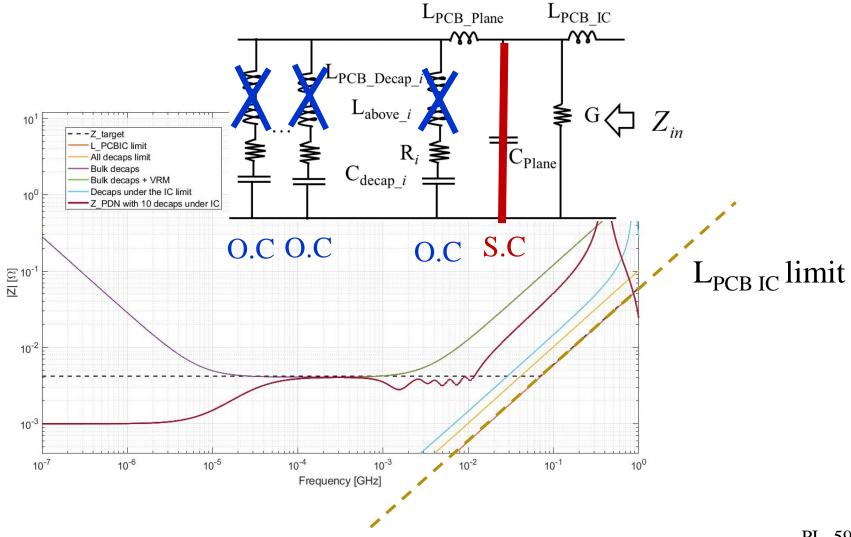

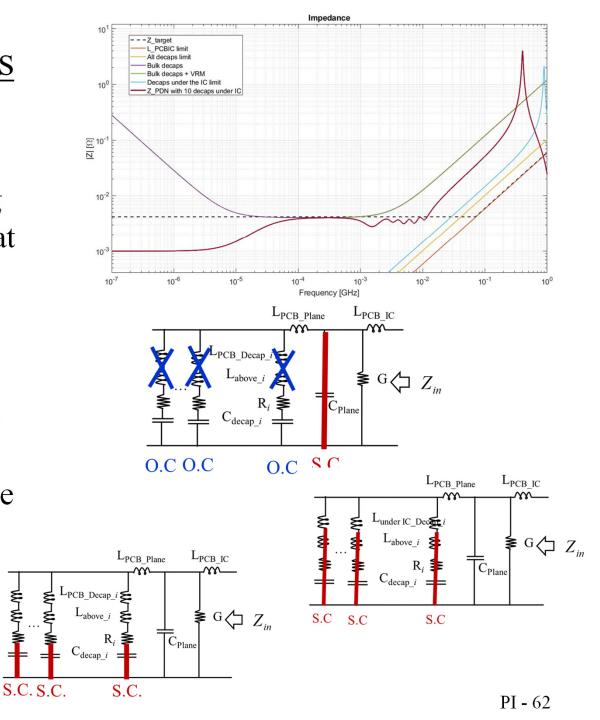

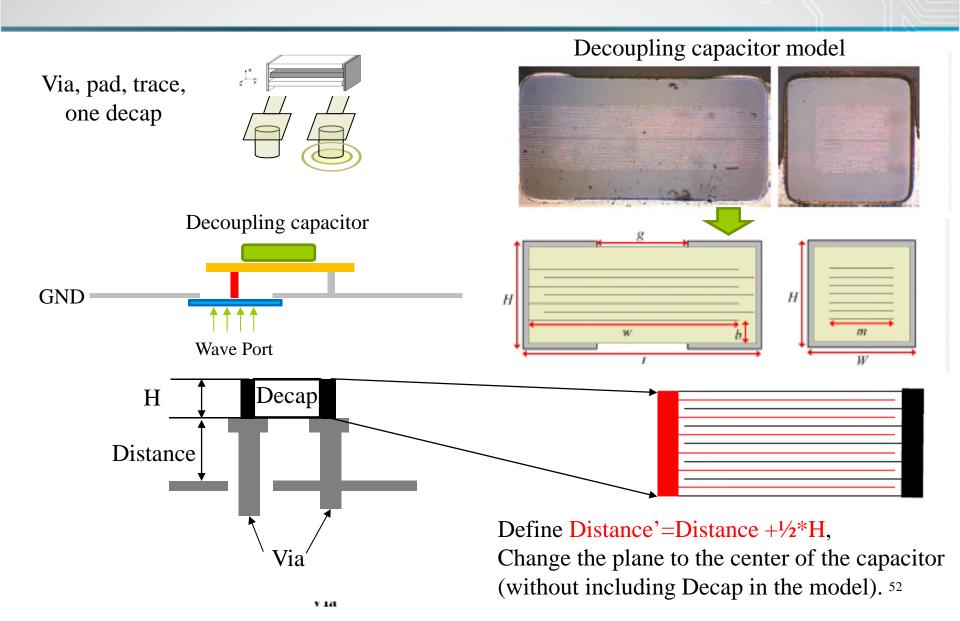

### L<sub>PCB IC</sub> Physical Limit

$L_{PCB\ IC}$  is the physical limit at high frequencies when the current returns through the interplane capacitance of the power net area fill and return

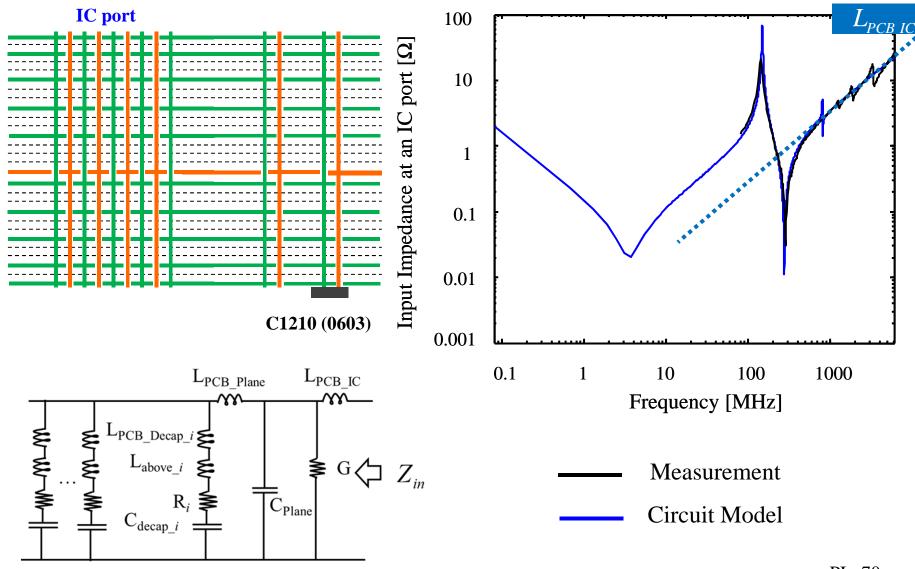

#### Real Board L<sub>PCB IC</sub> Examples

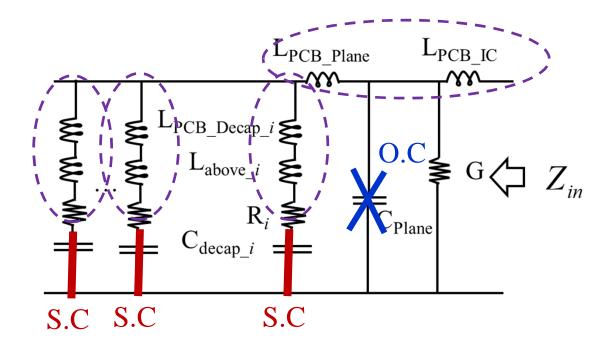

### L<sub>PCB IC</sub> Physical Limit

L<sub>PCB IC</sub> is the physical limit at high frequencies when the current returns through the interplane capacitance of the power net area fill and return

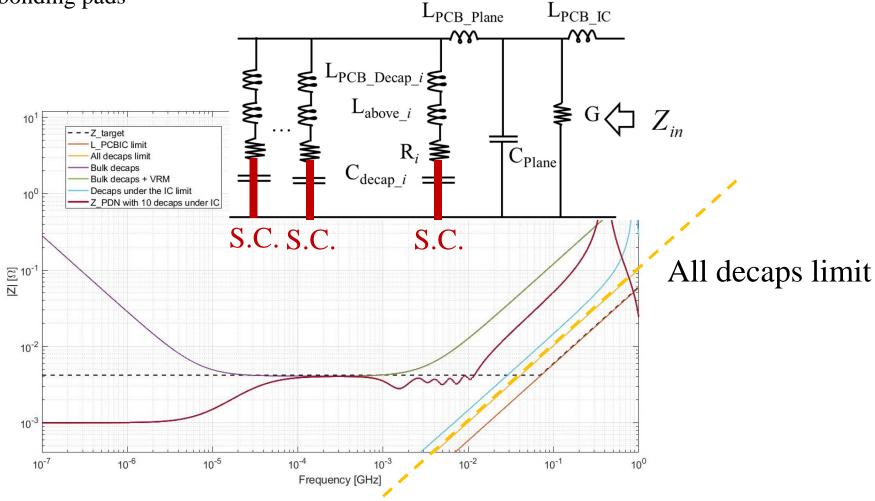

#### All Decaps Physical Limit

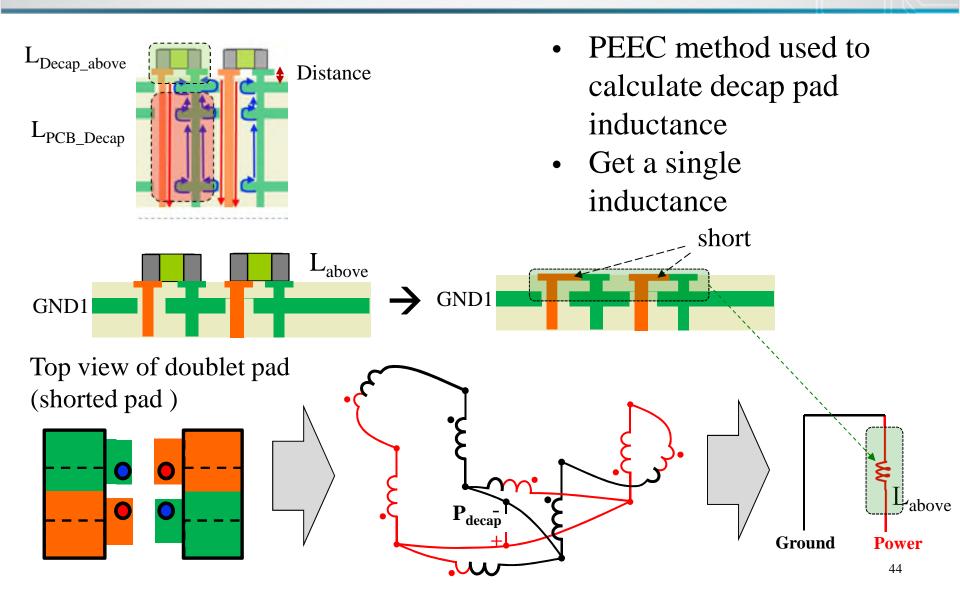

The All Decaps physical limit is when shorts are placed across all decap locations under the IC, and a ring of many capacitor locations on the top and bottom of the PCB are shorted at the bonding pads

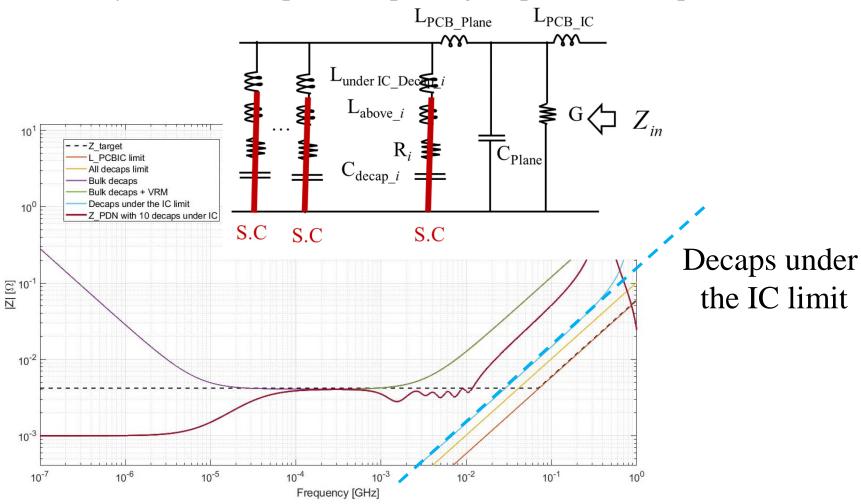

#### Decaps Under the IC Physical Limit

There is a physical limit when all the power pins under the IC are shorted on the bottom layer that corresponds to placing all possible decaps under the IC

#### **Key Points**

- Physical limits can be established for the upper bound of placing decoupling capacitors at various locations

- L<sub>PCB IC</sub>

- Decaps under the IC

- All decaps

- If the target impedance cannot be met due to a particular limitation, the nature of the limitation and the impedance equivalent circuit can guide the design direction.

#### PI Module Overview Part 1 – Concepts and Physics

- The PDN problem

- Noise on the PDN and an FPGA example

- PDN design considerations

- A couple of preliminary concepts

- Current and inductance physics

- A reduced order circuit model from a first principles formulation

- Characteristic  $Z_{PDN}$  and relationship to physics

- Understanding PDN physics and design through examples

- Identifying limiting physics in design

- Adding decoupling capacitors

- Values of decaps to use

- Where to place around the IC

- Connecting the decap to the PCB

- Convergence of  $L_{\text{PCB Decap}}$  for large number of decaps

#### Two Approaches for SMT Decoupling

- Use an <u>array</u> of capacitor values:

- This may be the best known approach in the signal integrity design community

- Rationale: to maintain a flat impedance profile below a target impedance over a wide frequency range

- Typically a logarithmically spaced (10, 22, 47, 100, 220, 470nF, etc.) array of several values per decade.

- Use a <u>large</u> capacitor value in the package size

- This is less well-known, but an approach in the EMI design community

- Rationale: to keep impedance as low as possible, less emphasis on a target impedance and a flat profile

#### <u>Decoupling Strategy – Geometry</u>

| Capacitor Description              |             |             |                           |         | # of Caps |      |      |

|------------------------------------|-------------|-------------|---------------------------|---------|-----------|------|------|

| Value<br>(nF)                      | ESR<br>(mΩ) | ESL<br>(nH) | Inter-<br>connect<br>(nH) | Туре    | A         | В    | B1   |

| 3.30E+06                           | 60          | 15          | 2                         | E-lytic | 1         | 1    | 1    |

| 100000                             | 11          | 1.4         | 2                         | 1812    | 4         | 16   | 16   |

| 47000                              | 12          | 1.4         | 2                         | 1812    | 4         |      |      |

| 22000                              | 14          | 1.4         | 2                         | 1812    | 4         |      |      |

| 10000                              | 16          | 1.4         | 2                         | 1812    | 4         |      |      |

| 4700                               | 16          | 0.5         | 1.6                       | 0603    | 4         | 24   |      |

| 2200                               | 19          | 0.5         | 1.6                       | 0603    | 4         |      |      |

| 1000                               | 23          | 0.5         | 1.6                       | 0603    | 4         |      |      |

| 470                                | 29          | 0.5         | 1.6                       | 0603    | 4         |      |      |

| 220                                | 23          | 0.5         | 1.6                       | 0603    | 4         |      |      |

| 100                                | 30          | 0.5         | 1.6                       | 0603    | 4         |      |      |

| 47                                 | 40          | 0.4         | 1.35                      | 0402    | 4         | 20   | 44   |

| 22                                 | 55          | 0.4         | 1.35                      | 0402    | 4         |      |      |

| 10                                 | 75          | 0.4         | 1.35                      | 0402    | 4         |      |      |

| 4.7                                | 104         | 0.4         | 1.35                      | 0402    | 4         |      |      |

| 2.2                                | 211         | 0.4         | 1.35                      | 0402    | 4         |      |      |

| Total # of Decoupling Capacitors = |             |             |                           |         | 61        | 61   | 6    |

| Total Capacitance (milliF) =       |             |             |                           |         | 4.05      | 5.01 | 4.90 |

t=10 mils. tan  $\delta = 0.02$  $\epsilon_r$ =4.5

#### Approaches for SMT Decoupling Values

- Approach A: values of decoupling capacitors logarithmically spaced, i.e. 3 values per decade: 10, 22, 47, 100, etc.

- Approach B: largest values of decoupling available in two package sizes, i.e., 0603 and 0402

- Approach B1: largest values of decoupling available in one package size, i.e., 0402.

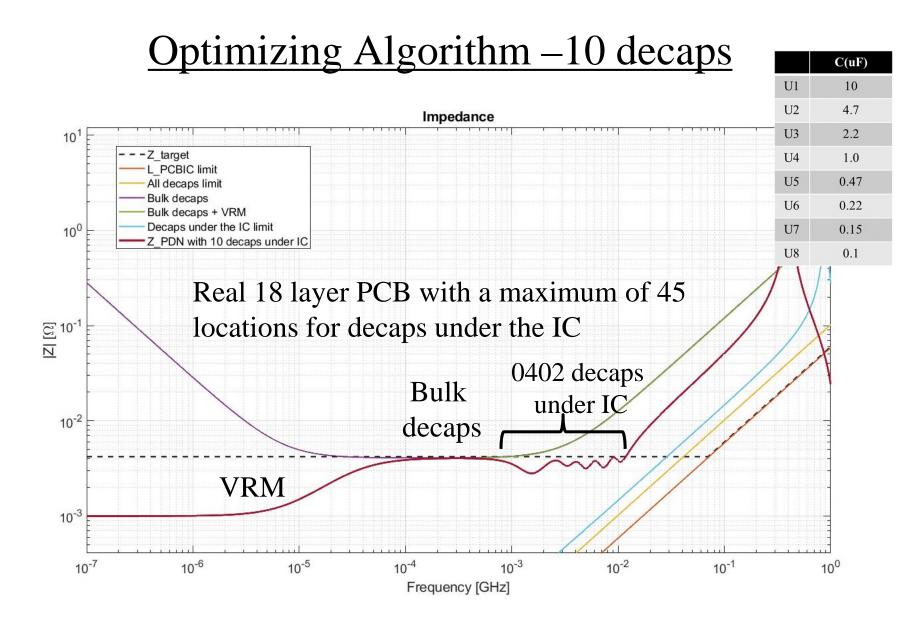

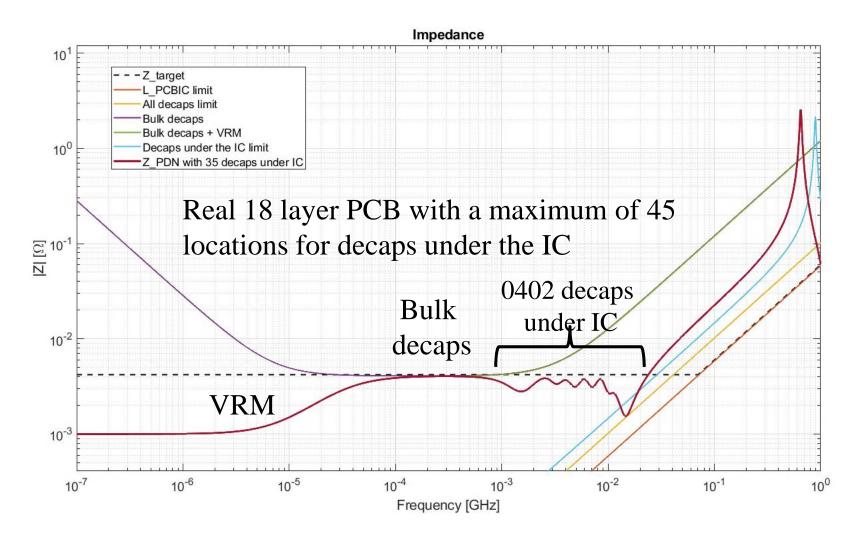

#### Optimizing Algorithm –35 decaps

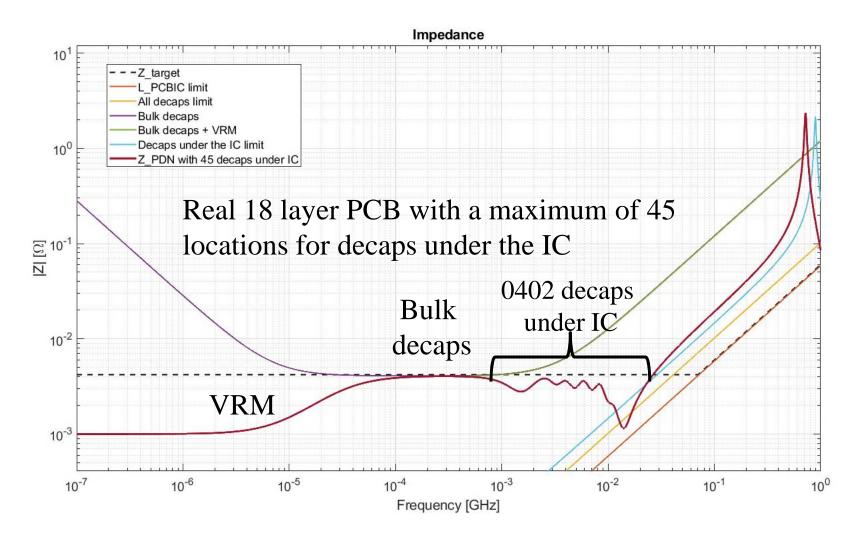

#### Optimizing Algorithm –45 decaps

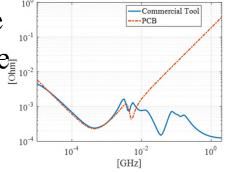

#### 28 Layer Real PCB Design: 1 Capacitor

### 28 Layer Real PCB Design: 19 Capacitors

#### 28 Layer Real PCB Design: 43 Capacitors

#### **Key Points**

- Decoupling capacitors can be added using several values in a given decade to decouple over wide frequency ranges

- Decoupling capacitors can be added as the largest value in a package size to achieve a target impedance as well.

#### PI Module Overview Part 1 – Concepts and Physics

- The PDN problem

- Noise on the PDN and an FPGA example

- PDN design considerations

- A couple of preliminary concepts

- Current and inductance physics

- A reduced order circuit model from a first principles formulation

- Characteristic  $Z_{PDN}$  and relationship to physics

- Understanding PDN physics and design through examples

- Identifying limiting physics in design

- Adding decoupling capacitors

- Values of decaps to use

- Where to place around the IC

- Connecting the decap to the PCB

- Convergence of  $L_{\text{PCB Decap}}$  for large number of decaps

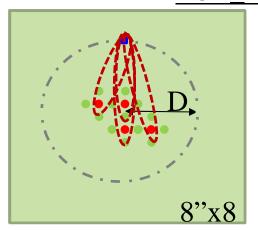

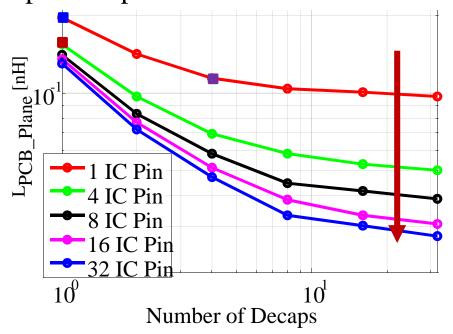

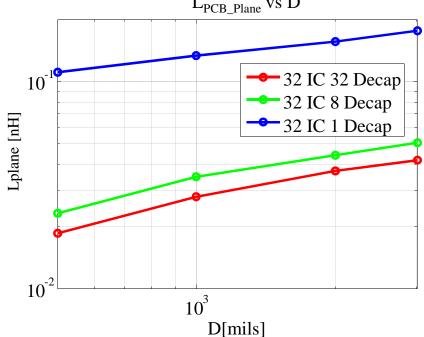

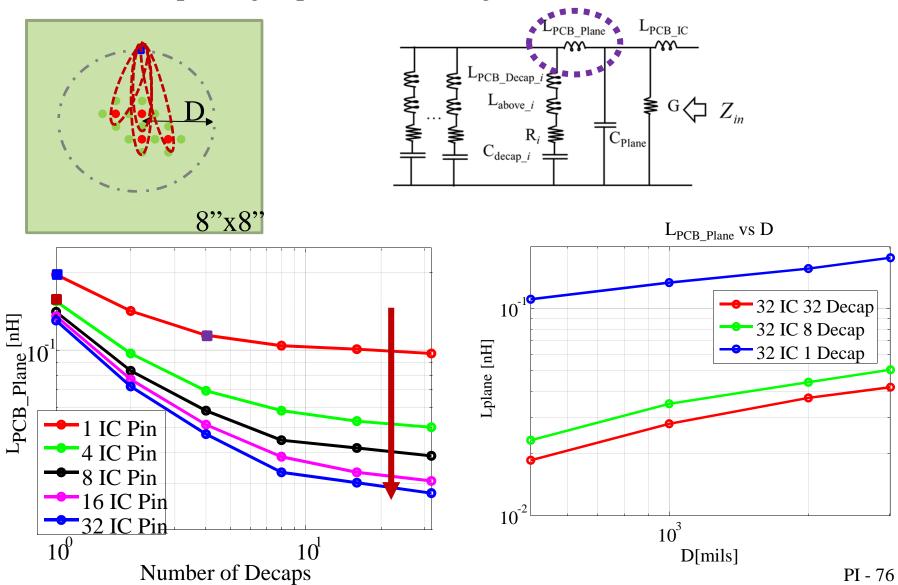

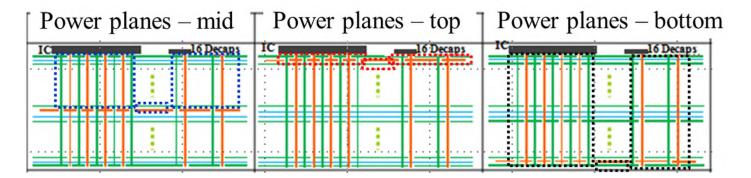

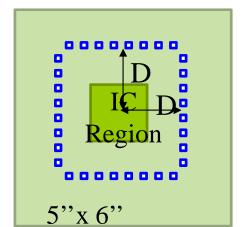

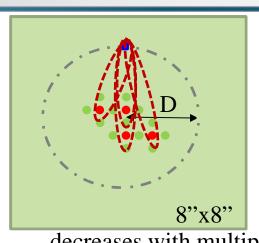

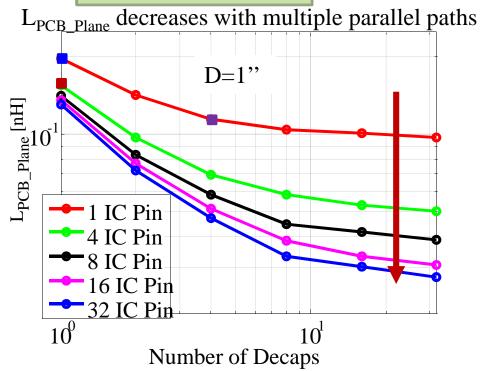

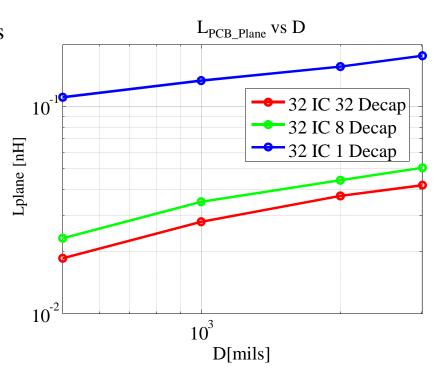

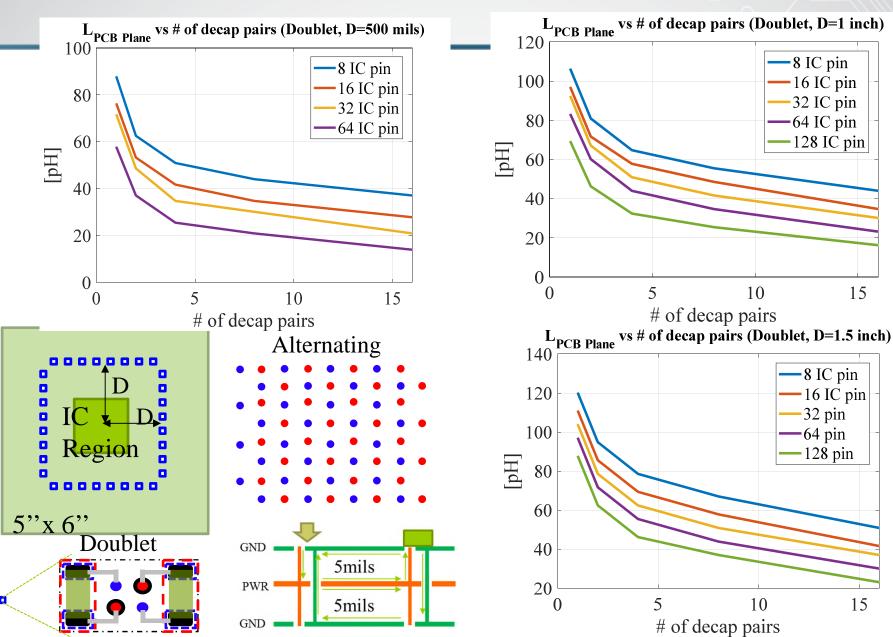

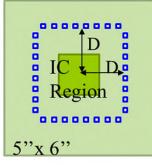

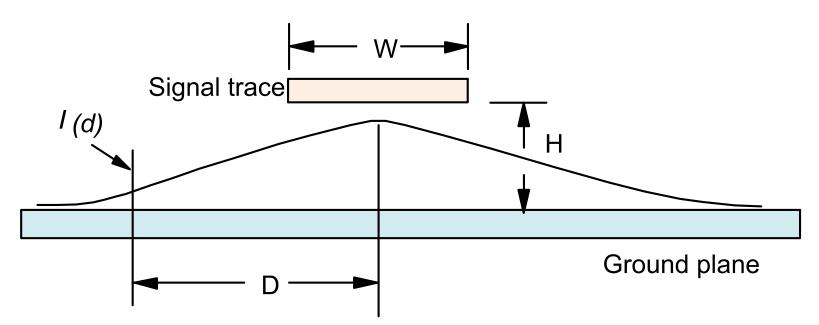

## <u>L<sub>PCB\_Plane</sub></u> Current Physics and Inductance

D=1", Pitch = 1mm

$L_{PCB\_Plane}$  decreases with multiple parallel paths

PI - 75

## <u>L<sub>PCB\_Plane</sub></u> Current Physics and Inductance

Q: When is placing capacitors in a ring around the IC most beneficial?

Current Path, and Inductance

Q: If the current path from IC to the decaps is not in direct line (e.g., crosses a cutout or slot, goes around a corners, etc.), which portion of the inductance is affected, and can potentially become dominant?

PI - 77

#### **Key Points**

- If  $L_{PCB\ Plane}$  is dominant, e.g., when the power net area fill is near the top, and the decaps are placed on the top layer, then placing the capacitors in a ring around the IC can minimize  $L_{PCB\ Plane}$

- In general, L<sub>PCB Plane</sub> is typically not the limiting factor, and decaps are often limited to "keep-in" regions where signal routing channels are not compromised.

#### PI Module Overview Part 1 – Concepts and Physics

- The PDN problem

- Noise on the PDN and an FPGA example

- PDN design considerations

- A couple of preliminary concepts

- Current and inductance physics

- A reduced order circuit model from a first principles formulation

- Characteristic  $Z_{PDN}$  and relationship to physics

- Understanding PDN physics and design through examples

- Identifying limiting physics in design

- Adding decoupling capacitors

- Values of decaps to use

- Where to place around the IC

- Connecting the decap to the PCB

- Convergence of  $L_{\text{PCB Decap}}$  for large number of decaps

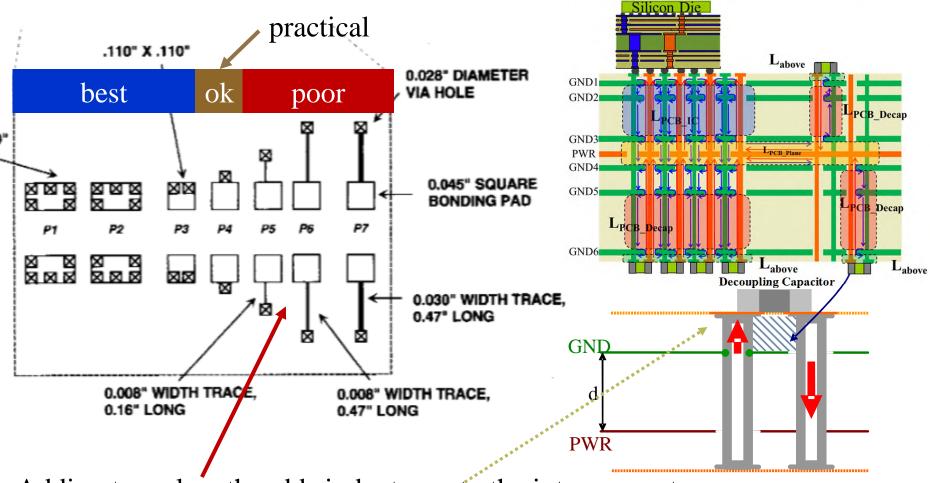

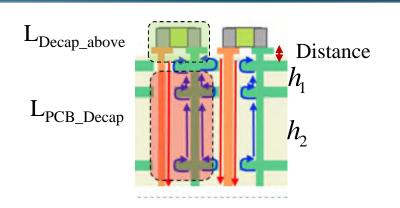

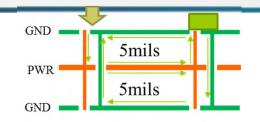

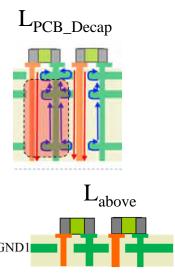

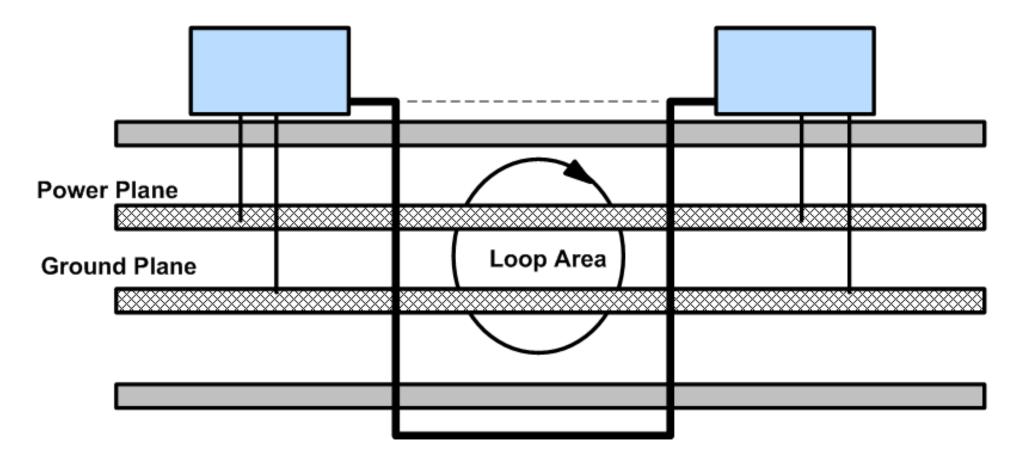

#### Practices for Mounting SMT Capacitors

Adding trace length, adds inductance to the interconnect:

- "loop area" above the planes—L<sub>above</sub>

- Area between the power and GND return vias vertically connecting to the PWR planes

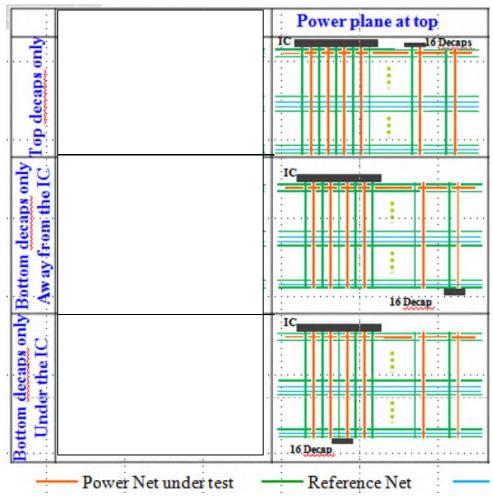

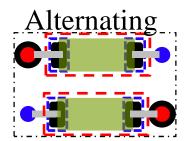

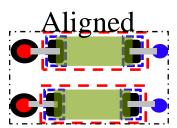

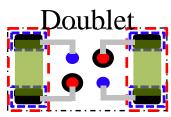

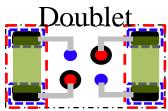

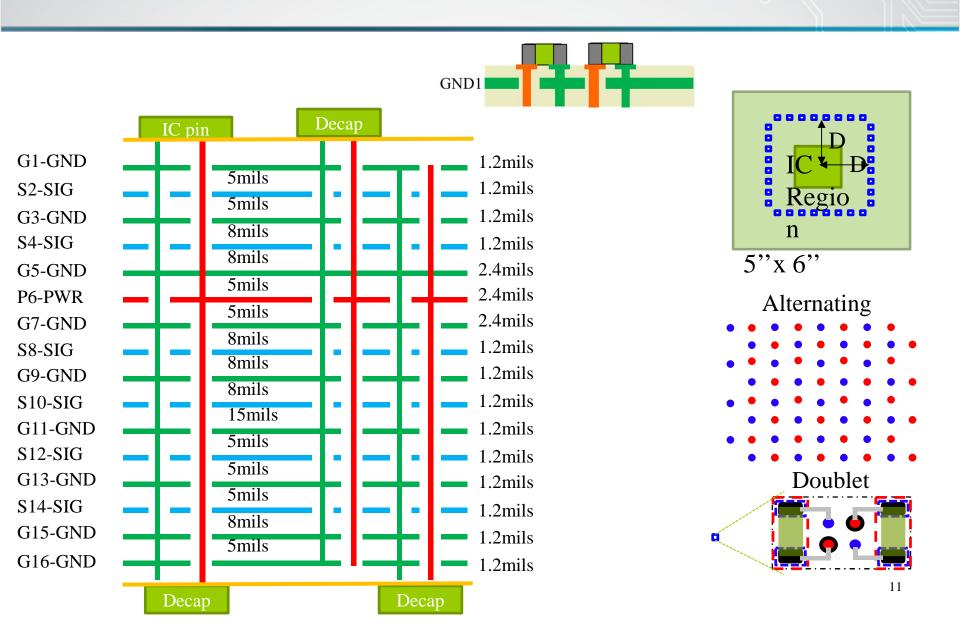

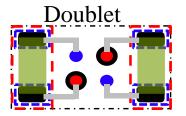

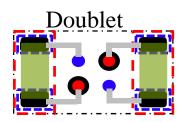

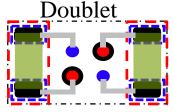

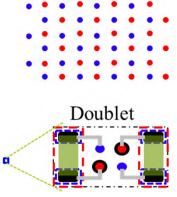

## Example 1: The Doublet – Minimizing L<sub>PCB Decap</sub>

Placing decaps on in pairs allows to use mutual inductance to minimize overall  $L_{PCR\ Decan}$

Q: If  $L_{PCB\ IC}$  is negligible, in which cases can the doublet configuration be beneficial? Which cases less so.

## Example 2: The Doublet – Minimizing L<sub>PCB Decap</sub>

Placing decaps on in pairs allows to use mutual inductance to minimize overall  $L_{PCR\ Decan}$

Decap Decap Decap Decap Power Net under test Reference Net Floating Net

Q: If  $L_{PCB\ IC}$  is negligible, and decaps can be placed under the IC, in which cases can the doublet configuration be beneficial? Which cases less so.

Q: Which of these cases is not well chosen for the decap location?

#### PI Module Overview Part 1 – Concepts and Physics

- The PDN problem

- Noise on the PDN and an FPGA example

- PDN design considerations

- A couple of preliminary concepts

- Current and inductance physics

- A reduced order circuit model from a first principles formulation

- Characteristic  $Z_{PDN}$  and relationship to physics

- Understanding PDN physics and design through examples

- Identifying limiting physics in design

- Adding decoupling capacitors

- Values of decaps to use

- Where to place around the IC

- Connecting the decap to the PCB

- Convergence of LPCB Decap for large number of decaps

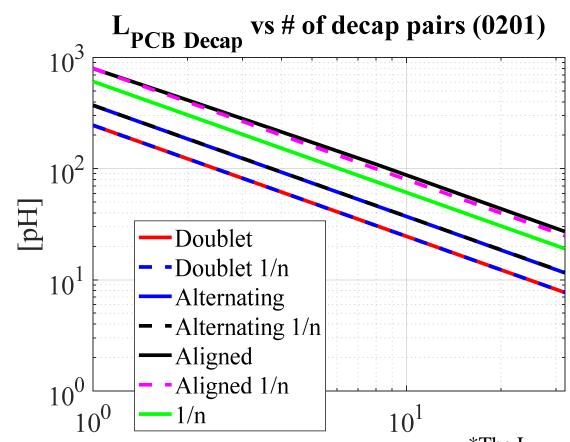

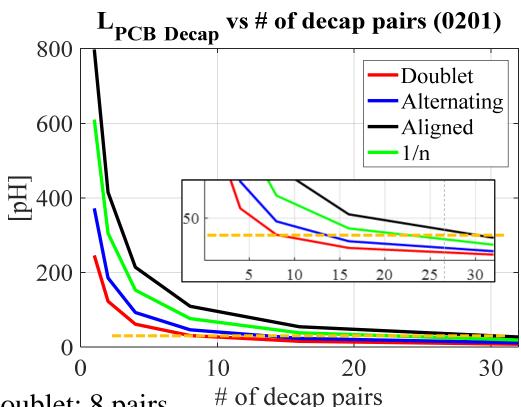

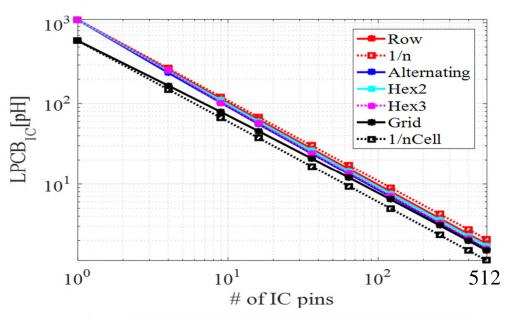

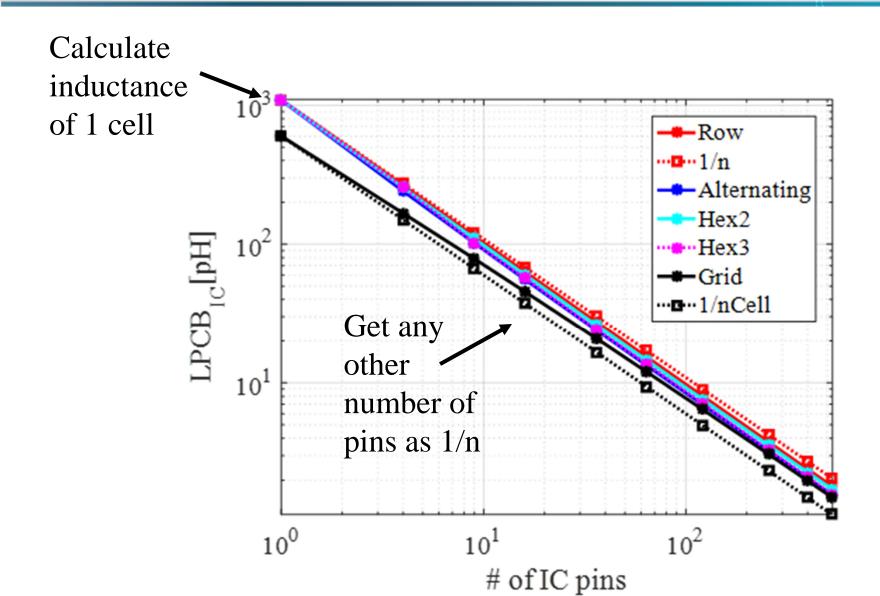

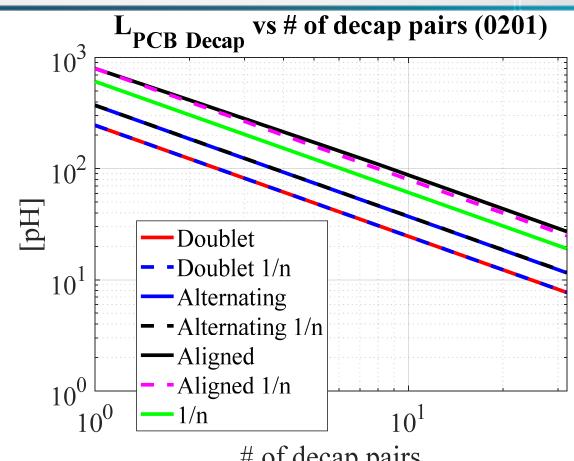

## <u>L<sub>PCB\_Decap</sub></u> Convergence

# of decap pairs

$\frac{1}{n_{pair}}$  convergence rate for all SMT package sizes

\*The  $L_{PCB\_Decap}$  is simulated in PDN Tool and the inductance is extracted from  $|Z_{PDN}|$ .

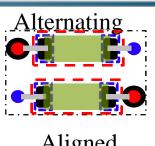

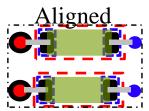

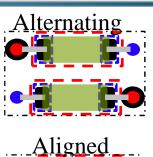

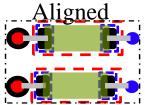

## <u>L<sub>PCB\_Decap</sub></u> Capacitor Configuration Example

- Doublet: 8 pairs

- Alternating: 14 pairs

- 1/n: 25 pairs (no mutual coupling between individual decaps)

- Aligned: 30 pairs

#### **Key Points**

- Adding capacitors

decreases L<sub>PCB Decap</sub> as

1/n

- Geometries such as the Doublet or 3-terminal capacitors reduce inductance over geometries where there is no benefit of mutual inductance.

#### **Design Implications**

- Use the impedance equivalent circuit model to try to identify what component is dominant and use it to guide meeting the target impedance.

- PWR/GND plane pair nearer to the IC in stackup will minimize  $L_{PCB\_IC}$  from package balls to power net area fill (smaller loop)

- PWR/GND plane pairs closely spaced will reduce L<sub>PCB\_plane</sub>.

- Place caps close to the power layer to minimize the inductance from the capacitor to the power net area fill layer, i.e.,  $L_{PCB\ decaps}$ . (minimize the loop)

- Placing caps on the underside of PCB opposite package can benefit the design

- The space is available and requires no additional vias

- If the pkg/planes/decap path is shorter due to PWR/GND near package in stackup decaps around the IC will be more effective

- Power and ground vias placed adjacent to the caps reduces the inductance in the current return path (or in the bonding pads). (smaller loops)

- Capacitor arrangements that utilize mutual inductance, e.g., doublet, or 3-terminal capacitor, can significantly reduce  $L_{PCB\ decaps}$ .

# Thank you!

# Power Integrity for High-Speed Design on Multi-Layer PCBs

Concepts and Physics

James L. Drewniak

Clear Signal Solutions and

Missouri S&T EMC Laboratory

james.drewniak@clearsig.com

#### Contributors

- IBM B. Archambeault, S. Connor, M. Cocchini, W. Becker, M. Cracraft, A. Ruehli

- Cisco B. Achkir, S. Scearce, Q. Gaumer, M. Sapazhnikov

- Missouri S&T B. Zhao, S. Bai, S. Liang, X. Zhu, K. Shringapure, S. Pan, J. Xu, J. Fan

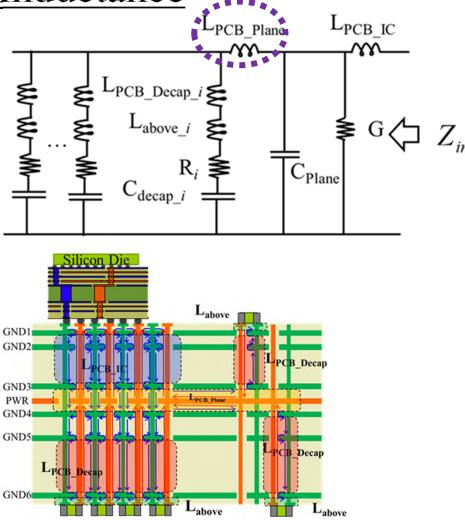

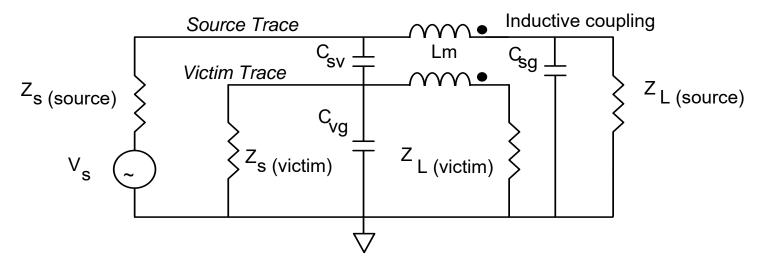

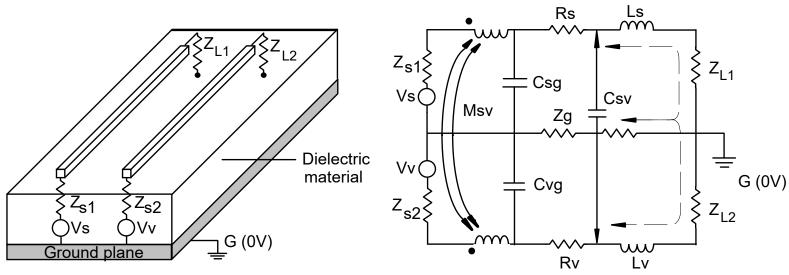

#### Overview – Pre-layout Methodology

Problem and concepts

PDN pre-layout design methodology

Circuit model

Example

#### **Problem Introduction**

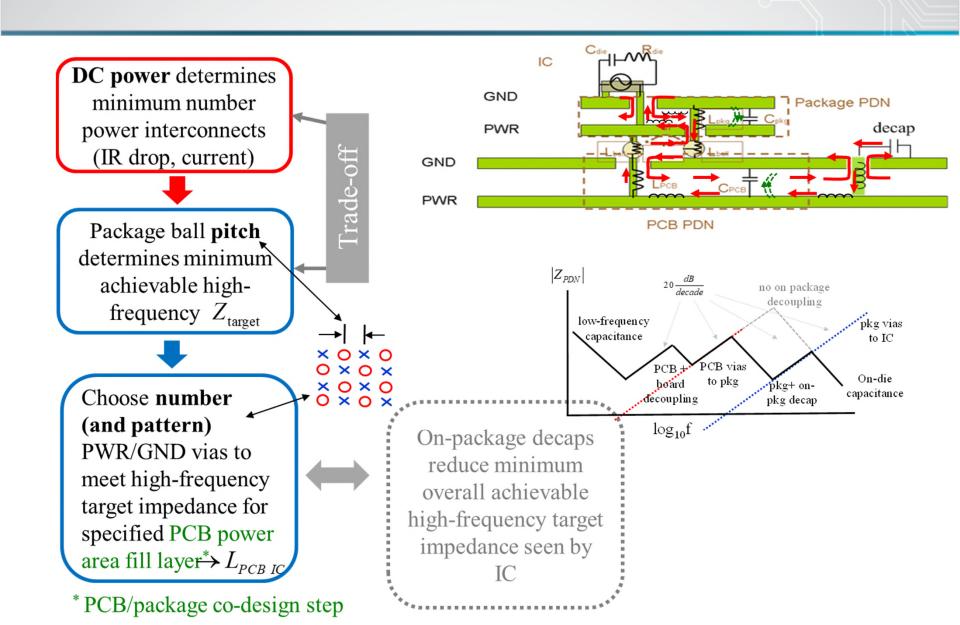

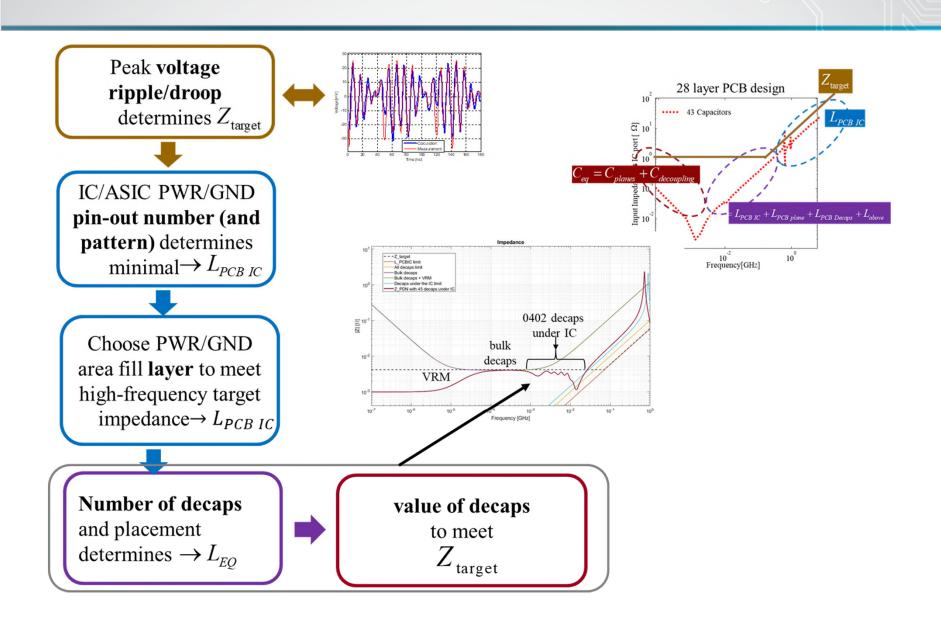

#### A Systematic Approach for Achieving PI

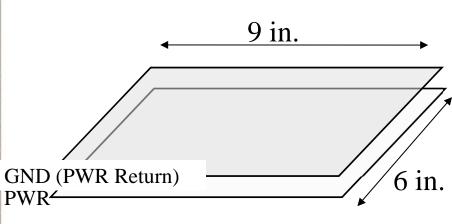

#### PDN Design Considerations

The pre-layout methodology is for multi-layered PCB PDN geometry.

#### PI Design Flow – Package

#### Design Flow – PCB

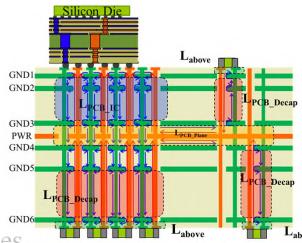

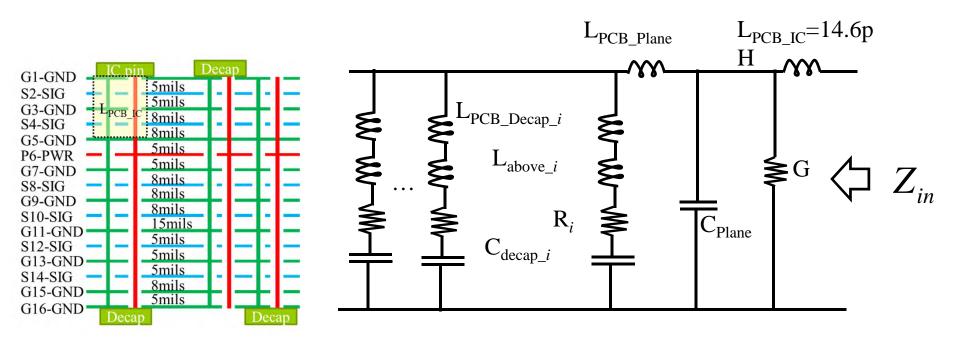

#### Objective: PCB Impedance Equivalent Circuit

#### Overview – Pre-layout Methodology

Problem and concepts

- PDN pre-layout design methodology

- Example geometry

- L<sub>PCB IC</sub> calculation

- L<sub>PCB\_decap</sub> calculation

- L<sub>PCB\_plane</sub> calculation

- L<sub>above</sub> calculation

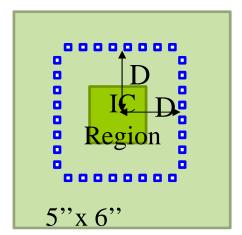

#### PCB PDN Example - Geometry

### Overview – Pre-layout Methodology

Problem and concepts

- PDN pre-layout design methodology

- Example geometry

- $L_{PCB\_IC}$  calculation

- L<sub>PCB\_decap</sub> calculation

- L<sub>PCB\_plane</sub> calculation

- L<sub>above</sub> calculation

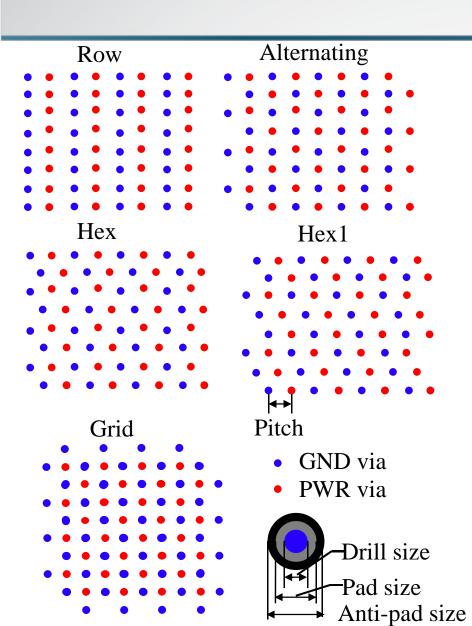

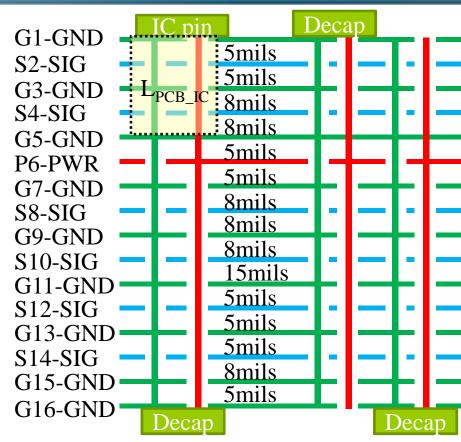

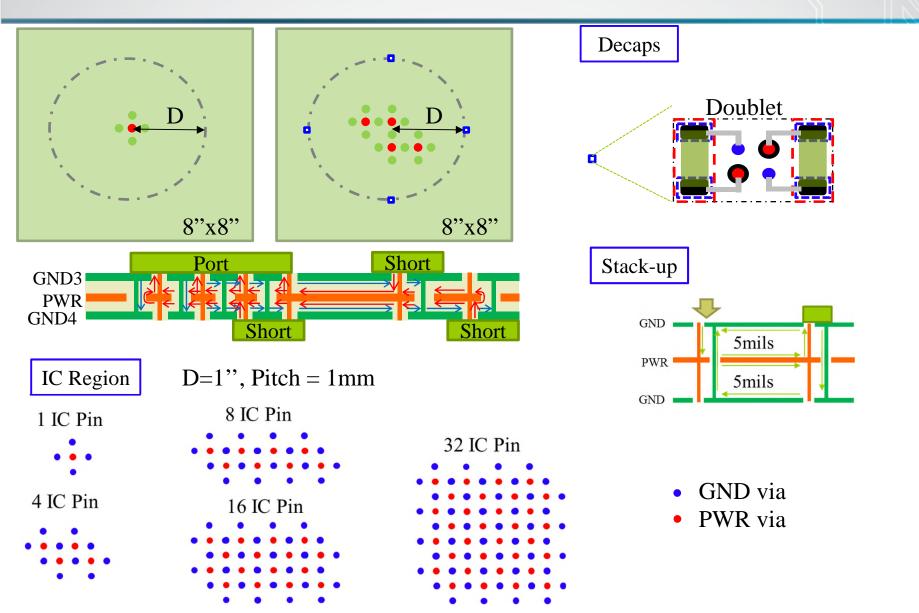

# L<sub>PCB\_IC</sub> Geometry

| Pitch  | Drill size | Anti-pad size |

|--------|------------|---------------|

| 1 mm   | 8mils      | 20mils        |

|        | 12mils     | 32mils        |

|        | 15mils     | 39mils        |

| 0.8 mm | 8mils      | 20mils        |

|        | 12mils     | 20mils        |

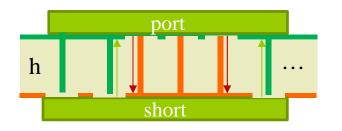

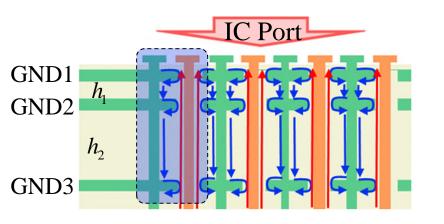

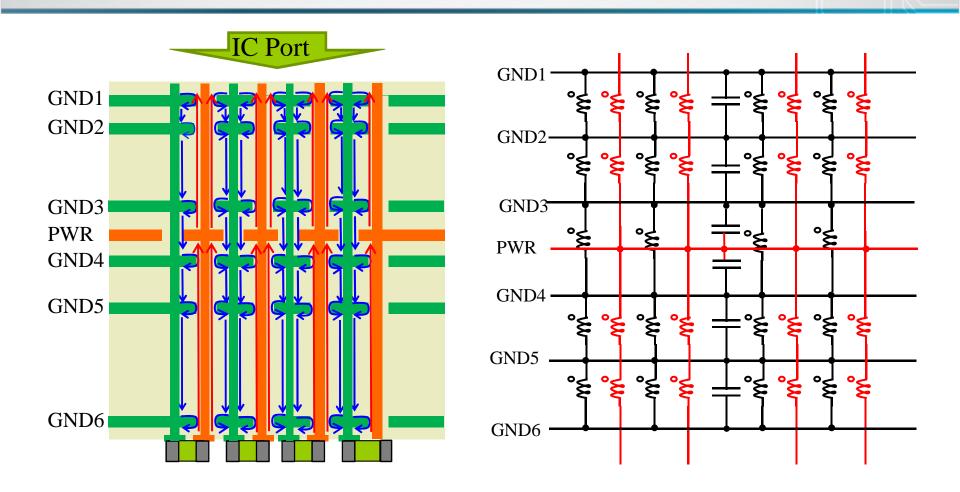

### $L_{PCB\ IC}$ Inductance Physics – goes as h

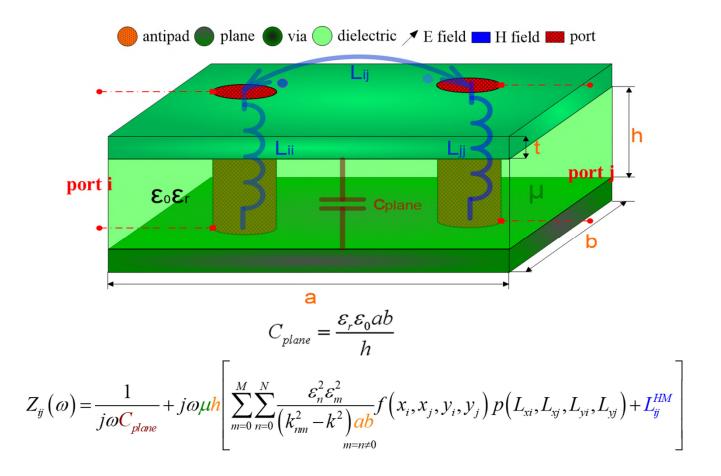

#### Cavity Model

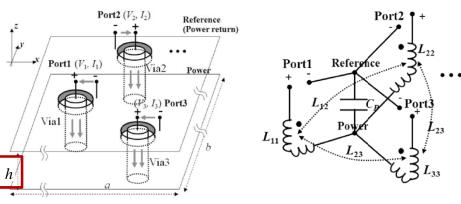

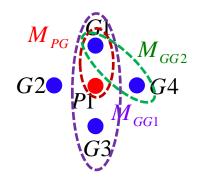

$$L_{ij} = \frac{\mu h}{ab} \sum_{m=0} \sum_{n=0}^{\infty} \frac{\varepsilon_{m}^{2} \varepsilon_{n}^{2}}{k_{mn}^{2}} f(x_{i}, y_{i}, x_{j}, y_{j}) \Big|_{(m,n) \neq (0,0)}$$

$$h = h_1 + h_2$$

$$L_{PCB\_IC\_grid} = h! \frac{L_{self\_PUL,1unitcell}}{n_{ICpin}} + L_{Mutual,unitcell\_PUL})$$

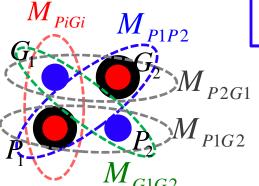

$$L_{\textit{self}\_\textit{PUL},\textit{lunitcell}} = L_{\textit{self},\textit{PWR}} + \frac{L_{\textit{self},\textit{GND}}}{4} - 2M_{\textit{PG}} + \frac{M_{\textit{GG1}}}{2} + \frac{M_{\textit{GG2}}}{4}$$

Calculate a per-unitlayer inductance

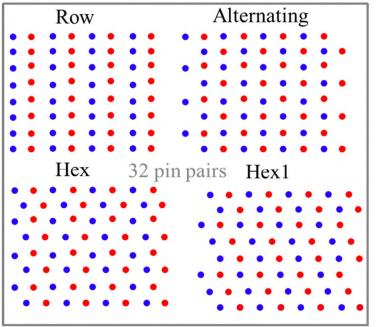

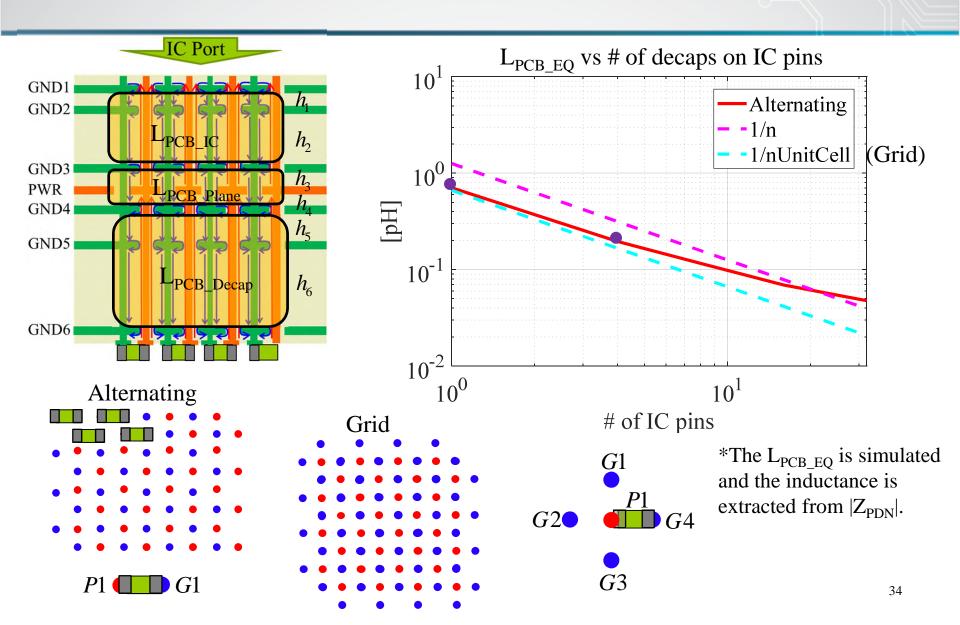

### L<sub>PCB\_IC</sub> Convergence for 1mm Pitch

#### PWR:GND=1:1

#### L<sub>PCB IC</sub> [pH] WHEN THE DRILL DIAMETER IS 8 MILS AND THE THICKNESS FROM THE IC TO THE POWER CAVITY IS 40 MILS

| IC power pin #           | Cavity Model | CST  |

|--------------------------|--------------|------|

| 72 (6 rows by 12 cols)   | 12.3         | 12.5 |

| 200 (10 rows by 20 cols) | 4.2          | 4.1  |

# Additional pin pairs or unit cells converges as

$$\frac{1}{n}$$

or  $\frac{1}{n_{unit\ cell}}$

\*The  $L_{PCB\_IC}$  is simulated in PDN Tool and the inductance is extracted from  $|Z_{PDN}|$ .

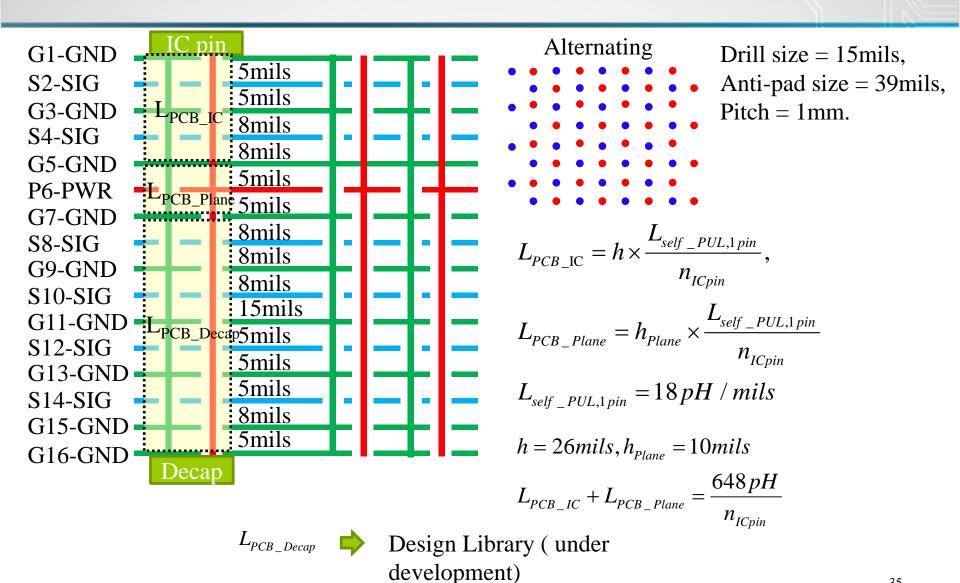

# L<sub>PCB\_IC</sub> Caclulation

### L<sub>PCB\_IC</sub> Design Calculations

Layers are "in series"

$$h = h_1 + h_2$$

$$L_{PCB\_IC} = h \times \frac{L_{self\_PUL,1pin}}{n_{ICpin}}$$

All mutual inductances are accounted for

$L_{PCB\ IC}$  per mil for one IC pin [pH]

| Pitch  | Drill size | 1/n  | 1/n <sub>UnitCell</sub> |

|--------|------------|------|-------------------------|

| 1 mm   | 8mils      | 24.5 | 13.5                    |

|        | 12mils     | 20.4 | 11.0                    |

|        | 15 mils    | 18   | 9.5                     |

| 0.8 mm | 8mils      | 22.0 | 12.0                    |

|        | 12mils     | 17.9 | 9.5                     |

### L<sub>PCB</sub> IC Design Calculations per-unit-layer

TABLE II IC PIN DESIGNS WITH DIFFERENT PITCH SIZES AND VIA-PADSTACK SIZES

| Pitch Size | Drill (Diameters) | Anti-pad (Diameters) |

|------------|-------------------|----------------------|

| 1 mm       | 8 mils            | 20 mils              |

|            | 10 mils           | 30 mils              |

|            | 12 mils           | 32 mils              |

| 0.8 mm     | 8 mils            | 20 mils              |

|            | 12 mils           | 20 mils              |

| 0.5mm      | 8mils             | 20mils               |

TABLE III. LDCB TO [PH/MIL] FOR THE UNIT CELL.

| <u> </u> | L <sub>PCB IC</sub> [PH/MIL] FOR THE UNIT CELL. |                 |                     |      |                           |      |  |

|----------|-------------------------------------------------|-----------------|---------------------|------|---------------------------|------|--|

| _        | Pitch<br>[mm]                                   | Drill<br>[mils] | PG pair.<br>formula | CST  | Grid unit cell<br>formula | CST  |  |

|          | 1                                               | 8               | 24.5                | 24.0 | 13.5                      | 12.9 |  |

|          |                                                 | 10              | 22.2                | 21.8 | 12.1                      | 11.5 |  |

|          |                                                 | 12              | 20.4                | 20.0 | 11.0                      | 10.2 |  |

|          | 0.8                                             | 8               | 22.0                | 21.8 | 12.0                      | 11.3 |  |

|          |                                                 | 12              | 17.9                | 17.3 | 9.5                       | 8.6  |  |

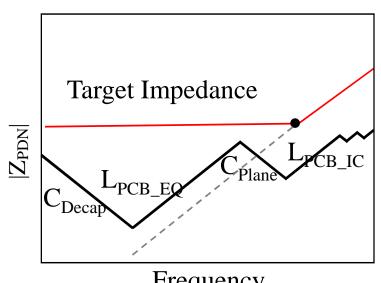

### L<sub>PCB\_IC</sub> Design Flow

- Use the IC pin placement with the lowest n=1 inductance

- Adjust the stack-up to reduce the height from the IC port to the power net area fill

- Approximate the range of the L<sub>PCB\_IC</sub> using the 1/n and 1/n<sub>UnitCell</sub> value to meet the high-frequency target impedance

- Calculate the # of IC pins needed according to the 1/n and 1/n<sub>UnitCell</sub> curve for the geometry

Frequency

### L<sub>PCB\_IC</sub> Example

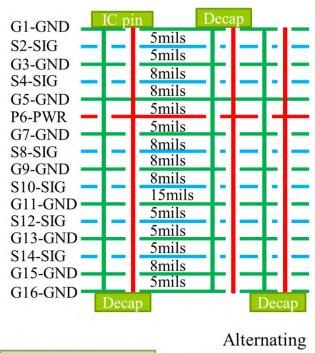

#### Alternating

Drill size = 15mils, Anti-pad size = 39mils, Pitch = 1mm.

#### Frequency

#### Requirement:

$$|Z_{PDN}| < 50m\Omega$$

, when  $f = 100MHz$

$$L_{self\_PUL,1pin} = 18 pH / mils$$

$$h = 26mils$$

$$L_{PCB\_IC\_needed} = \frac{468 \, pH}{n_{ICpin}} < 79.6 \, pH \quad \bigcirc \quad n_{ICpin} \ge 6$$

The IC pin # is 32, given by package designer.

$$L_{PCB\_IC} = h \times \frac{L_{self\_PUL,1pin}}{n_{ICpin}} = \frac{468pH}{32} = 14.6pH$$

--

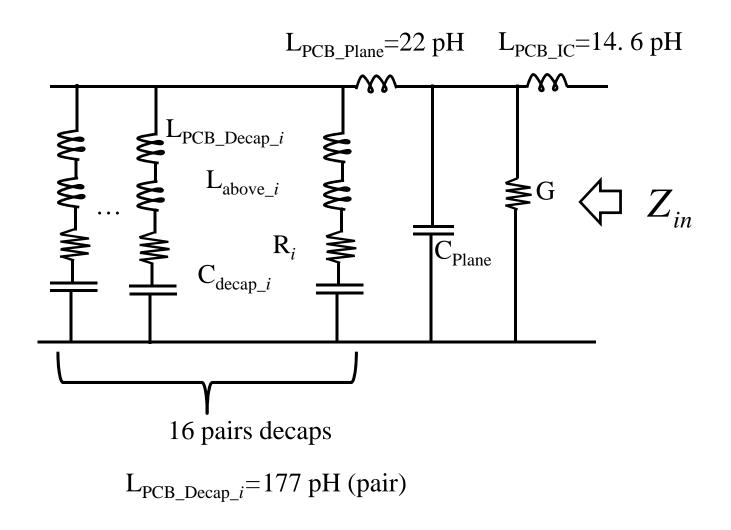

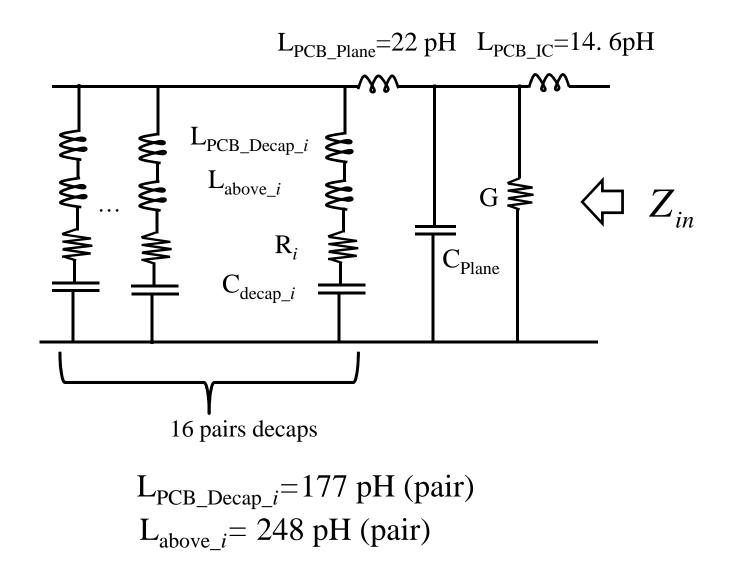

#### Impedance Equivalent Circuit

#### L<sub>PCB</sub> EO Components Approximation

$$L_{high\_needed}$$

=79.6 pH  $\downarrow$   $L_{PCB\_EQ\_min}$ =79.6 pH

$$L_{PCB\_IC}=14.6 \text{ pH}$$

Frequency

$$L_{PCB\_EQ} = L_{PCB\_IC} + L_{PCB\_Decap} + L_{PCB\_Plane} + L_{above} \le 79.6 \, pH$$

Assume: L<sub>PCB</sub> Decap is the similar to L<sub>above</sub>, L<sub>PCB</sub> Plane

$$L_{PCB\_Decap} = 22pH,$$

$$L_{PCB above} = 22pH$$

,

$$L_{PCB\_Plane} = 22pH.$$

#### Overview – Pre-layout Methodology

Problem and concepts

- PDN pre-layout design methodology

- Example geometry

- L<sub>PCB\_IC</sub> calculation

- $L_{PCB\_decap}$  calculation

- L<sub>PCB\_plane</sub> calculation

- L<sub>above</sub> calculation

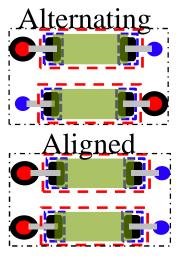

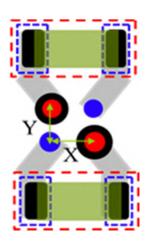

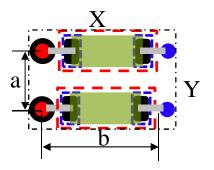

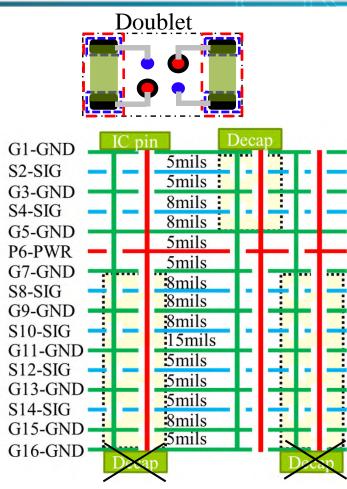

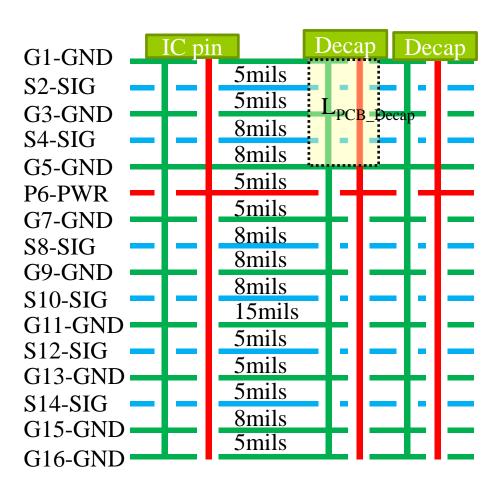

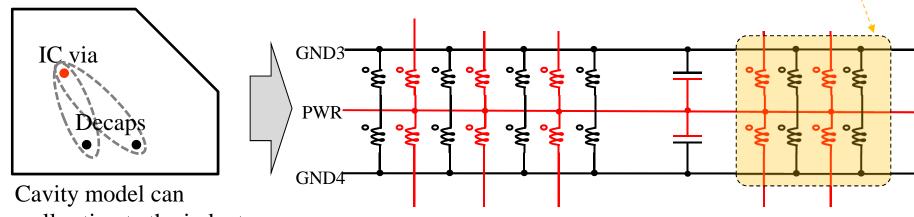

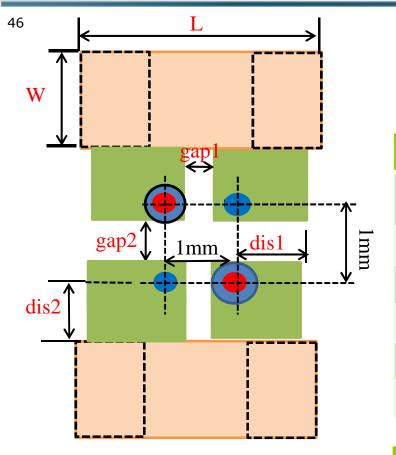

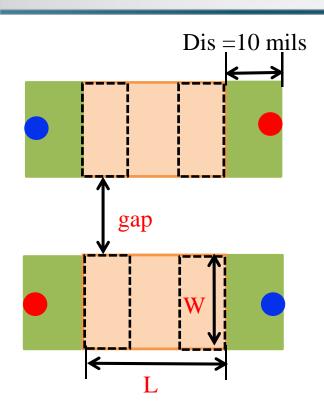

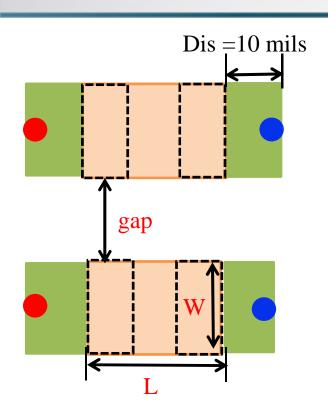

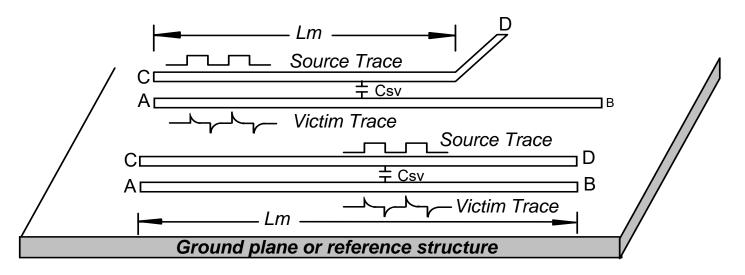

### L<sub>PCB\_Decap</sub> Geometry

Alternating

X a b

Aligned

Doublet

Relative via locations and package size ([mils]) of the three decoupling capacitor placement patterns

| Placement pattern | Size | a   | b   | X   | Y   |

|-------------------|------|-----|-----|-----|-----|

|                   | 0201 | 45  | 120 | 159 | 85  |

| Alternating/      | 0402 | 53  | 136 | 175 | 101 |

| Aligned           | 0603 | 88  | 207 | 246 | 171 |

|                   | 0805 | 108 | 223 | 262 | 211 |

|                   | 0201 | 32  | 32  | 149 | 71  |

| Doublet           | 0402 |     |     | 165 | 87  |

|                   | 0603 |     |     | 235 | 158 |

|                   | 0805 |     |     | 275 | 174 |

Occupied area

Solder land

Solder resist pattern

Package area

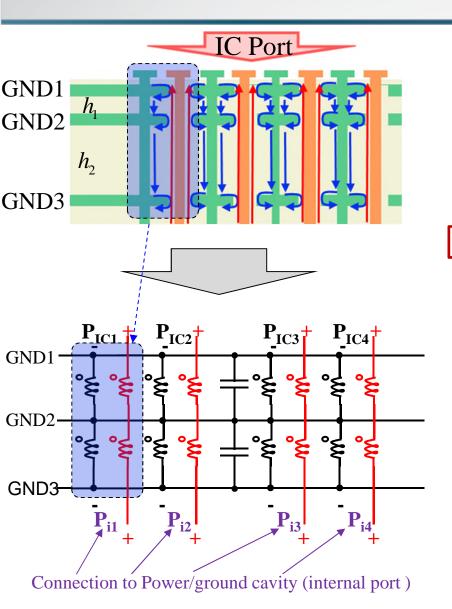

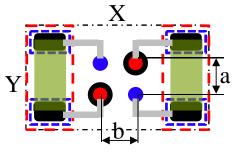

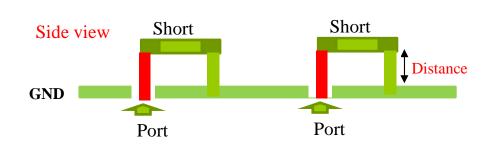

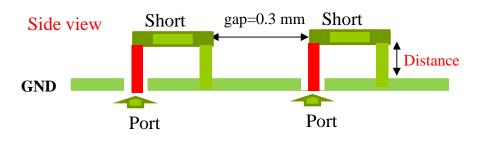

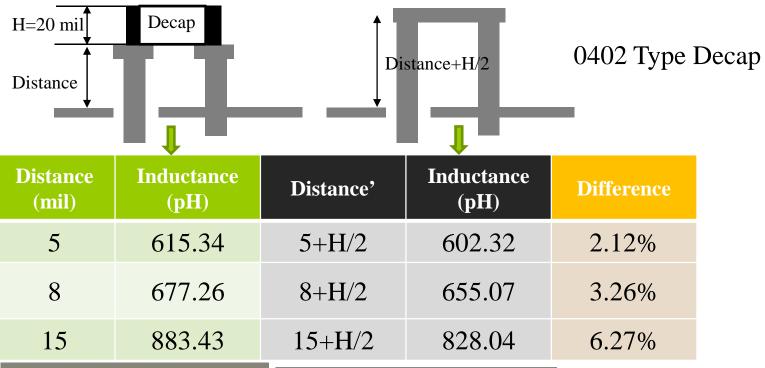

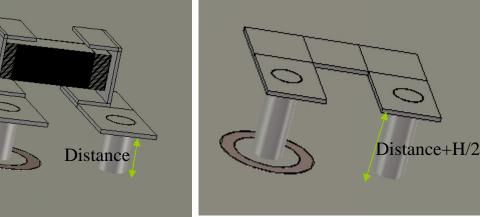

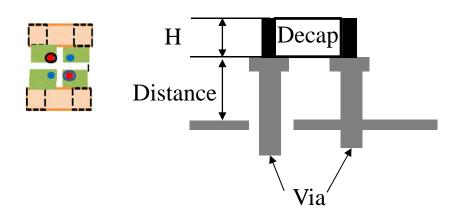

# L<sub>PCB\_Decap</sub> Inductance Physics

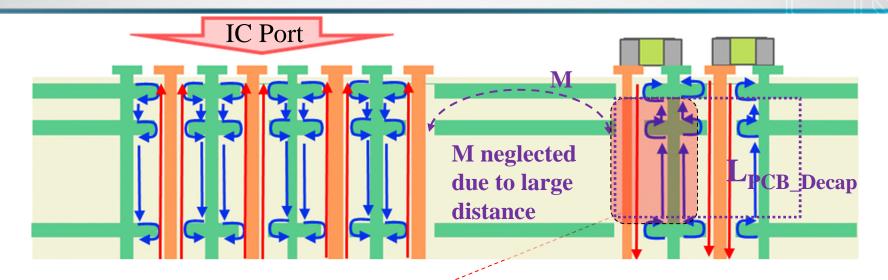

- Coupling between IC via and decap via neglected

- IC vias and decoupling capacitor vias can be modeled separately

## L<sub>PCB\_Decap</sub> Inductance Physics

$$L_{PCB\_Decap} = \frac{L_{PCB\_Decap\_PUL} \mid_{n_{(decap\ pair)}=1}}{n_{(decap\ pair)}} \times h$$

$$L_{PCB\_Decap\_PUL} \mid_{n_{(decap\ pair)}=1} =$$

$$\frac{1}{2}(L_P + L_G \bigcirc 2M_{PiGi} \bigcirc M_{P1P2} \bigcirc M_{G1G2} \bigcirc M_{P2G1}),$$

$$i = 1 \ or \ 2$$

The sign shows the contributions of the mutual inductances

Mutual inductance between the PWR and GND vias for one decap Mutual inductance between the PWR and PWR, or between GND and GND vias in different decaps Mutual inductance between the PWR and GND, or between PWR and GND vias in different decaps

| <b>Decap 0201, h=40mils</b>                      | Aligned | Alternating | Doublet |

|--------------------------------------------------|---------|-------------|---------|

| L <sub>PCB_Decap</sub>   <sub>nDecapPair=1</sub> | 798pH   | 372pH       | 246pH   |

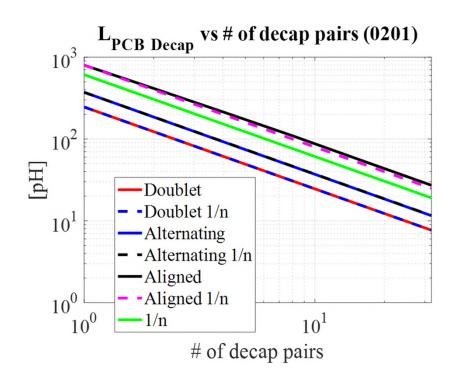

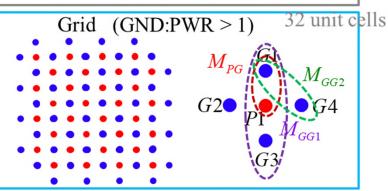

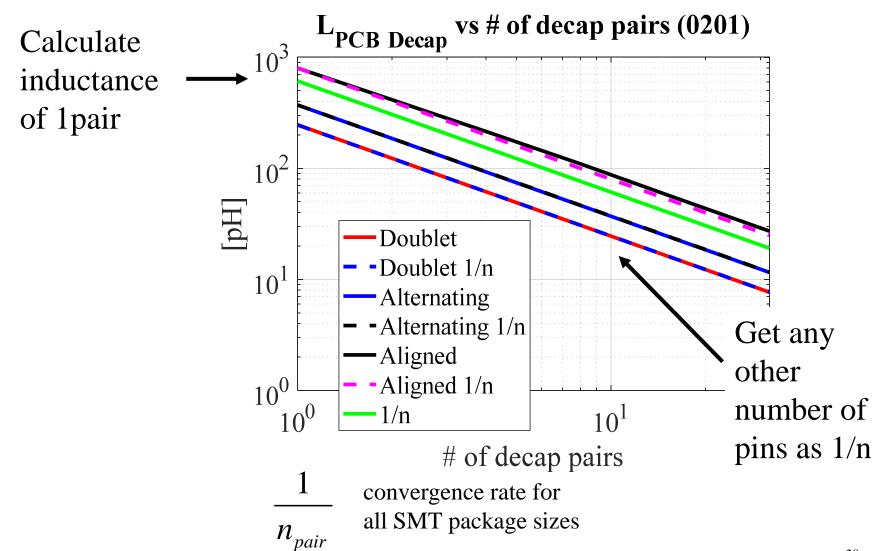

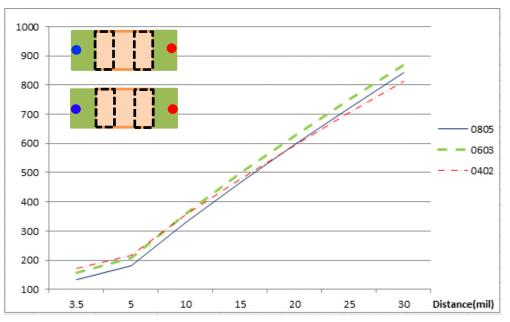

# L<sub>PCB\_Decap</sub> Functional Variation

# of decap pairs

$n_{pair}$  convergence rate for all SMT package sizes

\*The  $L_{PCB\_Decap}$  is simulated in PDN Tool and the inductance is extracted from  $|Z_{PDN}|$ .

### L<sub>PCB\_Decap</sub> Convergence

### L<sub>PCB\_Decap</sub> Design Calculations

$$\begin{split} L_{Decap\_total\_1\,pair} &= L_{Decap\_above} + L_{PCB\_Decap} \\ L_{PCB\_Decap\_1\,pair} &= h \times \boxed{L_{PCB\_Decap\_PUL}\mid_{npair=1}} \\ h &= h_1 + h_2 \end{split}$$

$L_{PCB\_Decap}$  per mil for one decap pair [pH]

| $L_{PCB\_Decap\_PUL} _{npair=1}$ | Aligned | Alternating | Doublet | Single decap /2 |

|----------------------------------|---------|-------------|---------|-----------------|

| 0201                             | 20.8    | 11.3        | 6.8     | 14.6            |

| 0402                             | 21.4    | 11.8        | 6.8     | 15.3            |

| 0603                             | 23.4    | 14.6        | 6.8     | 17.4            |

| 0805                             | 23.4    | 15.5        | 6.8     | 17.8            |

### L<sub>PCB\_Decap</sub> Design Considerations

- Use the decap placement with the lowest  $L_{PCB\_Decap}$  value

- Based on the stack-up, place the decaps on bottom or top layer closer to the power net area fill layer (to make the loop area of the decap interconnect smallest)

- Calculate the # of decaps needed to achieve

L<sub>PCB EO</sub> below the target impedance

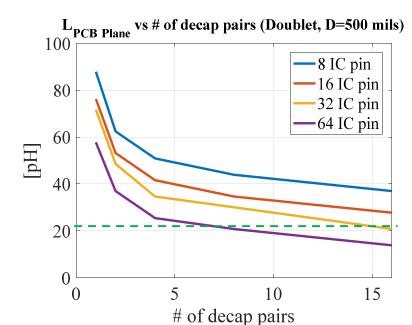

#### L<sub>PCB\_Decap</sub> Design Example

Requirement

$$L_{PCB\_Decap} \le 22 \text{ pH}$$

$$L_{PCB\_Decap\_1pair} = h \times L_{PCB\_Decap\_PUL} \mid_{npair=1}$$

$$L_{PCB\_Decap\_PUL} \mid_{npair=1} = 6.8 \, pH \, / \, mil$$

$$h = 26mils$$

$$L_{PCB\ Decap\ 1\,pair} = 177\,pH$$

$$L_{PCB\_Decap} = \frac{L_{PCB\_Decap\_PUL} \mid_{n_{(decap\ pair)}=1}}{n_{(decap\ pair)}} \times h$$

$$\frac{177\,pH}{n_{(decap\;pair)}} < 22\,pH$$

$$n_{(decap\_pair)} \ge 8$$

#### Impedance Equivalent Circuit

#### Decaps Under the IC

# L<sub>PCB\_EQ</sub> Variation for Decaps Under the IC

#### L<sub>PCB</sub> Example for Decaps Under the IC

#### Outline

- Problem and concepts

- PDN pre-layout design methodology

- Example geometry

- L<sub>PCB IC</sub> calculation

- L<sub>PCB\_decap</sub> calculation

- $L_{PCB\_plane}$  calculation

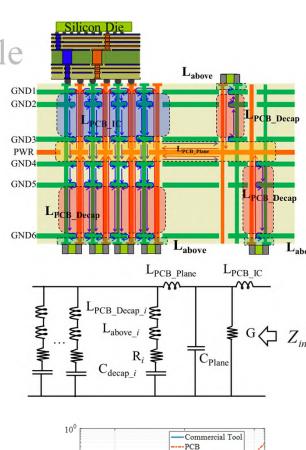

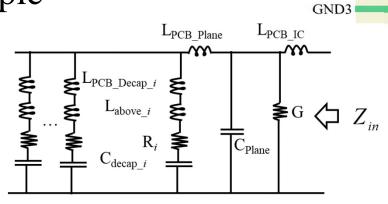

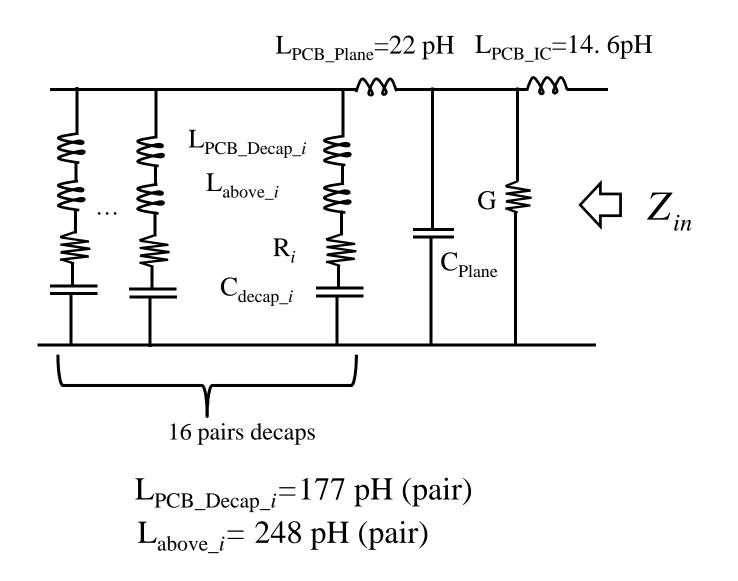

$L_{\text{PCB\_Decap\_}i}$

$L_{above\_i}$

$C_{decap\_i}$

- L<sub>above</sub> calculation

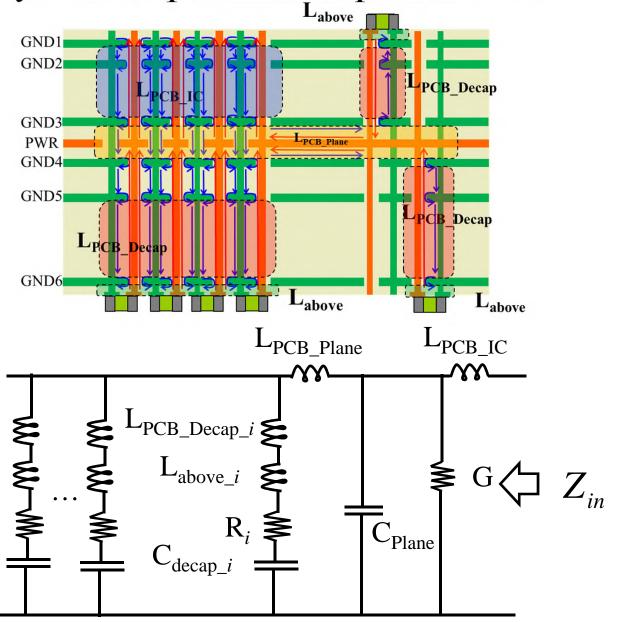

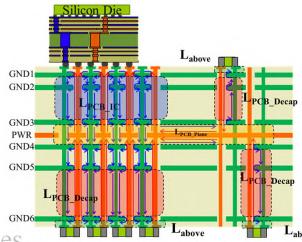

- If the current path on the power net is direct to decaps and L is not significantly changed due to power net voids, the following design curves are used.

- Horizontal inductance and vertical inductance are merged in the model and final equivalent circuit model is constructed as below.

well estimate the inductance.

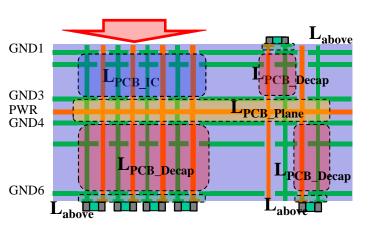

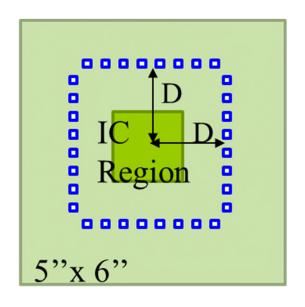

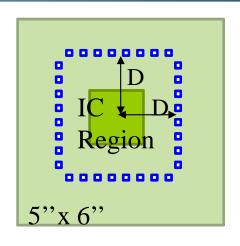

# L<sub>PCB\_Plane</sub> Geometry

# L<sub>PCB\_Plane</sub> Current Physics and Inductance

Pitch = 1mm Decaps are placed on the top layer

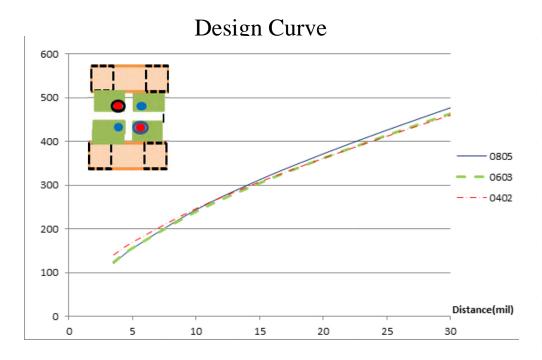

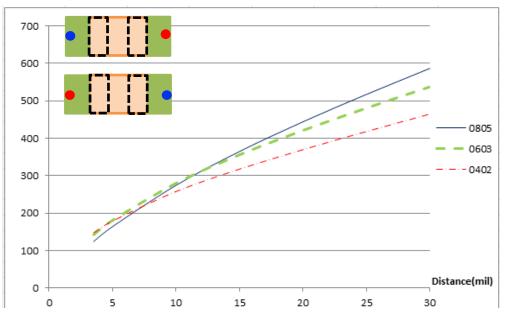

# L<sub>PCB\_Plane</sub> Design Curves

## L<sub>PCB Plane</sub> Example

Requirement: L<sub>PCB\_Plane</sub> <=22 pH

From the design curves, D=500mils,  $n_{Decap\_Pair}$  >=16.

Combine the requirement from  $L_{PCB\_IC}$ ,

$$L_{PCB\_Decap}$$

,  $n_{ICpin} >= 6$ ,  $n_{Decap\_Pair} >= 8$

$$n_{ICpin} = 32$$

,  $n_{Decap\_Pair} > = 16$

## Impedance Equivalent Circuit

#### Outline

Problem and concepts

- PDN pre-layout design methodology

- Example geometry

- L<sub>PCB\_IC</sub> calculation

- L<sub>PCB\_decap</sub> calculation

- L<sub>PCB\_plane</sub> calculation

- L<sub>above</sub> calculation

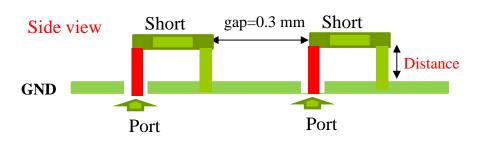

## L<sub>above</sub> Geometry

## L<sub>above</sub> Geometries

Decoupling capacitor of sizes 0805/0603/0402/0201 for  $L_{above}$  design space

| # | Name                  | Figure | # | Name                            | Figure | # | Name                    | Figure | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---|-----------------------|--------|---|---------------------------------|--------|---|-------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Shared<br>Via         |        | 2 | Power<br>Via<br>Alternati<br>ng | 00     | 3 | Doublet                 |        | 40 27 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4 | Via in<br>Pad         |        | 5 | Shared<br>Pad                   | 0 0    | 6 | Via in pad alternat ing |        | 24<br>19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |