# Analog Circuit Design with Submicron Transistors

Bernhard Boser UC Berkeley Department of Electrical Engineering and Computer Sciences boser@eecs.berkeley.edu

© 2004 B. Boser 1

# Analog Circuit Design

- <u>Objective</u>: Translate circuit specifications (gain, bandwidth, dynamic range, ...) into transistor sizes and bias currents

- <u>Challenge</u>:

Accurate device models for deep submicron transistors

- "Square-law model"

- Simulation models (BSIM, EVK, ...)

- "Model" for analog design

# **Device Model Objectives**

- Device Physics

- Simulation / Verification

- Accuracy, efficiency

- (Analog) Circuit Design

- Relate device characteristics to circuit specifications

- E.g.

- Bandwidth

- Gain

- Power dissipation

- Dynamic range (noise)

- Accurate, simple

## **Device Parameters for Analog Design**

- Large signal

- Current  $I_D \rightarrow$  power dissipation

- Minimum  $V_{DS} \rightarrow$  available signal swing

- Small signal

- Transconductance  $g_m \rightarrow$  speed / voltage gain

- Capacitances  $C_{GS}$ ,  $C_{GD}$ , ...  $\rightarrow$  speed

- Output impedance  $r_o \rightarrow voltage gain$

# Metrics for Design

- Transistor Objectives: High transconductance

- Without large  $I_D$

- Without large C<sub>GS</sub>

- Figures of Merit

- Current efficiency

$$\frac{g_m}{I_D}$$

Transit frequency

$$\frac{g_m}{C_{gs}}$$

# **Current Efficiency**

• "Square-law transistor":

$$I_{D} = \frac{1}{2} \mu C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^{2}$$

$$g_{m} = \frac{2I_{D}}{V_{GS} - V_{TH}}$$

$$= \frac{2I_{D}}{V_{d}^{sat}} \quad \leftarrow \text{Overdrive voltage}$$

• High efficiency  $\rightarrow$  low overdrive voltage

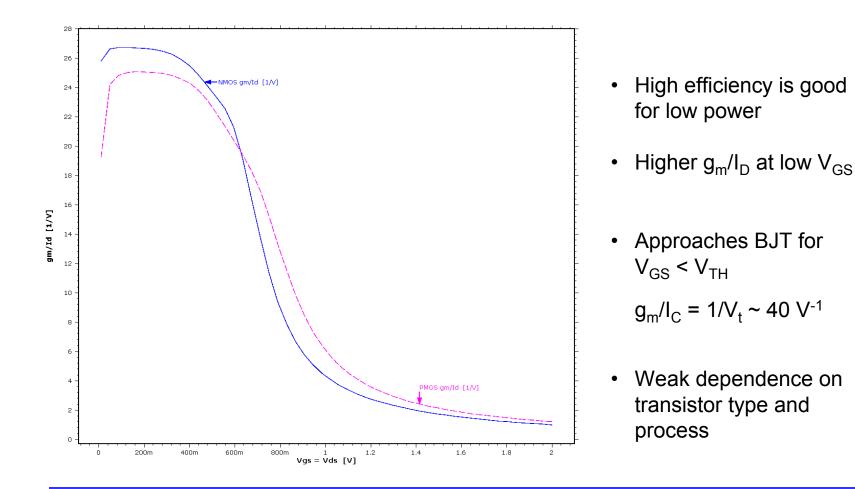

# Current Efficiency $g_m/I_D$

© 2004 B. Boser 7

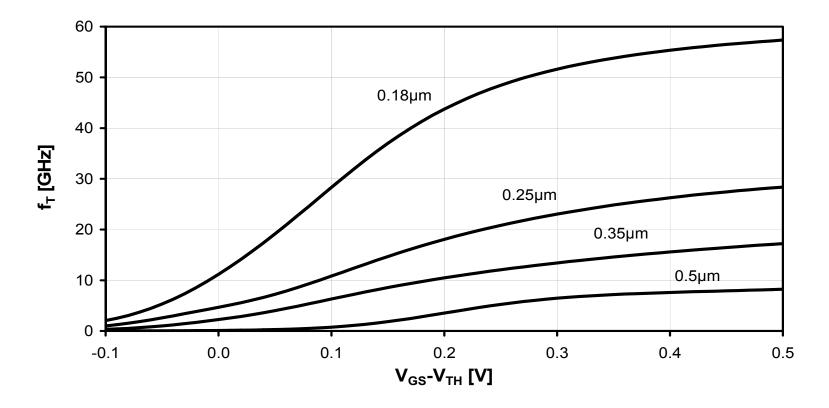

# Transit Frequency $\omega_T$

Unity current-gain bandwidth

$$\omega_T = \frac{g_m}{C_{gs} + C_{gd}}$$

$$\approx \frac{\mu V_d^{sat}}{L^2} \qquad (square - law model)$$

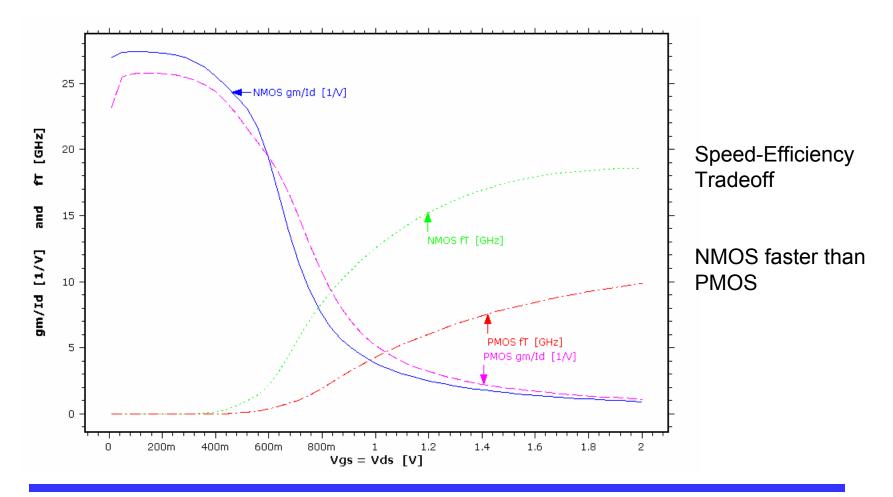

# Efficiency $g_m/I_D$ versus $f_T$

## **Device Scaling**

#### Short channel devices are significantly faster!

#### Current Efficiency vs Transient frequency

• Tradeoff:

$$\frac{g_m}{I_D} \propto \frac{1}{V_d^{sat}}$$

$$\omega_T \propto V_d^{sat}$$

• What about:

$$\frac{g_m}{I_D} \times \omega_T \propto \frac{\mu}{L^2}$$

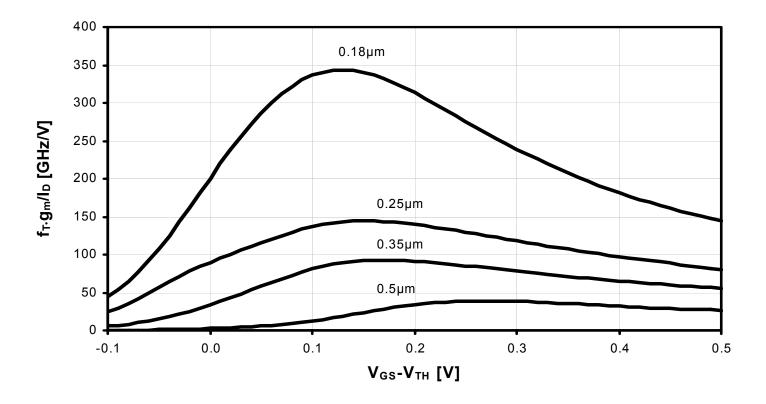

# **Device Figure-of-Merit**

Peak performance for low  $V_{GS}$ - $V_{TH}$

### **Device Scaling for Analog Circuits**

- "Moore's Law"

- $L_{min}$  decreases ~ 2x every 5 years

- L<sub>min</sub> = 10μm in 1970, 90nm in 2004

- Benefits (for analog circuits):

- Higher speed: increase  $g_m/C_{gs}$  while keeping  $g_m/I_D$  constant

- Lower power: increase  $g_m/I_D$  while keeping bandwidth ( $g_m/C_{gs}$ ) constant

- In both cases, reducing L is advantageous!

# **Short Channel Devices**

- Short channel effects

- Velocity saturation

- Mobility degradation (thin oxide)

- Prior considerations assume "square law" models and ignore these effects

→ Significant discrepancies

- Let's fix this ...

# Efficiency $g_m/I_D$

- Important design parameter ... but a little unusual: units 1/V

- Let's define

$$V^* = \frac{2I_D}{g_m} \qquad \Leftrightarrow \qquad \frac{g_m}{I_D} = \frac{2}{V^*}$$

e.g. V\* = 200mV  $\rightarrow$  g<sub>m</sub>/I<sub>D</sub> = 10 V<sup>-1</sup>

• Square-law devices <u>only</u>:  $V^* = V_{GS} - V_{TH} = V_{dsat}$

Square law:

$$g_m = \frac{2I_D}{V_{GS} - V_{TH}} = \frac{2I_D}{V^*}$$

# Saturation Voltage versus V\*

- Saturation voltage

- Minimum  $V_{DS}$  for "high" output resistance

- Poorly defined: transition is smooth in practical devices

- "Long channel" (square law) devices:

$$-V_{GS} - V_{TH} = V_{dsat} = V_{ov} = V^*$$

- Significance:

- Channel pinch-off

nalogCircuit Desat with Submicron Transistors

© 2004 B. Boser 16

Boundary between triode and saturation

# Design Example

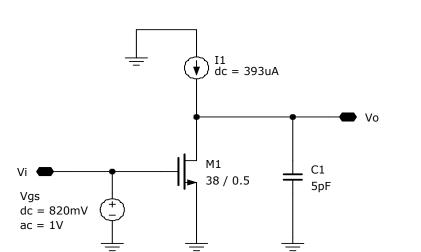

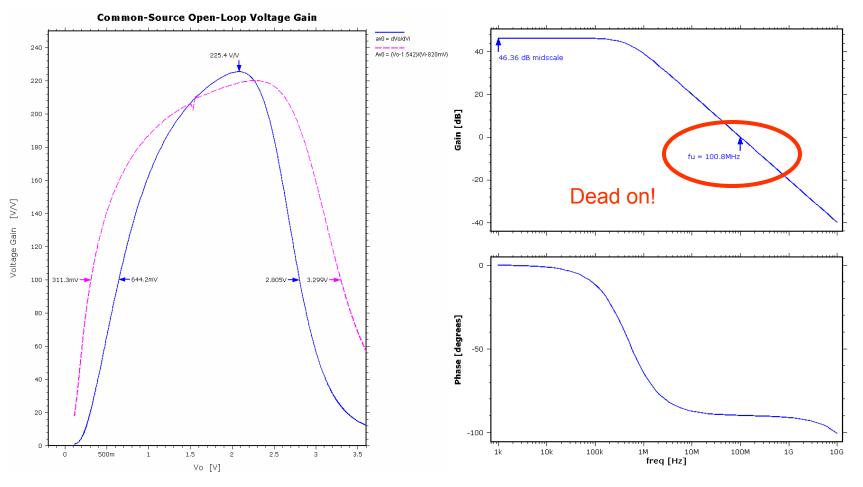

#### <u>Example</u>: Common-source amp $a_{v0} > 100$ , $f_u = 100$ MHz for $C_L = 5$ pF

**DC Analysis** DC1 Device Vgs sweep from 800m to 900m (1001 steps)

•  $a_{v0} > 100 \rightarrow L = 0.5 \mu m$

AC Analysis AC1 log sweep from 1k to 10G (101 steps)

- $g_m \approx 2\pi f_u C_L = 3.14 \text{mS}$

- High  $f_T$  (small  $C_{GS}$ ): V\* = 250mV

•

$$I_D = \frac{g_m V^*}{2} = 393 \mu A$$

Analog Circuit Design with Submicron Transistors

© 2004 B. Boser 17

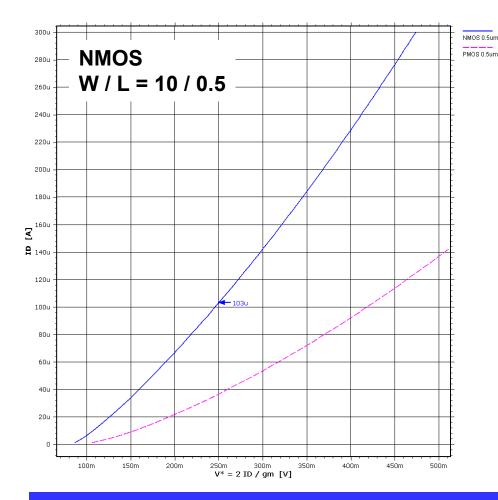

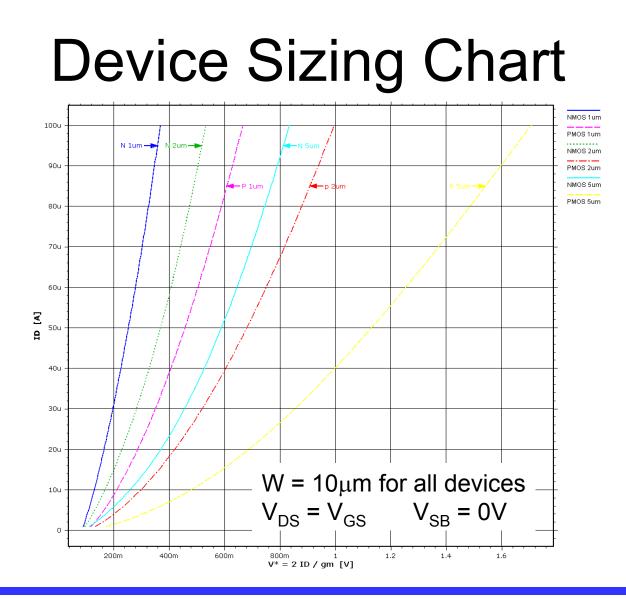

## **Device Sizing**

- Pick L 0.5μm

- Pick V\* 250mV

- Determine g<sub>m</sub> 3.14mS

- $I_D = 0.5 g_m V^*$  393µA

- W from graph (generate with SPICE)

- → W = 10μm (393μA /103μA) = <u>38μm</u>

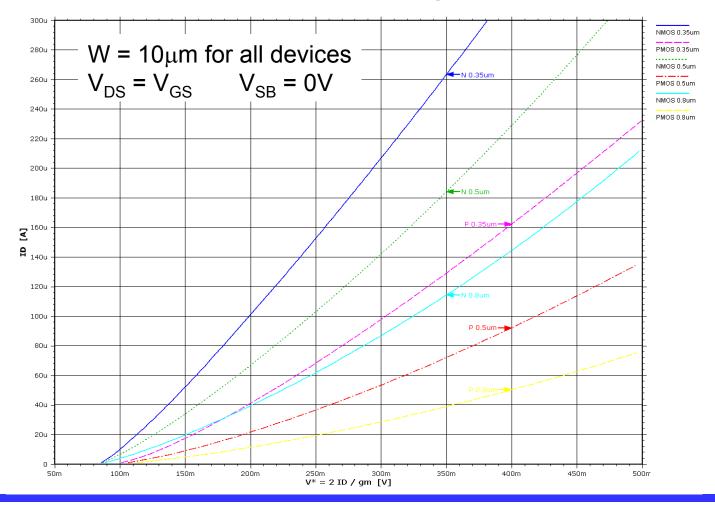

- Create such graphs for several device length' for design reference

## **Common Source Example**

## **Device Sizing Chart**

## **Device Parameters for Analog Design**

- Large signal

- Current  $I_D \rightarrow$  power dissipation

- Minimum  $V_{DS} \rightarrow$  available signal swing

- Small signal

- Transconductance  $g_m \rightarrow$  speed / voltage gain

- Capacitances  $C_{GS}$ ,  $C_{GD}$ , ...  $\rightarrow$  speed

- Output impedance  $r_o \rightarrow voltage gain$

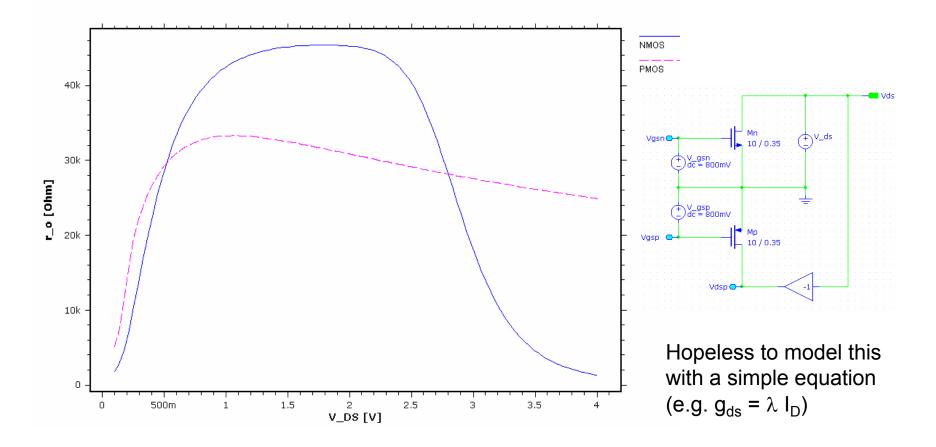

## Output Resistance r<sub>o</sub>

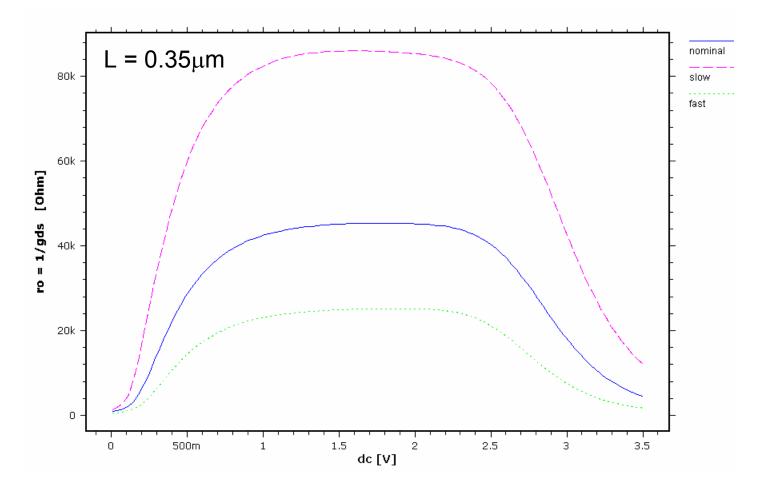

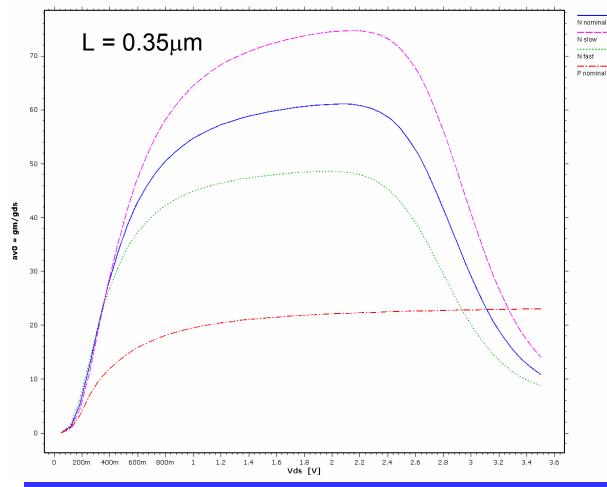

## Process Variations for r<sub>o</sub>

© 2004 B. Boser 24

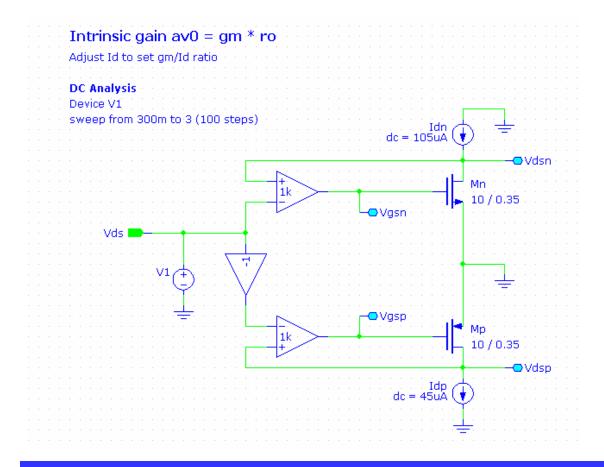

# Open-loop Gain a<sub>v0</sub>

More useful than r<sub>o</sub>

Analog Circuit Design with Submicron Transistors

© 2004 B. Boser 25

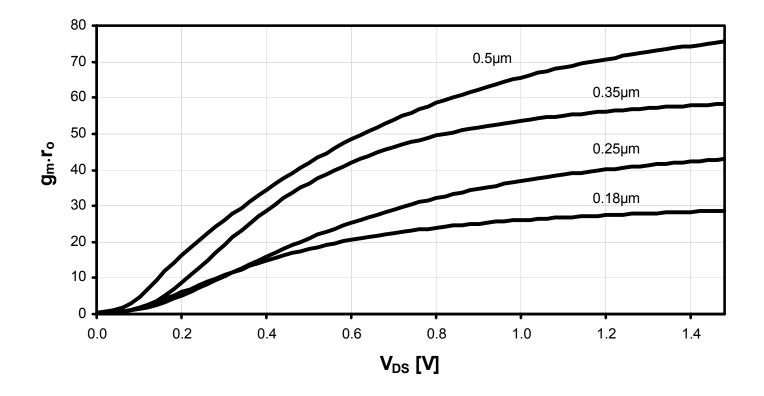

# Gain, $a_{v0} = g_m r_o (g_m / I_D = 10 / V)$

Strong tradeoff: a<sub>v0</sub> versus V<sub>DS</sub> range

Create such plots for several device length' for design reference

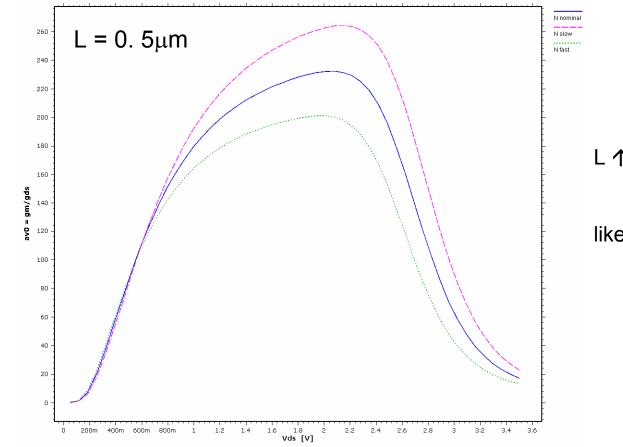

# Gain, $a_{v0} = g_m r_o (g_m / I_D = 10 / V)$

$L \uparrow \rightarrow a_{v0} \uparrow$

like long channel device

# **Technology Trend**

Short channel devices suffer from reduced per transistor gain

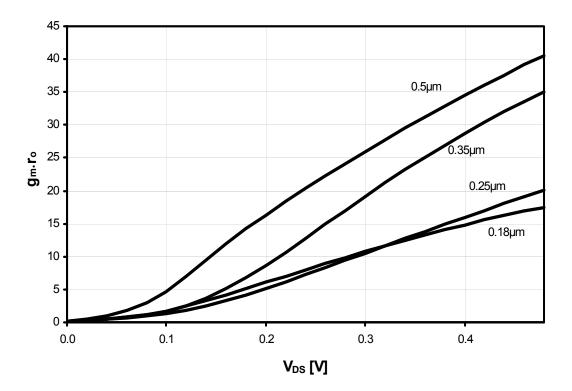

# **Transistor Gain Detail**

For practical  $V_{DS}$  the effect the "short-channel" gain penalty is less severe (remember: worst case  $V_{DS}$  is what matters!)

# Current Sources (Biasing)

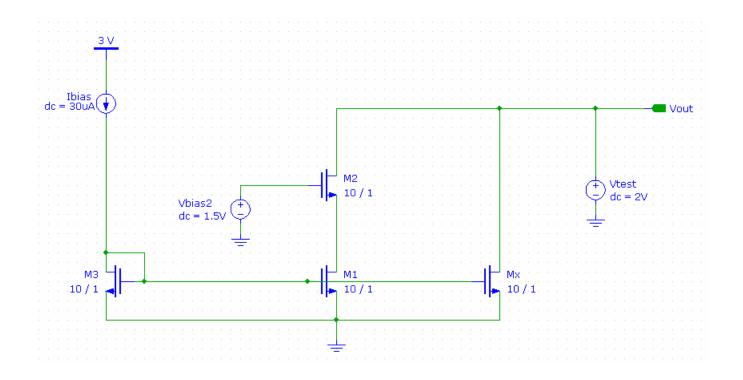

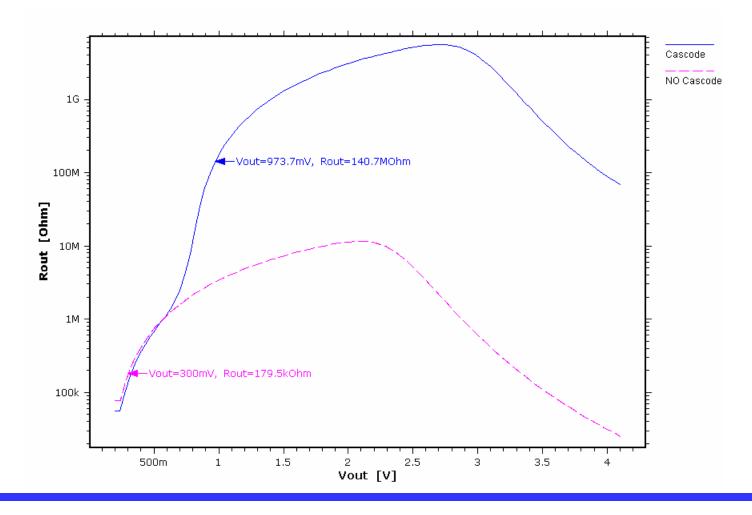

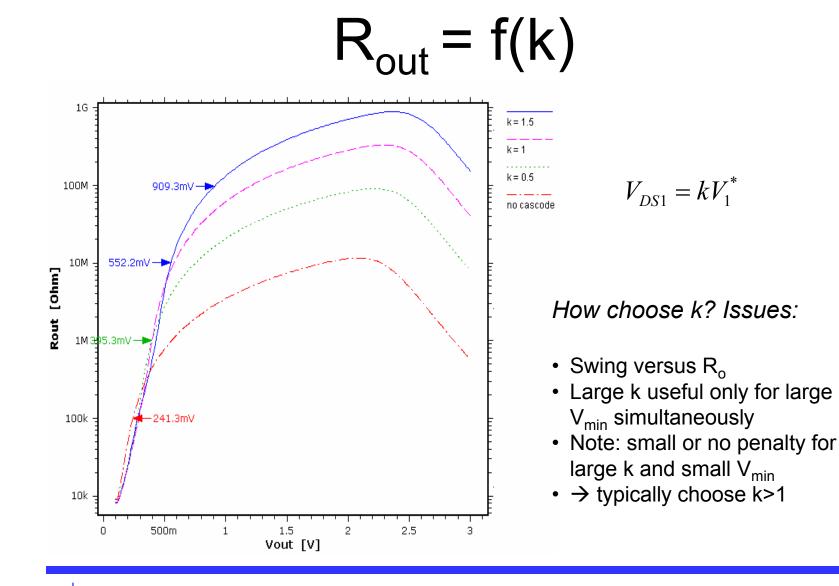

# Cascoding

How choose V<sub>bias2</sub>?

### **Output Resistance**

© 2004 B. Boser 33

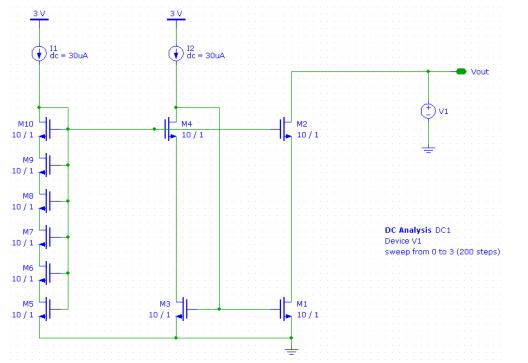

# **High-Swing Bias Example**

- M5 ... M10 replace quarter size device

- All devices same size

- Less sensitive to body-effect

```

• L<sub>current-source</sub> = L<sub>cascode</sub>

```

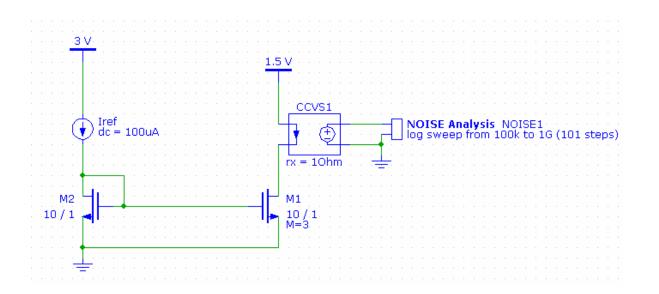

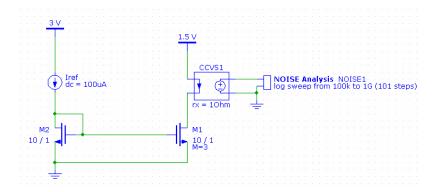

# Noise

$$\overline{i_{on}^{2}} = \overline{i_{d1}^{2}} + M^{2}\overline{i_{d2}^{2}}$$

$$= 4k_{B}T\gamma(g_{m1} + M^{2}g_{m2})\Delta f$$

$$= 4k_{B}T\gamma g_{m1}(1+M)\Delta f$$

$$= 4k_{B}T\frac{1}{R_{N}}\Delta f$$

$$R_{N} = \frac{1}{g_{m1}} \frac{\gamma^{-1}}{1+M}$$

$$= \frac{r_o}{a_{v0}} \frac{\gamma^{-1}}{1+M} << R_o = r_o$$

1

- M2 (and I<sub>ref</sub>!) can add noise

- Choose small M (power penalty), or

- Filter at gate of M1

- Current source FOMs

- Output resistance R<sub>o</sub>

- Noise resistance R<sub>N</sub>

- Active sources boost R<sub>o</sub>, not R<sub>N</sub>

# V<sub>min</sub> versus Noise

$$V_{\min} = k \times V^*$$

typ.  $k = 1...2$

$$R_{N} = \frac{1}{g_{m1}} \frac{\gamma^{-1}}{1+M} = \frac{V_{\min}}{2KI_{D}} \frac{\gamma^{-1}}{1+M}$$

- Voltage required for large R<sub>o</sub> (saturation): V<sub>min</sub> ~ V\* (based on intuition from square-law model)

- Minimizing noise (for given I<sub>D</sub>):

→ large R<sub>N</sub>

→ large V<sub>min</sub> (k >> 1)

- At odds with signal swing (to maximize the dynamic range)

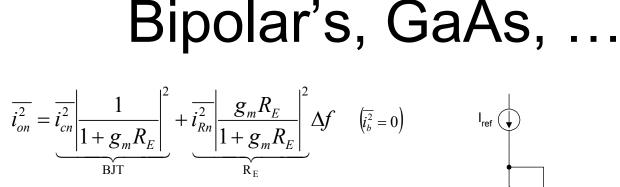

a)

$$g_m R_E = 0$$

$i_{on}^2 = 2k_B T g_m \Delta f$

$R_N = \frac{2}{g_m} = \frac{2V_t}{I_C}$  set by  $I_C$

b)

$$g_m R_E >> 1$$

$\overline{i_{on}^2} = 4k_B T \frac{1}{R_E} \Delta f$

$$R_N = R_E = \frac{V_{\min}}{I_C} \frac{V_{\min} - V_{ce}^{sat}}{V_{\min}}$$

$R_{N,MOS} = \frac{V_{\min}}{I_{\rm D}} \frac{\gamma^{-1}}{2K}$

compare

$$I_{ref}$$

- BJT and R<sub>E</sub> contribute noise

- Increasing R<sub>E</sub> <u>lowers</u> overall noise

- BJT and MOS exhibit essentially same noise / V<sub>min</sub> tradeoff

- Lowest possible noise source is a resistor (and large  $V_{\text{min}},\,V_{\text{DD}})$

# Small Signal Design Summary

- Determine g<sub>m</sub> (from design objectives)

- Pick L

- − Short channel → high  $f_T$

- − Long channel → high  $r_o$ ,  $a_{v0}$

- Pick V\* =  $2I_D/g_m$

- − Small V\* → large signal swing

- − High V\* → high  $f_T$

- Dynamic range:  $P_{sig} \sim 1/V^*$ ,  $P_{noise} \sim V^*$

- Determine I<sub>D</sub> (from g<sub>m</sub> and V\*)

- Determine W (SPICE / plot)

- <u>Accurate</u> for short channel devices → key for design

# **Device Parameter Summary**

| Device<br>Parameter | Circuit Implications                                                |

|---------------------|---------------------------------------------------------------------|

| V*                  | <ul> <li>Current efficiency, g<sub>m</sub>/I<sub>D</sub></li> </ul> |

|                     | <ul> <li>Power dissipation (I<sub>D</sub>)</li> </ul>               |

|                     | • Speed (g <sub>m</sub> )                                           |

|                     | • Cutoff frequency, $f_T \rightarrow$ phase margin                  |

|                     | • Headroom, V <sub>DS,min</sub>                                     |

| L                   | • Cutoff frequency, $f_T \rightarrow$ phase margin                  |

|                     | <ul> <li>Intrinsic transistor gain (a<sub>v0</sub>)</li> </ul>      |

| W                   | Obtain from L, I <sub>D</sub>                                       |

|                     | • Self loading (C <sub>GS</sub> , C <sub>DB</sub> ,)                |