# Challenges in achieving first-silicon success for 10M-gate SoCs: A silicon engineering perspective (Updated & Expanded)

Aurangzeb Khan Cadence Design Systems, Inc. IEEE Solid State Circuits Society - Santa Clara Valley September 19, 2003

CADENCE CONFIDENTIAL

# **Topics**

- Motivation

- Design challenges

- Silicon Engineering focus

- Design approach

- Design challenges and solutions

- Innovative design technology

- Results

- Summary

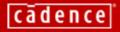

## There is no market ... for a second-to-market

| Market Trends              | 2002   | 2006   |

|----------------------------|--------|--------|

| SoC semiconductor revenues | \$ 23B | \$ 53B |

| SoC design starts (% ASIC) | 59%    | 80%    |

#### First-to-Market <u>and</u> First-to-Volume SOCs → Business Success 1st Silicon Success<sup>®</sup> critical

Dataquest 2002

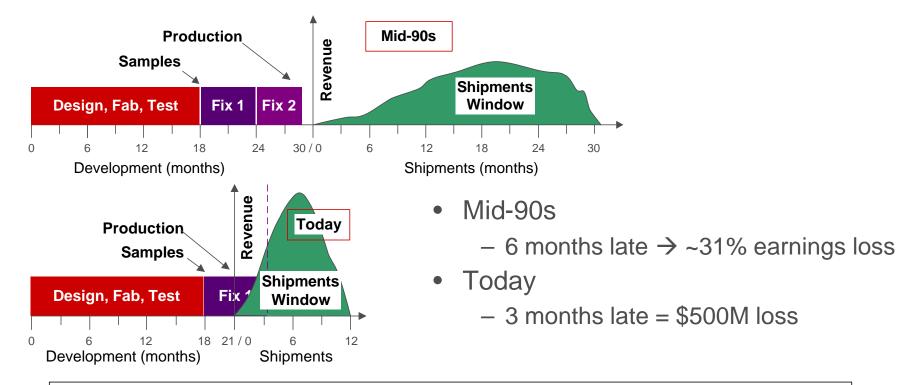

## **Design complexity intensifies challenge**

| <ul> <li>IC integration density and content</li> </ul> |                       |  |  |

|--------------------------------------------------------|-----------------------|--|--|

| <ul> <li>Integration (# transistors)</li> </ul>        | ~30M - 300M           |  |  |

| <ul> <li>Die Size (sq. mm.)</li> </ul>                 | ~12x12 - ~22x22       |  |  |

| <ul> <li>Clock Rate (MHz)</li> </ul>                   | 200 - 900             |  |  |

| <ul> <li>Memory Instances (#)</li> </ul>               | ~100 - 600            |  |  |

| <ul> <li>Analog Blocks (#)</li> </ul>                  | ~1 - 10               |  |  |

| <ul> <li>Routed Nets (#)</li> </ul>                    | ~8M - 20M+            |  |  |

| <ul> <li>Functional design modes</li> </ul>            |                       |  |  |

| <ul> <li>Operational Modes (#)</li> </ul>              | 1 – 13                |  |  |

| <ul> <li>Package, board technology</li> </ul>          |                       |  |  |

| <ul> <li>Package Types</li> </ul>                      | Flip-chip BGA, EBGA   |  |  |

| <ul> <li>I/O Ckt. Types (#)</li> </ul>                 | ~1 - 10               |  |  |

| <ul><li>I/Os (total #)</li></ul>                       | ~2,000+               |  |  |

| <ul> <li>I/O Frequency</li> </ul>                      | 200 MHz – 3.125+ Gb/s |  |  |

| – Power (W)                                            | ~5 – 25               |  |  |

| <ul> <li>Board Layers</li> </ul>                       | ~2 - 50               |  |  |

| <ul> <li>Supply chain</li> </ul>                       |                       |  |  |

| <ul> <li>IP Providers (#)</li> </ul>                   | 1 – 10                |  |  |

| <ul> <li>Supply chain Providers</li> </ul>             | 3 – 5                 |  |  |

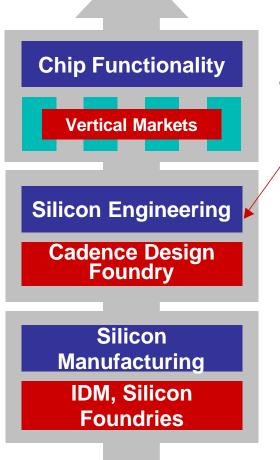

# Specialize and partner to build the product delivery value chain

- ...to achieve First-to-Market and First-to-Volume with increasing design complexity

- Differentiated value

- Broad and deep Silicon Engineering expertise

- Analog, IP, IC, package, board; DFT, DFM

- Design-proven methodology (mixed-signal)

- Design-proven technologies

- Design-proven IP (supply, integration)

- Supply chain management

- "...We have reached the point where back-end physical design and verification takes far longer than front-end system, architecture and logic design!"

Dr. H Samueli; Co-Chairman & CTO, Broadcom Corp.; Invited Keynote Address; ISSCC, 2/99

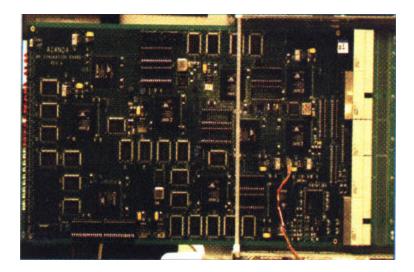

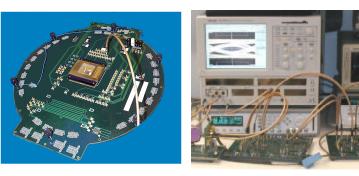

# Customers focus on architecture, logic design challenges

- Design verification

- Custom FPGA-based system

- Accelerate system bring-up

- RTL, apps. verified prior to silicon

Azanda Network Devices, Inc. material used with permission

# We focus on Silicon Engineering

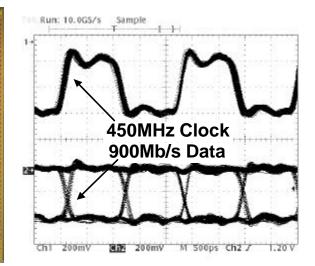

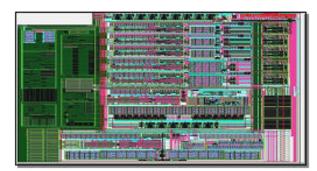

- Azanda Network Devices Scimitar<sup>™</sup> AZ61100

- Industry-First Single-Chip,Full-Duplex, OC-48 Traffic Manager and ATM Segmentation and Reassembly SoC

1M simultanous traffic flows

5 Gb/s bandwidth

900 Mb/s data rate

~78M transistors

1,800+ I/Os

#### **1st Silicon Success®**

Azanda Network Devices, Inc. material used with permission

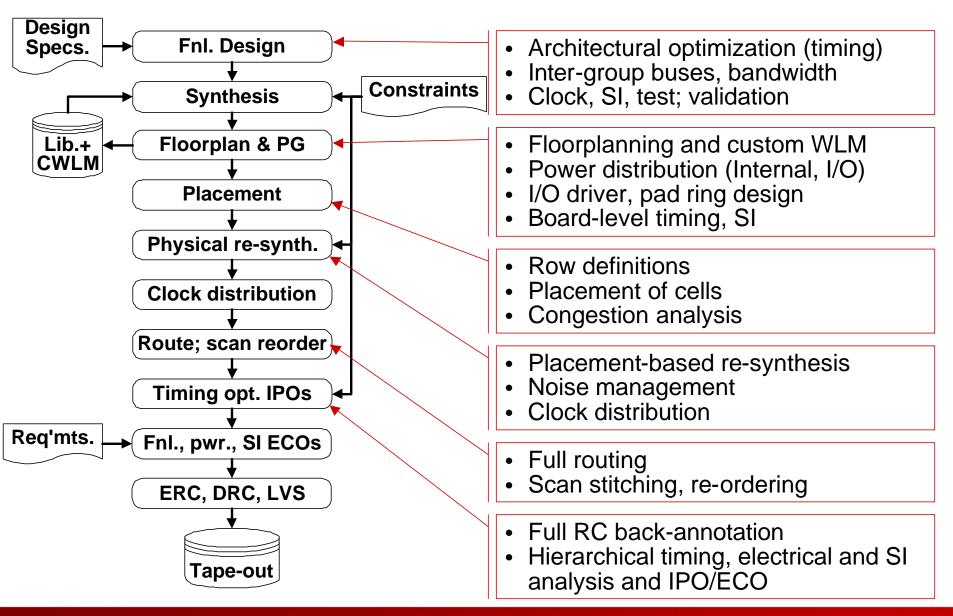

# Leading by Design

Accelerate / focus innovative design methodology, technology by creating leading-edge SoCs

- Silicon engineering

- Architectural, functional design & verification

- Unified verification

- Electrical & physical design

- Mixed-signal Soc design methodology

- Hierarchical design

- Wiring-centric design

- Timing, clocking, power, SI

- IP

- Analog, digital IP development, reuse

- Third-party IP integration

- Technology Readiness

- IC/package/board co-optimization

- Supply chain

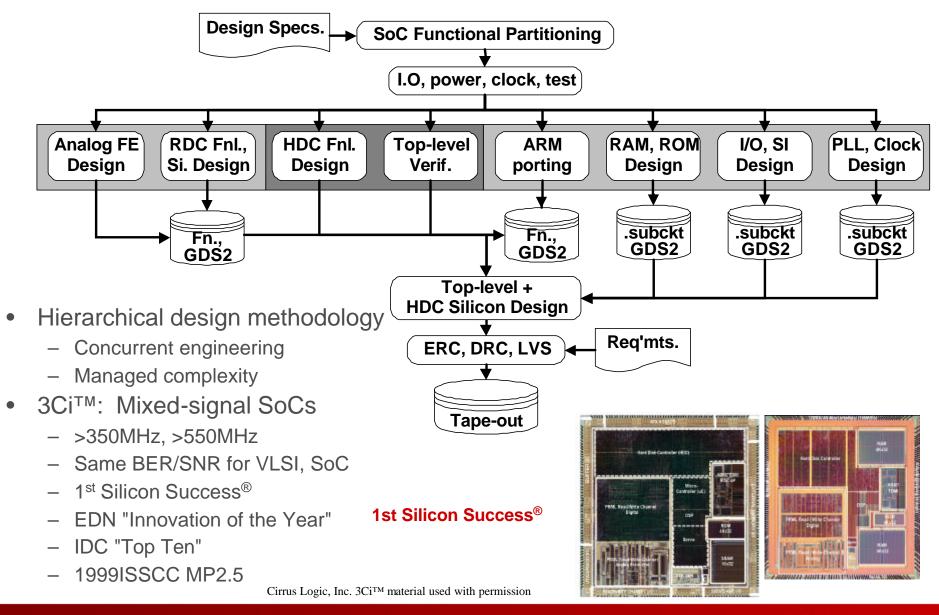

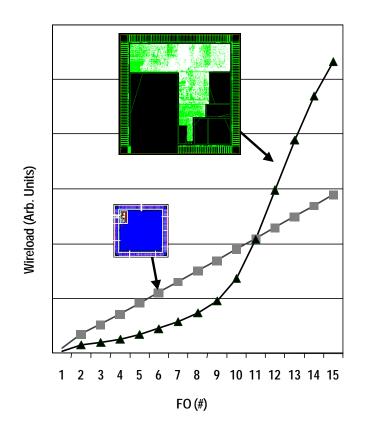

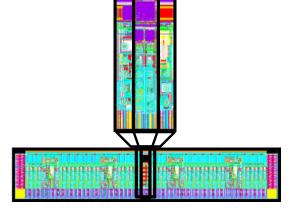

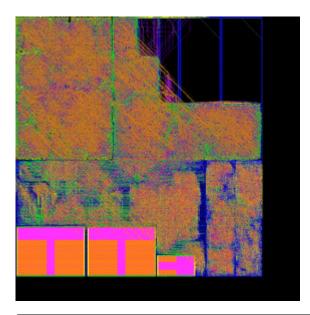

# **Top-level design methodology (example)**

### Wireload models $\rightarrow$ Physical synthesis

- 40% 80% of core area memory-based

- Physical synthesis critical to timing closure

Material used with permission

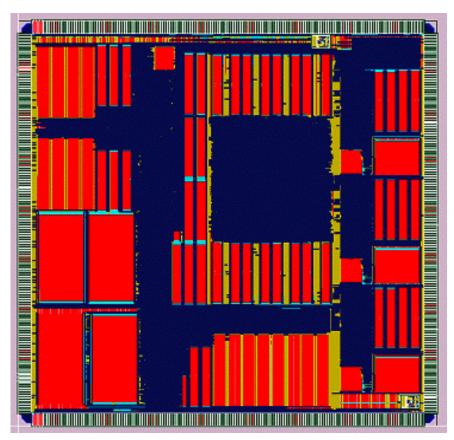

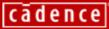

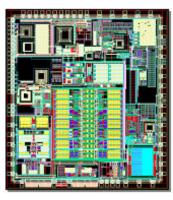

# Block-level design methodology (example)

## Sony Computer Entertainment GS®I-32

- Architectural design enhancements

- 8x higher eDRAM vs. PS2 Rendering Processor (256 Mb)

- eDRAM bandwidth = 48 GB/s (Buses >2K bits wide)

- Rendering speed = 75M polygons/s

- "Gscube" renders 1.2G polygons/s

- Exceeds highest HDTV standard

- 1920x1080, 60 fps progressive

- 280M + 7.5M transistors

- 21.7 x 21.3 mm<sup>2</sup>

- >400K components

- >500K signal nets

- >2K nets >10 mm. long

- 0.18 um, 6-metal eDRAM CMOS

- Netlist to tape-out = 10 weeks

- 1st Silicon Success<sup>®</sup>

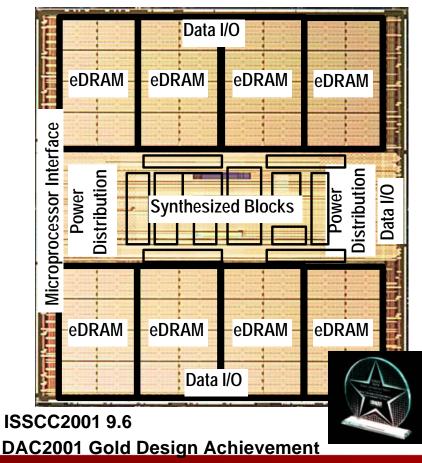

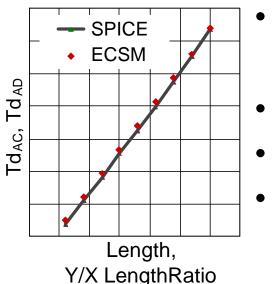

# Accurate numerical model for circuit behavior

- Circuit behavior nonlinear

- Conventional linear model  $\rightarrow$  >5% error in delay calculation

- Nonlinear model → accurate di/dt

- Instance-based, net-by-net delay calculation

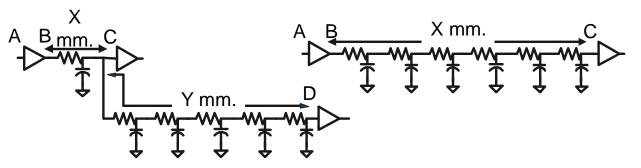

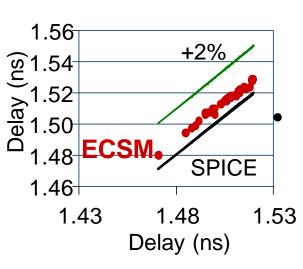

## **Accurate delay calculation**

- Net lengths from ~100um to multiple mm.

- Modeling RC effects critical

- Short / long net segments ratios varied

- Complex RC topologies

- ~2% correlation to SPICE

Improved accuracy  $\rightarrow$  Faster to market, volume

- Design IP: 260K placeable objects; 187K nets

- 10%  $\rightarrow$  5% accuracy: 1,512 of 2,807 STA paths OK

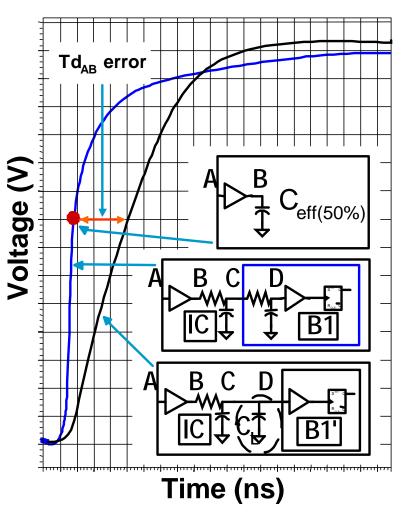

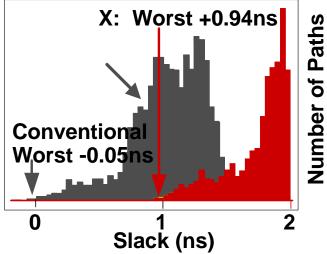

## **Accurate fully-hierarchical timing**

- Signal paths traverse hierarchy

- Block inputs with ~0 − 2 mm. metal → RC delay

- Model block boundary pin input RC as C<sub>L</sub>

- C<sub>L</sub> over-estimates effective capacitance when RC significant

- Driver delay over-estimated

- Design issues

- Latent hold time defects

- Signal nets overdriven for setup margin

- Delay calculation with C<sub>eff(50%)</sub> fits RC waveform at threshold

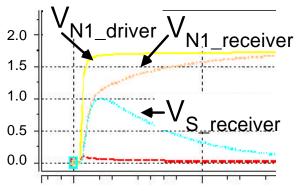

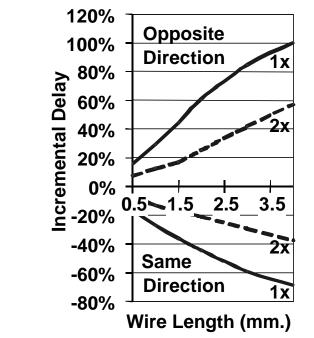

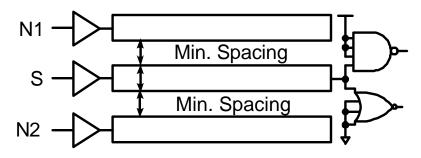

# **Signal integrity**

- All 3 signals switch concurrently

- 1x, 2x: 1-grid, 2-grid spacing

- Crosstalk-induced timing uncertainty

- Effect proportional to victim & aggressor strengths, timing overlap, coupled length & spacing, voltage switching direction, current switching direction, etc.

- Insert buffers ~1.5 2.5 mm.

- Bound timing uncertainty; reduce total delay

- Address impact in Static Timing Analysis

X/2 mm. →

- Reduce setup, bounded hold time margin

X/2 mm.

cādence

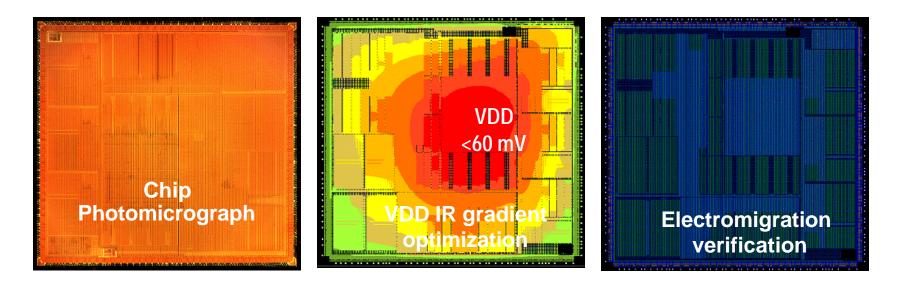

## **Power / current distribution**

• IC power distribution ~1-2 full metal layers; >5-15+ A current

#### • Design needs

- Manage static, dynamic draw

- Ensure valid timing across design envelope

- Ensure electromigration immunity

- Manage noise immunity, simultaneously-switched outputs, inputs

Material used with permission.

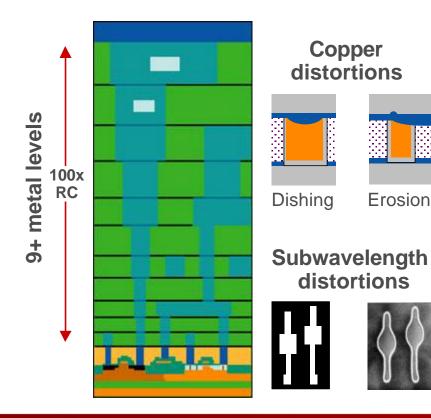

# Wiring is central to nanometer SoC design

- Wiring dominates electrical closure – Differing properties across M1-8

- Wires dominate manufacturability

- RLC variation; vias

- Wiring interacts

- Timing, clocking, crosstalk, signal integrity, power inter-related

Delta VDD  $\rightarrow$  Hold time failure

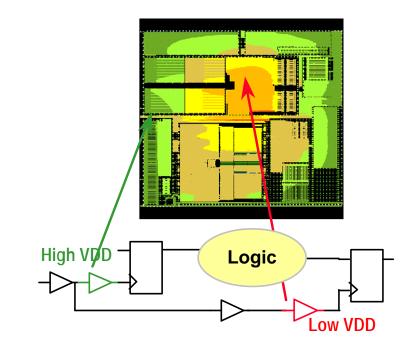

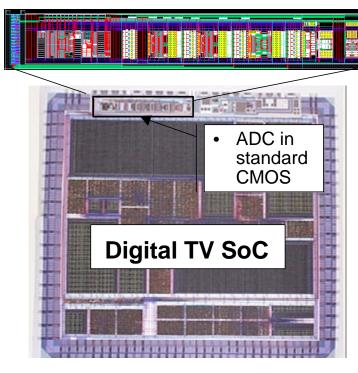

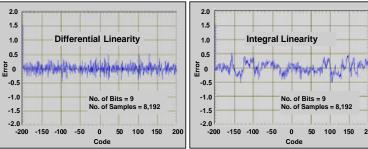

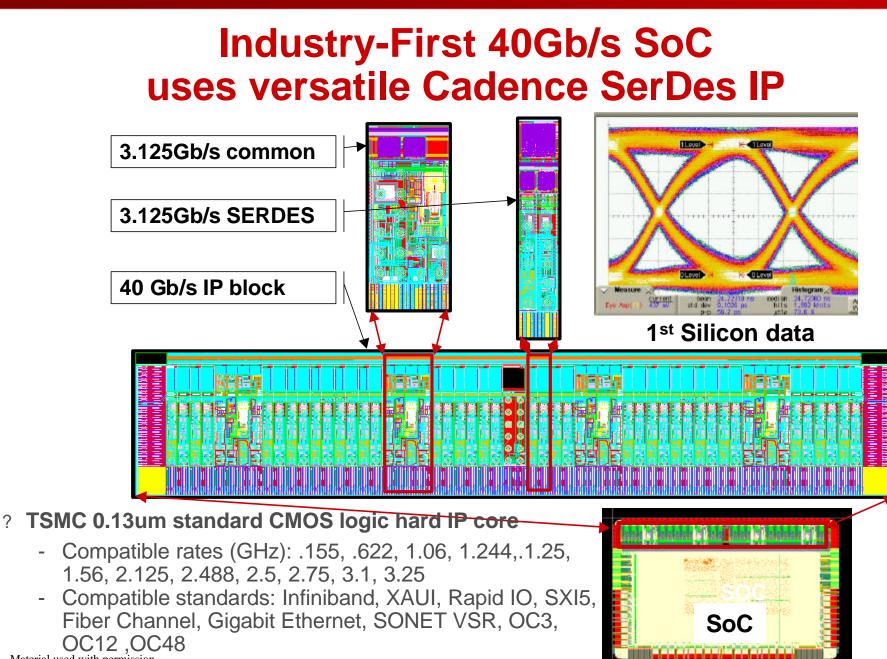

## Most SoCs are mixed-signal

#### Proven std. CMOS analog IP is essential Critical building blocks for SoCs (datacom, RF, consumer)

8b,10b 10-100MHz ADCs 130nm

1.25, 2.5, 3.125G SerDes 130nm

Low Jitter Ring/LC PLLs 130nm

USB 2.0 PHYs

10/100BT Ethernet PHYs

2.4GHz RF XCVRs

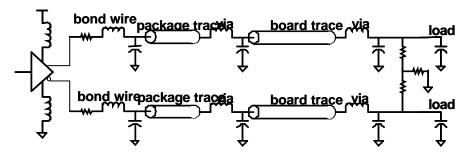

### **Mixed-signal SoCs** Analog IP + SoC design experience is critical

- Electrical / physical design

- Analog / digital isolation

- Quality of RLCs in std. CMOS

- Metal fill effects on analog

- Clk jitter impacts on SNR, BER

- Analog spice/package models

- Board/package/chip co-design

- Signal, power distri., pin locations

- Lead inductance/mutual coupling

- Low R and C I/O ESD

- Verification

- Analog and digital compatibility

- Test requirements

- Tester, measurements, test time

Material used with permission

# Industry-first OC768 framer-mapper processor electrical design

Infineon Technologies, Inc. material used with permission

- 0.15-micron, 8 metal

- Over 50 clock domains

− 100MHz → ~700MHz

- 1,413 bumps flip-chip BGA

- 560 signals @ 622 MHz LVDS

- Some design challenges

- Clock distribution

- Timing

- RDL design

- Power distribution

- Signal integrity

- Full signal transmission path

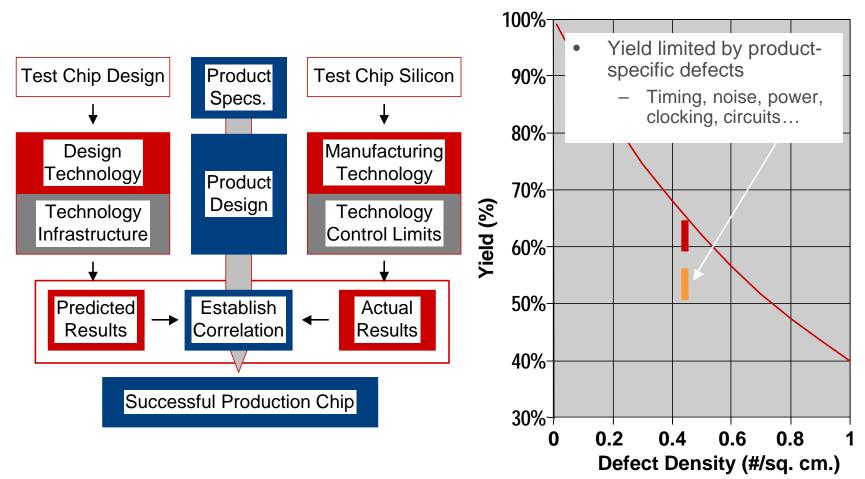

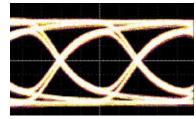

# Industry-first OC768 framer-mapper processor design results

- First silicon success

- 160 Gb/s throughput

Infineon Technologies, Inc. material used with permission.

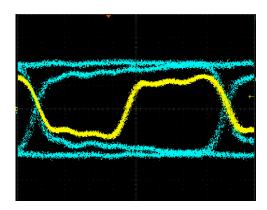

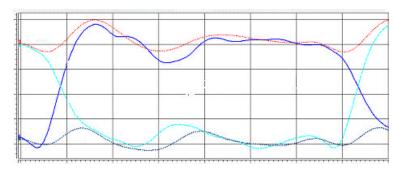

#### **Technology Readiness** On-time delivery of new products with new technology

Validated, robust design margins

- Validate design space across manufacturing boundary limits

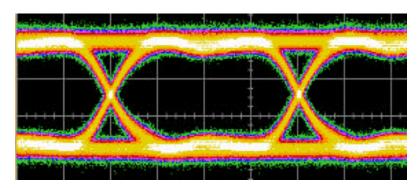

### Analog, digital signal transport

#### No Pre-emphasis

Near end

Far end- 34" Tyco Board

#### With Pre-emphasis

Near end

Far end- 34" Tyco Board

## X-architecture based microprocessor design

- Concurrent improvements to all three metrics

- 19.8% path delay reduction <u>and</u> 10% area reduction

- Performance <u>and</u> power <u>and</u> cost (area, # vias)

| Tile | Reduction |      |  |

|------|-----------|------|--|

|      | Wire      | Via  |  |

| A    | 25 %      | 37 % |  |

| В    | 13 %      | 28 % |  |

| C    | 21 %      | 35 % |  |

| D    | 22 %      | 32 % |  |

Igarashi, et. al., "A Diagonal Interconnect Architecture and its Application to RISC Core Design," 2002 International Solid State Circuits Conference, Feb. 2002. Material used with permission.

### **Design partnerships critical to success**

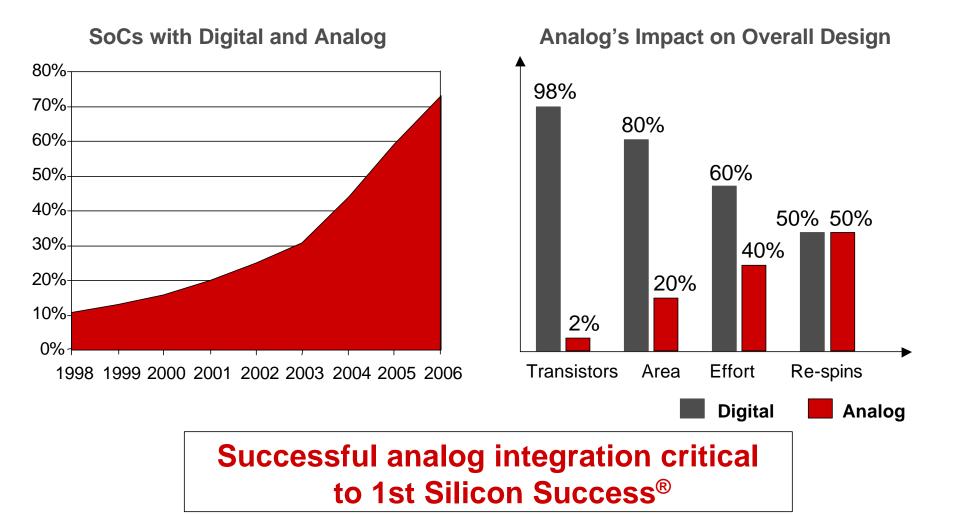

- Rapid growth in SoC market

- \$23B in 2002 to \$53B in 2006; 59% → 80% SoCs

- Design complexity growing exponentially on many dimensions: Conventional methods do not scale

- Leading-by-Design accelerates / focuses SoC design

- Mixed-signal design methodology, fully-hierarchical design, physical synthesis, nonlinear delay calculation, power distribution, signal integrity, transmission line effects, analog IP

- Design partnerships critical to success

- Specialize, innovate and partner to build the product delivery value chain

- First-to-Market and First-to-Volume drives business success

- First silicon success critical