# Software Optimization Workshop for Real Time Video Applications

By

Dr. Jagadeesh Sankaran,

Member of the Group of Technical Staff,

DSP Software Applications Engineer,

Streaming Media Team.

# **COURSE ABSTRACT**

Software techniques that are crucial to extracting performance from DM642 DSP for video applications.

Techniques That Will be Reviewed a) Code Optimization Techniques.

- b) System Optimization Techniques.

- c) Showcase DM642 performance for video applications.

My algorithm is in C, TI says it has an optimizing compiler that can get up to 80% of the performance in assembly coding from C, yet my performance is terrible.

I have used the correct instructions in C using intrinsics yet the compiler is showing a high dependency bound, and hence my performance is messed up.

I do not believe in the compiler, I always write my own hand coded assembly.

This one algorithm consumes my whole chip (or nearly) and hence it cannot be performed on a DSP. TI C6000 DSP's are hard to optimize.

Does not matter whether the DSP runs at 600MHz, 720MHz if the code that is written does not take advantage of the available units and the instructions of the architecture.

VLIW is a good architectural style in the hands of developers who know how to expose the available parallelism for the compiler to take advantage of.

An act, process, or methodology of making something fully perfect, functional, or effective as possible.

Continuous process of refinement in which code being optimized executes faster and takes fewer cycles, until a specific objective is achieved (real-time execution).

How do we know when to stop ??

**Optimum:**

Greatest degree attained or attainable under specified or implied conditions.

How do we figure out how fast a given algorithm can run on a given architecture?

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

#### **Connecting Real People with Real Solutions**

### How do we determine the Optimum

Analysis is specific to the algorithm.

- b) Number of multiply operations needed.

- c) Number of logical operations needed.

- d) Size of the data that is being worked on shorts, bytes.

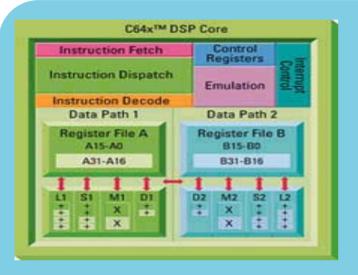

Are there any data related dependencies between the computations that will prevent performing "K" computations in parallel?

If there are no data dependencies then we should take only as many cycles as the most intensive arithmetic operation divided by how many such arithmetic operations can be performed on the architecture in a given cycle, which is the raw throughput of the architecture.

Because of the data dependency how much does the performance degrade from the raw throughput of the architecture.

##

# TI Developer Conference

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

#### **Connecting Real People with Real Solutions**

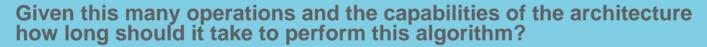

1 Execute Cycle:

32-bit Registers: 64

2 Data paths: A and B

Units:

L: Logical units, AND, OR, XOR

S: Shifter unit, ADD, SHR, SHL, Extract, Branch

D: Load/Store unit

M: Multiply unit

**Predication Registers:**

A0, A1, A2, B0, B1, B2

Fetch packet: 256 bits

|       | -       |       |             |          |               |         |

|-------|---------|-------|-------------|----------|---------------|---------|

|       | BDEC    | .s1   | LOOP,       | A_i      |               | ;[24,1] |

| [!A_p | d]ADD   | .L2X  | B_t0,       | A_t0,    | B_temp1       | ;[24,1] |

| [!A_p | d]ADD   | .L1   | A_prodC,    | A_prodD, | A_v0          | ;[24,1] |

| П     | DOTP2   | .M2   | B_x5x4,     | B_y4y3,  | B_prod6       | ;[16,2] |

| П     | DOTP2   | .M1   | A_x3x2,     | A_y2y1,  | A_prod5       | ;[16,2] |

| П     | PACKLH2 | .S2   | в_у7у6,     | B_y5y4,  | в_убу5        | ;[16,2] |

| П     | LDDW    | .D2T2 | *B_xptr++[2 | 1,       | B_x7x6:B_x5x4 | ;[8,3]  |

| 11    | LDDW    | .D1T1 | *A xptr++[2 | 1.       | A x3x2:A x1x0 | ;[ 8,3] |

# TI Developer Cose FCT WARE PIPELINING

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

# **Code Optimization Goals**

Code should be written only after analyzing the optimum to serve as a proof of concept that the analysis performed can indeed translate to actual performance.

Several issues with code and code generation that may limit the performance obtained from compilers.

Is there any preferred/systematic methodology to perform code development for developers to share their results.

This systematic methodology can be provided back to TI (if there are no IP issues) for them to improve the compiler or provide suggestions on ways and means to improve the performance.

### **Code Optimization Methodology**

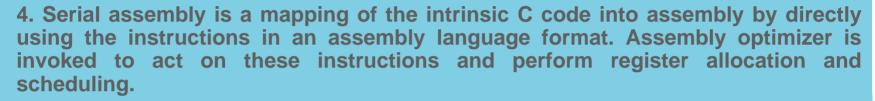

Six different flavors of the same function being optimized.

1. Natural C code or Committee code. Text Book implementation of the algorithm to be optimized. Used to compare other flavors for speedup and for bit-exactness. This can also be viewed as the golden C code.

Optimized C code can use manual loop unrolling of inner and outer loops. It can also use compiler pragma's and \_nasserts to the compiler to inform it about the alignment of various input and output arrays. This allows the compiler to perform automatic SIMD transformations, which works in some

cases but not all.

3. Intrinsic C code allows for the use of all the instructions on the given architecture and can be used to express any assembly language code in a high level environment. The only limitation is circular addressing support. The compiler may not be able to perform memory alias disambiguation or partition instructions correctly between the two data paths of the architecture.

5.Partitioned serial assembly performs partitioning of the instructions by appending a .1 or .2 in front of the unit. Load/Store operations can be partitioned as .DxTx to indicate which side the pointer comes from and to which side the loaded value lands. The use of .1x shows that the second operand comes from the opposite data path.

Both partitioned and linear assembly do not have any latencies that the programmer must take care of. The assembly optimizer figures out latencies and dependencies and then performs instruction scheduling.

6. Of course, there is always hand code where the user does instruction set selection, register allocation and the latencies of the instructions.

## **Code Optimization Methodology**

#### **Connecting Real People with Real Solutions**

Intrinsic C code: More effort. However very flexible method to map out all the instructions and the algorithmic transformations that are needed for optimizing the algorithm. Can be very useful for mapping algorithm to serial assembly.

Serial assembly and Partition serial assembly allow further control and mapping to units and remove scheduling issues associated with C code.

#### All flavors except hand code can benefit as follows:

a. Improvements to the compiler and code generation tools.

b. Can be re-scheduled to avoid new architecture restrictions. eg. C64x cross path stall can be avoided in C62x code by re-compiling.

c. Memory dependencies and latencies are automatically taken care of by tools, whereas hand code assumes a fixed latency. Hence serial and partitioned serial assembly code are pipeline independent but yet high performance.

**CHOICE IS IN YOUR HANDS**

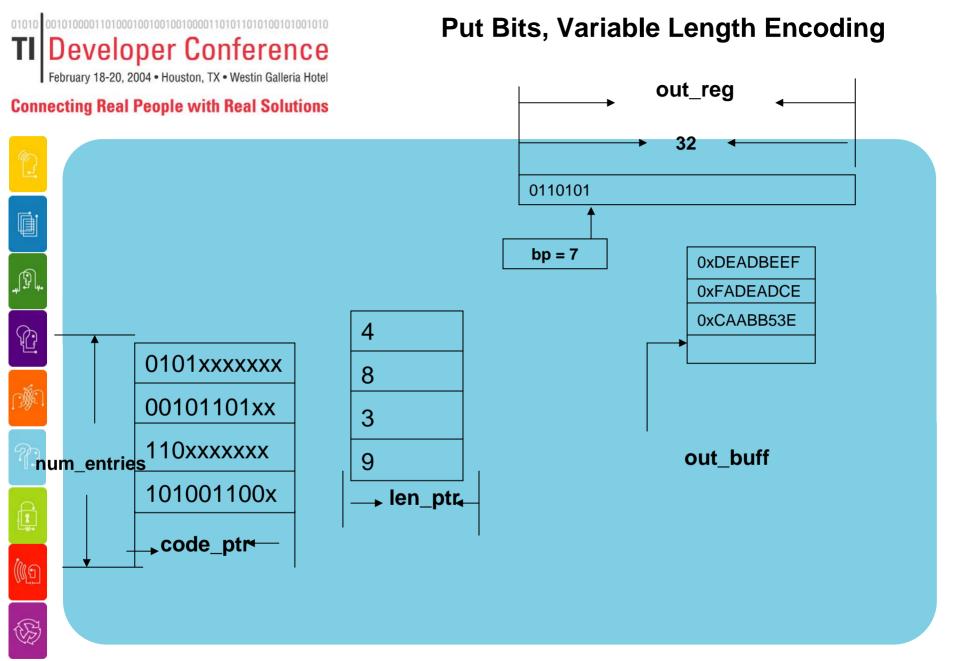

1) Motion Estimation (8x8) search for minimum SAD value. Put Bits, Variable length encoding.

**Image/Video Processing Lab Examples on DM642**

3) Convolution, Quantization conv\_3x3

4) Threshold operation (Rate Control).

Each example will be optimized using the code optimization methodology outlines earlier in six flavors as discussed earlier.

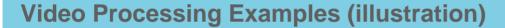

Find (x, y) that is the best match for the 8x8 region in blue that we are searching in a green region of size X,Y. The (x, y) may not be word or double word aligned. Each pixel is differenced and the sum of absolute values is added. The value of (x,y) is the location which yields the minimum such value.

### Developer Conference February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

#### Natural C Code for mad 8x8

```

void mad 8x8 cn

const unsigned char *restrict refImg,

const unsigned char *restrict srcImg,

int pitch, int sx, int sy,

unsigned int *restrict motvec

int i, j, x, y, matx, maty;

unsigned matpos, matval;

matval = \sim 0U; matx = maty = 0;

pitch = sx;

for (x = 0; x < sx; x++)

for (y = 0; y < sy; y++)

unsigned acc = 0;

for (i = 0; i < 8; i++)

for (j = 0; j < 8; j++)

acc += abs(srcImg[i*8 + j] - refImg[(i+y)*pitch + x + j]);

if (acc < matval)</pre>

matval = acc; matx = x; maty = y;

= (0xffff0000 & (matx << 16)) | (0x0000ffff & maty);

matpos

motvec[0] = matpos;

motvec[1] = matval;

```

## **Analysis Of Optimal Implementation of**

mad\_8x8 for C64x DSP

#### **Connecting Real People with Real Solutions**

Number of Byte loads required: 128 \* sx \* sy.

Number of Absolute and differences required: 64 \* sx \* sy.

Number of additions required: 64 \* sx \* sy.

Number of compares: sx \* sy .

#### **Observations**

a. C64x DSP can perform 8 sum of absolute differences per cycle. Since 64 SAD computations need to be performed for a 8x8 block, this can at best be performed in 8 cycles provided we can load the required data within 8 cycles.

b. The C64x has a load/store bandwidth of 16 bytes/cycle if the loads are performed at an aligned double address. It has a load/store bandwidth of 8 bytes/cycle if the loads are performed at a non-aligned address.

Since the data needs to be loaded from any byte location, the addresses are not aligned to a word or a double word boundary and hence the C64x does not have the required bandwidth to load both source and reference data in 8 cycles. How do we overcome this ???

# Analysis Of Optimal Implementation of mad\_8x8 for C64x DSP

#### **Connecting Real People with Real Solutions**

Since we do not have the required load bandwidth, we should look for opportunities to re-use the data. This can be done by loading the 8x8 region into register file as it never changes during the loop. It is essentially loop invariant and hence can be kept in registers in 16 registers. Hence this data is read outside the loop into registers.

Given that we have solved the load bandwidth problem, there seems to be nothing limiting us from achieving an 8 cycle loop for computing a 8x8 minimum absolute difference.

Before we start it is interesting to observe the compiled output for natural C code to see our current performance.

For a search region of 32x64 the natural C code takes 22254 cycles to perform 32 \* 64 \* 64 = 131072 achieving 5.88 SAD/cycle.

#### **Analysis Of Optimal Implementation of** mad 8x8 for C64x DSP

```

The performance obtained from natural C code is more impressive than usual as the

compiler unrolls the two inner loops and uses the subabs4 instructions on its own

performing 16 SUBABS4 instructions in 10 cycles in the inner loop to achieve a 6.4

SAD/cycle.

```

```

for (x = 0; x < sx; x++)

for (y = 0; y < sy; y++)

Collapse these two loops together.

#pragma UNROLL(8);

for (i = 0; i <

abs(srcImg[i*8

8;

i++) acc

01

refImg[(i+y)*pitch

abs(srcImg[i*8

0])

2]

refImg[(i+y)*pitch + x + 1])

abs(srcImg[i*8

+ x + 2])

refImg[(i+y)*pitch

abs(srcImg[i*8

+ x + 3])

refImg[(i+y)*pitch

abs(srcImg[i*8

4]

abs(srcImg[i*8

refImg[(i+y)*pitch

4])

refImg[(i+y)*pitch

51)

abs(srcImg[i*8

abs(srcImq[i*8

refImg[(i+y)*pitch

6])

refImg[(i+y)*pitch + x + 7]);

if (acc < matval) { matval = acc; matx = x; maty = y; }</pre>

```

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

```

******* Loop Control**********

SUB B v1, 1, B v1

MV A p1, A f

[!B v1] MV A hfix, A f

[!B v1] MV B v dim, B v1

***** Row 7 ****

LDNDW *A ref d(A p7), A ref7h:A ref7l

SUBABS4 B src7h, A ref7h, B err7h

SUBABS4 A src71, A ref71, A err71

DOTPU4 B err7h, B k one, B mad 7

DOTPU4 A err71, A k one, A mad 7

******* Row 6 **********

LDNDW *A ref d(A p6), B ref6h:B ref6l

SUBABS4 B src6h, B ref6h, B err6h

SUBABS4 A src61, B ref61, A err61

DOTPU4 B err6h, B k one, B row 6

DOTPU4 A err61, A k one, A row 6

ADD B row 6, B mad 7, B mad 6

ADD A row 6, A mad 7, A mad 6

******* Check for best match ******

ADD B mad 0, A mad 2, B mad

CMPGT2 B best, B mad, B bst

ADD B hvl, 1, B hvl

[B bst] MV B mad, B best

[B bst] SUB B hvl, 1, B bhvl

[A i] BDEC loop, A i

```

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

```

mad8x8 loop:

ADD

.D2

B hvl,

B hvl

; [25,1]

1,

DOTPU4

.M1

; [17,2]

ADD

.S2

; [17,2]

DOTPU4

.M2

; [ 9,3]

SUBABS4 .L1

B src5h, A ref5h,

SUBABS4 .L2X

B err5h

; [ 9,3]

*\overline{A} ref d(A p7),

A ref7h:A ref7l ; [ 1,4]

LDNDW

.D

.S1

A f

MV

A p1,

; [ 1,4]

loop 1:

A_row_0, B_mad_0, B_mad_0

B_row_1, B_mad_2, B_mad_1

A_row_3, A_mad_4, A_mad_3

A_src41, B_ref41, A_err41

B_src4h, B_ref4h, B_err4h

.D2X

; [26,1]

ADD

.S2

ADD

;[18,2]

.S1

; [18,2]

ADD

.L1X

SUBABS4

; [10,3]

SUBABS4 .L2

; [10,3]

B_err5h, B_k_one,

DOTPU4

. M2

B row 5

; [10,3]

DOTPU4

.M1

A err61, A k one,

A row 6

; [10,3]

LDNDW

*\overline{A} ref d(A p6),

B ref6h:B ref6l ; [ 2,4]

.D

loop 2:

mad8x8 loop,

[A i] BDEC

Ai

.S1

; [27,1]

.S2X

B mad \overline{0}, A mad 2, B mad

; [27,1]

ADD

B_src2h, B_ref2h, B_err2h

A_src31, A_ref31, A_err31

B_err4h, B_k_one, B_row_4

.L2

; [11,3]

SUBABS4

.L1

SUBABS4

; [11,3]

DOTPU4

; [11,3]

. M2

A err51, A k one,

A row 5

; [11,3]

DOTPU4

.M1

*\overline{A} ref d(A p3),

LDNDW

.D

B v1,

1,

; [ 3,4]

SUB

.D2

B v1

```

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

```

loop 3:

B best,

B mad,

B bst

CMPGT2

.S2

; [28,1]

B_src1h, A_ref1h, B_err1h

B_err2h, B_k_one, B_row_2

A_src21, B_ref21, A_err21

SUBABS4 .L2X

; [12,3]

DOTPU4

.M2

; [12,3]

SUBABS4 .L1X

; [12,3]

A err41, A k one,

B row 6, B row 7,

A row 4

DOTPU4

. M1

; [12,3]

.D2

B mad 6

ADD

; [12,3]

*\overline{A} re\overline{f} d(A p5),

A \text{ ref} \overline{5} h : A \text{ ref} 51 ; [4,4]

LDNDW

.D

[!B v1]MV

.S1

A h fix,

Af

; [4,4]

loop 4:

[ B bst]SUB

.D2

B hvl,

1,

B bhvl

; [29,1]

B_mad, B_best

A_row_2, A_mad_3,

A_src01, B_ref01,

B_src0h, B_ref0h,

B_err1h, B_k_one,

.S2

[ B bst]MV

; [29,1]

.S1

ADD

A mad 2

; [21,2]

.L1X

A err01

; [13,3]

SUBABS4

SUBABS4 .L2

B err0h

; [13,3]

DOTPU4

B row 1

. M2

; [13,3]

DOTPU4

. M1

A err31,

A k one,

A row 3

; [13,3]

[A i]LDNDW

.D

*\overline{A} ref d(A p4),

B ref \overline{4}h: B ref 41 ; [5,4]

DOTPU4

B row 0

B k one,

; [14,3]

.M2

B err0h,

A src11,

A_ref11,

A k one,

A err11

.L1

SUBABS4

; [14,3]

.M1

A err21,

; [14,3]

DOTPU4

A row 2

B row 5,

.D2

B mad 6,

B mad 5

ADD

; [14,3]

ADD

.S1

A row 6,

A row 7,

A mad 6

; [14,3]

*\overline{A} re\overline{f} d(A p2),

B ref \overline{2}h: B ref 21 ; [6,4]

[A i]LDNDW

.D

B \overline{src7h},

[A i]SUBABS4 .L2X

A ref7h,

B err7h

; [ 6,4]

B v dim,

[!B v1]MV

.S2

B v1

; [ 6,4]

```

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

#### **Connecting Real People with Real Solutions**

|         | A<br>D                          | ( |

|---------|---------------------------------|---|

|         | A<br>[A_i]L<br>[A_i]S<br>[A i]D |   |

| <b></b> | [A_i]S                          |   |

| P       | A<br>A<br>A                     |   |

|         | [A i]L                          | ı |

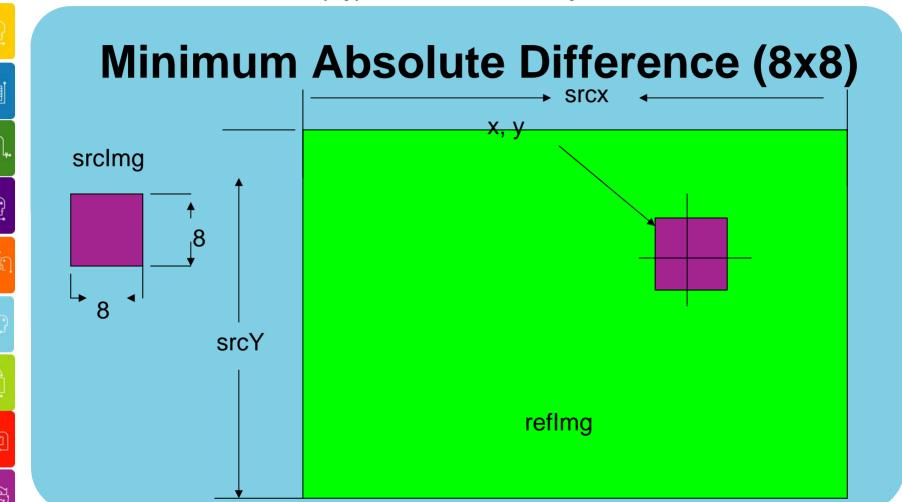

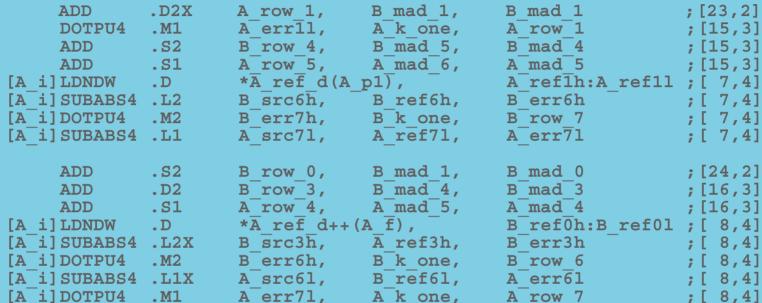

64 sum of absolute differences is computed in 8 cycles at the peak throughput rate of 8/cycle. Also as suspected the full non-aligned load bandwidth of 64 bits/cycle is used.

The performance of the different flavors of code is now summarized in the next slide.

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

#### **Connecting Real People with Real Solutions**

### MAD\_8x8 Performance Summary for (64x32)

| CN              | СО              | Intrin.         | Serial<br>Assem. | Part.<br>Serial<br>Assem. | Hand<br>Assem.       |

|-----------------|-----------------|-----------------|------------------|---------------------------|----------------------|

| 22254<br>cycles | 22254<br>cycles | 22254<br>cycles | 20561<br>cycles  | 16454<br>cycles           | 16458<br>cycles      |

| 1280<br>bytes   | 1280<br>bytes   | 1248<br>bytes   | 1056<br>bytes    | 1280<br>bytes             | 800<br>bytes<br>7.96 |

|                 |                 |                 |                  |                           | MAD/cycle            |

# Put Bits, Variable Length Encoding

```

void put bits

unsigned int

*code ptr,

unsigned int

*len ptr,

int

bp,

unsigned char

*out buf,

num entries,

int

unsigned int

out reg

int i:

unsigned int code, len, cws, r;

for( i = 0; i < num entries; i++)</pre>

code = code ptr[i]; len = len ptr[i];

cws = (code >> bp);

if (len) out_reg = out_reg

CWS;

bp = (bp + len); r

= (bp - 31);

if (r)

*out buf++ = out reg;

out reg = (code << (len - r));

= len - r;

bp

4 cycle loop from C Code

```

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

```

L2: ; PIPED LOOP KERNEL

```

```

.S2

B8,B6,B6

; |30| <0,9>

.L2X

MV

A1

A5,B7

; |38| <0.9> Define a twin register

AOI OR

.D1X

B8,A3,A3

|30| <0.9> Define a twin register

ROTL

|27| <1,5> Split a long life

.M1

A8,0,A0

ADD

.S1

A8,A4,A4

[31] <1,5> ^

LDW

*B4++,B8

; |26| <2,1>

STB

B6,*B5++

.D2T2

; |36| <0,10>

A1] SHL

.S1X

B9,A5,A3

; |37| <0,10>

ROTL

.M2

B8,0,B9

; |26| <1,6> Split a long life

ADD

.L2X

|31| <1,6> Define a twin register

A8,B7,B7

.S2

SHRU

B8,B7,B8

|30| <1,6>

ADD

.D1

A6.A4.A2

: <1.6> ^

ROTL

.M1

A2,0,A1

; <1,7> Split a long life

BO] BDEC

.S2 L2,B0

; |40| <1,7>

SUB

.D1

A0,A2,A5

: |37| <1.7> ^

MV

.D2X

A3,B6

|37| <0,12> Define a twin register

A5,A4

.S1

A21

MV

; |38| <1,8> ^

.DW

.D1T1

*A7++.A8

; |27| <3,0>

```

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

#### **Connecting Real People with Real Solutions**

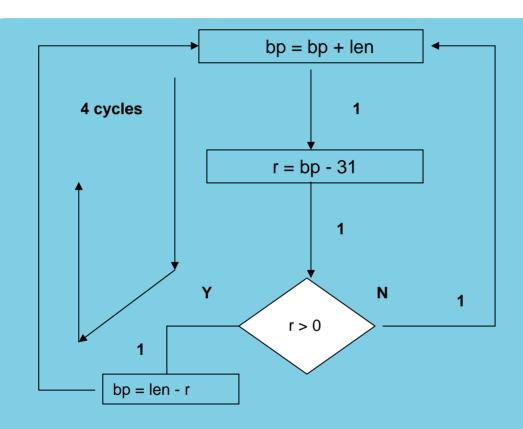

**Put Bits: Variable Length Encoding, Complexity Analysis**

**Put Bits: Variable Length Encoding, Complexity Analysis**

February 18-20, 2004 . Houston, TX . Westin Galleria Hotel

#### **Connecting Real People with Real Solutions**

# Optimized Put Bits Routine

```

void put bits

*code ptr,

unsigned int

unsigned int

*len ptr,

int

bp,

unsigned char

*out buf,

int

num entries,

unsigned int

out req

int i;

unsigned int code, len, cws, cwl, r;

for( i = 0; i < num entries; i++)</pre>

code = code ptr[i];

= len ptr[i];

= (code >> bp);

= (code << (32 - bp));

if (len) out reg = out reg

= (bp + len);

bp

= (bp - 31);

r

= bp & 31;

bp

if (r)

*out buf++ = out reg;

out \overline{req} = cwl;

```

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

#### **Connecting Real People with Real Solutions**

# 3 cycle loop for put bits.

| L2:                   | ; I            | PIPED LOG                        | OP KERNEI                           | ı                                                         |      |                                                                                                |

|-----------------------|----------------|----------------------------------|-------------------------------------|-----------------------------------------------------------|------|------------------------------------------------------------------------------------------------|

|                       | [В0]           | SHL<br>MVD<br>BDEC<br>LDW        | .S1X<br>.M1<br>.S2<br>.D2T2         | B16,A6,A6<br>A0,A1<br>L2,B0<br>*B7++,B8                   | ; 2  | 30   <0,9> 27   <1,6> Split a long life 42   <1,6> 30   <3,0>                                  |

|                       | [ A1]<br>[ A0] | ADD<br>OR<br>ADD<br>SHRU<br>LDW  | .D2<br>.S1X<br>.L2X<br>.S2<br>.D1T1 | B4,B9,B1<br>B5,A5,A5<br>A0,B6,B9<br>B16,B6,B5<br>*A7++,A0 | ; 3; | 34   <0,10><br>32   <0,10><br>33   <1,7><br>32   <1,7><br>27   <3,1>                           |

| and the second second | [ B1]<br>[ B1] | MV<br>STB<br>EXTU<br>SUB<br>ROTL | .L1<br>.D1T1<br>.S2<br>.S1X<br>.M2  | A6,A5<br>A5,*A4++<br>B9,27,27,B6<br>A3,B6,A6<br>B8,0,B16  | ; 3; | 40   <0,11> ^<br>39   <0,11> ^<br>35   <1,8> ^<br>30   <1,8> ^<br>30   <2,5> Split a long life |

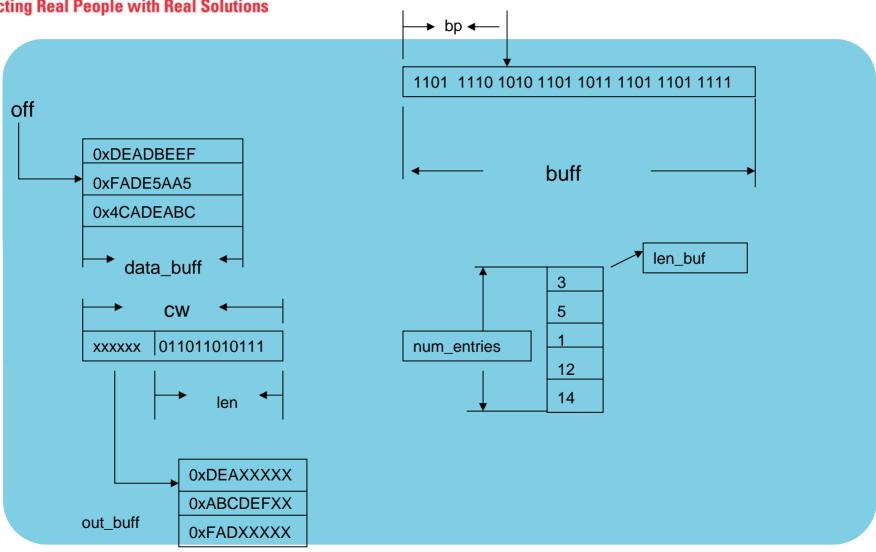

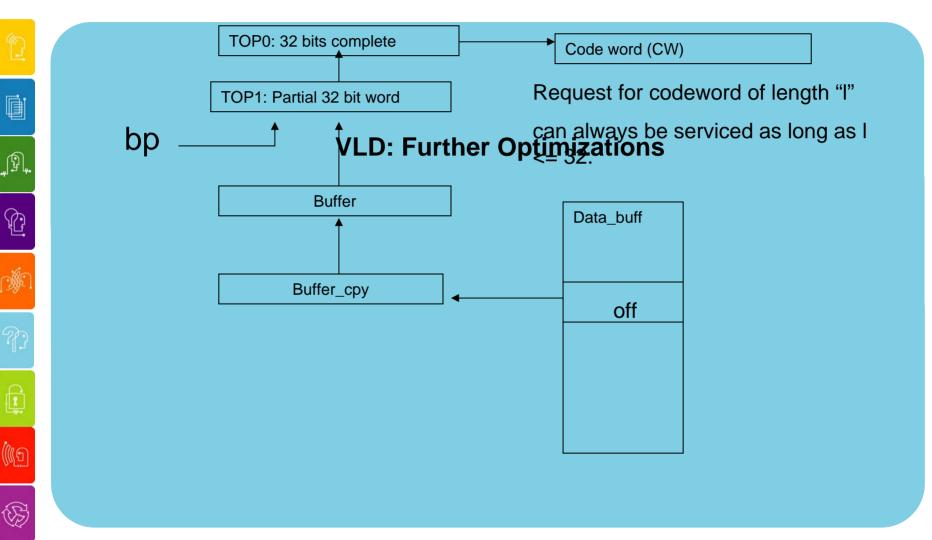

# **Get Bits, Inverse of Put Bits**

# **Get Bits: Function to Mimic Variable Length Decoding**

```

void get bits

unsigned char

*len buf,

unsigned int

*data buf,

unsigned int

*bptr,

unsigned int

*buffer,

*offset,

unsigned int

unsigned int

num entries,

unsigned int

*output

int i;

unsigned int cw;

unsigned int bp

= *bptr;

unsigned int buff = *buffer;

unsigned int off = *offset;

unsigned int length;

unsigned int rem;

```

# **Get Bits: Function to Mimic Variable Length Decoding**

```

for (i = 0; i < num entries; i++)</pre>

length = len buf[i];

if (length <= bp)</pre>

= (buff >> (32 - length));

buff = (buff << length);</pre>

bp = bp - length;

else

cw = (buff >> (32 - bp));

buff = data buf[off];

off++;

rem = (length - bp);

cw = (cw << rem) | (buff >> (32 - rem));

buff = (buff << rem);</pre>

bp = 32 - rem;

output[i] = cw;

*buffer = buff;

*offset = off;

*bptr = bp;

```

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

#### **Compiler Analysis for Natural C code**

```

SOFTWARE PIPELINE INFORMATION

: *

Loop source line

: 23

Loop opening brace source line

Loop closing brace source line

Known Minimum Trip Count

Known Max Trip Count Factor

; *

Loop Carried Dependency Bound(^): 4

Unpartitioned Resource Bound

; *

Partitioned Resource Bound(*)

Resource Partition:

; *

A-side

B-side

.L units

.S units

.D units

.M units

.X cross paths

; *

.T address paths

; *

Long read paths

Long write paths

Logical ops (.LS)

(.L or .S unit)

Addition ops (.LSD)

; *

(.L or .S or .D unit)

Bound(.L .S .LS)

; *

Bound(.L .S .D .LS .LSD)

; *

Searching for software pipeline schedule at ...

; *

ii = 5 Schedule found with 3 iterations in parallel

```

### Assembly Code From C for Get Bits/ VLD 5 cycle loop

| L4: ; ]                                               | PIPED LOOP KEF                                      | RNEL                                             |                                                                                                                |

|-------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| [!B1]<br>   [ B1]<br>   [ B1]<br>   [ B1]             | SUB .D2 SUB .S1X SHL .S2 MV .L2                     | B21,B22,B21<br>A4,B21,A5<br>B20,B4,B6<br>B19,B21 | ;   30   <0,9><br>;   37   <0,9> Define a twin register<br>;   38   <0,9><br>;   39   <0,9> ^                  |

| [ B1]<br>   [!B1]<br>   [!B1]                         | ADD .D1 SHRU .S2X SHL .S1 CMPGTU .L2 LDBU .D27      | A6,B5,B20<br>A6,A4,A6<br>B22,B21,B0              | ;  36  <0,10><br>;  28  <0,10><br>;  29  <0,10><br>; <1,5><br>;  25  <2,0>                                     |

| [ B1]<br>   [ B1]<br>   [ B0]<br>   [ B0]<br>   [ B0] | SHL .S1 SHRU .S2X ROTL .M2 SUB .D2 SUB .L2 LDW .D17 | B0,0,B1<br>B22,B21,B4<br>B17,B22,B8              | ;  40  <0,11><br>;  38  <0,11><br>; <1,6> Split a long life<br>;  37  <1,6><br>;  38  <1,6> ^<br>;  29  <1,6>  |

| [ B1]<br>   [ B0]<br>   [ B0]                         | OR .L2<br>SUB .D2<br>ADD .S2                        | B7,B6,B20<br>B17,B21,B9<br>B21,B8,B19            | ;   38   <0,12><br>;   28   <1,7><br>;   38   <1,7>                                                            |

| [!B1]<br>[B1]<br>[A0]                                 | STW .D27 SUB .L2 MV .D1X SHRU .S2X BDEC .S1         | B17,B22,B5<br>B22,A4<br>A6,B9,B20                | ;   43   <0,13><br>;   28   <1,8><br>;   25   <1,8> Define a twin register<br>;   28   <1,8><br>;   44   <1,8> |

# Optimized C Code for get bits/VLD

```

for (i = 0; i < num entries; i++)</pre>

length = len buf[i];

cw = (buff >> (32 - length));

buff

= (buff << length);</pre>

bp c = bp - length;

rem = (length - bp);

flag = (length <= bp);</pre>

buff t = data buf[off];

fld \bar{t} = (buf\bar{f} t \gg (32 - rem));

buff n = (buff t << rem);</pre>

if (flag) bp = bp c;

if (!flag) bp = 32 - rem;

if (!flag) off++;

if (!flag) cw = cw | fld t;

if (!flag) buff = buff n;

output[i] = cw;

*buffer = buff;

*offset = off;

*bptr = bp;

```

#### **COMPILER ANALYSIS OF OPTIMIZED C CODE**

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

#### **Connecting Real People with Real Solutions**

|    | SOFTWARE PIPELINE INFORMATI | OIV         |      |         |     |    |      |      |       |  |

|----|-----------------------------|-------------|------|---------|-----|----|------|------|-------|--|

| :  | Loop source line            |             | : 3  | 2       |     |    |      |      |       |  |

| k  | Loop opening brace sourc    | e line      |      |         |     |    |      |      |       |  |

| *  | Loop closing brace sourc    |             |      |         |     |    |      |      |       |  |

| *  | Known Minimum Trip Count    |             |      |         |     |    |      |      |       |  |

| *  | Known Max Trip Count Fac    |             |      |         |     |    |      |      |       |  |

| *  | Loop Carried Dependency     |             |      |         |     |    |      |      |       |  |

| *  | Unpartitioned Resource B    |             |      |         |     |    |      |      |       |  |

| *  | Partitioned Resource Bou    |             |      |         |     |    |      |      |       |  |

| *  | Resource Partition:         |             |      |         |     |    |      |      |       |  |

| *  |                             | A-side      | В    | -side   |     |    |      |      |       |  |

| *  | .L units                    | 0           |      | 2       |     |    |      |      |       |  |

| *  | .S units                    | 3           |      | 2       |     |    |      |      |       |  |

| k  | .D units                    | 2           |      | 1       |     |    |      |      |       |  |

| *  | .M units                    | 0           |      | 0       |     |    |      |      |       |  |

| *  | .X cross paths              | 3 2         |      | 4       |     |    |      |      |       |  |

| *  | .T address paths            | 2           |      | 1       |     |    |      |      |       |  |

| *  | Long read paths             | 1           |      | 0       |     |    |      |      |       |  |

| *  | Long write paths            | 0           |      | 0       |     |    |      |      |       |  |

| *  | Logical ops (.LS)           | 2<br>6<br>3 |      |         | (.L | or | .s u | nit) |       |  |

| *  | Addition ops (.LSD)         | 6           |      | 3       | (.L | or | .S o | r .D | unit) |  |

| le | Bound(.L .S .LS)            |             |      | 3       |     |    |      |      |       |  |

| k  | Bound(.L .S .D .LS .LSD)    | 5*          |      | 4       |     |    |      |      |       |  |

| ř. |                             |             |      |         |     |    |      |      |       |  |

| k  | Searching for software p    | ipeline s   | sche | dule at |     |    |      |      |       |  |

Loop carried dependency bound has gone down, which is good. We are on the right track.

February 18-20, 2004 . Houston, TX . Westin Galleria Hotel

```

LOOP:

*A len++,

A lcw

; length of code word needed

LDW

A lcw,

B lcw

; copy of length

MV

SUB

A 32,

A lcw,

A rs

rs = 32 - 1cw

SUB

B 32,

A lcw,

B rs

: rs = 32 - 1cw

A top0, A rs,

SHRU

A top0 rs

; top0 rs = top0 >> rs

A top0 rs, *A optr++

: Store out

STW

; Keep top0 at 32 bits

A top0,

A lcw,

A top0 ls

; top0 ls = top0 << lcw

SHL

B top1,

B rs,

B top1 rs

; top1 rs = top1 >> rs

SHRU

A top0 ls, B top1 rs, A top0

; top0 = top0 ls | top1 rs

OR

; New almost 32 bit top0

SHL

B top1,

B lcw,

; top1 = top1 << lcw

B top1

Вp,

B lcw,

; p = p + lcw

ADD

Вр

r = p - 32

SUB

B 32,

Br

Вр,

AND

Вp,

B 31,

Вр

p = p % 32

-1,

A rw

; Check for overflow

CMPGT

Br,

SUB

B 32,

; Left shift for

Br,

B ru

SHRU

B buff,

B ru,

B top1 ru

; Missing bits

[A rw]OR

A top0,

B top1 ru, A top0

; Complete 32 bits

; Update top1

[A rw] SHL B buff,

Br,

B top1

[A rw] MV B buff cpy, B buff

; Update buff

*B ptr++, B buff cpy

; Load buff cpy

[A rw] LDW

[A it] SUB.1 A it,

A it

1,

[A it]B.1 LOOP

; Branch

```

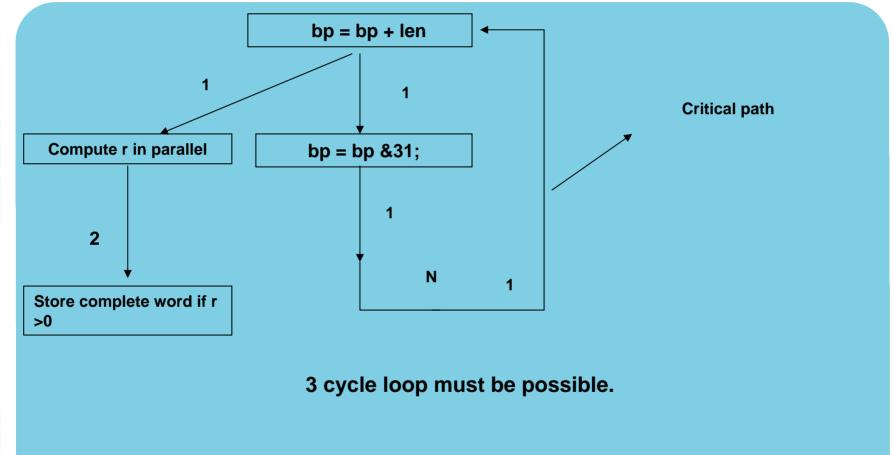

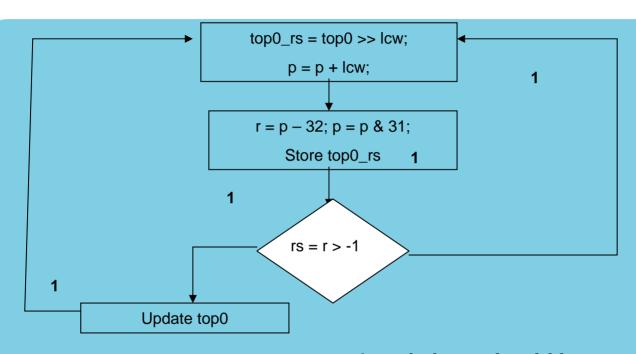

## GET BITS COMPLEXITY ANALYSIS

#### **Connecting Real People with Real Solutions**

4 cycle loop should be possible.

Recurrence is on top0 of length 3 cycles.

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

#### **Connecting Real People with Real Solutions**

| LOOP:                                                        |                                     |                                                             |                                                         |                                      |                                                                                                                              |

|--------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------|---------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| SUB SHL AND SHRU LDW                                         | .D2<br>.S1<br>.L2<br>.S2<br>.D1T1   | B_p,<br>A_top0,<br>B_p,<br>B_top1,<br>*A_len++,             | B_32,<br>A_1cw,<br>B_31,<br>B_rs,<br>A_1cw<br>Scheduled | B_r<br>A_top0_ls<br>B_p<br>B_top1_rs | ;[ 9,2] p = p % 32<br>;[ 9,2] top1_rs = top1 >> rs<br>;[ 1,4] length of code word                                            |

| STW SUB CMPGT SHRU SHL MV                                    | .S1<br>.S2                          | A_top0_rs,<br>B_32,<br>B_r,<br>A_top0,<br>B_top1,<br>A_lcw, | B_r,<br>-1,<br>A_rs,                                    | A_top0_rs                            |                                                                                                                              |

| OR   [A_rwLDW   [A_it]B   SHRU   SUB   [A_it]SUB             | .L1X<br>.D2T2<br>.S1<br>.S2<br>.L2X | A_top0_ls,  *B_ptr++, LOOP  B_buff, B_32, A_it,             | B ru,                                                   |                                      | <pre>;[11,2] top0_ls   top1_rs ;[11,2] Load buff_cpy ;[11,2] Branch ;[11,2] Missing bits ;[ 7,3] rs = 32 - lcw ;[ 7,3]</pre> |

| [ A_rw]SHL<br>  [ A_rw]MV<br>  [ A_rw]OR<br>   ADD<br>   SUB |                                     | B_buff_cpy,<br>A_top0,                                      | B_r,<br>B_buff<br>B_top1_ru,<br>B_lcw,<br>A_lcw,        |                                      | <pre>;[12,2] Update top1 ;[12,2] Update buff ;[12,2] Complete 32 bits ;[ 8,3] p = p + lcw ;[ 8,3] rs = 32 - lcw</pre>        |

22 operations in 4 cycles ffor an average IPC of 5.5 instructions/cycle

**Connecting Real People with Real Solutions**

## CONVOLUTION: 3x3 LAB - 1

# Developer Conference February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

### **CONVOLUTION 3x3**

```

conv 3x3 cn -- Natural C version of conv 3x3().

*/

void conv 3x3 cn(const unsigned char *restrict inptr,

unsigned char *restrict outptr,

int

x dim,

const char

*restrict mask,

int

shift)

const unsigned char *IN1,*IN2,*IN3;

unsigned char

*OUT;

short pix10, pix20, pix30;

short mask10, mask20, mask30;

sum, sum00, sum11;

int

int i;

int sum22, j;

/* Set imgcols to the width of the image and set three pointers for */

/* reading data from the three input rows. Alos set the output poin- */

/* ter.

IN1

= inptr;

IN2 = IN1 + x dim;

= IN2 + x dim;

IN3

= outptr;

OUT

```

## Developer Conference February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

### **CONVOLUTION 3x3, Natural C Code**

```

for (j = 0; j < x \dim ; j++)

sum = 0;

for (i = 0; i < 3; i++)

pix10 =

IN1[i];

pix20 = IN2[i];

pix30 =

IN3[i];

mask10 =

mask[i];

mask[i + 3];

mask20 =

mask30 =

mask[i + 6]:

sum00 =

pix10 * mask10;

sum11 = pix20 * mask20;

sum22 =

pix30 * mask30;

sum00 + sum11+ sum22;

sum

IN1++; IN2++; IN3++;

sum = (sum >> shift);

if (sum < 0) sum = 0;

if (sum > 255) sum = 255;

*OUT++ =

sum;

```

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

```

SOFTWARE PIPELINE INFORMATION

Loop source line

: 83

Loop opening brace source line

: 84

Loop closing brace source line

: 128

Known Minimum Trip Count

: 1

Known Max Trip Count Factor : 1

Loop Carried Dependency Bound(^): 3

Unpartitioned Resource Bound

Partitioned Resource Bound(*)

: 5

Resource Partition:

A-side

B-side

.L units

1

.S units

0

.D units

5*

.M units

5*

.X cross paths

5*

.T address paths

5*

Long read paths

0

Long write paths

0

Logical ops (.LS)

(.L or .S unit)

Addition ops (.LSD)

(.L or .S or .D unit)

Bound(.L .S .LS)

Bound(.L .S .D .LS .LSD)

5*

Searching for software pipeline schedule at ...

ii = 5 Did not find schedule

ii = 6 Schedule found with 6 iterations in parallel

COMPILER ANALYSIS OF NATURAL C CODE

```

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

| L4: ; P | PIPED LOO                           | P KERNEL                                  | ı                                                                                           |                                        |                                                 |                                                |   |

|---------|-------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------|------------------------------------------------|---|

| [ A0]   | BDEC<br>CMPLT<br>ADD<br>ADD<br>LDBU | .S1<br>.L1<br>.S2X<br>.D1X<br>.D2T2       | L4,A0<br>A8,0,A4<br>A4,B4,B5<br>B23,A17,A17<br>*++B19,B22                                   | ;<br>;<br>;                            | 128  <br>  120  <br>  106  <br>  106  <br>  106 | <0,28> <1,22> <2,16> <3,10> <4,4>              | ^ |

|         | ADD<br>MPY<br>LDBU<br>LDBU<br>MPY   | .S2X<br>.M1<br>.D1T1<br>.D2T2<br>.M2      | A25,B5,B24<br>A18,A16,A9<br>*A6++,A5<br>*-B19(1),B20<br>B4,B9,B23                           | ;<br>;<br>;                            | 106<br>106<br>106<br>106<br>106                 | <2,17> <3,11> <4,5> <4,5> <4,5>                |   |

|         | MV ADD ADD MPY MPY LDBU LDBU        | .L2<br>.S2<br>.S1X<br>.M2<br>.M1<br>.D1T1 | B4,B24<br>B21,B24,B21<br>B23,A17,A25<br>B22,B6,B4<br>A9,A19,A4<br>*++A22,A18<br>*+B19(2),B4 | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | 120<br>106<br>106<br>106<br>106<br>106<br>106   | <0,30> <2,18> <3,12> <3,12> <3,12> <4,6> <5,0> |   |

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

### Analysis of Convolution Algorithm

#### **Connecting Real People with Real Solutions**

| # | of | byte I | oads/  | outpι  | ıt p | ixel | : 18 |

|---|----|--------|--------|--------|------|------|------|

| # | of | multi  | plies/ | pixel: | 9 (  | 16 x | 16)  |

# of additions: 9 # of stores/pixel: 1

Based on these numbers, and given that we can load 2 bytes/cycle, this algorithm appears to be load bottlenecked at 9 cycles/output pixel.

To overcome this, we can preload values of the 3x3 mask, which is loop invariant into register file and reduce byte loads/output pixel to 9.

| b00 | b01     | b02 |  |

|-----|---------|-----|--|

| b10 | b10 b11 |     |  |

| b20 | b21     | b22 |  |

|     |         |     |  |

- a) Load data for b02, b12, b22 only.

- b) For other bytes pre-load and issue moves, to move the other bytes by moving the data in register file.

- b00 = b01; b01 = b02; b10 = b11;

b11 = b12; b20 = b21; b21 = b22;

Load b02, Load b12, Load b22.

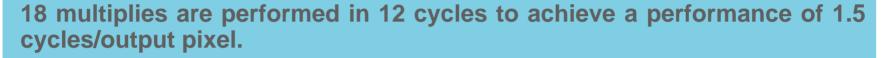

## Analysis of Convolution Algorithm

**Connecting Real People with Real Solutions**

# of byte loads/output pixel = 9

Therefore we can use double word wide loads to load eight pixels along every row. Therefore loads are not a bottleneck.

C64x can perform 8 (8x8) multiplies, and we need to perform 9 (8x8) multiplies/output pixel, therefore an optimal implementation should achieve 9/8 = 1.125 cycles/output pixel.

We can compute multiple output pixels in parallel. If we compute eight output pixels in parallel we would need 72 (8x8) multiplies which can be performed in 72/8 = 9 cycles.

Optimal implementation must compute 8 output pixels in 9 cycles to achieve a compute rate of 1.125 cycles/output pixel.

## **Optimized C Code**

```

/* Set loop counter for output pixels and three input pointers x dim

/* apart from the user passed input pointer. Copy output pointer

= x dim >> 1;

count

IN1

inptr;

= IN1+ x_{dim};

IN2

= IN2+ x_{dim};

IN3

OUT

outptr;

/* In order to minimize data loads, dat re-use is achieved by moves.

/* The data to be used for pix10, pix11 are pre-loaded into pix12 and

/* pix13 and moved within the loop. The process is repeated for rows 2

/* and 3 for pix20, pix21 and pix30 and pix31 respectively.

* /

pix12

*IN1++;

pix13

*IN1++;

pix22

*IN2++;

pix23

*IN2++;

pix32

*IN3++;

pix33

*IN3++;

```

## **Optimized C Code**

```

for ( j = count; j > 0; j--)

pix10 = pix12; pix11 = pix13; pix12 = *IN1++;

pix20 = pix22; pix21 = pix23; pix22 = *IN2++;

pix13

*IN1++;

pix23

*IN2++:

pix30 =

pix32;

pix32 =

*IN3++:

*IN3++;

pix31 =

pix33;

pix33

sum00 = ((pix10*mask10) + (pix11*mask11) + (pix12*mask12));

sum11 = ((pix20*mask20) + (pix21*mask21) + (pix22*mask22));

sum22 = ((pix30*mask30) + (pix31*mask31) + (pix32*mask32));

sum0 = (sum00 + sum11 + sum22) >> shift;

if (sum0 < 0)  sum0 = 0;

if (sum0 > constant) sum0 = constant;

*OUT++ = sum0;

sum00 = ((pix11*mask10)+(pix12*mask11)+(pix13*mask12));

sum11 = ((pix21*mask20)+(pix22*mask21)+(pix23*mask22));

sum22 = ((pix31*mask30)+(pix32*mask31)+(pix33*mask32)):

= (sum00 + sum11 + sum22) >> shift;

if (sum1 < 0)  sum1 = 0:

if (sum1 > constant) sum1 = constant;

*OUT++ = sum1;

```

## COMPILER REPORT FOR OPTIMIZED C CODE

```

SOFTWARE PIPELINE INFORMATION

Loop source line

: 200

Loop opening brace source line

: 201

Loop closing brace source line

: 263

Known Minimum Trip Count

: 1

Known Max Trip Count Factor : 1

Loop Carried Dependency Bound(^) : 3

Unpartitioned Resource Bound

, *

: 10

Partitioned Resource Bound(*)

: 12

Resource Partition:

A-side

B-side

.L units

.S units

0

.D units

.M units

10

.X cross paths

10

12*

.T address paths

5

; *

Long read paths

Long write paths

Logical ops (.LS)

(.L or .S unit)

0

Addition ops (.LSD)

(.L or .S or .D unit)

21

Bound(.L .S .LS)

1

; *

Bound(.L .S .D .LS .LSD)

Searching for software pipeline schedule at ...

. *

ii = 12 Schedule found with 4 iterations in parallel

, *

```

**Connecting Real People with Real Solutions**

This requires the use of wider loads using double words and the 8 bit multiply instructions of the C64x.

This requires intrinsics or serial assembly.

## Developer Conference February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

## INTRINSIC C CODE

```

mask00 =

mask[0]:

mask01

mask[1]:

mask02 =

mask[2]:

mask10

mask[3]:

mask11

mask[4]:

mask12 =

mask[5]:

mask20 =

mask[6];

mask21

mask[7];

mask22 =

mask[8];

h00word

= pack2(mask00, mask00);

= pack2(mask01, mask01);

h01word

= pack2(mask02, mask02);

h02word

= packl4(h00word, h00word);

h00word

= packl4(h01word, h01word);

h01word

h02word

= pack14(h02word, h02word);

10 dword0

= memd8 const(IN1);

11 dword0

= memd8 const(IN2);

12 dword0

= memd8 const(IN3);

IN1 += 1;

IN2 += 1;

IN3 += 1;

10 dword1

= memd8 const(IN1);

11 dword1

= memd8 const(IN2);

12 dword1

= memd8 const(IN3);

IN1 += 1;

IN2 += 1;

IN3 += 1;

10 dword2

= memd8 const(IN1);

11 dword2

= memd8 const(IN2);

12 dword2

= memd8 const(IN3);

IN1 += 6;

IN2 += 6;

IN3 += 6;

```

### INTRINSIC C CODE

```

= lo(10 dword0);

line00

line01 = hi(10 dword0);

line10

= lo(l1 dword0);

line11

= hi(11 dword0);

line20

= lo(12 dword0);

line21

= hi(12 dword0);

= lo(10 dword1);

line02

line03

= hi(10 dword1);

#if 0

line12

= lo(l1 dword1);

line13

= hi(11 dword1);

#endif

line22

= lo(12 dword1);

line23

= hi(12 dword1);

line04

= lo(10 dword2);

line05 = hi(10 dword2);

line14

= lo(11 dword2);

line15 = hi(11 dword2);

line24

= lo(12 dword2);

line25

= hi(12 dword2);

#if 1

line12

= shrmb(line11, line10);

line13

= shlmb(line14, line15);

#endif

```

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

#### INTRINSIC C CODE

```

prodA d0

mpysu4 (h00word, line00);

= mpysu4(h00word, line01);

prodA d1

prodA d2

= mpysu4(h01word, line02);

prodA d3

= mpysu4(h01word, line03);

prodA d4

mpysu4(h02word, line04);

prodA d5

mpysu4(h02word, line05);

lo(prodA d0);

prodA0

prodA1

hi(prodA d0);

prodA2

lo(prodA d1);

prodA3

hi(prodA d1);

prodA4

lo(prodA d2);

prodA5

hi(prodA d2);

lo(prodA d3);

prodA6

prodA7

hi(prodA d3);

prodA8

lo(prodA d4);

prodA9

hi(prodA d4);

prodAA

lo(prodA d5);

prodAB

hi(prodA d5);

```

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

#### **Connecting Real People with Real Solutions**

#### **Intrinsic C Code**

```

ta 01

= add2(prodA0,

prodA4);

= add2(prodB0, prodB4);

tb 01

tc 01

= add2(prodC0, prodC4);

= _add2(ta_01, prodA8);

= _add2(tb_01, prodB8);

= _add2(tc_01, prodC8);

sum a01

sum b01

sum c01

= add2(sum a01, sum b01);

sum t01

= add2(sum c01, sum t01);

sum 001

= shr2(sum o01, shift);

pix 01

pix 23

= shr2(sum o23, shift);

pix 45

= shr2(sum o45, shift);

pix 67

= shr2(sum o67, shift);

out word0 = spacku4(pix 23, pix 01);

out word1 = spacku4(pix 67, pix 45);

out d0

= itod(out word1, out word0);

memd8(OUT) = out d0;

+= 8:

OUT

```

## Developer Conference February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

#### COMPILER ANALYSIS FOR INTRINSIC C

#### **Connecting Real People with Real Solutions**

| . 4          |                                 |     |               | *                     |

|--------------|---------------------------------|-----|---------------|-----------------------|

| ; ^ -<br>; * | SOFTWARE PIPELINE INFORMATION   |     |               |                       |

| , *          | DOFTMAND TITEDING INFORMATION   |     |               |                       |

| <b>;</b> *   | Loop source line                | :   | 284           |                       |

| <b>;</b> *   | Loop opening brace source line  | :   | 285           |                       |

| <b>;</b> *   | Loop closing brace source line  | :   | 514           |                       |

| <b>;</b> *   | Known Minimum Trip Count        | _   | 1             |                       |

| <b>;</b> *   | Known Max Trip Count Factor     |     |               |                       |

| <b>;</b> *   | Loop Carried Dependency Bound(^ |     |               |                       |

| <b>;</b> *   | Unpartitioned Resource Bound    |     |               |                       |

| <b>;</b> *   | Partitioned Resource Bound(*)   | :   | 10            |                       |

| <b>;</b> *   | Resource Partition:             |     | m at a        |                       |

| <b>;</b> *   |                                 | .e  | B-side        |                       |

| <b>;</b> *   | .L units 0                      |     | 0             |                       |

| ; *<br>; *   | .S units 5 .D units 3           |     | 2<br>6        |                       |

| ; *          | .M units 9                      |     | 9             |                       |

| ; *          | .X cross paths                  |     | <i>5</i><br>7 |                       |

| ; *          | .T address paths 9              |     | 9             |                       |

| ,<br>, *     | Long read paths 0               |     | Ó             |                       |

| ; *          | Long write paths 0              |     | Ö             |                       |

| <b>;</b> *   | Logical ops (.LS)               |     | 1             | (.L or .S unit)       |

| <b>;</b> *   | Addition ops (.LSD) 18          |     |               | (.L or .S or .D unit) |

| <b>;</b> *   | Bound(.L .S .LS)                |     | 2             |                       |

| <b>;</b> *   | Bound(.L .S .D .LS .LSD) 9      |     | 10*           |                       |

| <b>;</b> *   |                                 |     |               |                       |

| <b>;</b> *   | Searching for software pipeline | SC  | hedule at     |                       |

| <b>;</b> *   | ii = 10 Schedule found with     | 4 i | terations     | s in parallelh        |

|              |                                 |     |               |                       |

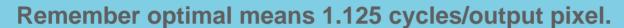

72 multiplies in 10 cycles for 8 output pixels to achieve 10/8 = 1.25 cycles/output pixel.

### Convolution3x3 for a row of 480 pixels.

| Natural<br>C             | Optimized<br>C        | Intrinsic<br>C         | Serial<br>Assembly        | Hand<br>Assembly          |

|--------------------------|-----------------------|------------------------|---------------------------|---------------------------|

| 2934                     | 2934                  | 655                    | 581                       | 581                       |

| 6.1<br>cycles/o<br>utput | 6.1 cycles/<br>output | 1.36 cycles/<br>output | 1.21<br>cycles/<br>output | 1.21<br>cycles/<br>output |

## Lab 2: Threshold

```

Thrgt2max:

for (i = 0; i < pixels; i++)

out data[i] = in data[i] > threshold ? 255 : in data[i];

Thrqt2thr:

for (i = 0; i < pixels; i++)

out data[i] = in data[i] > threshold? threshold:in data[i];

Thrle2min:

for (i = 0; i < pixels; i++)

out data[i] = in data[i] <= threshold ? 0 : in data[i];</pre>

Thrle2thr:

for (i = 0; i < pixels; i++)

out data[i] = in data[i] <= threshold ? threshold : in data[i];</pre>

```

### **C64x SIMD Instructions**

#### **Connecting Real People with Real Solutions**

February 18-20, 2004 • Houston, TX • Westin Galleria Hotel

```

THRGT2MAX

for (i = 0; i < pixels; i += 4)

p3p2p1p0 = amem4 const(&in data[i]);

x3x2x1x0 = xpnd4(\_cmpgtu4(p3p2p1p0, thththth));

_{amem4(\&out\_data[i])} = p3p2p1p0 \mid x3x2x1x0;

THRGT2THR

for (i = 0; i < pixels; i += 4)

_amem4(&out_data[i]) =

minu4( amem4 const(&in data[i]), thththth);

Can you quess the sequence of instructions for thrle2min

thrle2thr ?

and

Can you analyze the complexity and throughput of these

algorithms?

```

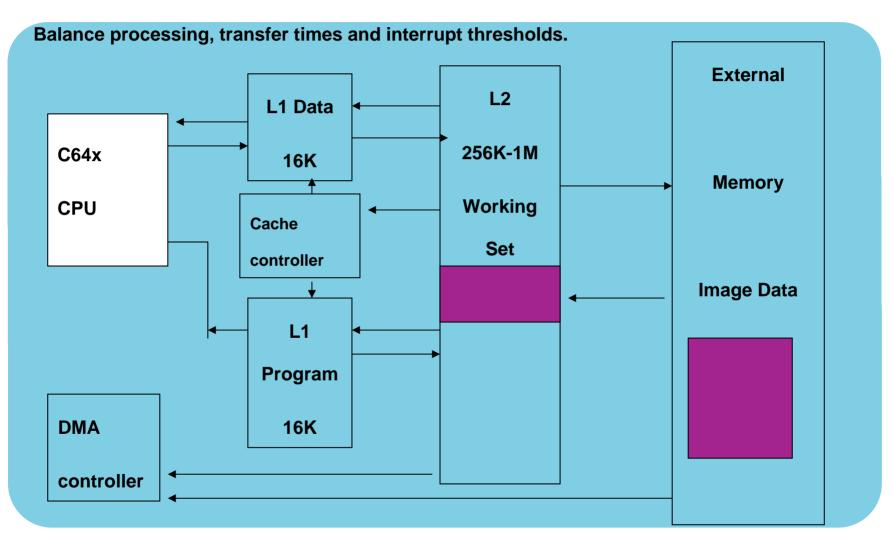

#### SYSTEM OPTIMIZATION

#### **Connecting Real People with Real Solutions**