Research on Extending and Surpassing the Limits of CMOS

> IEEE Circuits and Systems Society DFW Chapter 3/07 Seminar

> > Dallas, Texas

March 21, 2007

Dr. Robert Doering

**Texas Instruments**

**RRD 3/21/07**

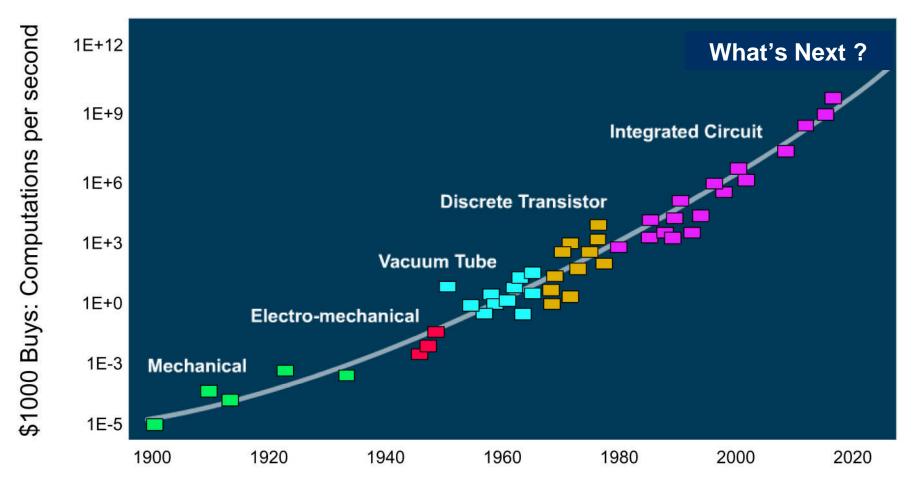

# Miniaturization ("Scaling" today) has driven multiple eras of information technology

Smaller Components  $\rightarrow$  Cheaper, Faster, More Energy-Efficient Systems

**RRD 3/21/07**

Source: Ray Kurzweil

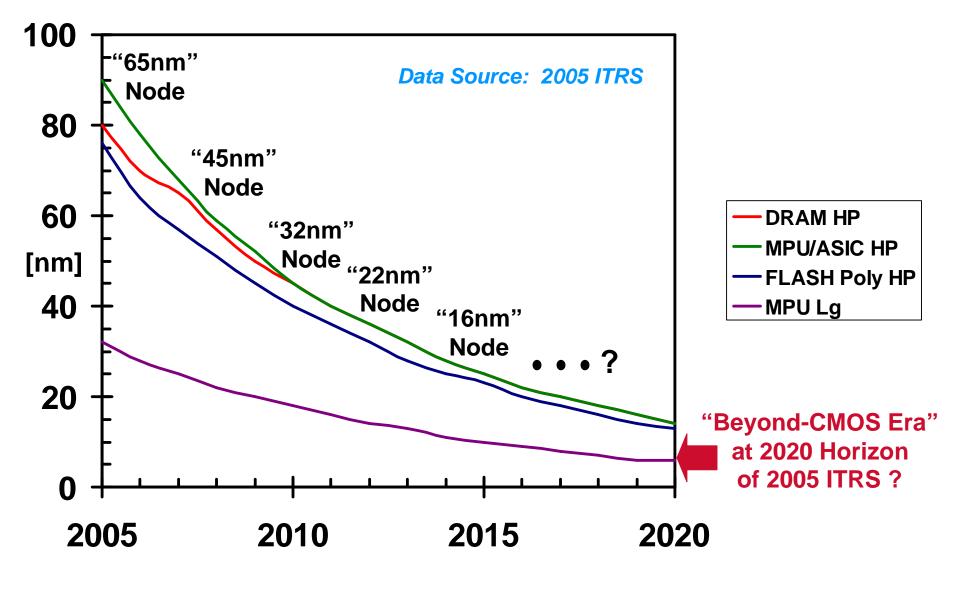

### **CMOS Scaling as "Technology Nodes"**

**RRD 3/21/07**

How long can we continue to scale CMOS?

### International Consensus Building on Future IC Technology Challenges

**First – identify and categorize the R&D needs**

**RRD 3/21/07**

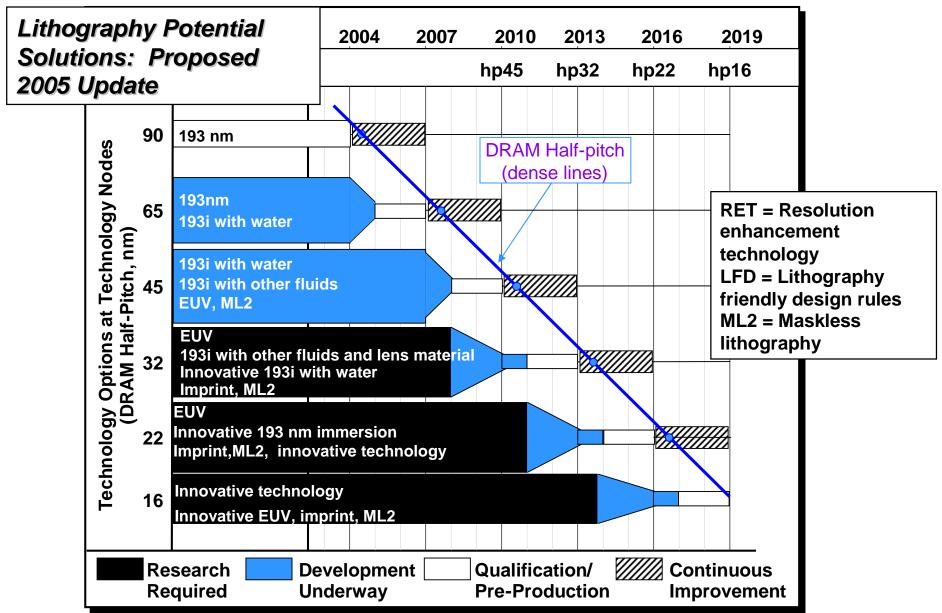

### ITRS Methodology for highlighting challenges/opportunities

| <b>Production Year:</b>            | 2001    | 2004    | 2007    | 2010    | 2013      | 2016      |

|------------------------------------|---------|---------|---------|---------|-----------|-----------|

| DRAM Half-Pitch [nm]:              | 130     | 90      | 65      | 45      | 32        | 22        |

| Overlay Control [nm]:              | 45      | 32      | 16      | 11      | 8         | 5.5       |

| Gate Length [nm]:                  | 65      | 37      | 25      | 18      | 13        | 9         |

| CD Control [nm]:                   | 6.3     | 3.3     | 2.6     | 1.9     | 1.3       | 0.9       |

| T <sub>ox</sub> (equivalent) [nm]: | 1.3-1.6 | 1.2     | 1.1     | 0.65    | 0.5 (UTB) | 0.5 (MUG) |

| I <sub>ON</sub> (NMOS) [μΑ/μm]:    | 900     | 1110    | 1200    | 2050    | 2198      | 2713      |

| l <sub>oFF</sub> (NMOS) [μΑ/μm]:   | 0.01    | 0.05    | 0.2     | 0.28    | 0.29      | 0.11      |

| Interconnect K <sub>EFF</sub> :    | -       | 3.1-3.6 | 2.7-3.0 | 2.5-2.8 | 2.1-2.4   | 1.9-2.2   |

**RRD 3/21/07**

values from the 2001, 2004, and 2005 editions of the ITRS

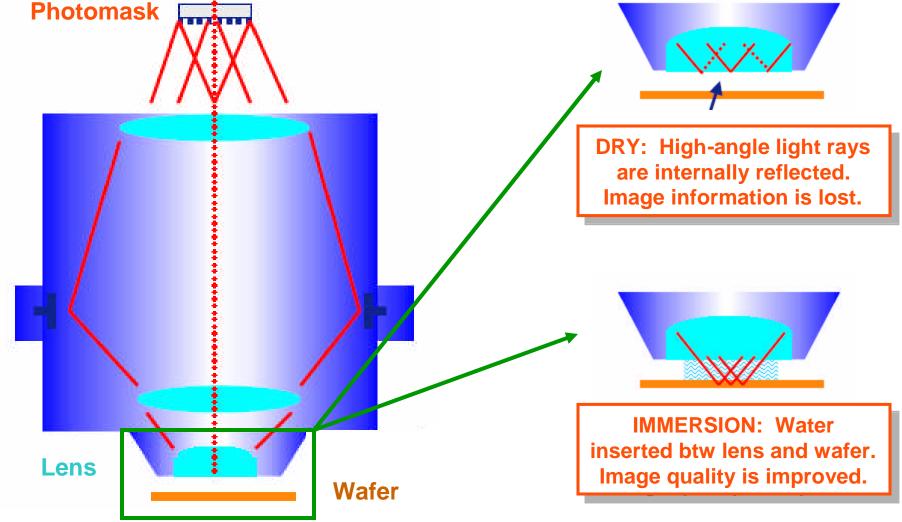

Notes: RET and lithography friendly design rules will be used with all photon projection lithography solutions, including with immersion; therefore, it is not explicitly noted.

**RRD 3/21/07**

**RRD 3/21/07**

### **Scaling is limited**

# by more than just lithography !

- Growing Significance of Non-Ideal Device-Scaling Effects:

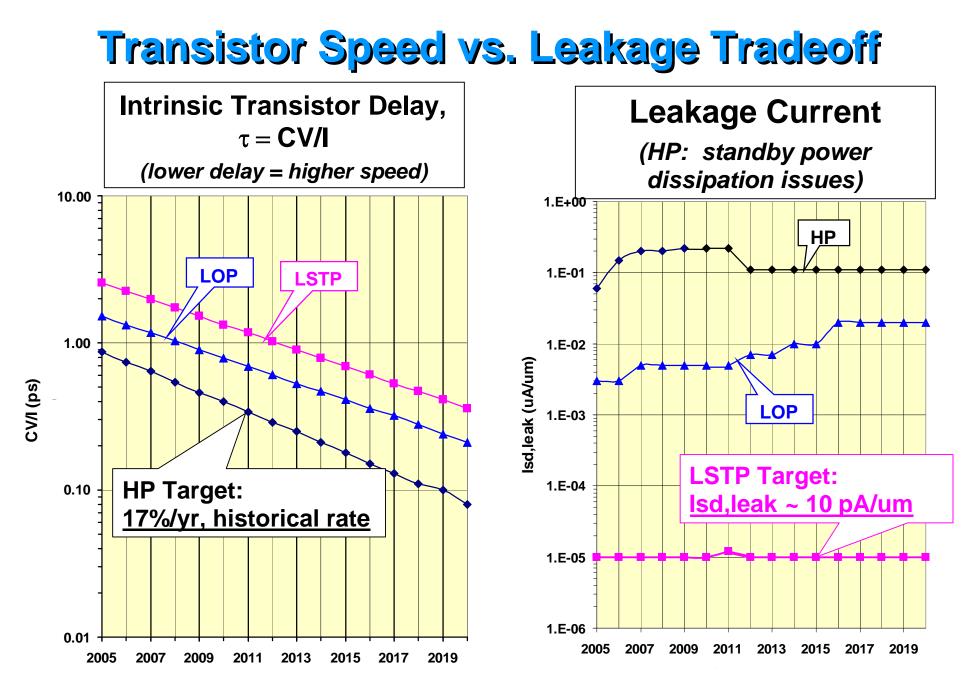

- ➢ I<sub>ON</sub> vs. I<sub>OFF</sub> tradeoff

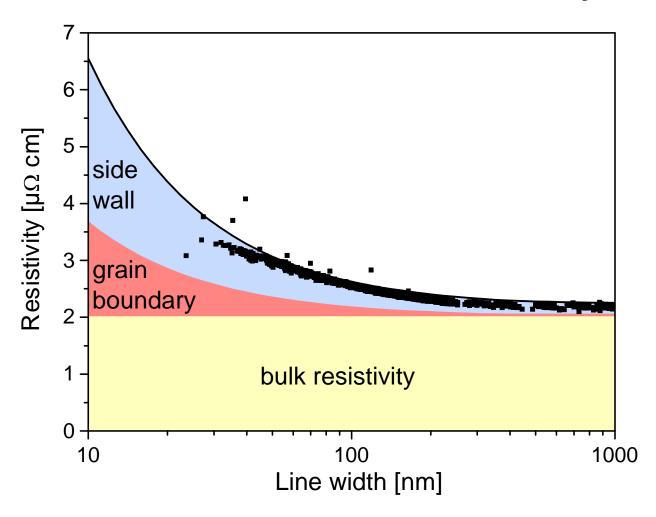

- $\succ$  unfavorable  $\rho$  and length scaling for interconnects

- Approaching Limits of Materials Properties

- > Heat removal and temperature tolerance

- ➤ C<sub>MAX</sub> vs. leakage tradeoff for gate dielectric

- ➤ C<sub>MIN</sub> vs. mechanical-integrity tradeoff for inter-metal dielectric

- Increases in Manufacturing Complexity/Control Requirements

- cost and yield of increasingly complex process flows

- metrology and control of L<sub>GATE</sub>, T<sub>OX</sub>, doping, etc.

- Affordability of R&D Costs

- development of more complex and "near cliff" technologies

- design of more complex circuits with "less ideal" elements

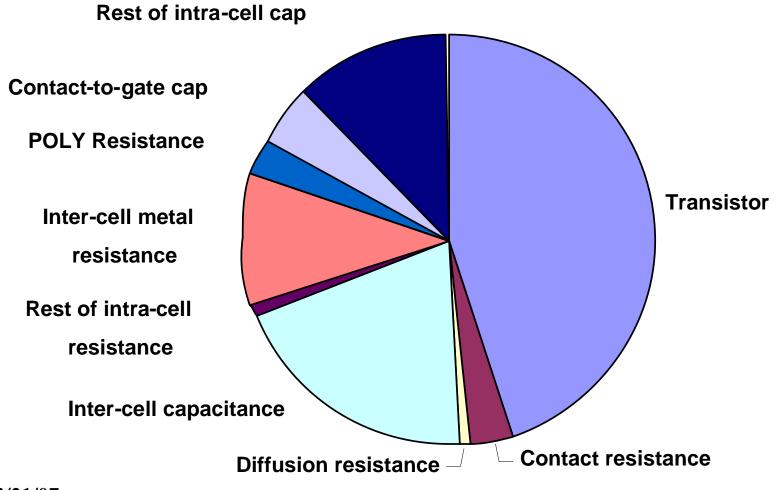

IC Performance: Transistors & Wires At 65-nm, the speed of typical dense logic is about equally limited by transistor and wire performance

RRD 3/21/07

**2005 Interconnect Update** New Data and Models of Cu Resistivity Scaling

Courtesy: Infineon Technologies

**RRD 3/21/07**

Source: 2005 ITRS

### PIDS: The "CMOS Change Crunch" Multiple, Big Changes Over ~7 Years

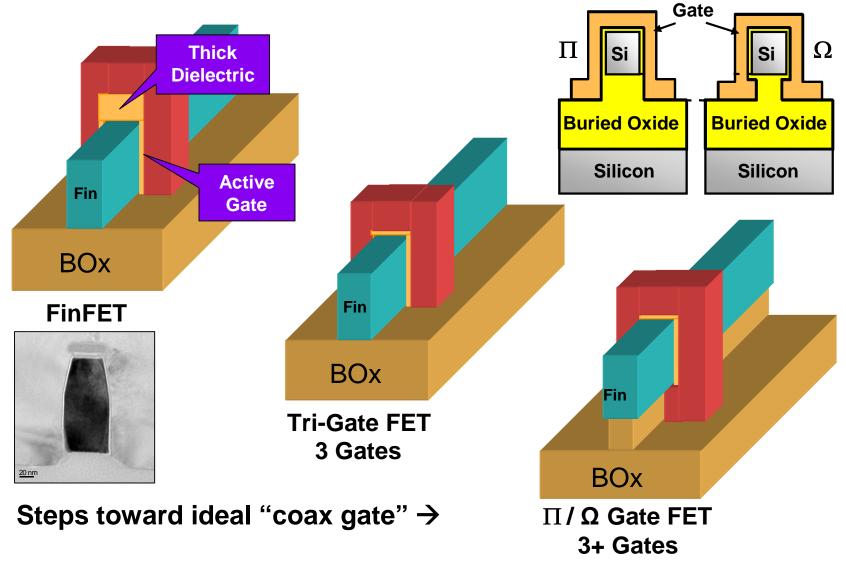

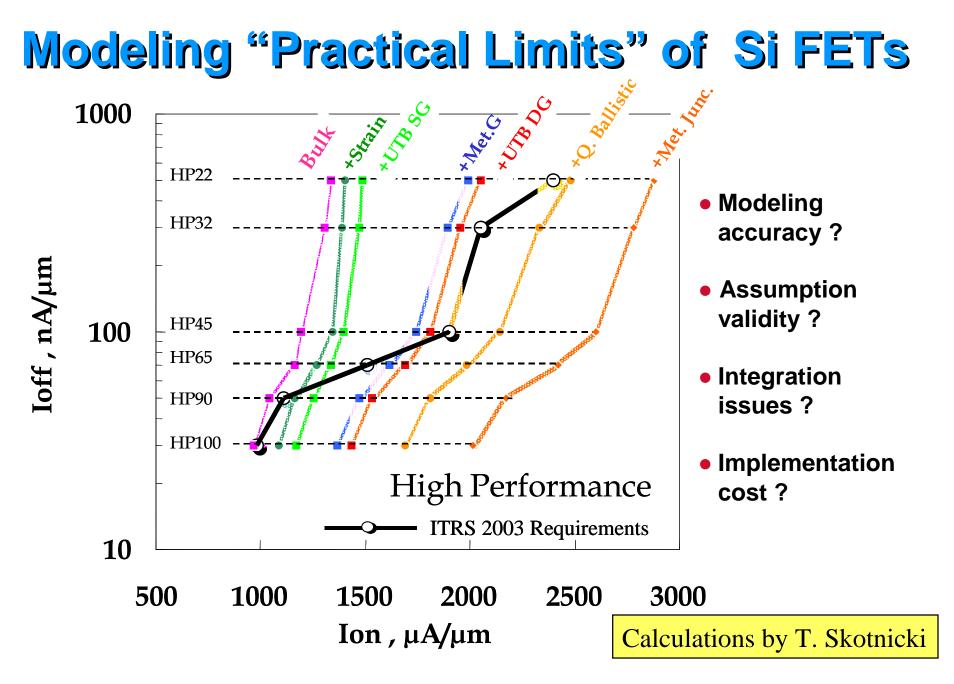

First Year of "Volume Production" 2020 2000 2015 2005 2010 Strained Si HI LP High-k Gate LP **Dielectric** Metal Gate LP **Electrode** HP LP **Fully-Depleted SOI Multiple-Gate** HP LP **MOSFET Others** = High Performance = Low Power LP **Driver**: HP **Applications Applications**

#### Potential path to "better electrostatics"... (unfortunately, with I<sub>OFF</sub> still limited by kT/q)

Source: 2003 ITRS

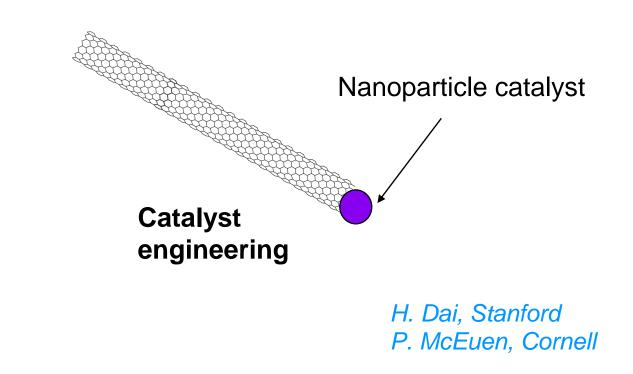

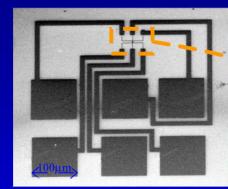

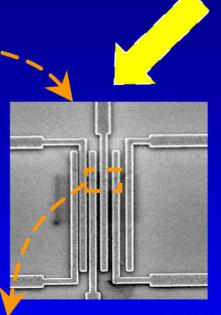

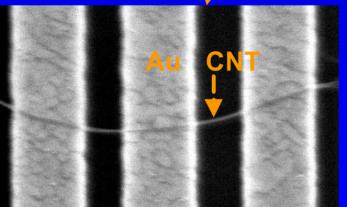

### **Carbon Nanotube FETs ?**

Some carbon nanotubes have very good device characteristics, but:

- Can we consistently make nanotubes with the desired properties ?

- Can we connect nanotubes to form complex electronic circuits ?

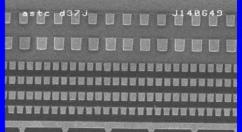

**Substrate Patterning**

# Nanotube <u>Technology</u>?

#### How do you get from here to there?

5:1:115 BHF:GLA-PULL JY 3CU24J31MG61 LM-PULL JY 008844 4.0 kV X10.0K 3.00/m

Plenty of room for improvement !

SL

No new architecture !

# How close is today's volume technology to fundamental transistor limits ?

$$E_{S}|_{\min} = \ln(2) k_{B}T$$

$$L_{\min} \approx \hbar / \sqrt{2mE_{\min}} = 1.5 \,\mathrm{nm}(300 \,\mathrm{K})$$

$$\tau_{\min} \approx \hbar / E_{S}|_{\min} = 0.04 \,\mathrm{ps} \quad (300 \,\mathrm{K})$$

$$n_{\max}(\mathrm{at} \ 100 \,\mathrm{W/cm}^{2}) = 1.5 \,\mathrm{B/cm}^{2}$$

Fundamental EET Limite

**90nm technology** (from ITRS)  $E_s \approx 35,000 \times E_s \big|_{min}$  $L \approx 25 \times L_{min}$  $\tau \approx 24 \times \tau_{min}$  $n \approx 0.13 \times n_{max}$

**RRD 3/21/07**

Source: Prof. Mark Lundstrom

# Can anything replace the FET ?

**RRD 3/21/07**

### 2005 ITRS Risk Assessment of Potential Future Logic Devices

| Logic Device<br>Technologies<br>(Potential) | Scalability [A] | Performance<br>[B] | Energy<br>Efficiency<br>[C] | Gain [D2] | Operational<br>Reliability<br>[E] | Room<br>Temp<br>Operation<br>[F] *** | CMOS<br>Technological<br>Compatibility<br>[G]** | CMOS<br>Architectural<br>Compatibility<br>[H]* |

|---------------------------------------------|-----------------|--------------------|-----------------------------|-----------|-----------------------------------|--------------------------------------|-------------------------------------------------|------------------------------------------------|

| 1D Structures<br>(CNTs & NWs)               | 2.4             | 2.5                | 2.3                         | 2.3       | 2.1                               | 2.8                                  | 2.3                                             | 2.8                                            |

| Resonant<br>Tunneling<br>Devices            | 1.5             | 2.2                | 2.1                         | 1.7       | 1.7                               | 2.5                                  | 2.0                                             | 2.0                                            |

| SETs                                        | 1.9             | 1.5                | 2.6                         | 1.4       | 1.2                               | 1.9                                  | 2.1                                             | 2.1                                            |

| Molecular<br>Devices                        | 1.6             | 1.8                | 2.2                         | 1.5       | 1.6                               | 2.3                                  | 1.7                                             | 1.8                                            |

| Ferromagnetic<br>Devices                    | 1.4             | 1.3                | 1.9                         | 1.5       | 2.0                               | 2.5                                  | 1.7                                             | 1.7                                            |

| Spin Transistor                             | 2.2             | 1.3                | 2.4                         | 1.2       | 1.2                               | 2.4                                  | 1.5                                             | 1.7                                            |

# > 20 > 16 - 18 > 18 - 20 ≤ 16

For each Technology Entry (e.g. 1D Structures, sum horizontally over the 8 Criteria Max Sum = 24 Min Sum = 8

Source: 2005 ITRS

Motivation for hybridization of "nano-devices" with CMOS

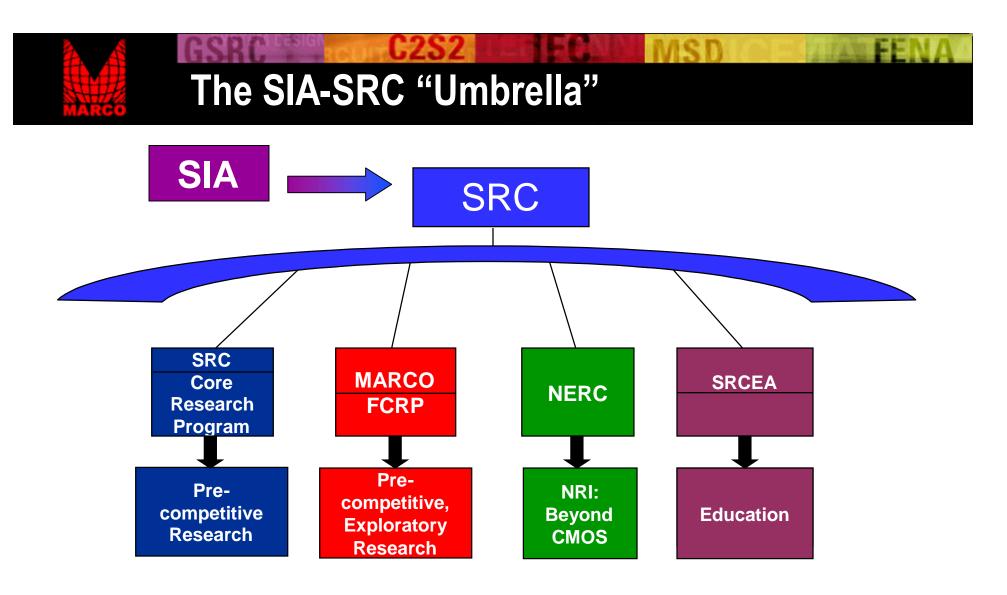

MARCO and NERC use SRC infrastructure and support staff Science Area Directors provide linkage to SRC Core Programs

DARPA S.T.08.05.05

Semiconductor Industry

semr

#### **MARCO FCRP: SIA-DoD Partnership** to Extend CMOS to Its Ultimate Limits

Princeton

Purdue

MIT

UIUC

Caltech

UCLA

Stanford

**U** T Austin

Georgia Tech

UC Berkeley

#### GSRC – System Design & Test Focus Cntr

Director: Prof. Jan Rabaey - UC Berkeley

- Design, verification, and test of heterogeneous SoC

- · Covers spectrum from system specification to implementation.

#### C2S2 – Circuit Design & Test Focus Cntr

Director: Prof. Rob Rutenbar - Carnegie Mellon

- · Circuit techniques & system concepts for heterogeneous devices

- Design of end-of-roadmap and post-CMOS devices for robust performance

#### IFC – Interconnect & Optoelectr Focus Cntr

#### Director: Prof. James Meindl - GeorgiaTech

- · Nanoscale electrical and optical interconnects

- Novel thermal management solutions

- Interconnect-driven circuit & system design

#### NST – NanoScale Devices Focus Cntr

Director: Prof. Dimitri Antoniadis - MIT

- CMOS scaling to ultimate limit

- Advanced FETs incorporating novel materials

- Nanotubes, molecular devices & spin-based FETs ٠

#### FENA – NanoScale Mat'rl Synth Focus Cntr Director: Prof. Kang Wang - UCLA

Novel nanoscale devices. materials and structures

| Cornell      | UCSD        |

|--------------|-------------|

| Ga Tech      | U. Florida  |

| MIT          | UIUC        |

| Stanford     | U. Wash     |

| Georgia Tech | UCSB        |

| Stanford     | RPI         |

| MIT          | UT Austin   |

| SUNY Albany  | CMU         |

| U Central FI | NC State U  |

| Cornell      | UC Berkeley |

| МІТ          | SUNY Albany |

UC Berkeley

UCLA

UCSB

UC SC

UCSD

CMU

CMU

Ca

Co

NC

Pe

Pri Pu Sta

UCLA

UCSB

Michigan

Penn State

Columbia

| I<br>Itech<br>rnell<br>State<br>nn State<br>nceton<br>rdue<br>anford | SUNY Albany<br>UT Austin<br>Univ Virginia<br>UC Berkeley<br>UCLA<br>UC SB<br>Univ Florida<br>Univ Maryland |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| anford                                                               | Univ Maryland                                                                                              |

| raue<br>anford                                                       |                                                                                                            |

#### Source: MARCO. 2004

#### Members

| AMD            | LSI Log |

|----------------|---------|

| Analog Devices | Micron  |

| Conexant       | Motoro  |

| Cypress        | Nationa |

| IBM            | TI      |

| Intel          | Xilinx  |

|                |         |

lic

Air Products **Applied Materials** Cadence Novellus Teradyne

#### Dept. of Defense

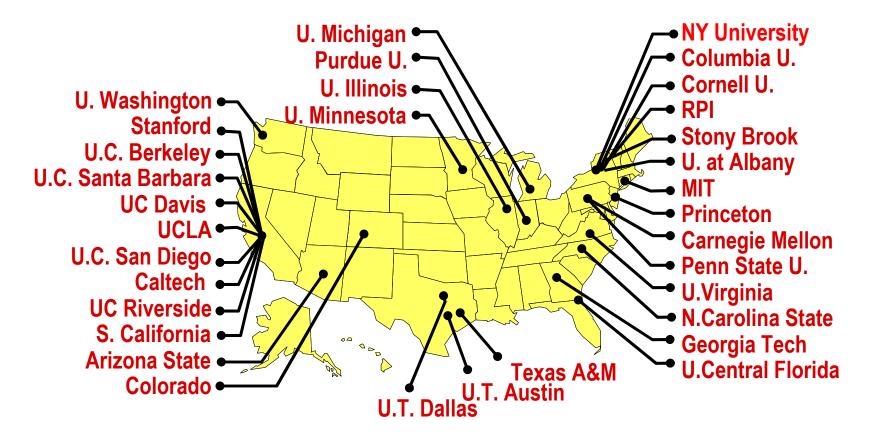

### **Top U.S. Universities in the FCRP**

Many of country's top universities and faculty are already part of at least one Focus Center

- 33 Universities and ~200 research faculty

#### 12/03 SIA Recommendations to PCAST

- In the long term, the SIA feels that we face two grand challenges worthy of >\$200M/year in new federal funding:

- (1) Scaling limits of "evolutionary lithography/thin-film manufacturing"

- (2) Scaling limits of "charge-transport devices/interconnect"

- We suggest that these might be overcome through new and synergistic research in the under-funded broad areas of:

- (1) "Directed self-assembly" of complex structures with "nanoelectronics-functionality" (computation, comm., etc.)

- (2) "Beyond (classical) charge transport" signal-processing/

computational technology (e.g., based on quantum-states)

"Nanoelectronics Research Initiative"

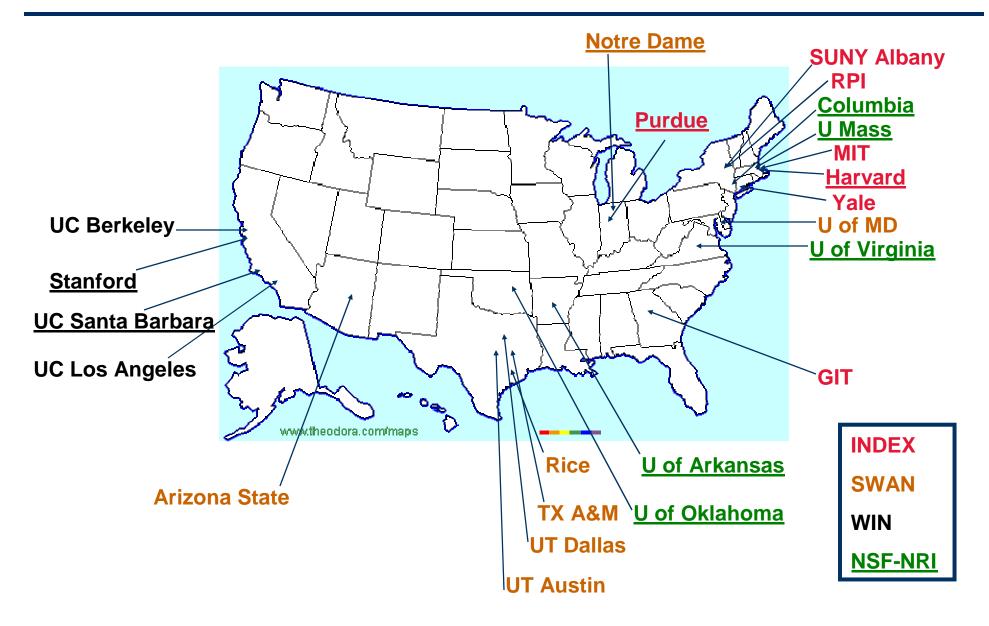

The Search for a "New Switch": The NERC Consortium NRI Program

- NERC members: AMD, Intel, IBM , Freescale, Micron, TI

- Started in March, 2005

- First project: partnership with NSF on supplemental funding for selected N/MR-SECs on nanoelectronics

- NERC-NSF award announcements at SNB-III, 12/05

- Latest program: formation of three regional NRI Centers in partnership with state governments, et al.

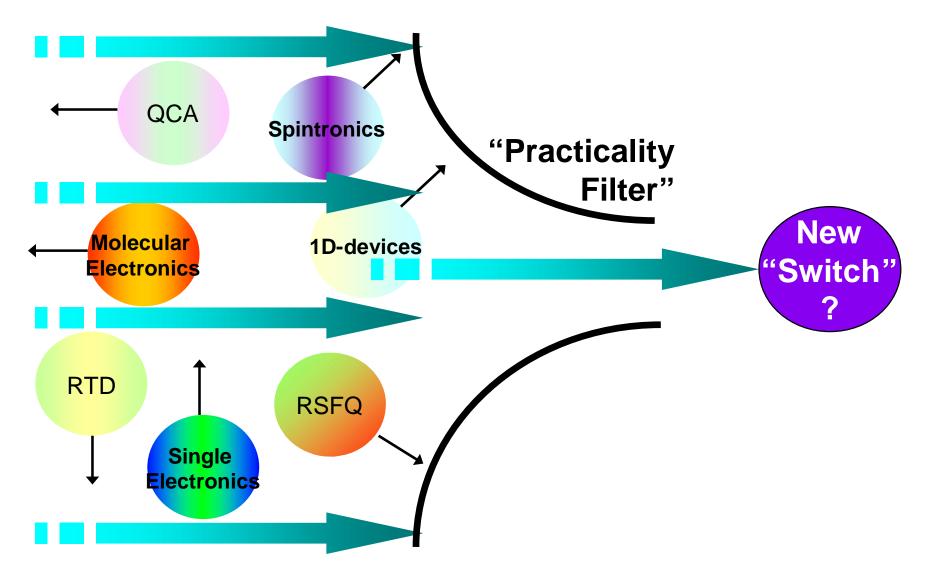

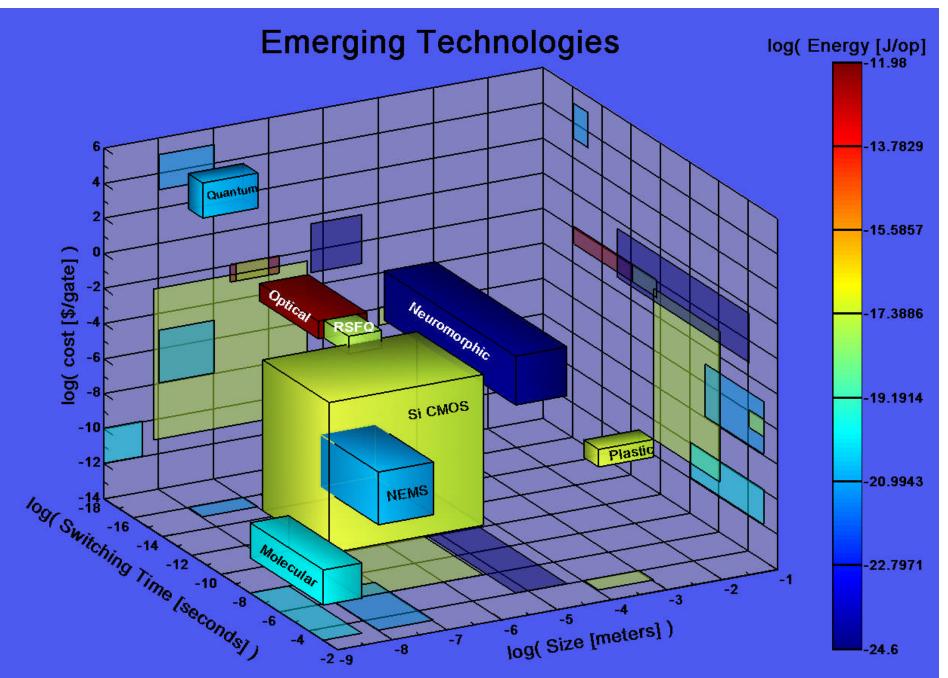

Promising Directions in the search for a new switch

→ NRI "Research Vectors"

"Bits" represented by variables other than charge (e.g., spin)

- Non-equilibrium systems  $\rightarrow$  lower power, less heat

- ♦ Novel energy-transfer mechanisms → overcome RC limits

- Nanoscale thermal management  $\rightarrow$  cooler operation

- ♦ Directed self-assembly → less variability, higher density, more reliable, lower cost

**RRD 3/21/07**

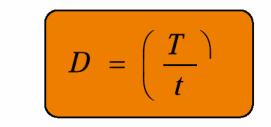

# What about Quantum Computing ? Big Challenges !

We require:

Difficult at room temp

Iow noise = long decoherence time T

fast coherent switching time t

Figure of merit D

We want D as big as possible + quantum error correction

Source: A. Ekert, Oxford University

### Rationale for Non-Electric-Charge-Based Signal-Processing/Computation

Break the "electrical scaling tyranny," e.g.:

- (1) Voltage (limiting speed/power/error-rate tradeoff)

- (2) Resistance (limiting speed and low power)

- (3) Capacitance (limiting speed and low active power)

- (4) Charge-Transport (e.g., mobility -- limiting speed)

- (5) Charge-Leakage Mechanisms (limiting standby power)

Some Potential State Variables Alternative to Electric Charge

- Molecular/atomic state

- Magnetic-dipole magnitude/orientation (e.g., electron/nuclear spin)

- Electric-dipole magnitude/orientation

- Photon number

- Photon polarization

- Quantum phase

- Mechanical state

SWAN

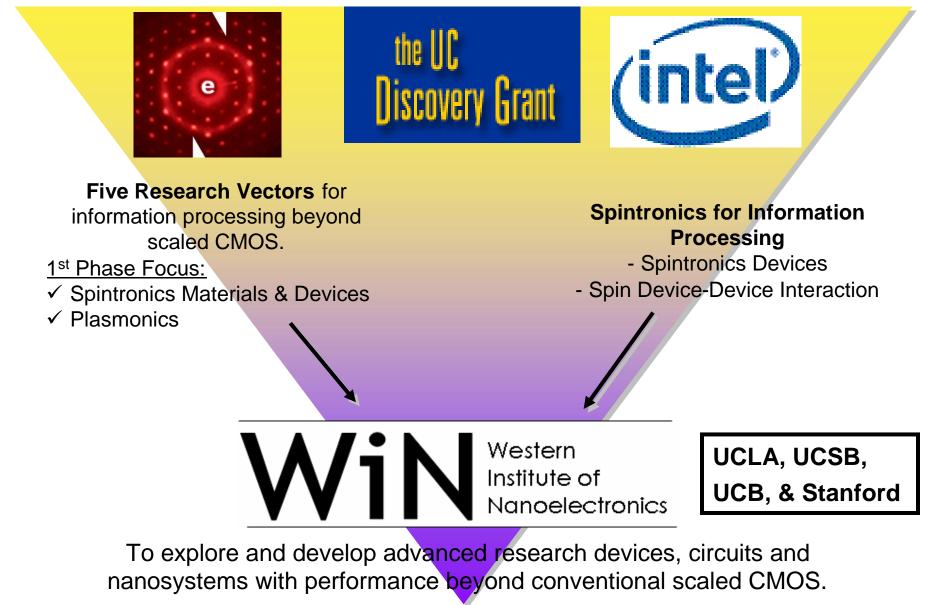

### **Initial WIN Programs**

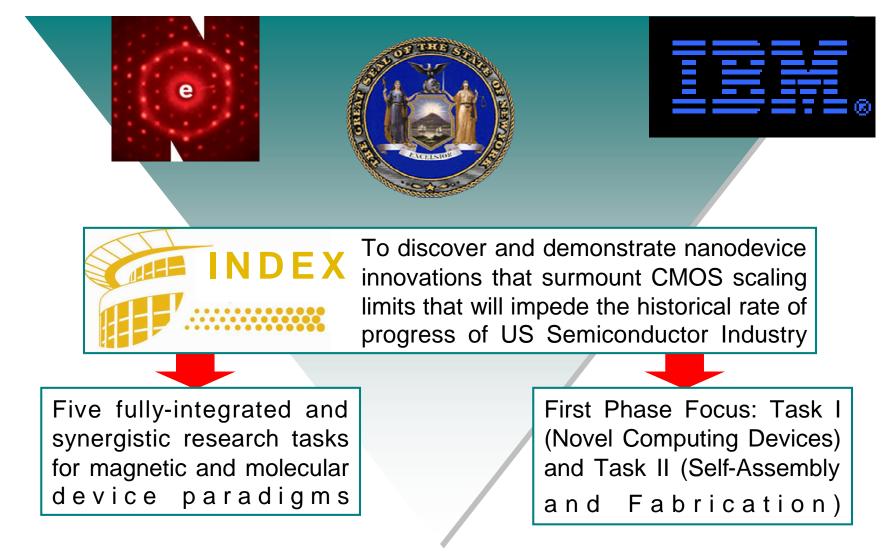

### **Initial INDEX Programs**

UAlbany, MIT, Yale, Harvard, Georgia Tech, RPI, and Purdue

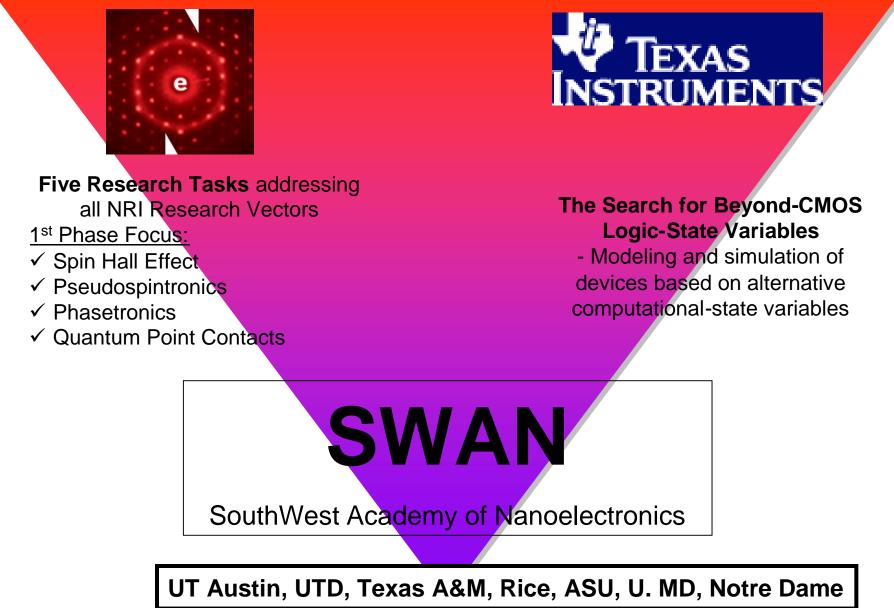

### **Initial SWAN Programs**

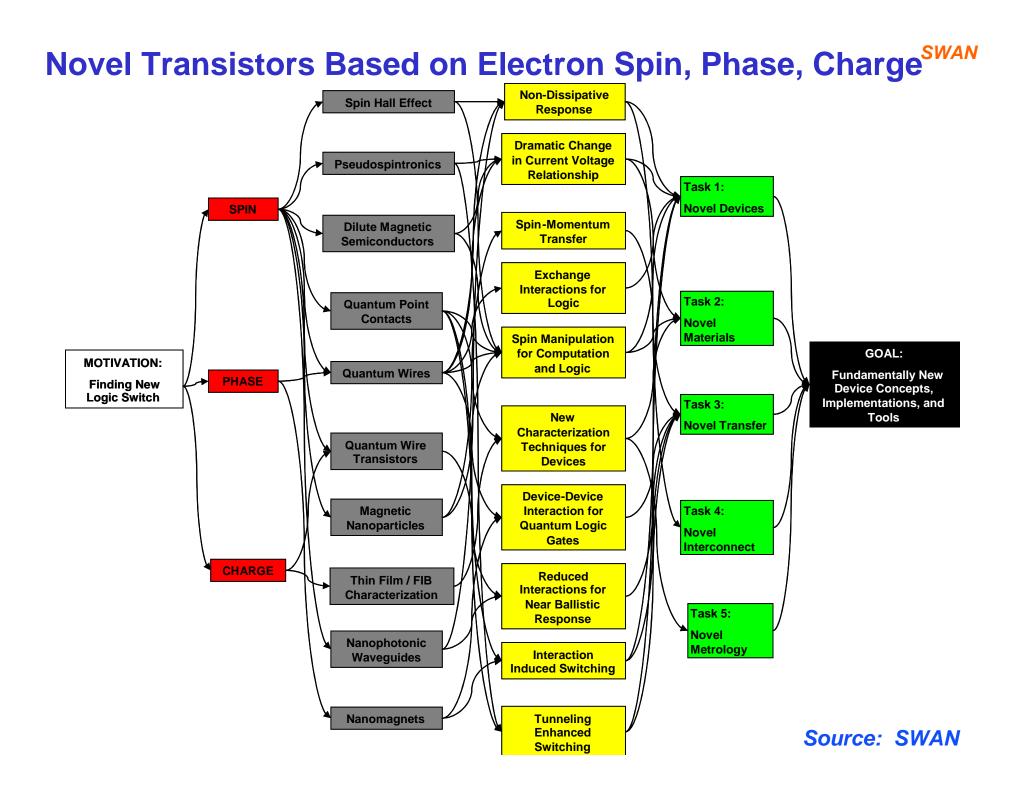

#### **SWAN Tasks and Investigators**

- Task 1: Logic Devices based on new computational state variables (UT: Banerjee, Gilbert, MacDonald, Register; Maryland: Das Sarma, TAMU: Sinova, ASU: Shumway)

- Task 2: Novel materials and structures (TAMU: Sinova; Notre Dame: Porod, , Bernstein; UT: Gilbert, Banerjee, Maryland: Das Sarma)

- Task 3: Directed Self-assembly and nanoscale thermal management (UT: Gilbert, Register, Banerjee; Maryland: Das Sarma)

- Task 4: Novel interconnect, and architectures (Rice: Massoud, Nordlander, Halas)

- Task 5: Nanoscale Characterization (UT Dallas: Gnade/Kim)

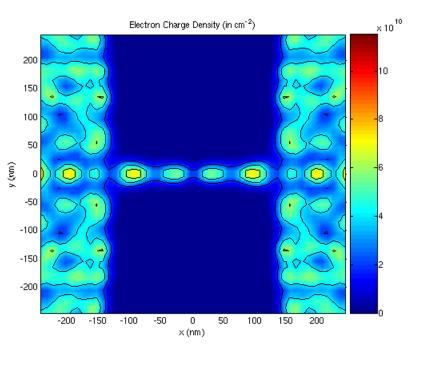

#### Task 1,3: Spin Degree of Freedom in Quantum Point Contacts (QPC) and Quantum Wires (QW)

#### Investigators: Shumway, Gilbert

Use many body Path Integral Monte Carlo to determine spin-charge separation in strongly correlated, low density quantum point contacts and quantum wires for novel switches.

#### In the figure:

•Spin down correlation function assuming a spin up electron at the center of the channel of a 100 electron quantum point contact.

•The length of the QPC is 200 nm

•The gate voltage is  $V_g$ =-0.30 V.

•Clear antiferromagnetic ordering associated with a Heisenberg spin chain is shown.

•This is a system which may exhibit spin-charge separation.

#### **Novelty:**

Use a new method for calculating the electrical and spin conductance of fully-interacting, low electron density systems to explore their use for fast, dissipation-less logical switches.

#### Source: SWAN

**SWAN**

**SWAN**

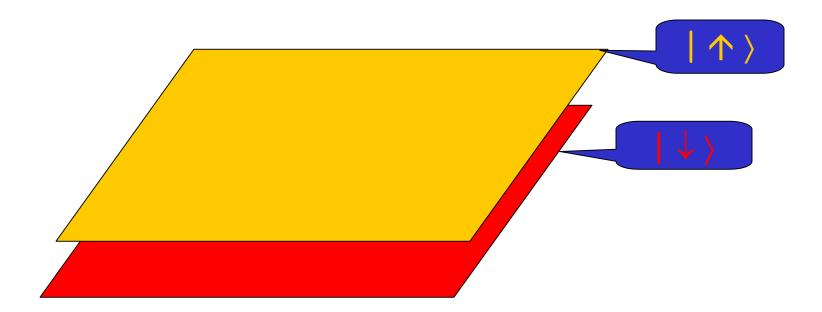

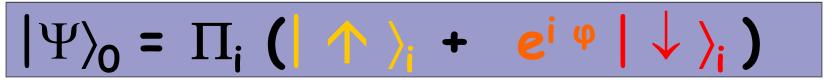

# **Pseudospintronics - What?**

#### Spontaneous Interlayer Phase Coherence = Pseudospin Ferromagnetism

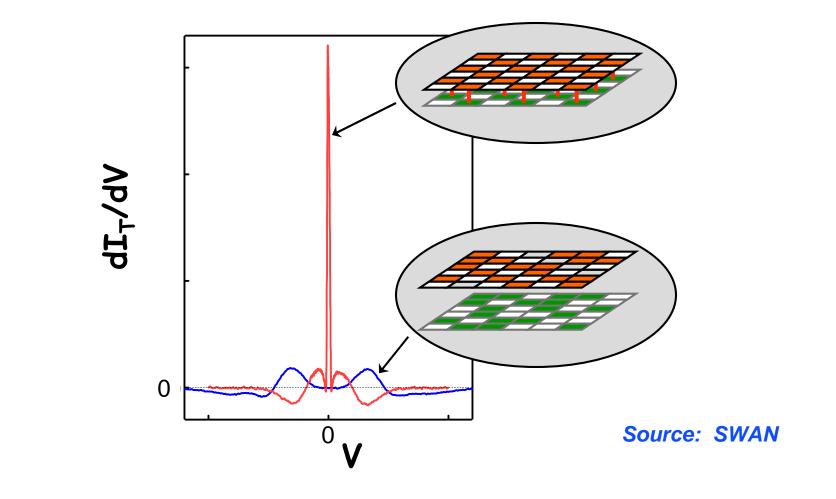

# **Pseudospintronics - Why?**

Spielman et al. PRL (2000) Kellogg et al. Wiersma et al., Tutuc et al. PRL (2004)

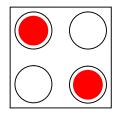

# **Quantum-Dot Cellular Automata**

#### A Quantum-Dot Cell

A cell with 4 dots

2 extra electrons

Represent binary information by charge configuration

#### An Array of Cells

Neighboring cells tend to align due to direct Coulomb coupling

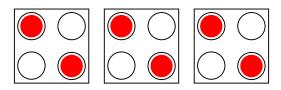

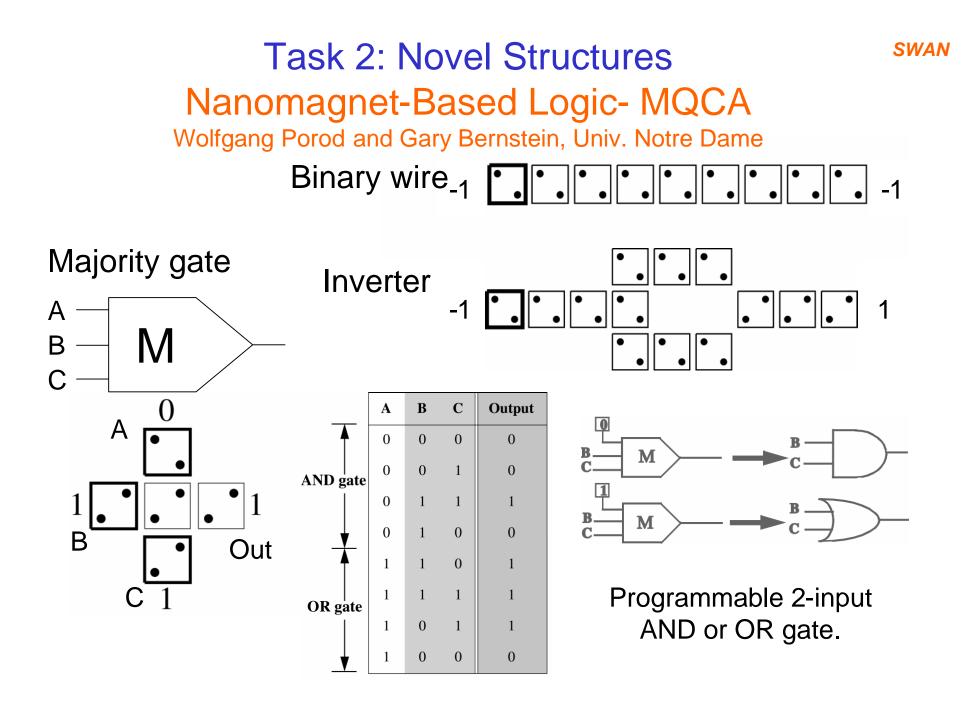

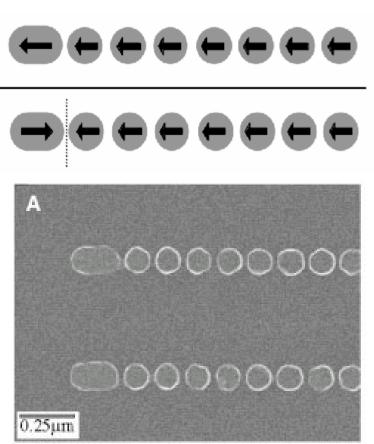

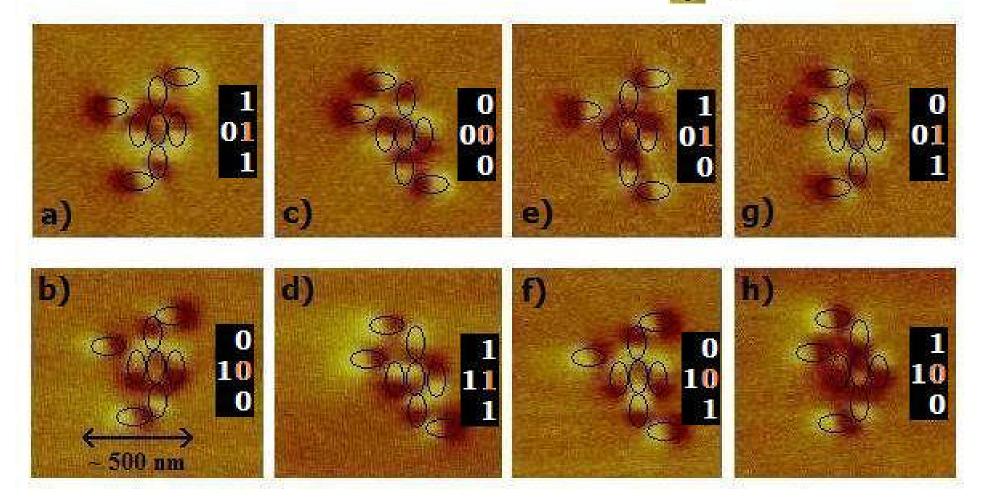

#### First room temperature magnetic "quantum-dot cellular automata"

R.P. Cowburn and M.E. Welland SCIENCE, VOLUME 287, 1466 (2000)

The circular dots, each of diameter 110 nm, placed on a pitch of 135 nm. The dots were 10 nm thick and were made from the common magnetic alloy supermalloy ( $Ni_{80}Fe_{14}Mo_5X_1$ , where X is other metals) by e-beam lithography and lift-off.

Evolution of a soliton propagating along a chain of coupled nanomagnets under the action of a 30Oe field applied:

#### Demonstration of majority gate operation

(Note that the output is inverted)

Source: SWAN

**SWAN**

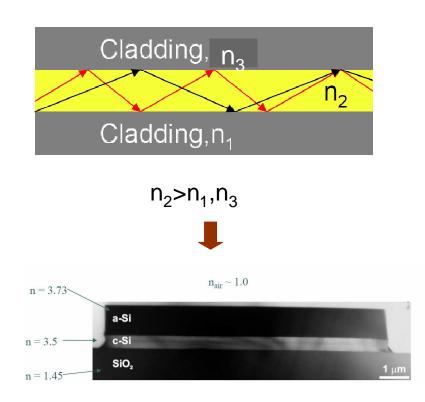

### **Optical Interconnects**

#### Planar optical interconnect

**Pros:**

- Broad bandwidth

- Faster medium

- Several channels through one data path

- Reduced interference and cross-talk

#### Cons:

- Transmitter and receiver units are required

- Diffraction limits miniaturization

- min(size) > wavelength/2

- IR-telecom: wavelength =  $1.55 \mu m$

- Difficult and lossy bending

H. Zimmerman, 2000.

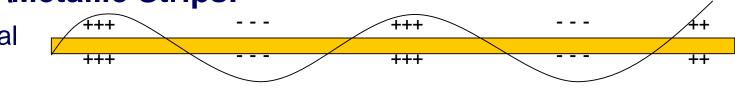

### **An Alternative: Surface Plasmons**

#### **Dielectric\Metallic Strips:**

Conceptual Model

- Plasmonic Waveguides

- High light-confinement

- Low bending loss

- Single mode propagation

- Fiber accessible

- Optoelectronic applications:

- Optical interface

- Filters

- Micro-cavities

- Directional couplers,...

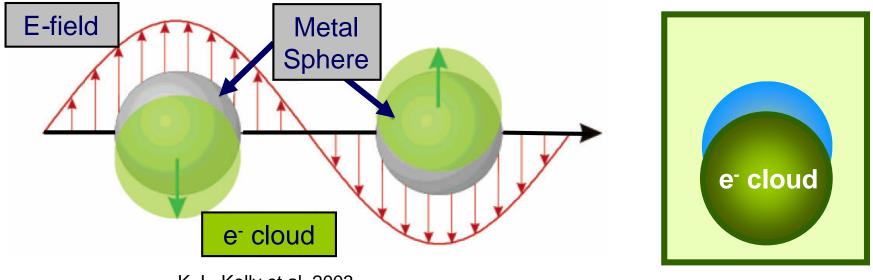

#### **Surface Plasmons on Nanoparticle "Wires"**

Oscillating electric field causes the conduction electrons to oscillate coherently.

- K. L. Kelly et al, 2003.

- Plasmonic waveguides enable sub-wavelength transmission

- Can propagate light at sharp edges

- Other applications include chemical sensing\detection

# And, we're not yet "crazy idea"-limited! e.g.: ~ any issue of Nature, Science, ...

#### **Devices:**

- "Intrinsic Localized Modes" <u>Physics Today</u>, 1/04

- "Slow Light" -- <u>Nature</u>, 7/11/03

- "Orbital Electronics" <u>Physics Today</u>, 7/03

#### **Self-Assembly of Devices:**

- "DNA-Templated CNT FET" <u>Science</u>, 11/03

- "Virus Toolkit for Directed Synthesis of Magnetic and Semiconducting Nanowires" -- <u>Science</u>, 1/9/04