#### **Michael Clinton**

Apr 23, 2008

IEEE – Dallas, TX

📲 Texas Instruments

#### Outline

- □ What's the problem?

- □ Bit Cell related design techniques

- Non-Bit Cell related design techniques

- Conclusion

#### □ What's the problem?

□ Bit Cell related design techniques

Non-Bit Cell related design techniques

Conclusion

### What's the problem?

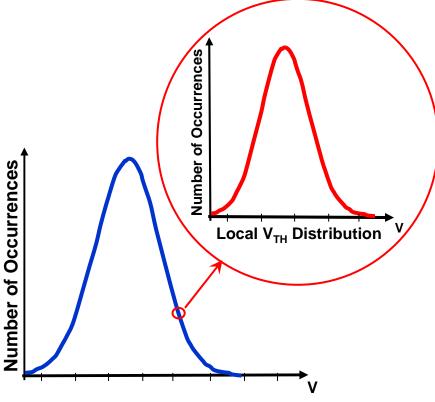

Global V<sub>TH</sub> Distribution

#### Sources of "Within Die Variation"

- Random Dopant Fluctuations (RDF)

- Line Edge Roughness (LER)

- Gate Stack (t<sub>OX</sub>, etc.)

- Lithography (ACLV, edge effects, etc.)

- Temperature and temperature gradients

- Different sensitivity to back gate bias

- Hot Carriers

- NBTI

$$\Rightarrow Local transistor mis-match:$$

$$\sigma_{Vth} = \sqrt{\sigma_{Vth}^{2}(RDF) + \sigma_{Vth}^{2}(LER) + \sigma_{Vth}^{2}(other)}$$

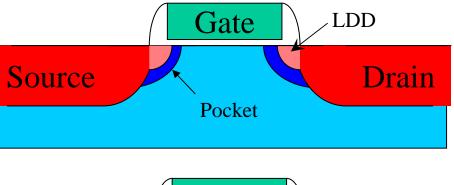

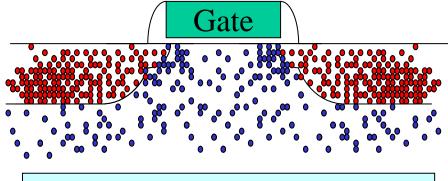

## Random Dopant Fluctuation (RDF) [2]

- Statistical variation in the number and placement of dopants in the channel

- At 32nm it is expected the channel doping may only be made up of <100 atoms.

David Scott, ISSCC 2007 Short Course, Texas Instruments

• The variability of V<sub>th</sub> due to RDF:

$$\sigma_{Vth} \propto 1/\sqrt{(WL)}$$

SRAM bit cell devices will have a higher  $\sigma V_{th}$  than the logic devices, due to the channel area difference

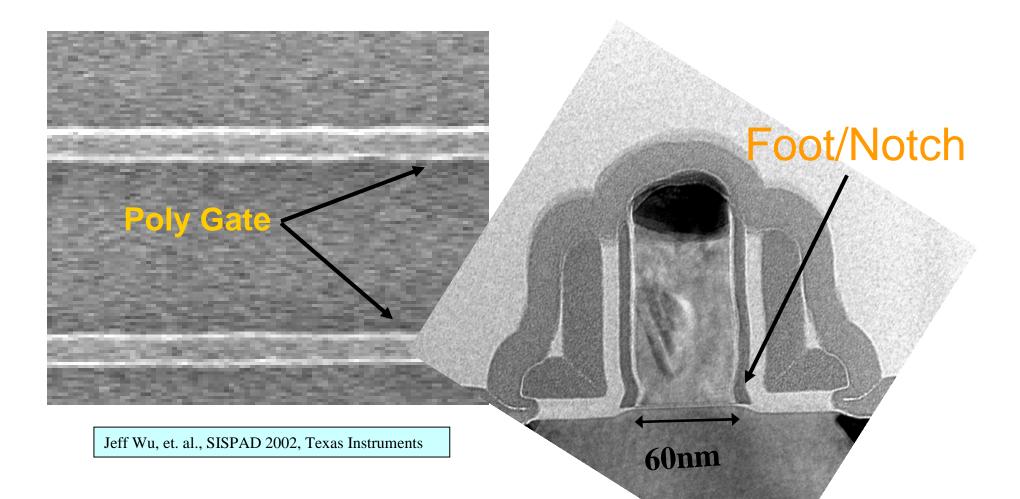

#### Line Edge Roughness (LER) [3]

## What's the problem for SRAM's?

#### Variability in the SRAM Bitcell

- Difficult to reduce the Operating Voltage (VDD<sub>MIN</sub>)

- Read Fails (SNM)

- Write Fails (VTRIP)

- Access Fails (I\_{\text{READ}} \text{ or } I\_{\text{CELL}})

- Data Retention Fails ( $V_{HOLD}$ )

- Increased leakage (IDDQ Fails)

#### Variability in the Sense Amp

- Increased input offset for differential BL sensing

- Decreased accuracy of timing tracking circuits

- Shifted trip points for large signal sensing

#### What are the consequences?

#### **Scaling less than Entitlement**

- Bit Cell & SRAM area is scaling less than 50%:

- -65nm: bit cell area > 0.50 um<sup>2</sup>

- -45nm: bit cell area > 0.25um<sup>2</sup>

- Difficult to get SRAM performance scaling

- SRAM VDD is not scaling

- SRAM leakage is increasing

#### U What's the problem?

#### Bit Cell related design techniques

- Minimum Operating voltage

- Read Margin improvement

- Write Margin improvement

- Alternative SRAM Bit Cell options

- IDDQ improvement

Non-Bit Cell related design techniques

#### **Summary**

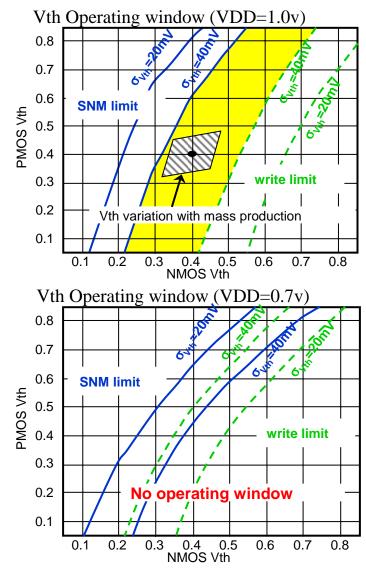

# **VDD<sub>MIN</sub> Failures** [6]

- The SRAM bit cell is much more sensitive to lowering VDD than standard logic gates

- The SRAM bit cell is a ratioed circuit which depends on the relative strengths of its transistors

- <u>Every</u> bit cell must work properly

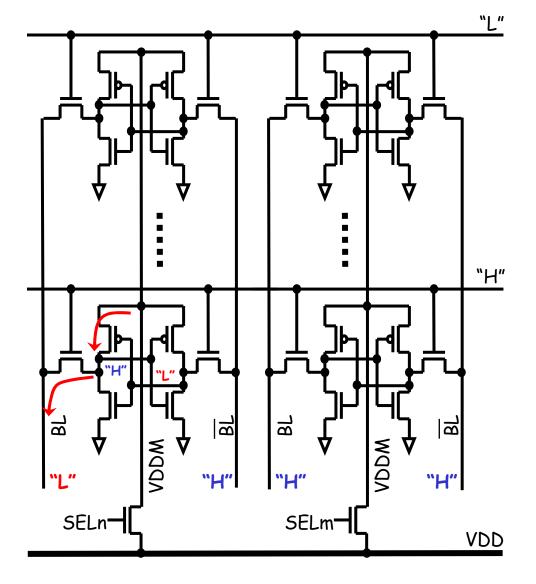

Diagrams: Masanao Yamaoka, et. al., VLSI 2004, Hitachi

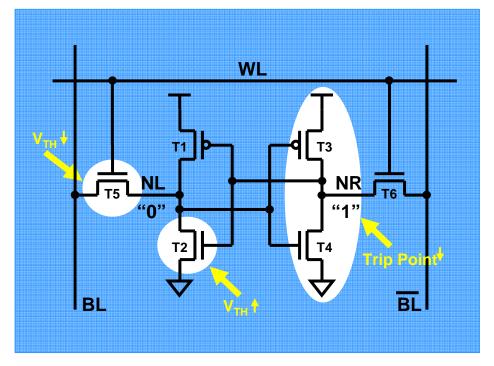

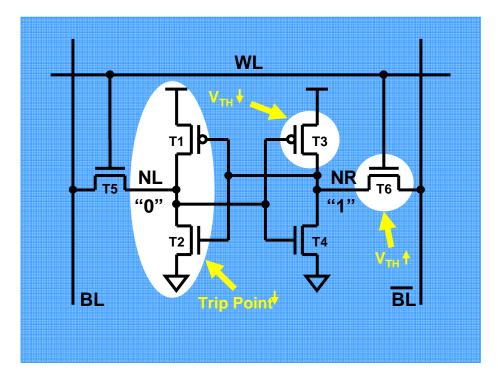

#### **READ Failures (SNM)**

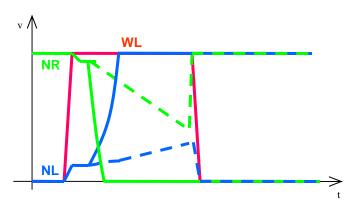

- When the WL turns on node NL will rise due to voltage divider action between T5 and T2

- If this level is higher than the trip point on of the INV(T3,T4) the latch will loose it's state: Read Failure

| Device | Vth M/M for Read Failures |

|--------|---------------------------|

| T1     | Decrease                  |

| T2     | Increase                  |

| Т3     | Increase                  |

| Τ4     | Decrease                  |

| Т5     | Decrease                  |

| Т6     | Increase                  |

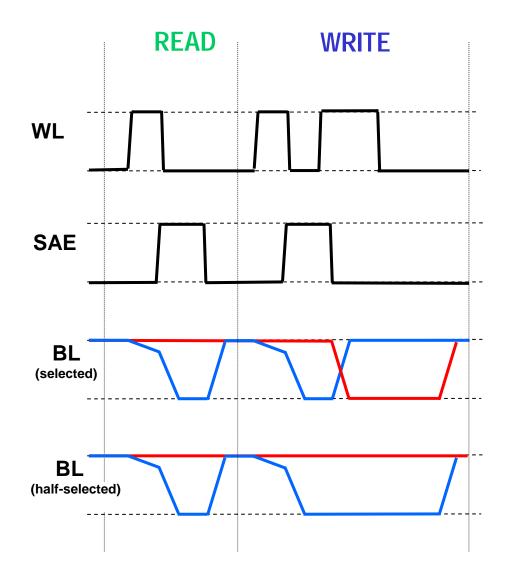

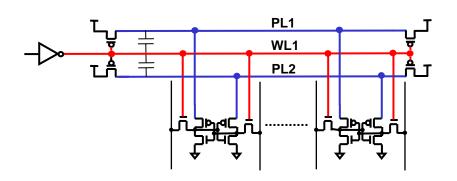

#### **Read Assist: Read & Write-Back**

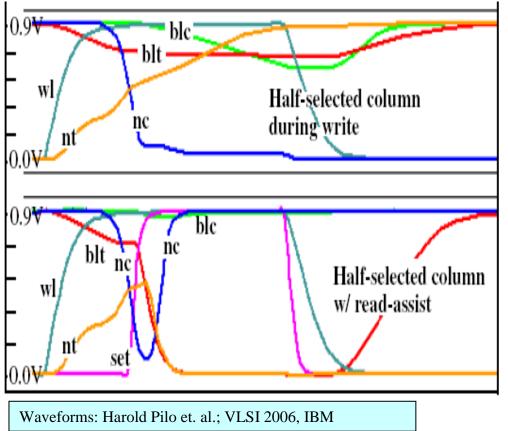

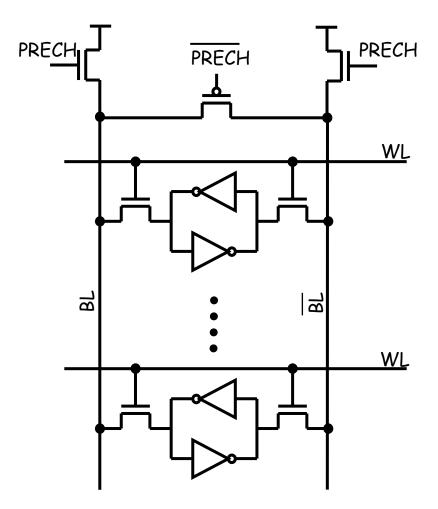

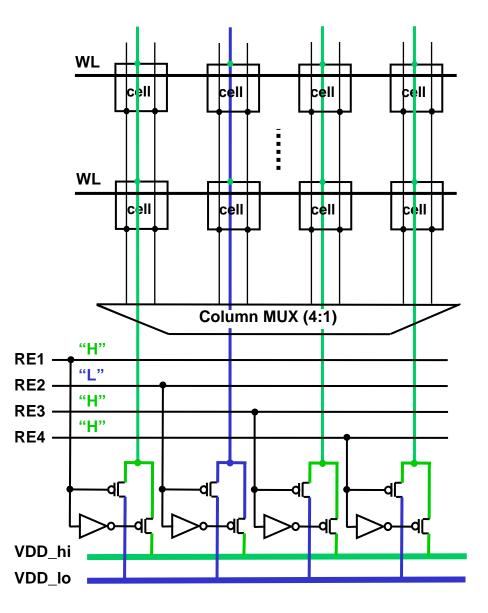

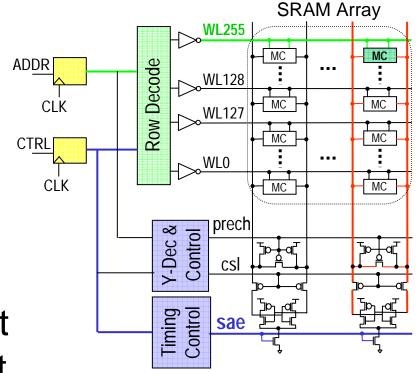

• SRAM's typically use a multiplexed column architecture

Columns with an active wordline, but not being accessed are "half-selected" columns

• The half-selected BL's have the greatest chance of causing an upset due to longer time the BL is at a high level

Placing a sense amp on every column amplifies the half selected columns on every read and write cycle (eliminating the half-selected state)

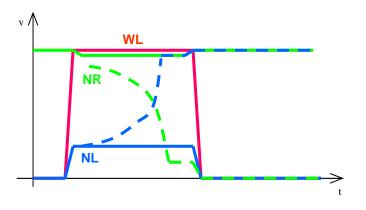

#### Read Assist: Pulsed Wordline (PWL)<sup>[8]</sup>

• Pulse WL only long enough to transfer signal to BL's, but not long enough to allow weak bits to flip

• Write requires wider WL pulse, so unselected columns must first be read then written back along with normal writes (aka Read-Modify-Write)

RMW requires Sense Amp on every column

#### Read Assist: Lower BL Precharge [8,10]

- When the WL turns on the voltage divider action between the PG and PD causes the low node of the bit to rise

- The optimum BL precharge voltage is VDD-V<sub>TH</sub>(PG)  $^{\rm 10}$

- Several proposals for generating the BL precharge voltage:

- Precharge with NMOS

- Pulsed BL pull-down

- Separate/generated supply

- Precharge levels below the optimum value cause a dramatic increase in fails due to disturb from the high node

#### Read Assist: Lower WL Level [11,12]

- The WL level is held below the memory VDD

- The gate drive of the Pass Gate is reduced, relative to the Pull-Down device and SNM is improved

- Read current is reduced, and write is more difficult

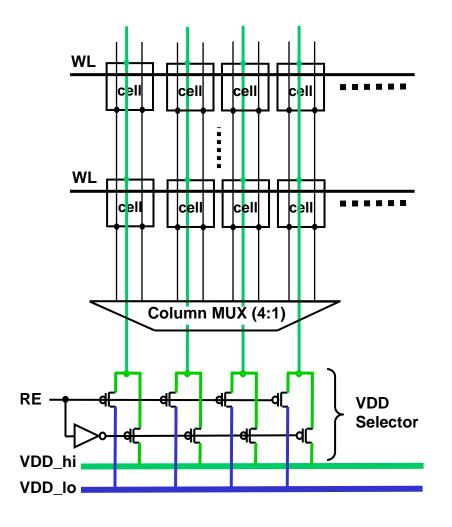

#### Read Assist: Raised VDD Level [15]

- Raise VDD level of the bit cell above the WL voltage

- This will increase the gate drive of the Pull-Down device and improve SNM

- During a read, VDD of all columns must be raised

- When the memory is inactive, the lower VDD will reduce leakage

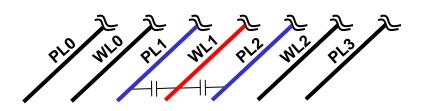

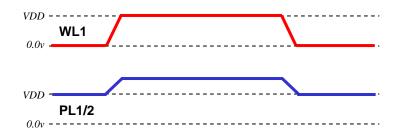

#### Read Assist: Raised VDD Level [9, 13]

• Raise VDD level of the bit cell above the WL voltage, using capacitive coupling

• This will increase the gate drive of the Pull-Down device and improve SNM

• This scheme does not require additional power supplies

### **Review: Read Assist Techniques**

- Control of the bit cell supplies can compensate for mis-match between the PG and PD transistors during a read operation and improve SNM

- Reduce influence of the bitline bias to stress bit cell SNM:

- Pulsed Wordline

- Amplify signal on all bitlines

- Short Bitlines

- Lower Bitline precharge level

- Reduce gate drive of PG relative to PD device

- Reduce Wordline level below the bit cell VDD level

- Increase gate drive of PD relative to PG device

- Raise bit cell VDD above Wordline level

- Raise the trip point of the cross-coupled inverters

#### **Write Failure**

- During a write node NR must be pulled low through T6

- If NR cannot be discharged below the trip point of INV(1,2), during the WL pulse, the result is a write failure

| Device | Vth M/M for Write Failures |

|--------|----------------------------|

| T1     | Increase                   |

| T2     | Decrease                   |

| Т3     | Decrease                   |

| T4     | Increase                   |

| Т5     | Increase                   |

| Т6     | Increase                   |

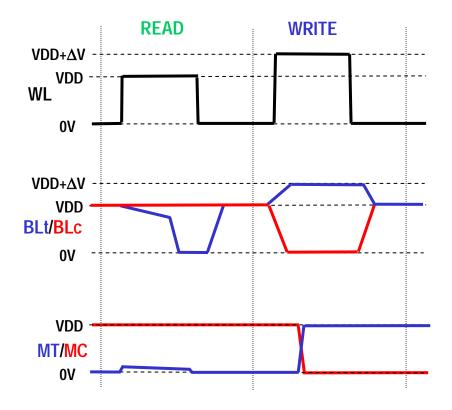

#### Write Assist: Lower VDD by Column [15]

- Similar to read assist techniques, we can dynamically change rail voltages and improve the write margin of the bitcell

- Write margin is improved with VDD lower than the WL voltage

- The gate drive of the PU device is reduced, relative to the Pass Gate

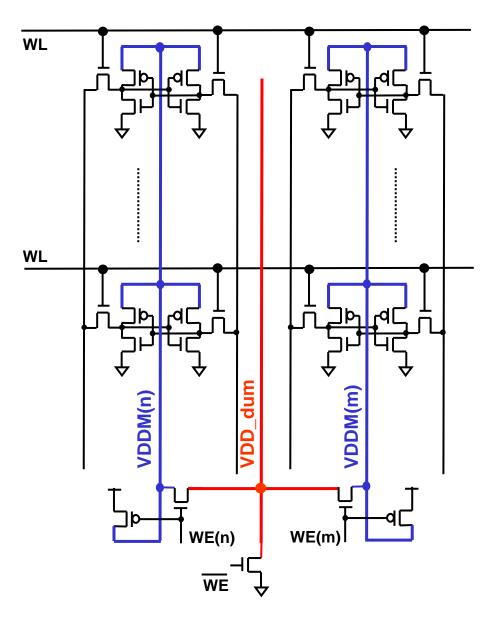

#### Write Assist: Lower VDD by Column [11,12]

• Typically, the VDD wire is not shared between adjacent columns

• The bit cell VDD is lowered below the WL level, thru a capacitive charge sharing scheme

#### Write Assist: Lower VDD by Column [16]

- Requires separate

VDD by column

- Float VDD of selected columns during a write

- This is a self-limiting technique: current flow will cease once the bit is written

- Lower VDD is shared with unselected rows along the same column

### Write Assist: Raised VSS [10,17]

- During a write VSS of the bit cell is floated

- When the wordline turns on the floating VSS begins to charge up

- The raised VSS level assists the write operation

- VSS is typically shared between adjacent columns, which raises SNM concerns on half-selected columns

- Unlike the "float VDD" scheme, this technique is not self limiting, so clamp devices are required

### Write Assist: Boosted WL [18]

- Driving the wordline to a voltage higher than the array VDD, will destabilize the accessed bit cell

- The gate drive of the Pass Gate is increased relative to the Pull-Up device, and VTRIP is improved

• Since the WL services all columns, all bit cells along the WL become unstable

Non-interleaved columns or a read and write-back scheme is required

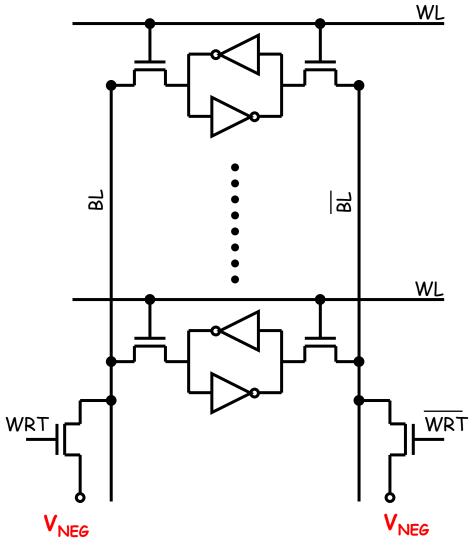

#### Write Assist: Negative Bitline Voltage

- During a write, connect the source of the driver to a negative voltage ( $V_{NEG}$ )

- The low BL will get pulled below VSS

- This will increase the gate drive of the PG relative to the PU device, and improve write margin

### **Review: Write Assist Techniques**

- Dynamic control of the bit cell supplies can compensate for mis-match between the Pass Gate and Pull-Up transistors during a write operation to improve WRITE margin:

- Reduce gate drive of Pull-Up relative to Pass Gate:

- Lower bit cell VDD

- Raised bit cell VSS

- Increase gate drive of the Pass Gate drive relative to Pull-Up device

- Boosted Wordline Voltage

- Negative Bitline Voltage

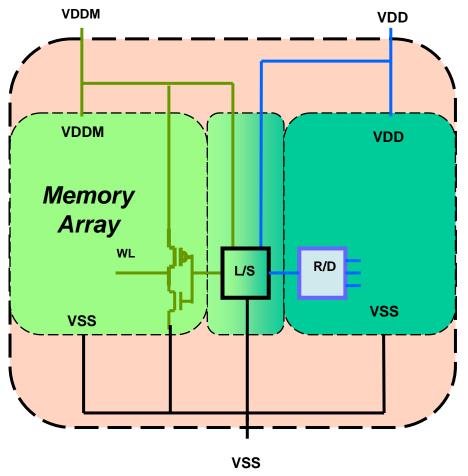

## Dual Rail Architecture [19]

- An alternative to using dynamic power rail techniques is the dual rail architecture

- Decouples logic VDD from SRAM bit cell constraints

- Chip level power routing is compromised and a second power supply is introduced

- Operate SRAM array at 1.2v for SNM, VTRIP and  $I_{READ}$

- Logic can operate with 0.7v to 1.2v VDD for low power

### **Alternative Bit Cells**

- At 45nm and 32nm; R/W Assist techniques or dual rail may not be sufficient to allow operation at low VDD

- $\bullet$  Bigger bit cells can have less variability, greater  $I_{\text{READ}}$  and better operating margins at low VDD levels

- If we consider bigger bit cells, there are alternatives to the standard 6T SRAM bit cell which can improve VDDmin operation

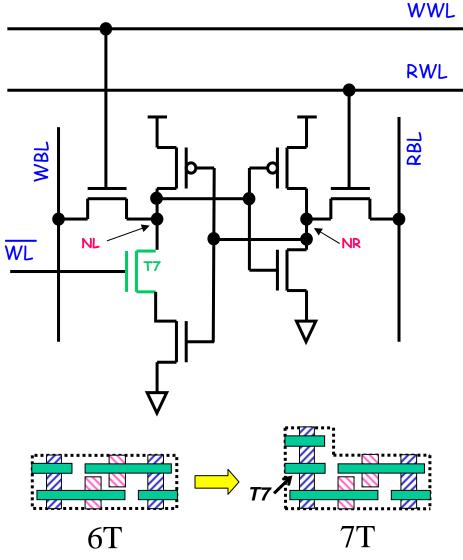

### Alternative SRAM Bit Cells: 7T [20]

- SNM-free bit cell

- Single-ended read

- Single-ended write

- Non-Interleaved columns

- Floating node issues

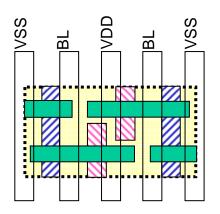

"L" shaped layout, allows precharge and sense amp devices to be placed throughout the memory array

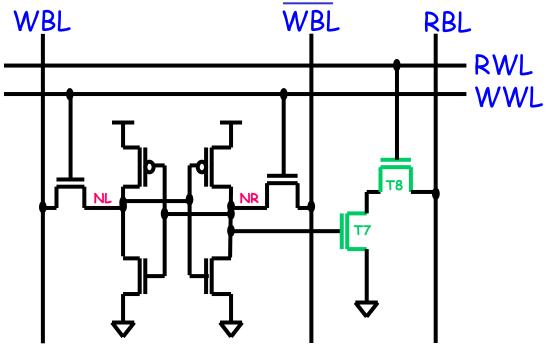

#### Alternative SRAM Bit Cells: 8T [21,43,44,45]

- SNM-free bit cell

- Single-ended read

- I<sub>READ</sub> is determined by read buffer

•Device sizes may be optimized to reduce leakage and V<sub>MIN</sub>

• The latch can be designed with very good write margin (i.e. poor stability when WWL is high)

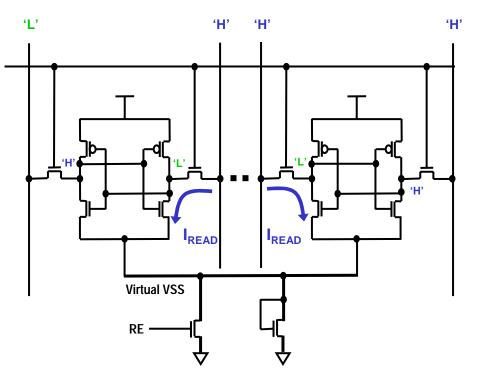

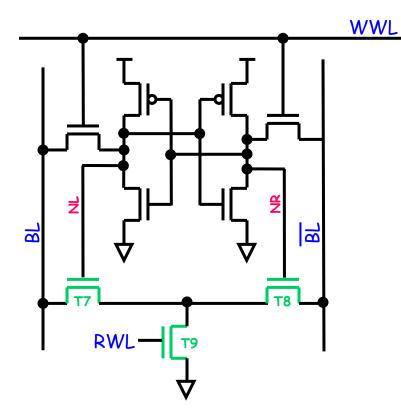

## Alternative SRAM Bit Cells: 9T [22]

- SNM-free bit cell

- Differential Sensing

- I<sub>READ</sub> is determined by T7/T8 and T9

- $\bullet$  Device sizes may be optimized to reduce leakage and  $V_{\text{MIN}}$

- The latch can be designed with very good write margin (i.e. poor stability when WWL is high)

### **Review: Alternative Bit Cells**

- Read margin and Write margin force conflicting requirements on the SRAM bit cell designer

- The alternative bit cell's discussed remove this conflicting requirement:

- Separate the read and write ports

- Margins associated with each of these operations can be improved without concern for the other

- Main problem with Alternative Bit Cells: AREA!!!

- More bit cell transistors

- Additional periphery circuits (e.g. WL drivers)

- Additional metal wires

- non-interleaved columns

## V<sub>HOLD</sub> Failures [29]

- SRAM leakage reduction techniques often apply the lowest possible voltage when the bit is not accessed

- If the bit cell cannot retain the proper data at the reduced voltage, this is referred to as a  $V_{\rm HOLD}$  failure

- V<sub>HOLD</sub> failures occur when the voltage on the high node is lower than the trip point of the latch

- In addition to lower VDD what can cause the high node to become lower than the trip point of the latch:

- Variability can increase driver transistor leakage

- Variability can reduce load transistor drive current

- Variability can shift the trip point of the latch

U What's the problem?

□ Bit Cell related design techniques

Non-Bit Cell related design techniques

- Sense Amps and Data Sensing

- Digital Techniques

Conclusion

## **Sense Amps and Data Sensing**

- Variability has always been an issue for S/A design

- Layout styles which reduce device mis-match

- Common mode noise rejection

- BL coupling noise reduction (twisting, shielding...)

- Design using statistical simulations & analysis

- At 45nm and 32nm, as device dimensions shrink, device mis-match poses much greater problems for the SRAM data path designer

- $\bullet$  Increased variability also leads to the occurrence of very low  $I_{\text{READ}}$  bit cell's

- Power, performance and area may be compromised in order to sense these weak bits

## Small Signal Sensing [32, 34]

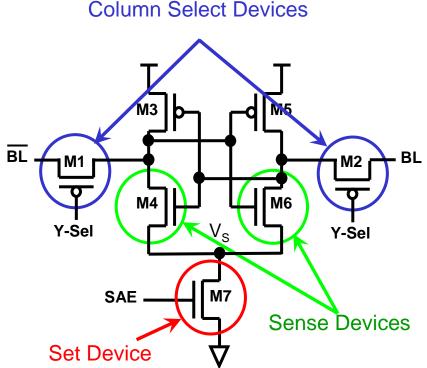

- How quickly node V<sub>S</sub> is pulled down to set latch can affect the influence of mismatch between set devices<sup>34</sup>

- $\bullet$  Ideally,  $V_{\rm S}$  is brought down slowly and after the latch starts setting in the right way,  $V_{\rm S}$  can be pulled to VSS

- Increasing device dimensions appropriately can reduce the probability of failure due to device mismatch by 99%<sup>32</sup>, but.....at a cost:

- Power, Performance and Area

# Sense Amp Enable Timing Variation

- Divergent timing paths for signal development and sense amp enable

- Transistor variability will affect these two paths differently

- The SAE timing circuit must allow for a slow bit and a fast timing path

• Various techniques used for SAE timing control; dummy MC's<sup>35</sup>, BL and WL RC tracking circuits......

## **Offset Cancellation Techniques**

• Auto-zero techniques have been described to cancel the input offset voltage of various S/A applications:

- DRAM's

- NVRAM's

- SRAM 's

- The general idea: measure the input offset of the S/A and adjust the input levels (voltage sense) or current levels (current sense) to zero-out the mismatch

- When applied to SRAM's these techniques have usually added too much complexity, area or delay

- Work continues in the OC area, but another option is to completely eliminate small signal sensing.....

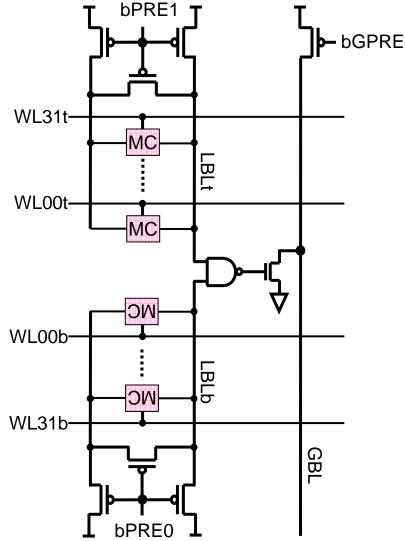

## Large Signal Sensing

- Issues related to sense amp device matching can be eliminated with large signal (typically single-ended) sensing schemes

- Just as the name implies, large signal sensing relies on the bit cell to develop a full logic level on the bitline

- Bitlines will be shorter than allowed with small signal sensing (for performance reasons)

- The low  $I_{READ}$  bit will still limit performance

- The full logic level is then "sensed" by a transistor, inverter or other type of logic gate (S/A enable timing no longer limits performance)

# Large Signal Sensing [37, 38, 44, 45]

- Small signal sensing is not scaling well:

- Performance: I<sub>READ</sub> and SAE timing variability is preventing entitlement

performance improvements

Area: in order to minimize

input offset, s/a area is not

scaling like logic

- Large signal sensing can offer performance and area scaling similar to logic

# **Review: Sense Amplifiers**

- Increased variability leads to larger input offset voltage for the SRAM sense amplifier

- As a result Sense Amp area and performance is not scaling with technology

- Several design techniques have been described which address the increased input offset:

- Selective upsizing of devices

- Adding additional transistors

- More effective timing control of SA enable

- Auto-Zeroing of input offset voltage

- Eliminate sense amps and use large signal sensing

Best suited to high performance designs

## **Digital Techniques Overview**

• The random variability being seen at 45nm and 32nm cannot be addressed simply by process modification or lithography compensation

• The circuit design techniques described earlier are effective ways to allow the SRAM bit cell to continue to operate with increased local variation

• Another design approach is to measure and compensate for variation with digital techniques

• Digital techniques use on-chip monitors or test structures which can evaluate the amount of device mis-match in a circuit and then feed this information back to the appropriate compensating circuit

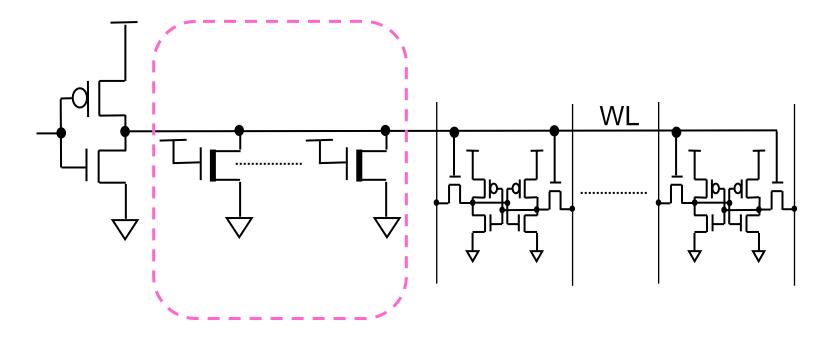

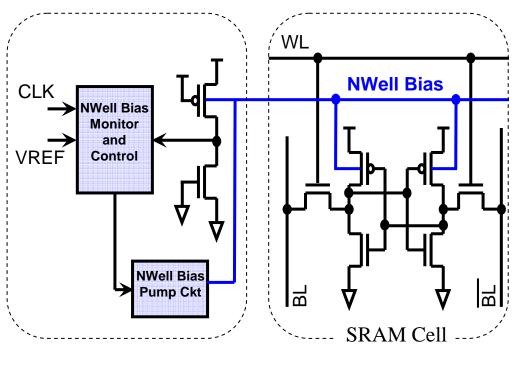

# **Digital Techniques** [27]

- Write margin degrades with a strong PU device and weak

PG device

- This circuit monitors the relative strength of the bit cell PMOS and NMOS

- An NWell pumping circuit which controls the bit cell NWell bias is raised or lowered

- $\bullet$  The  $V_{th}$  of the PMOS can be increased by raising the NWell bias voltage or decreased by lowering the bias

# **Review: Digital Techniques**

- Digital techniques generally employ a monitor and feedback system

- These techniques are effective in reducing die-die or global variation

- Digital techniques can also be used to limit the skew between NMOS and PMOS transistors

- Digital techniques are also being used to get a better balance between power and performance

- A more centered, less skewed design will be less sensitive to local variation and device mis-match

### Conclusion

- Transistor variability presents many problems for SRAM designers in nanometer-scale technologies

- During the course of this talk I have shown several of the innovative techniques being used by SRAM designers to meet this challenge

- Different applications will require different solutions:

Various circuit design techniques offer different trade-offs between power, performance and area

System/architecture options may be available

- Success in the future requires close collaboration between process/device/litho/manufacturing teams with the SRAM designer

### **Acknowledgements:**

**Ted Houston David Scott** Hugh Mair Wah Kit Loh Andrew Marshall Peter Rickert **Dennis Buss** Jeff Wu **Robert Baumann Clive Bittlestone** Ajith Amerasekera

#### **References (1)**

- 1. Harmander Singh Deogun1, Rahul Rao2, Dennis Sylvester1, Kevin Nowka2, "Adaptive MTCMOS for Dynamic Leakage and Frequency Control using Variable Footer Strength" SoC 2005, 1-University of Michigan, 2-IBM

- 2. D.Scott, International Solid-State Circuits Conference 2007 Short Course, Texas Instruments

- 3. J.Wu, Jihong Chen, Kaiping Liu, "Transistor Width Dependence of LER Degradation to CMOS Device Characteristics", (International Conference on Simulation of Semiconductor Processes and Devices (SISPAD) 2002, Texas Instruments

- 4. Evert Seevinck, Frans List, Jan Lohstroh, "Static-Noise Margin Analysis of MOS SRAM Cells", IEEE Journal of Solid-State Circuits, vol-22, no. 5, Oct. 1987

- 5. Saibal Mukhopadhyay, Hamid Mahmoodi, Kaushik Roy, "Modeling of Failure Probability and Statistical Design of SRAM Array for Yield Enhancement in Nanoscaled CMOS", IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems vol 24, no. 12, Dec 2005, Purdue University

- Masanao Yamaoka, Ken'ichi Osada, Ryuta Tsuchiya, Masatada Horiuchi, Shin'ichiro Kimura, Takayuki Kawahara, "Low Power SRAM Menu for SoC Application using Yin-Yang-Feedback Memory Cell Technology", 2004 Symposium on VLSI Circuits, Hitachi

- 7. Harold Pilo, John Barwin, Geordie Braceras, Chistopher Browning, Steve Burns, John Gabric, Steve Lamphier, Mark Miller, Al Roberts, Fred Towler, "An SRAM Design in 65nm and 45nm Technology Nodes Featuring Read and Write-Assist Circuits to Expand Operating Voltage", 2006 Symposium on VLSI Circuits, IBM

- Muhammad Khellah, Yibin Ye, Nam Sung Kim, Dinesh Somasekhar, Gunjan Pandya, Ali Farhang, Kevin Zhang, Clair Web, Vivek De, "Wordline & Bitline Pulsing Schemes for Improving SRAM Cell Stability in Low-Vcc 65nm CMOS Designs", 2006 Symposium on VLSI Circuits, Intel

- Azeez Bhavnagarwala, Stephen Kosonocky, Yuen Chan, Kevin Stawiasz, Uma Srinivasan, Steve Kowalczyk, Matt Ziegler, "A sub-600mV, Fluctuation tolerant 65nm CMOS SRAM Array with Dynamic Cell Biasing", 2007 Symposium on VLSI Circuits, IBM

- 10. Azeez Bhavnagarwala, Stephen Kosonocky, Carl Radens, Kevin Stawiasz, Randy Mann, Qiuyi Ye, Ken Chin, "Fluctuation Limits & Scaling Opportunities for CMOS SRAM Cells", IEDM 2005, IBM

- S.Ohbayashi, M.Yabuuchi, K.Nii, Y.Tsukamoto, S.Imaoka, Y.Oda, M.Igarashi, M.Takeuchi, H.Kawashima, H.Makino, Y.Yamaguchi, K.Tsukamoto, M.Inuishi, K.Ishibashi, H.Shinohara, "A 65nm Soc Embedded 6T-SRAM Design for Manufacturing with Read and Write Cell Stabilizing Circuits", 2006 Symposium on VLSI Circuits, Renesas

### **References (2)**

- Makato Yabuuchi1, Koji Nii1, Yasumasa Tsukamoto1, Shigeki Ohbayashi1, Susumu Imaoka2, Hiroshi Makino1, Yoshinobu Yamagami3, Satoshi Ishikura3, Toshio Terano3, Toshiyuki Oashi1, Keiji Hashimoto1, Akio Sebe3, Gen Okazaki3, Katsuji Satomi3, Hironori Akamatsu3, Hirofumi Shinohara1, "A 45nm Low-Standby-Power Embedded SRAM with Improved Immunity Against Process and Temperature Variations", IEEE International Solid-State Circuits Conference 2007, 1-Renesas Technology, 2-Renesas Design, 3-Matsushita

- Azeez Bhavnagarwala, Stephen Kosonocky, Stephen Kowalczyk, Rajiv Joshi, Yuen Chan, Uma Srinivasan, Jatinder Wadhwa, "A Transregional CMOS SRAM with Single, Logic VDD and Dynamic Power Rails", 2004 Symposium on VLSI Circuits, IBM

- 14. Jonathon.Chang, Jonathon Shoemaker, Mizan Haque, Ming Huang, Kevin Truong, Mesbah Karim, Siufu Chiu, Gloria Leong, Kiran Desai, Richard Goe, Sandhya Kulkarni, Arun Rao, Daniel Hannoun, Stefan Rusu, "A 0.13um Triple-Vth 9MB Third-Level On-Die Cache for the Itanium2 Processor", International solid-State circuits Conference 2004, Intel

- 15. Kevin Zhang, Uddalak Bhattacharya, Zhanping Chen, Fatih Hamzaoglu, Daniel Murray, Narendra Vallepalli, Yih Wang, Bo Zheng, Mark Bohr, "A 3GHz 70Mb SRAM in 65nm CMOS Technology with Integrated column-Based Dynamic Power Supply" IEEE Journal of Solid-State Circuits, vol 41, no. 1, Jan 2006, Intel

- 16. Masanao Yamaoka1, Noriaki Maeda2, Yoshihiro Shinozaki3, Yasuhisa Shimazaki2, Koji Nii2, Shigeru Shimada2, Kazumasa Yanagisawa2, Takayuki Kawahara1, "Low-Power Embedded SRAM Modules with Expanded Margins for Writing", 2005 IEEE International Solid-State Circuits Conference, 1-Hitachi, 2-Renesas, 3-Hitachi ULSI Systems

- 17. Masanao Yamaoka1, Yoshihiro Shinozaki2, Noriaki Maeda3, Yasuhisa Shimazaki3, Kei Kato4, Shigeru Shimada4, Kazumasa Yanagisawa4, Kenichi Osada1, 2004 IEEE International Solid-State Circuits Conference, 1-Hitachi, 2-Hitachi ULSI Systems, 3- SuperH, 4-Renesas

- Yasuhiro Morita1, Hidehiro Fujiwara2, Hiroki Noguchi3, Kentaro Kawakami2, Junichi Miyakoshi2, Shinji Mikami1, Koji Nii2, Hiroshi Kawaguchi3, Masahiko Yoshimoto3, "A Vth-Variation-Tolerant SRAM with 0.3V Minimum Operating Voltage for Memory-Rich SoC under DVS Environment", 2006 Symposium on VLSI Circuits, 1-Kanzawa University, 2-Kobe University, 3-Faculty of Engineering, Kobe University

- H.Mair, A.Wang, G.Gammie, D.Scott, P.Royannez, S.Gururajarao, M.Chau, R.Lagerquist, L.Ho, M.Basude, N.Culp, A.Sadate, D.Wilson, F.Dahan, J.Song, B.Carlson, U.Ko, "A 65nm Mobile Multimedia Applications Processor with an Adaptive Power Management Scheme to Compensate for Variations", 2007 Symposium on VLSI Circuits, Texas Instruments

- 20. Koichi Takeda, Yasuhiko Hagihara, Yoshiharu Aimoto, Masahiro Nomura, Yoetsu Kakazawa, Toshio Ishii, Hiroyuki Kobatake, "A Read-Static Noise-Margin-Free SRAM Cell for Low-VDD and High-Speed Applications", IEEE Journal of Solid-State Circuits, vol 41, no. 1, Jan 2006, NEC

### **References (3)**

- 21. Naveen Verma, Anantha Chandrakasan, "A 65nm 8T sub-Vth SRAM Employing Sense-Amplifier Redundancy", International Solid-State Circuits Conference 2007, MIT

- 22. Zhiyu Liu, Volkan Kursan, "High Read Stability and Low Leakage SRAM Cell Based on Data/Bitline Decoupling", SoC 2006, University of Wisconsin

- H.Kawasaki, K.Okano, A.Kaneko2, A.Yagishita2, T.Izumida, T.Kanemura, K.Kasai, T.Ishida, T.Sasaki, Y.Takeyama, N.Aoki, N.Ohtsuka, K.Suguro2, K.Eguchi2, Y.Tsunashima2, S.Inaba, K.Ishimaru, H.Ishiuchi, "Embedded Bulk FinFET SRAM Cell Technology with Planar FET Periphery Circuit for hp32nm node and beyond", 2006 Symposium on VLSI Technology, Toshiba

- 24. Chris Hyung-il Kim, Jae-Joon Kim, Saibal Mukhopadhyay, Kaushik Roy, "A Forward Body-Biased Low-Leakage SRAM Cache: Device, Circuit and Architecture Considerations", IEEE Transactions on VLSI Systems, vol 13, no. 3, Mar 2005

- F.Jummel, P.Royannez, H.Mair, D.Scott, A.ErRachidi, R.Lagerquist, M.Chau, S.Gururajarao, S.Thiruvengadam, M.Clinton, V.Menezes, R.Hollingsworth, J.Vaccani, F.Piacibello, N.Culp, J.Rosal, M.Ball, F.Ben-Amar, L.Bouetel, O.Domerego, J.Lachese, C.Fournet-Fayard, J.Ciroux, C.Raibaut, U.Ko, "A Leakage Management System Based on Clock Gating Infrastructure for a 65nm Digital Base-Band Modem Chip", 2006 Symposium on VLSI Circuits, Texas Instruments

- 26. Yasuhisa Takeyama, Hiroyuki Otake, Osamu Hirabayashi, Keiichi Kushida, Nobuaki Otsuka, "A Low Leakage SRAM Macro with Replica Cell Biasing Scheme", IEEE Journal of Solid-State Circuits, vol 41, no. 4, April 2006, Toshiba

- 27. Kouichi Kanda, Takayuki Miyazaki, Min Kyeong Sik, Hiroshi Kawaguchi, Takayasu Sakurai, IEEE ASIC/SOC Conference 2002, University of Tokyo

- 28. Koji Nii, Yoshihiro Tenoh2, Tomoaki, Yoshizawa Susumu Imaoka2, Yasumasa Tsukamoto, Yoshinobu Yamagami3, Toshikazu Suzuki3, Akinori Shibayama3, Hiroshi Makino, Shuhei Iwade, "A 90nm Low Power 32KB Embedded SRAM with Gate Leakage Suppression Circuit for Mobile Applications", 2003 Symposium on VLSI Circuits, 1-Mitsubishi System LSI Development Center, 2-Mitsubishi Electronic Devices Design Center, 3-Matsushita

- 29. Saibal Mukhopadhyay, Hamid Mahmoodi-Meimand, Kaushik Roy, "Modeling and Estimation of Failure Probability due to Parameter Variations in Nano-scale SRAM's for Yield Enhancement", 2004 Symposium on VLSI Circuits, Purdue University

- 30. Robert Baumann, "The Impact of Single Event Effects on Advanced Digital Technologies", International Test Conference 2005, Texas Instruments

- 31. Qian Ding, Rong Luo, Hui Wang, Huazhong Yang, Yuan Xie2, "Modeling the Impact of Process Variation on Critical Charge Distribution", System-on-Chip Conference 2006, Tsinghua University, 2-Pennsylvania State University

- 32. Joyce Yeung, Hamid Mahmoodi, System-on-Chip Conference 2006, San Francisco State University

- 33. Sang Dhong1, Osamu Takahashi1, Michael White1, Toru Asano2, Takaaki Nakazato2, Joel Silberman3, Atsushi Kawasumi4, Hiroshi Yoshihara5, "A 4.8GHz Fully Pipelined SRAM in the Streaming Processor of a CELL Processor", International Solid-State Circuits Conference 2005, 1-IBM Austin, 2-IBM Japan, 3-IBM Yorktown, 4-Toshiba, 5-Sony

### **References (4)**

- 34. Ravpreet Singh1, Navakanta Bhat2, "An Offset Compensation Technique for Latch Type Sense Amplifiers in High-Speed Low-Power SRAM's", IEEE Trans. on VLSI Systems, vol 12, no. 6, June 2004, 1-Texas Instruments,2-Indian Institute of Science

- 35. Kenichi Osada, Jin-Uk Shin, Masood Khan, Yu-de Liou, Karl Wang, Kenichi Shoji, Kenichi Kuroda, Shuji Ikeda, Koichiro Ishibashi, "Universal-Vdd 0.65-2.0v 32kB Cache using Voltage-Adapted Timing-Generation Scheme and a Lithographical-Symmetric Cell", International Solid-State Circuits Conference 2001, Hitachi

- 36. Sang Hoon Hong, Si Hong Kim, Jae-Kyung Wee, Jin Yong Chung, "An Offset Cancellation Bit-Line Sensing Scheme for Low-Voltage DRAM Applications", International Solid-State Circuits Conference 2002, Hynix Semiconductor

- 37. K.Zhang, K.Hose, V.De, B.Senyk, "Scaling of Data Sensing Schemes for High Speed Cache Design in sub-0.18um Technologies", 2000 Symposium on VLSI Circuits, Intel

- 38. Don Weiss1, John Wuu1, Victor Chin2, "The On-Chip 3MB Subarray Based 3<sup>rd</sup> Level Cache on an Itanium Microprocessor", International Solid-State Circuits Conference 2002, 1-Hewlett-Packard, 2-Intel

- 39. Y.Wang, H.Ahn, U.Bhattacharya, T.Coan, F.Hamzaoglu, W.Hafez, C-H.Jan, P.Kolar, S.Kulkarni, J.Lin, Y.Ng, I.Post, L.Wei, Y.Zhang, K.Zhang, M.Bohr, "A 1.1GHz 12uA/Mb-Leakage SRAM Design in 65nm Ultra-Low-Power CMOS with Integrated Leakage Reduction for Mobile Applications", IEEE International Solid-State Circuits Conference 2007, Intel

- 40. Jonathan Chang, Ming Huang, Jonathan Shoemaker, John Benoit, Szu-Liang Chen, Wei Chen, Siufu Chiu, Raghuraman Ganesan, Gloria Leong, Venkata Lukka, Stefan Rusu, Durgesh Srivastava, "The 65nm 16MB On-Die L3 Cache for a Dual Core Multi-Threaded Xeon Processor", 2006 Symposium on VLSI Circuits, Intel

- 41. Saibal Mukhopadhyay, Swaroop Ghosh, Keejong Kim, Kaushik Roy, "Low-Power and Process Variation Tolerant Memories in sub-90nm Technologies", System-on-Chip Conference 2006, Purdue University

- 42. Chris Hyung-il Kim1, Jae-Joon Kim2, ik-Joon Chang3, Kaushik Roy3, "PVT-Aware Leakage Reduction for On-Die Caches with Improved Read stability", IEEE Journal of Solid-State Circuits, vol 41, no. 1, Jan 2006, 1-University of Minnesota, 2-IBM, 3-Purdue University

- 43. Yasuhiro Morita1, Hidehiro Fujiwara1, Hiroki Noguchi1, Yusuke Iguchi1, Koji Nii1,2, Hiroshi Kawaguchi1, Masahiko Yoshimoto1, "An Area-Conscious Low-Voltage-Oriented 8T-SRAM Design under DVS environment", 2007 Symposium on VLSI Circuits, Kobe University, 2-Renesas

- 44. Leland Chang, Yutaka Nakamura, Robert Montoye, Jun Sawada, Andrew Martin, Kiyofumi Kinoshita, Fadi Gebara, Kanak Agarwal, Dhruva Acharyya, Wilfred Haensch, Kohji Hosokawa, Damir Jamsek, "A 5.3GHz 8T-SRAM with Operation Down to 0.41v in 65nm CMOS", 2007 Symposium on VLSI Circuits, IBM

- 45. R.Joshi, R.Houle, K.Batson, D.Rodko, P.Patel, W.Huott, R.Franch, Y.Chan, D.Plass, S.Wilson, P.Wang, "6.6+ GHz Low Vmin, Read and Half Select Disturb-Free 1.2Mb SRAM", 2007 Symposium on VLSI Circuits, IBM