### Two Zero Two Pole Active Compensation Replaces a Charge Pump and Regulator in PLLs 6-25-08

Stanley J. Goldman Texas Instruments

### Agenda

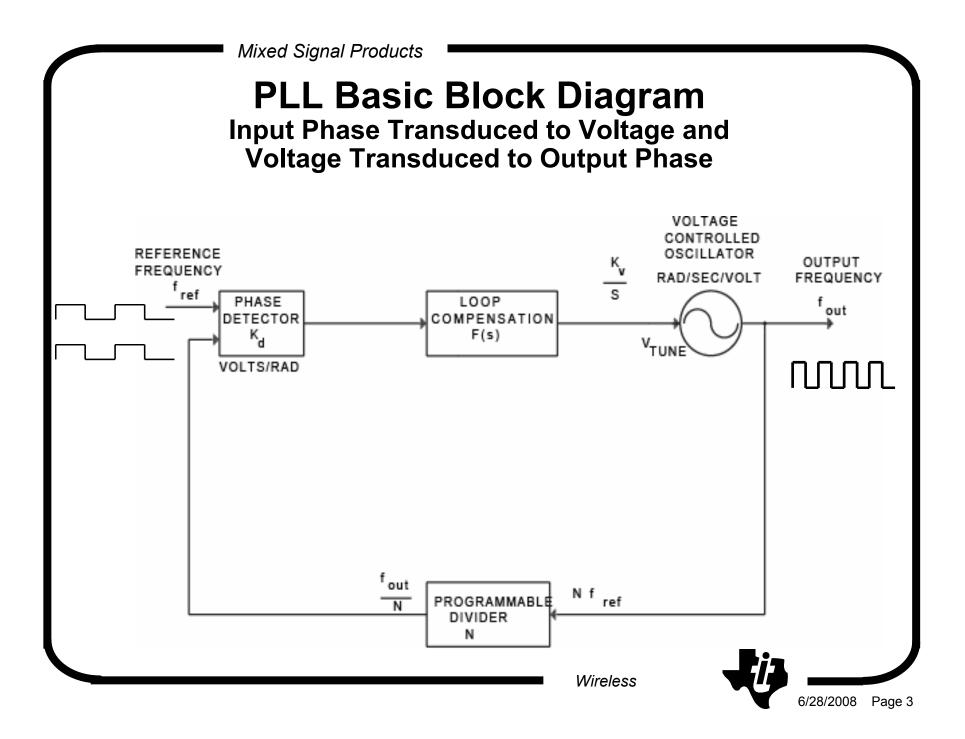

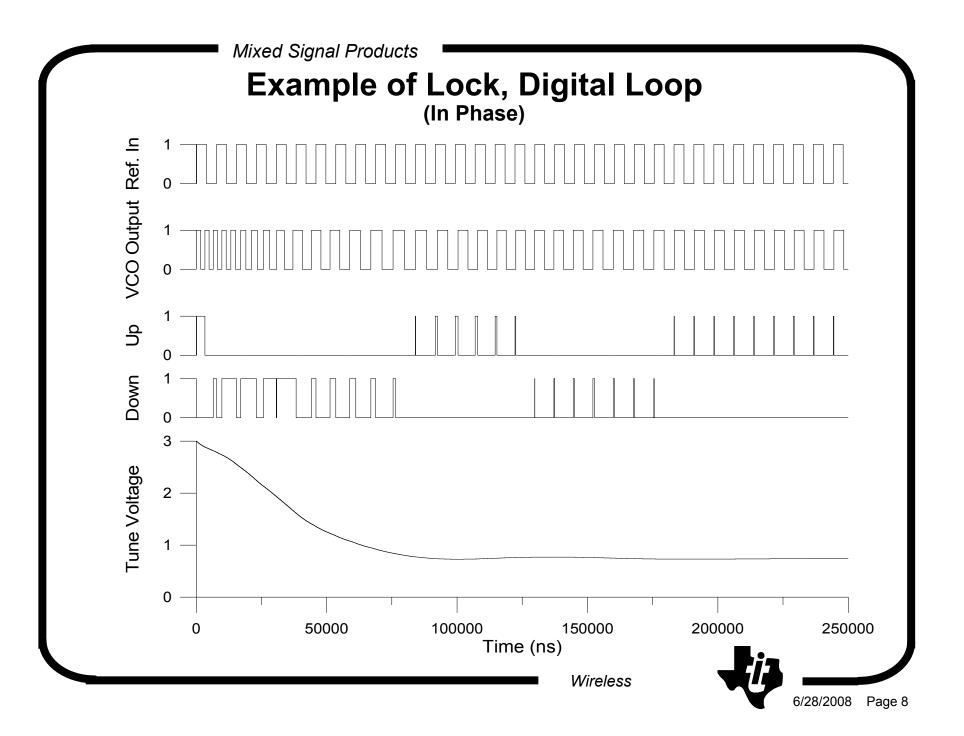

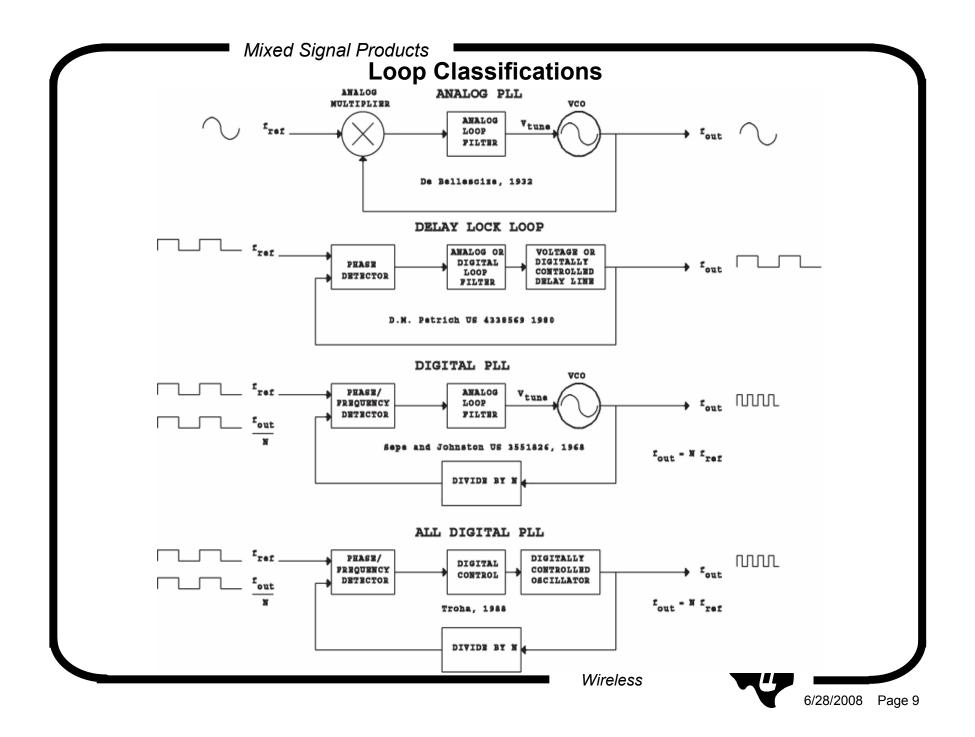

- PLL Review

- Various Loop Filters

- 2 Zero 2 Pole Plots and Equations

- 2 Zero 2 Pole Results

### Comparison of PLL Loop Filters with Regulators driving VCO

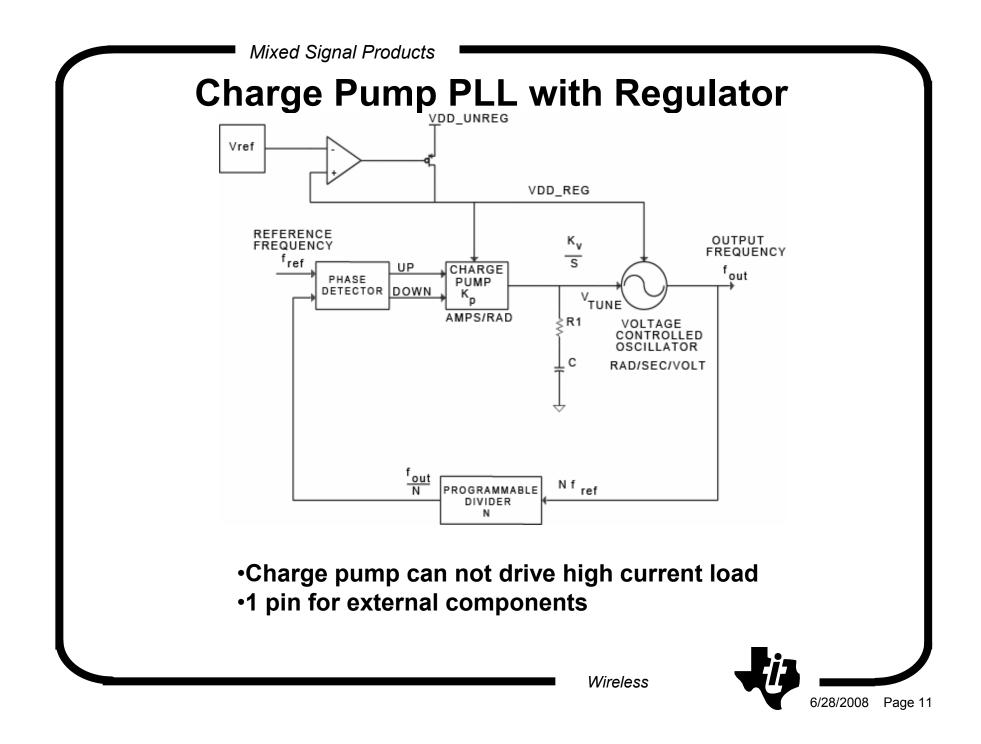

- Charge pump PLL

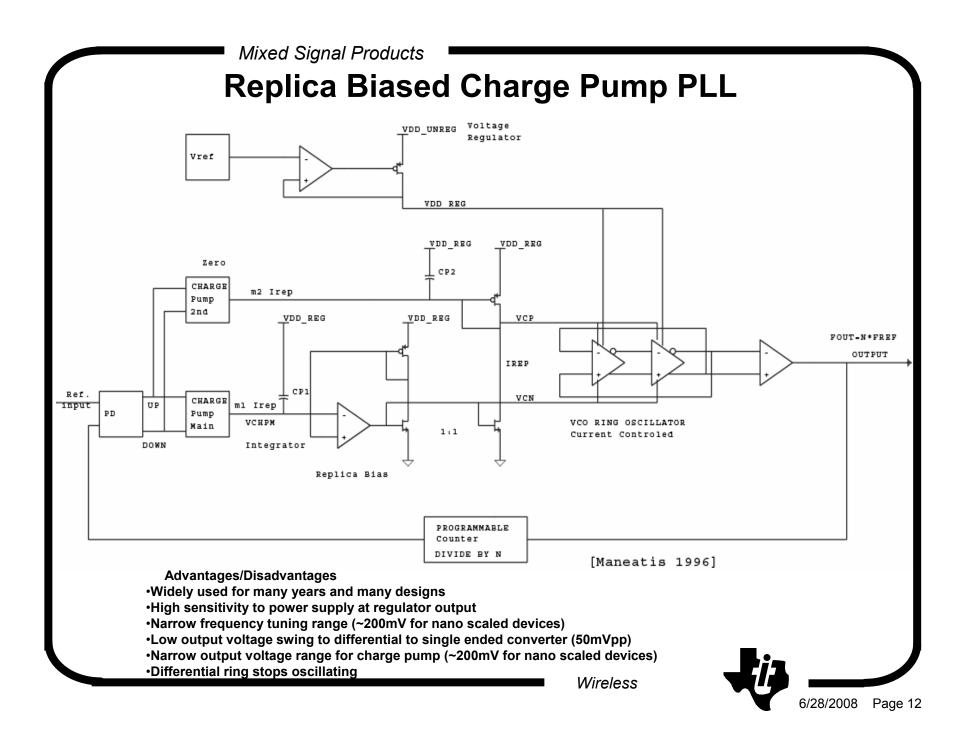

- Replica Bias PLL

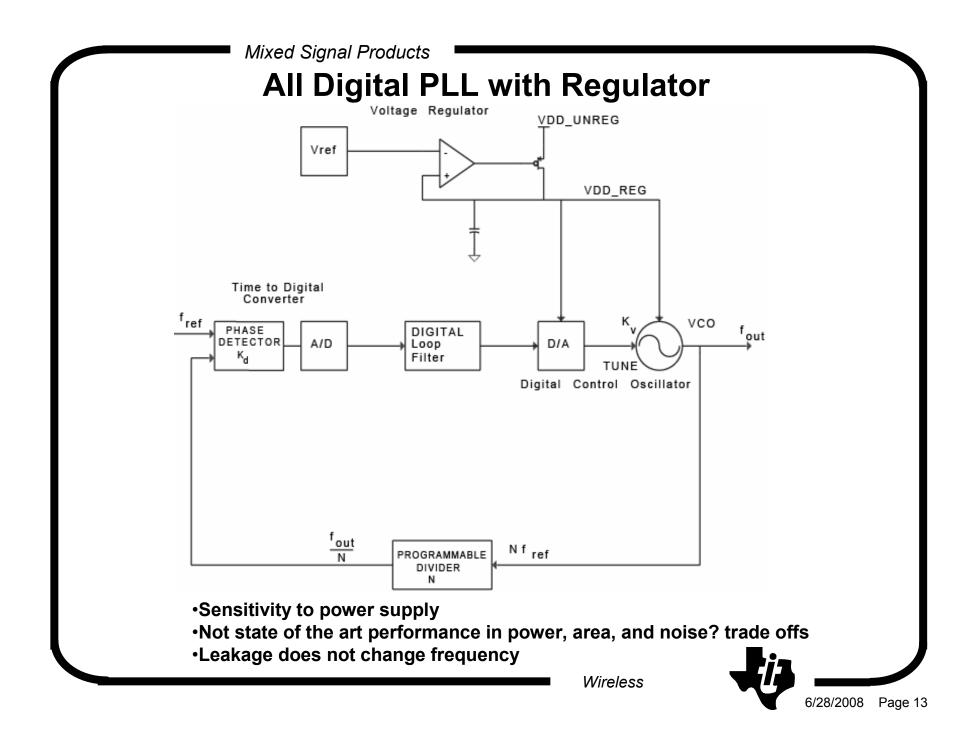

- Digital PLL

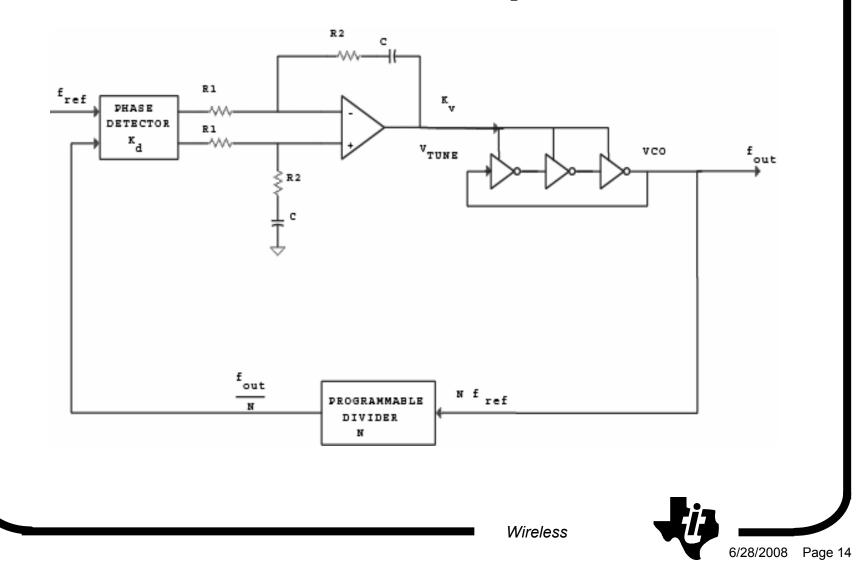

- 1 Zero Active PLL

### **1 Zero Active Compensation**

#### 1 Zero, Type 2 Second Order Open Loop Gain Function (Active Filter)

Cascade of Transfer functions for Open Loop Gain

G(s)H(s)= (Phase Detector Gain)(Filter Transfer Function) (VCO Transfer Function)(Divider Transfer Function)

Substitute and Rearrange for Open Loop Gain Expression

$$G(s) \cdot H(s) = \frac{K_{d} \cdot K_{v}}{n_{mf} \cdot C \cdot R_{1}} \cdot \left(\frac{1}{s^{2}}\right) \cdot \left(s \cdot C \cdot R_{2} + 1\right)$$

Substitute and Rearrange for Closed Loop Gain Expression

$$\frac{G(s)}{1 + G(s) \cdot H(s)} = \frac{\frac{K_{d} \cdot K_{v}}{C \cdot R_{1}} \cdot \left[\frac{s}{\left(\frac{1}{C \cdot R_{2}}\right)} + 1\right]}{s^{2} + s \cdot \left(\frac{K_{d} \cdot K_{v}}{n_{mf}} \cdot \frac{R_{2}}{R_{1}}\right) + \frac{K_{d} \cdot K_{v}}{n_{mf} \cdot C \cdot R_{1}}}$$

- <sup>c</sup>d = Phase detector gain (volts/radian),

- VCO transfer function gain constant (radians/second/volt),

$n_{mi}$  = Integer divider value,

- = Loop Frequency Multiplication Factor,

- = Output frequency/ input frequency,

- C = Capacitor in the operational amplifier's feedback path (F),

- R<sub>1</sub> = Resistor in operational amplifier's feedback path (ohms) and,

- R<sub>2</sub> = Resistor at the negative input terminal of the operational amplifier (ohms).

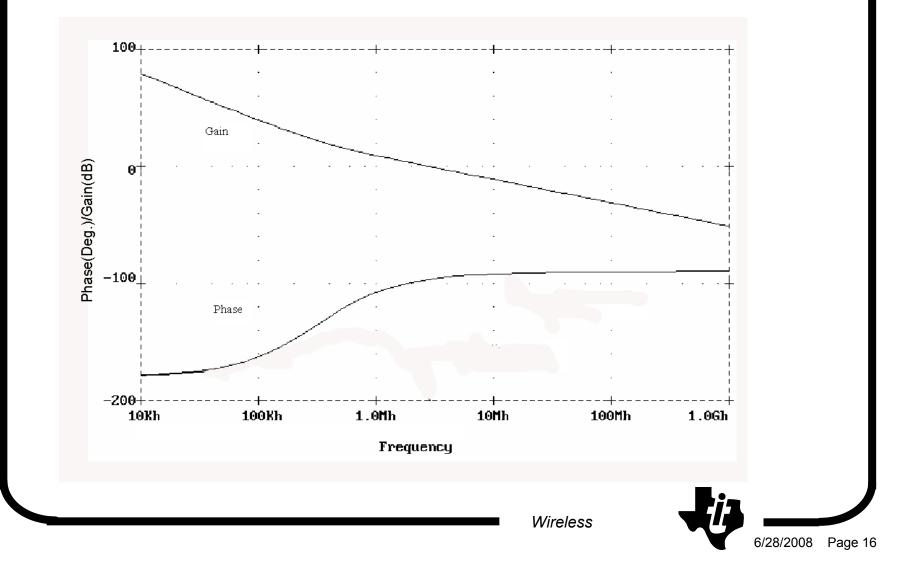

#### Uncentered Type 2 1 Zero Open Loop Magnitude and Phase, 1MHz Bandwidth example

- OPAMP Replacing a Charge Pump

- Wider Supply Operating Range, Rail to Rail

- Lower Voltage drop out

- Linear Differential to Single Ended Conversion

- Sources VCOs that draw current

- No power down resets

- Acts as voltage regulator to minimize sensitivity to power supply

- Flexibility in Compensation Polynomials

- 2 Zero 2 Pole Compensation

- >90 deg. Added to Phase Margin

- Wider Bandwidth

- Wider and Optimum Stable Region for less process sensitivity

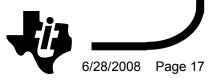

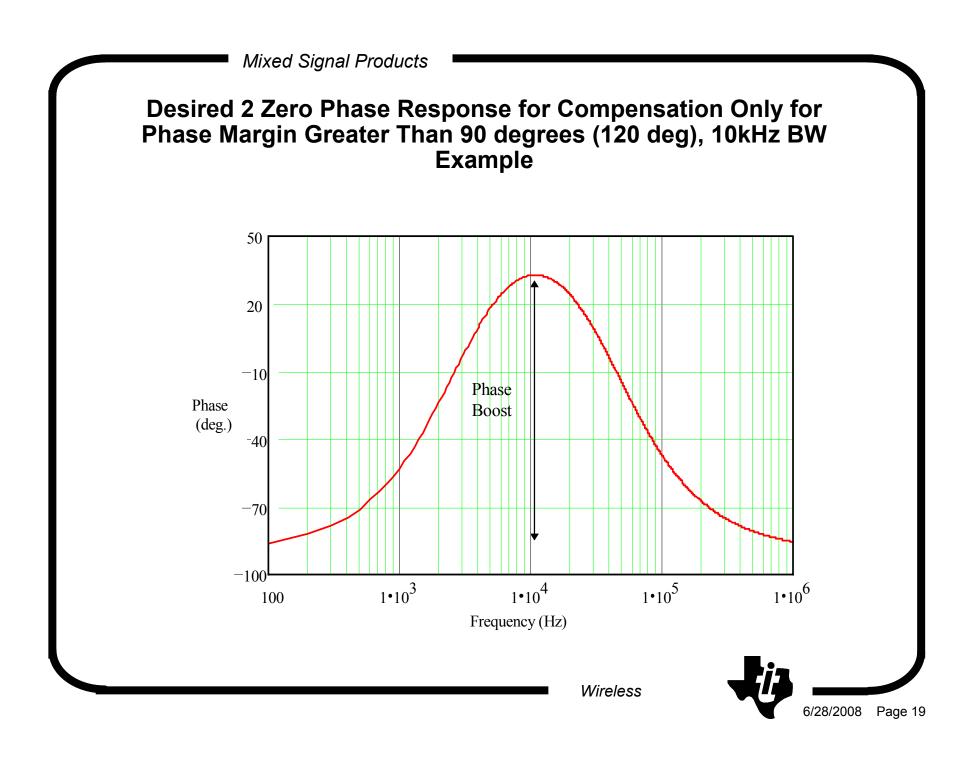

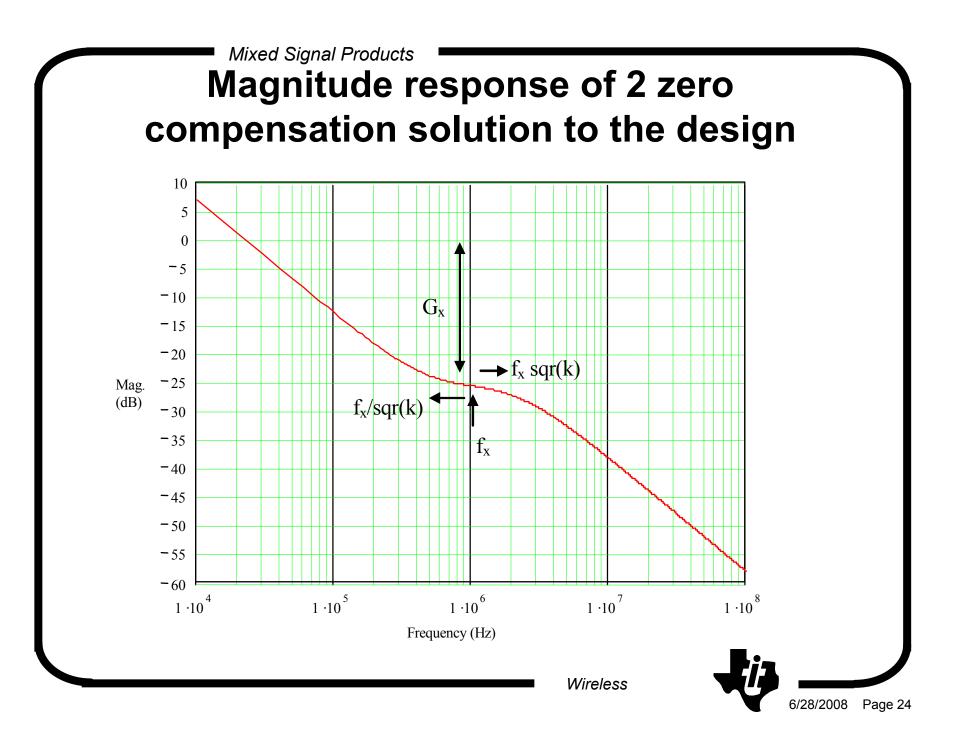

Desired high phase boost example of 2 zero 2 Pole magnitude response for compensation only and phase margin greater than 90 degrees, 10kHz BW Example

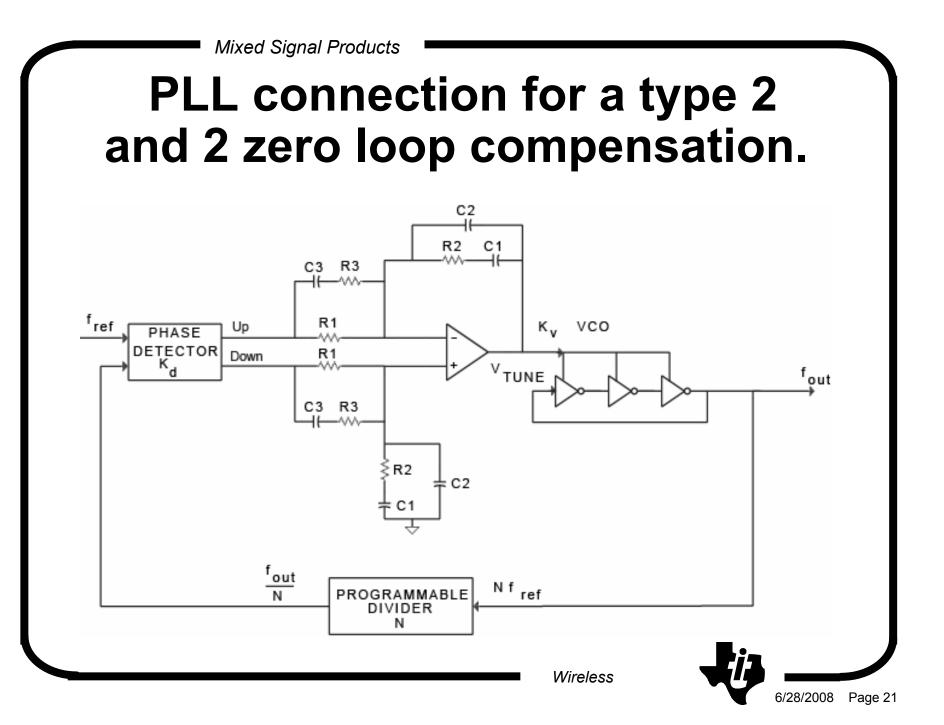

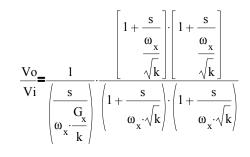

### 2 Zero 2 Pole Open Loop Transfer Function Equations

$$\frac{\mathbf{V}_{o}}{\mathbf{V}_{i}} = \frac{1}{\mathbf{s} \cdot \left(\mathbf{C}_{1} + \mathbf{C}_{2}\right) \cdot \mathbf{R}_{1}} \cdot \frac{\mathbf{s} \cdot \mathbf{C}_{1} \cdot \mathbf{R}_{2} + 1}{1 + \mathbf{s} \cdot \mathbf{R}_{2} \cdot \mathbf{C}_{2} \cdot \left(\frac{\mathbf{C}_{1}}{\mathbf{C}_{1} + \mathbf{C}_{2}}\right)} \cdot \frac{\mathbf{s} \cdot \left(\mathbf{R}_{1} + \mathbf{R}_{3}\right) \cdot \mathbf{C}_{3} + 1}{\mathbf{s} \cdot \mathbf{R}_{3} \cdot \mathbf{C}_{3} + 1}$$

$G_{x} = \frac{1}{\left(\frac{K_{d} \cdot K_{v}}{N \cdot \omega_{v}}\right)}$

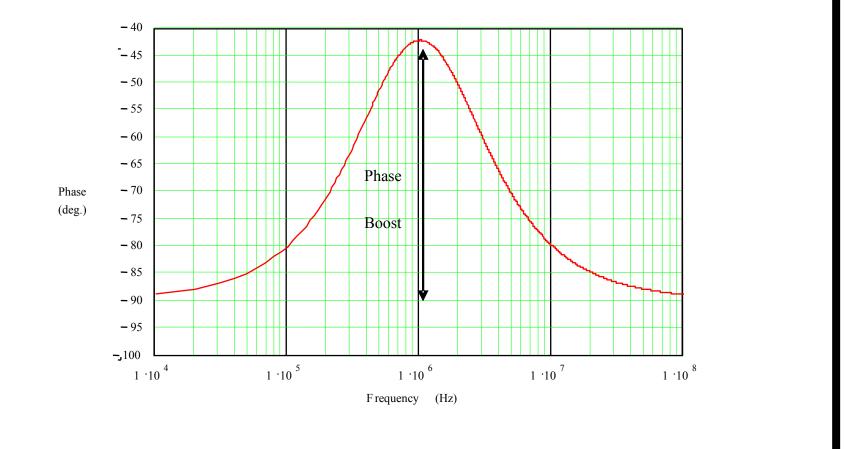

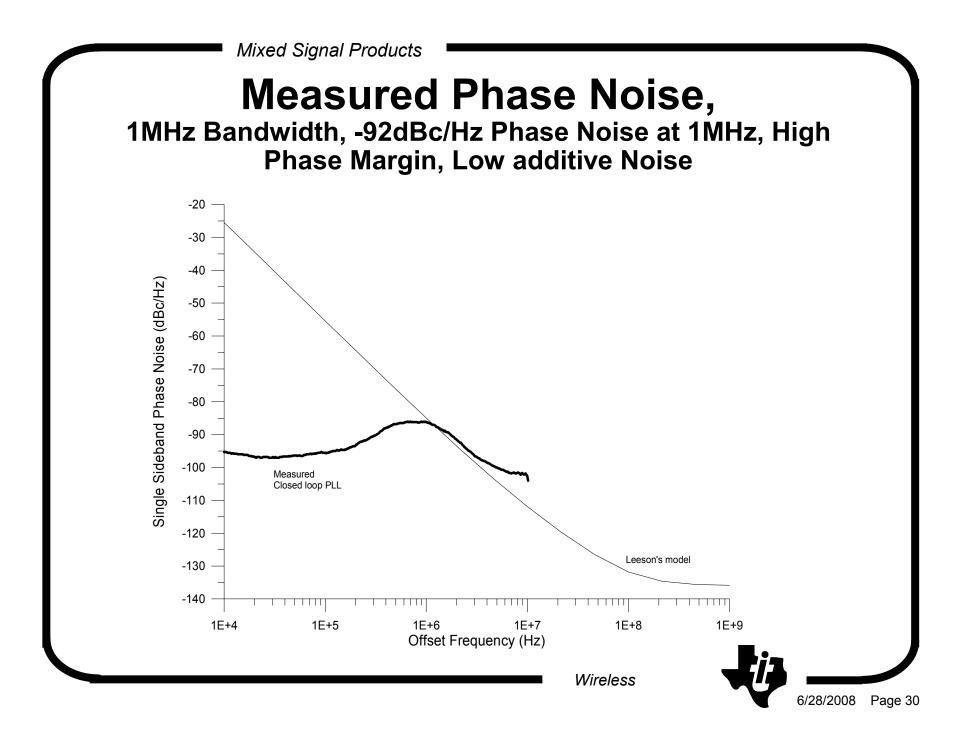

## Open loop phase response with type 2 and 2 zero compensation.

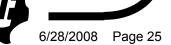

## Open loop magnitude response with type 2 and 2 zero compensation

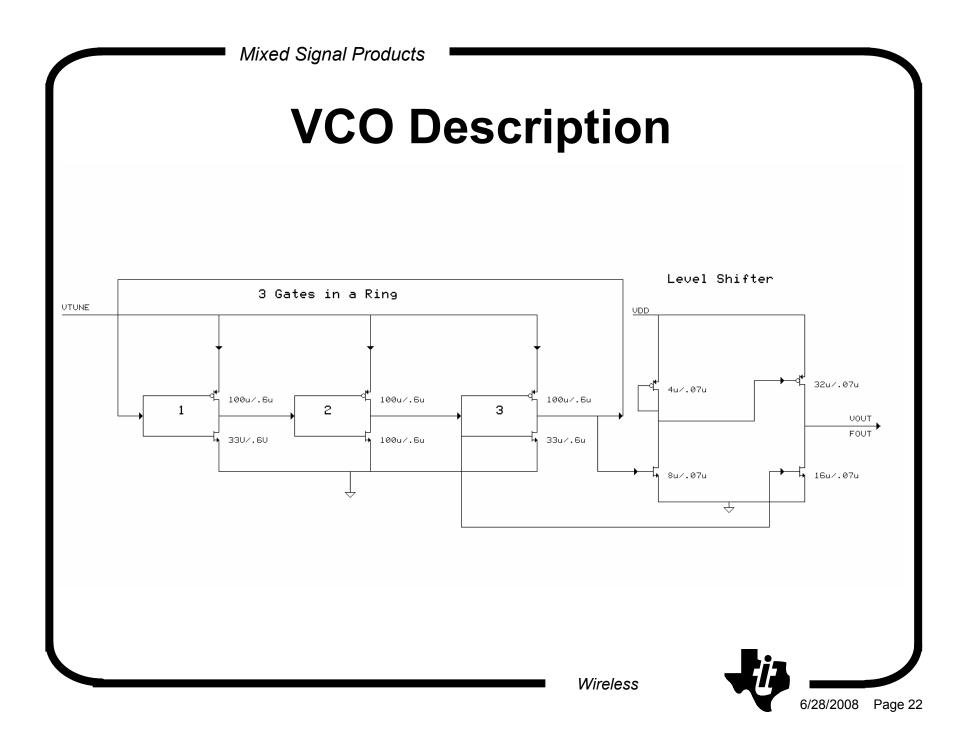

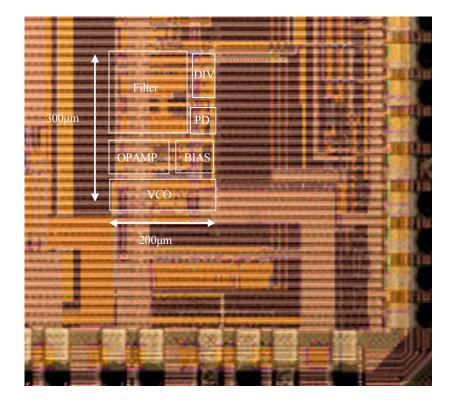

# C021 Die photo of the PLL circuit, 300x200um=0.06mm<sup>2</sup>

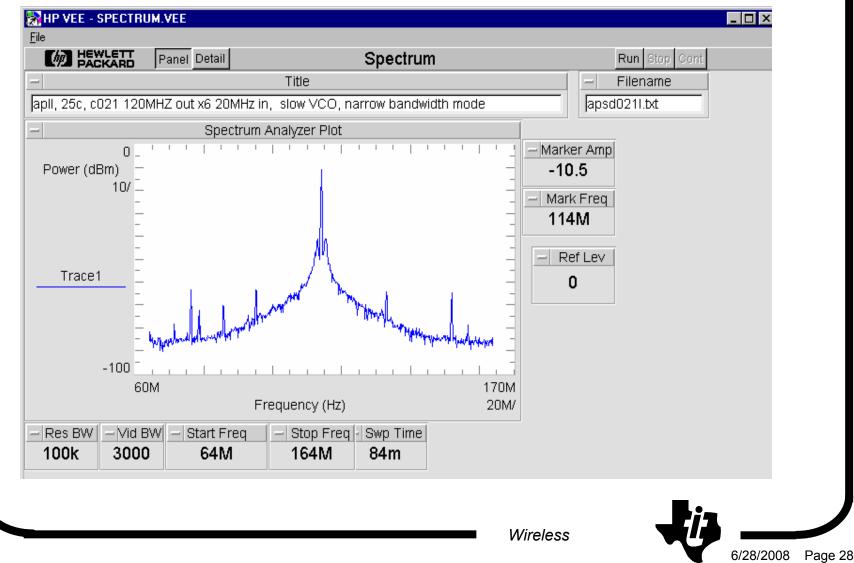

#### Mixed Signal Products Measured Data Spectrum, Reference Sidebands <-60dBc

### **Measured Data Jitter <80ps peak to peak**

| Tek      | Run              | San          | nple                                    |      | 9647 Acqs        |                            | Mea <u>s</u> ure |                       | Jun 05 16 | :38:59   |       |                  |                  |  |

|----------|------------------|--------------|-----------------------------------------|------|------------------|----------------------------|------------------|-----------------------|-----------|----------|-------|------------------|------------------|--|

| -        |                  | 1            |                                         |      |                  |                            | 11/1/1           |                       | 1         |          | · · - |                  | Buttons          |  |

|          |                  | 1            |                                         | 1    | 1                |                            |                  |                       |           |          |       | ch1 P            | osition          |  |

|          |                  | •            |                                         |      |                  |                            | <b>/</b>         |                       | •         |          |       |                  | 6div             |  |

| -        |                  |              |                                         |      |                  |                            |                  |                       |           |          |       | -1.1             | ourv             |  |

|          |                  |              |                                         |      |                  |                            | <b>-</b> 1       |                       |           |          | -     | Ch1              | Scale            |  |

|          |                  | ·<br>· · · · |                                         |      | •<br>• • • • • • | . <b>. </b> <mark>.</mark> | <mark></mark>    |                       | •         |          |       | 2.0              |                  |  |

|          |                  |              |                                         | 1    |                  | - ‡ 🥖                      |                  |                       |           | 1        |       |                  |                  |  |

| Ŀ        |                  | :            | :                                       | -    |                  | - ± 🖊                      |                  |                       | :         | 1        | и: 7  | k(Hs)<br>5.9995; | 76.0ps<br>72p    |  |

|          |                  |              |                                         |      |                  | · <b>+//</b> ·             |                  |                       |           |          | m: 8  | .0p              | M: 112.0p        |  |

| F        |                  |              |                                         |      |                  | - ‡/                       |                  |                       |           |          | _σ: 4 | 1.92f            | n: 766.0         |  |

|          |                  |              |                                         |      |                  |                            |                  |                       |           |          | Std I | Dev(Hs)          | 13.04ps          |  |

|          | $\left  \right $ | ++++         | + + + + + + + + + + + + + + + + + + + + | ++++ | ++++++           | -+ <mark>//</mark> +++     | + + + + + +      | +++++                 | ++++      | +++++    | µ: 1  | 3.0368           | 07p<br>M: 28.29p |  |

| -        |                  |              |                                         |      |                  |                            |                  |                       |           |          |       | .o<br>51.1a      | n: 12.01k        |  |

|          |                  |              |                                         |      |                  | <u> </u>                   |                  |                       |           |          | -     |                  |                  |  |

| 1+       |                  |              |                                         |      | · · : · · /      | / ‡ · · ·                  |                  |                       |           |          | ·     |                  |                  |  |

|          |                  |              |                                         | 1    | - : /            | ±                          |                  |                       |           | 1        |       |                  |                  |  |

| -        |                  |              |                                         |      | : . 🖊 .          | . <u>+</u>                 |                  |                       | •         |          |       |                  |                  |  |

| -        |                  |              |                                         |      | <mark>-</mark>   | +                          |                  |                       |           |          | -     |                  |                  |  |

|          |                  |              |                                         |      | <mark>-</mark>   | Ŧ                          |                  |                       |           |          | -     |                  |                  |  |

|          |                  |              |                                         |      | 📶                |                            |                  |                       |           |          |       |                  |                  |  |

|          |                  |              |                                         | 1    | <b>_</b>         | +                          |                  |                       |           |          | 1     |                  |                  |  |

|          |                  | 1            | :                                       | 1    | <u>/</u> :       | ±                          |                  |                       | :         |          | _     |                  |                  |  |

|          |                  | 2.0mU        |                                         |      |                  |                            | M 200            |                       | IT 6 0m - |          |       |                  |                  |  |

| Cł       | 11 7             | 2.0m¥        | 52                                      |      |                  |                            | A Ch1            | s 5.0GS/s<br>7 4.72mY | 11 4.0ps  | /pt 0.0s |       |                  |                  |  |

| <u> </u> |                  |              |                                         |      |                  |                            |                  |                       |           |          |       |                  |                  |  |

|          |                  |              |                                         |      |                  |                            |                  |                       |           |          |       |                  | 11               |  |

|          |                  |              |                                         |      |                  |                            |                  | ∎ W                   | ïreless   |          |       |                  |                  |  |

## Comparison Table of Measured Data with Comparable PLL References

|                            |                | i                   | i             | i                                | i                     | i                                             | ·                                                   |

|----------------------------|----------------|---------------------|---------------|----------------------------------|-----------------------|-----------------------------------------------|-----------------------------------------------------|

| Description                | Processes      | Power               | Area<br>(mm²) | VCO Output<br>Frequency<br>(MHz) | Jitter                | power supply<br>sensitivity, %-<br>fvco/%-Vdd | Comments                                            |

| S. Sidropoulos<br>VLSI '00 | .35um 3.3V     | 21.5mW@500MHz       | 0.047         | 30-650                           |                       | .06%/1%                                       | Simulated, Supply<br>Controled Ring<br>VCO, wide BW |

| J.M. Ingino<br>ISSCC '01   | .15um 3.3V     | 132mW@4GHz          | 1.48          | 600- <mark>4000</mark>           | 44ps p-p at<br>700MHz | .007%/1%                                      | Regulator<br>included, single<br>ended ring CCO     |

| H. Ahn JSSC<br>'00         | .25um 1.9V     | 25mW@320MHz         | 0.087         | 17-1320                          |                       | .32%/1%                                       | Supply Controled<br>Ring VCO, wide<br>BW, 2.5MHZ BW |

| K. Minami<br>CICC '01      | .1um 1.2V      | 30mW at 2000MHz     | 0.15          | 500-2350                         | 21ps p-p              |                                               | Single ended ring<br>CCO                            |

| Maneatis<br>ISSCC '03      | .13um 1.5V     | 7mW at 240MHz       | 0.18          | 30-650                           | 48ps p-p              |                                               | Differential ring VCO, self biased                  |

| Hozer ISSCC<br>'02         | .13um 1.5V     | 7mW at 200MHz       | 0.16          | 10-350                           | 155ps p-p<br>360MHz   |                                               | Differential ring<br>VCO, VCR                       |

| Fahim TCAS<br>'03          | .25um 1.9V     | 3.12mW at<br>160MHz |               | 30-160                           | 130ps p-p             |                                               | All Digital PLL, diff.<br>ring VCO                  |

| This work<br>APLL          | .065um<br>1.2V | 1mW at 240MHz       | 0.06          | 12-600                           | 80ps p-p              | .02%/1%                                       |                                                     |

### References,

- 1. Stanley Goldman, *Phase Locked Loop Engineering Handbook,* Artech House, Boston, 2007.

- 2. Roland Best, *Phase Locked Loops Design Simulation, & Applications,* McGraw Hill, New York, 1997.

- 3. Behzad Razavi, *Monolithic Phase-Locked Loops* and Clock Recovery Circuits, IEEE Press, New York 1996.

- 4. William Egan, *Frequency Synthesis by Phase-Lock*, Wiley Interscience, New York, 1981.

- 5. Floyd Martin Gardner, *Phaselock Techniques*, Wiley Interscience, New York, 1979.

## **Key Points**

- Voltage Regulator can be incorporated into loop compensation (Dual Use)

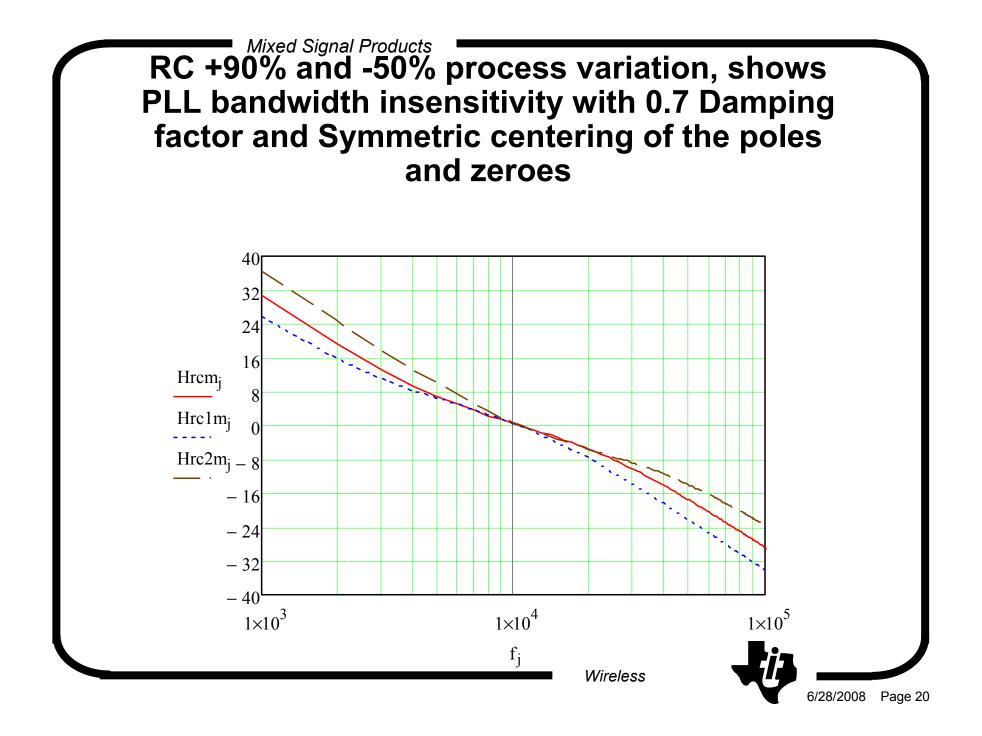

- Geometrically Centered Zeroes and Poles Reduces sensitivity to R C process variations

- Increasing Resistance can be used to reduce capacitor size and overall loop size.

- Wider loop bandwidths can be achieved with 2 zeros because of the increase in phase margin.

- Widest loops give lowest phase noise for references with lower noise than the VCO

- Further future improvements can be made to reduce power, size, and area.

- Active Compensation gives flexibility in compensation