# leti Ceatech

## ADVANCED PACKAGING FOR SILICON PHOTONICS BASED MODULES AND APPLICATIONS

EPS Webinar| Stéphane Bernabé | 25.06.19

- Silicon Photonics

- Promises

- Challenges

- What can advanced packaging bring to PIC modules ?

- Some work in progress

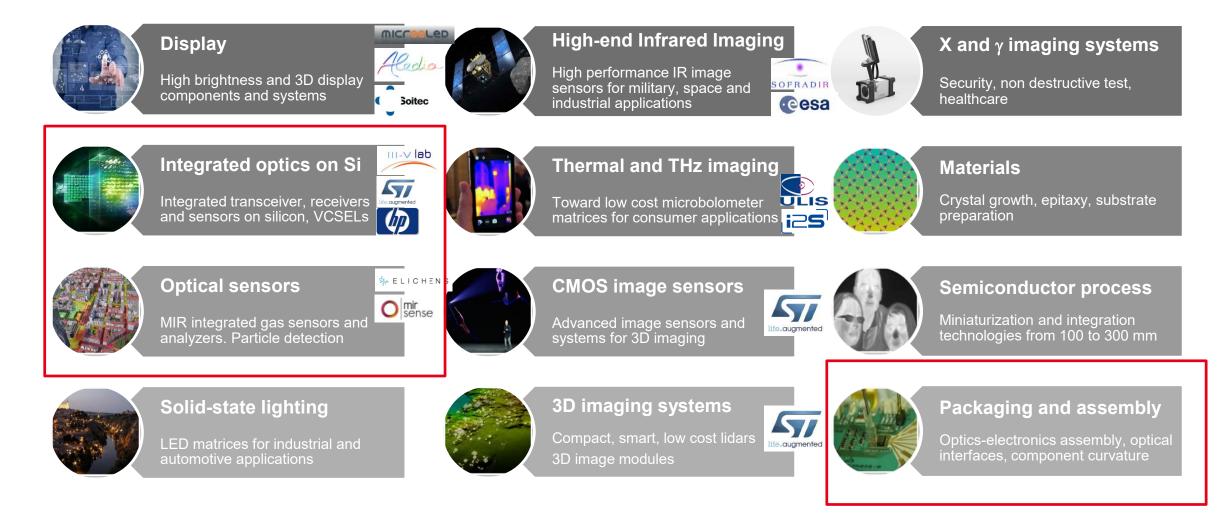

**Bio: Stéphane Bernabé** is the head of the Photonic Packaging Lab at CEA-LETI, Grenoble, France. His field of expertise is in Photonic Integrated Circuit packaging, Module integration (VCSEL and PIC), and Electronic/Photonic convergence for advanced applications of PICs. He previously led several R&D projects dealing with these topics and is currently involved in the EU-funded projects MASSTART, PIXAPP, and TINKER. He has also overseen module and packaging developments in companies Radiall and Intexys Photonics. He's a member of the Electronics Packaging Society (IEEE-EPS) and acts as committee member in the ESTC and ECTC conferences. He has co-authored 50 papers, 3 book chapters and holds 15 patents in the field of photonics packaging.

## **CEA-LETI AT A GLANCE**

**"3rd Innovative Public Research Organization** Worldwide" 2012 - 2020

Patents:

- > 3,000 in portfolio

- 40% under license agreement

#### Startups:

- 68 created for 20 years (75% in activity)

- 3500 jobs created

#### **Cleanrooms:**

- Æ 500 state-of-the-art equipment in 200 & 300 m<sup>2</sup>

- 10 000 square meters cleanroom **Budget:**

- 315 M€

- 85% from R&D contracts

Founded in 1967, based in France (Grenoble) with offices in USA and Japan

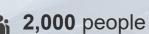

## **OPTICS & PHOTONICS DIVISION**

- 12600 m<sup>2</sup> incl. offices, labs and clean rooms

- Dedicated clean rooms for III-V and II-VI materials (growth, epitaxy, process and packaging) on versatile substrate geometries up to 150 mm

- Electro-optical test and characterization facilities

- Design and simulation capabilities for process, growth, optics

400 people

#### Patents:

- 80 per year

- > 700 in portfolio

- 40 % under license agreement

#### **Budget:**

- 70 M€

- 90% from R&D contracts

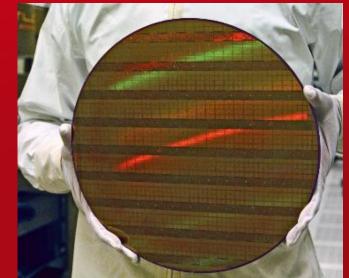

### CEA-LETI 8,500 m<sup>2</sup> CLEAN ROOMS for 200mm & 300mm wafers

## LETI PHOTONICS DIVISION

leti

Ceatech

Our mission : innovate by miniaturizing and integrating optical components for our industrial partners

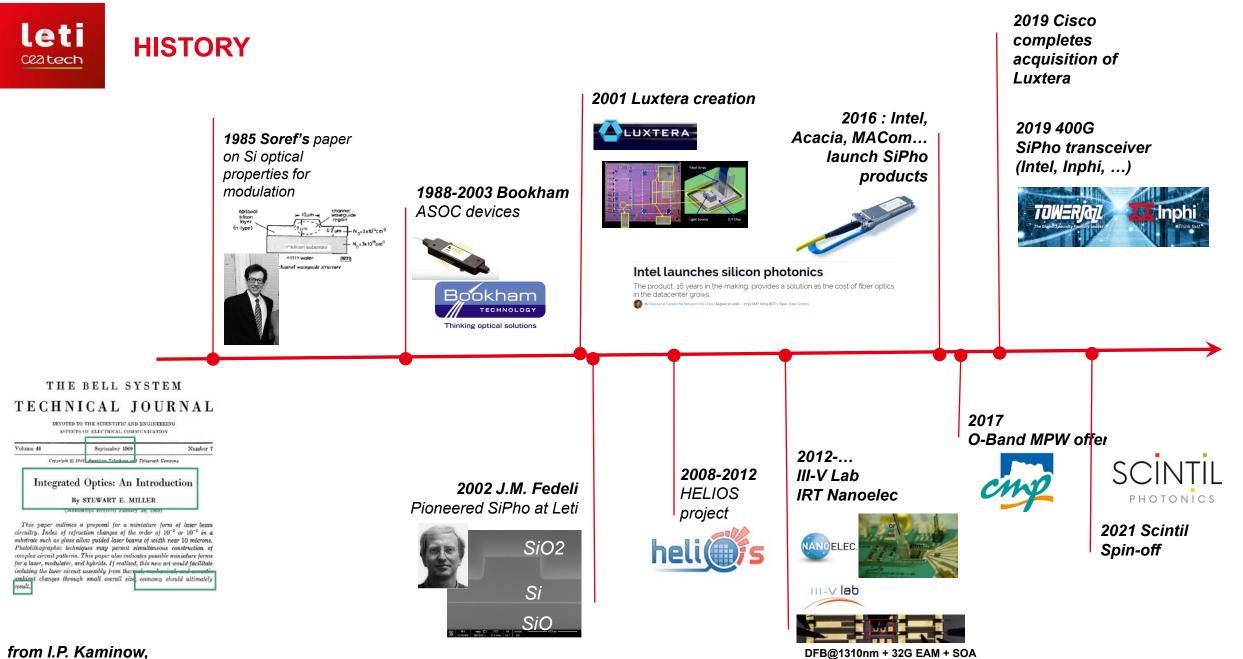

A SHORT HISTORY OF INTEGRATED OPTICS PACKAGING

## BASED ON MY OWN EXPERIENCE ON ALIGNING, GLUING AND TESTING FIBERS TO PICS

## EARLY STUDIES ON INTEGRATED OPTICS PACKAGING (70'S)

#### End fire coupling between optical fibers and diffused channel waveguides

W. K. Burns and G. B. Hocker

W. K. Burns is with U.S. Naval Research Laboratory, Washington, D. C. 20375; G. B. Hocker is with Honeywell Corporate Research Center, Bloomington, Minnesota 55420. Received 24 February 1977.

Single-mode optical-waveguide fiber coupler

Juichi Noda, Osamu Mikami, Makoto Minakata, and Masaharu Fukuma

A single-mode fiber coupler to the Ti diffused LiNbO<sub>2</sub> strip waveguide has been devised. The influences of three axial displacements and two angular misalignments on the coupling efficiency have been investigated at 6228-Å wavelength. The coupler has a special feature wherein coupling degradation caused by fiber displacement after connection can be recovered to the initial state. The total optical insertion loss is 3 dB after fixing the fiber to the LiNbO<sub>2</sub> strip waveguide, which is 4 µm wide and 8 mm long.

Fig. 1. Connecting equipment.

Fig. 2. Structure of the connection jig. This view shows the state after fixing the fiber to the waveguide—1: strip waveguide; 2: fiber; 3: stainless steel pipe; 4: sleeve; 5: flange; 6: set screws; 7: adhesive paste; 8: molder; 9: square block; 10: case.

A waveguide to single-mode fiber coupler has been devised, and its coupling characteristics have been investigated experimentally. This method can provide highly accurate optical alignment between a fiber and a waveguide and is applicable for connecting a laser source or a detector to a fiber. The coupler has a special feature wherein degradation in coupling, yielded by fiber displacement after the connection, can be reset to the initial state. Present coupling loss is large because of insufficient optical field overlap between the fiber and the waveguide. Therefore, further technical improvement to fabricate the waveguide with the optical field close to that of the fiber is necessary for coupling loss reduction. Especially, Li<sub>2</sub>O out-diffusion is one of the difficult problems which must be overcome in fabricating a narrow strip waveguide. More detailed investigation on coupling efficiency degradation due to aging effect or temperature variation will be made.

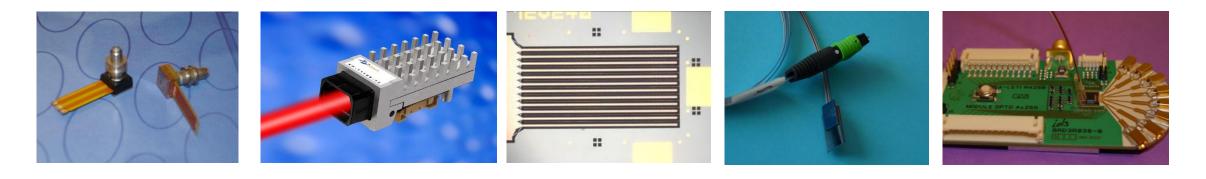

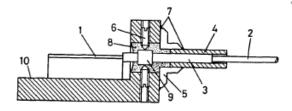

## **2K YEARS : PIGTAILING IS BECOMING MATURE**

#### Boom of optical devices

#### Several PIC technologies :

Glass Silica On Silicon Lithium Niobate (for modulators) ASOC from Bookham (thick SOI)

Glass optical 1x8 splitter, from Teem Photonics

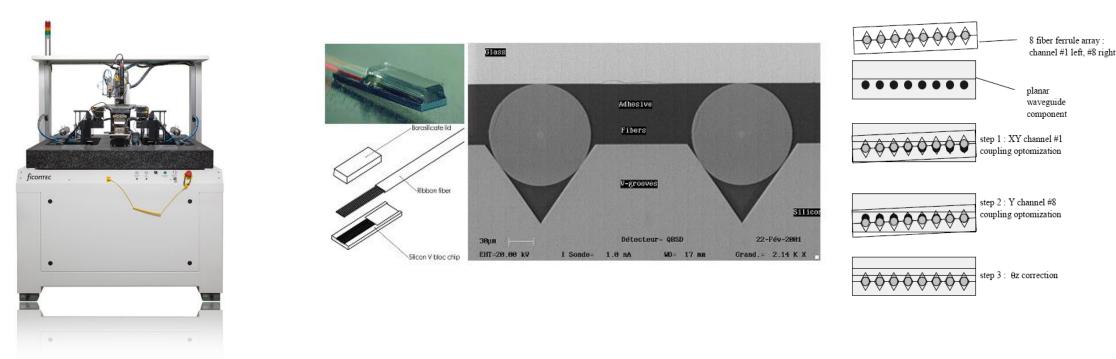

# LetiWHAT A PACKAGING ENGINEER SHOULD KNOW ABOUT (SINGLEMODE)CEALECHPHOTONICS

# LetiWHAT A PACKAGING ENGINEER SHOULD KNOW ABOUT (SINGLEMODE)CERTECHPHOTONICS (2)

PIC packager Golden rule The offset/tilt trade-off З. Axial vs Angular Tolerance (µm) 120 Lateral Tolerance (µm) 100 80 (mu) C **→** Δz **Feta** 60 3 Δθ Ν 40 20 0 0 8 0  $\mathbf{2}$ 6 10 2 3 5 6 8 1 MED (µm) waist laser (µm)  $\Delta \theta = 60 \frac{\lambda}{\pi^2} \sqrt{\frac{1}{2}}$  $\left|\frac{1}{\omega^2} + \frac{1}{\omega_f^2}\right|$  $\Delta x = 0.33 \sqrt{\left(\omega^2 + \omega_f^2\right)}$

lan R. Mickelson Ulrich H.P. Fischer-Hirchert Photonic Packaging Sourcebook Fiber-Chip Coupling for **Optical Components**

🕤 Springer

sic Calculations Module

## SILICON PHOTONICS : PLATFORM & ROADMAP

J. LT, 26,9,2008

## leti ceatech

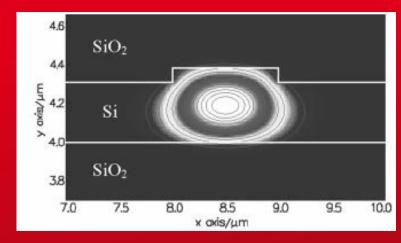

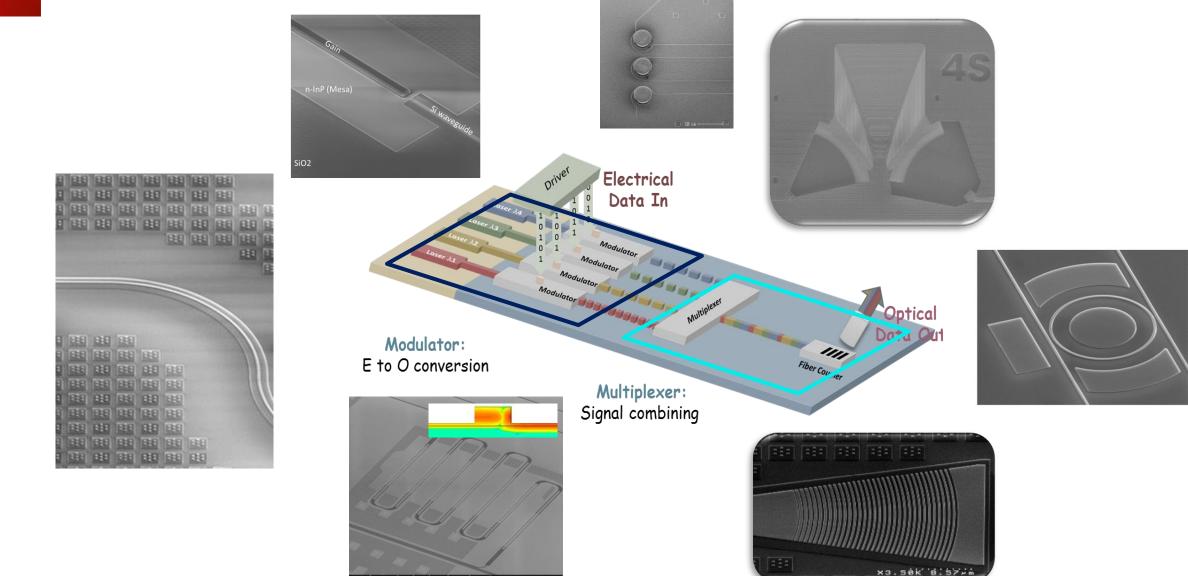

## SILICON PHOTONICS PLATFORM

Mag 02/24/16 Spot FWD Tilt E-Beam Det 350 X 11:53:44 4 4 738 52.0° 15.0 kV CDM-F

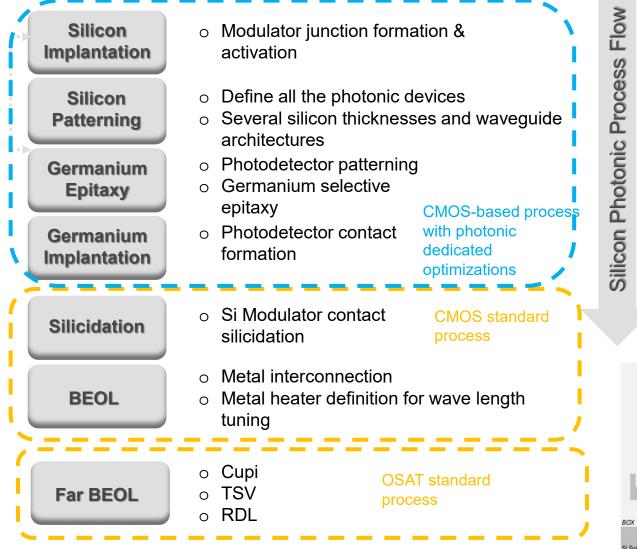

## SILICON PHOTONICS : TECHNOLOGY OVERVIEW

| Silicon           |   |

|-------------------|---|

| BOX               |   |

| 507               | l |

| Silicon Substrate |   |

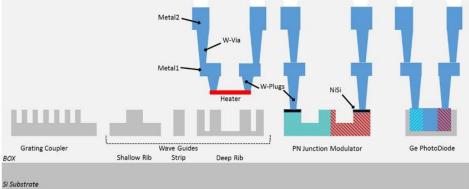

Silicon On Insulator (SOI) substrate :  $\emptyset 8$ " or  $\emptyset 12$ "

Schematic cross section of a silicon photonic circuit (Leti)

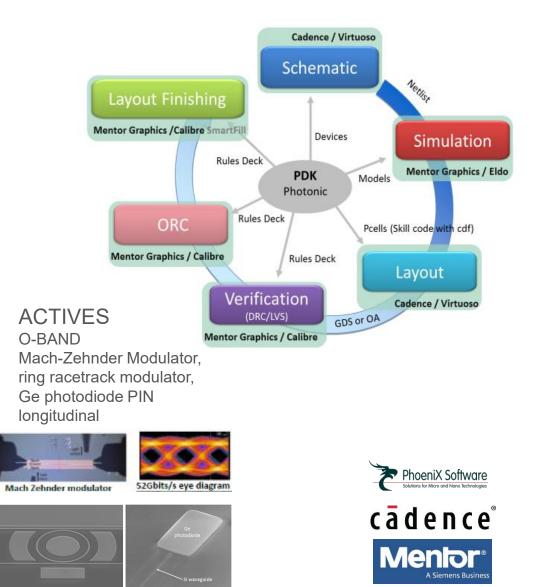

## **DEVICE LIBRARY AND PROCESS DESIGN KIT AVAILABLE**

Ŵ

PASSIVES O-BAND & C-BAND Rib, deep rib, strip, rib MM, bend strip, bend rib, bend deep rib, fiber grating coupler 1/2D, directional coupler, transitions, ring filter, MMI...

## SILICON PHOTONICS PLATFORM

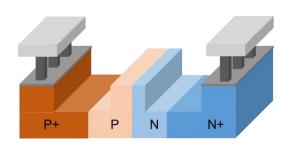

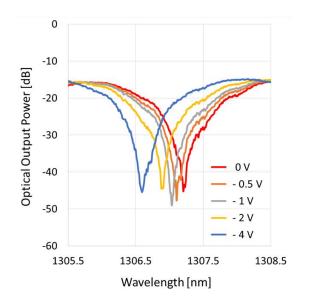

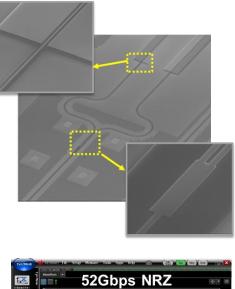

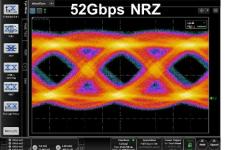

Carrier depletion in PN/PiN diode (reverse bias) for High Speed Modulation Section

Szelag B, et al. Optimization of 64Gbps O-band thin-rib PN junction. Mach- Zehnder Modulator fabricated on a 200mm silicon photonics platform. SSDM 2018.

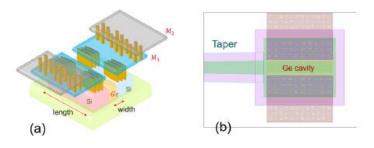

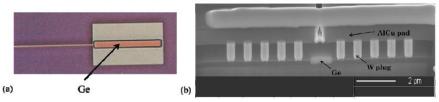

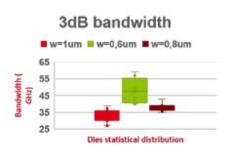

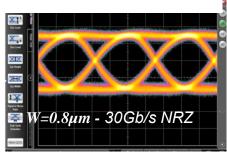

#### Ge epitaxy in cavity for High Speed Ge PIN Photodiodes

Figure 3. (a): Si/Ge/Si photodiode stack-up layers view. (b) Photo-diode planar view

Fig. 3. (a) Top-view of a fabricated 1  $\mu m$  wide Ge cavity after CMP. (b) Cross-sectional SEM image of a 1  $\mu m$  wide Ge cavity photodiode.

H. Zegmout *et al.*, « High speed integrated waveguide lateral Si/Ge/Si photodiodes with optimized transit time », 2020, vol. 11285. EPS Workshop| Stéphane Bernabé | 21.10.21| 17

## leti <sup>Ceatech</sup>

## **COUPLING STRUCTURES**

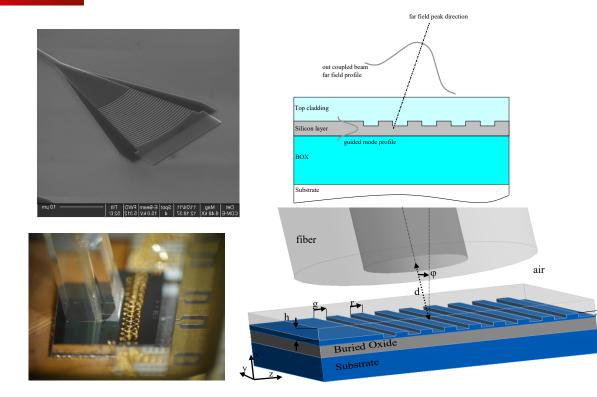

#### Vertical Grating coupler

- 50% to 80% efficiency for 1 polarization

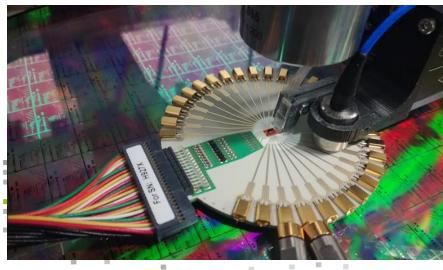

- Ideal for waferscale testing

- Limited bandwidth

- Alignment tolerance: +/- 2 µm (well fitting mode size)

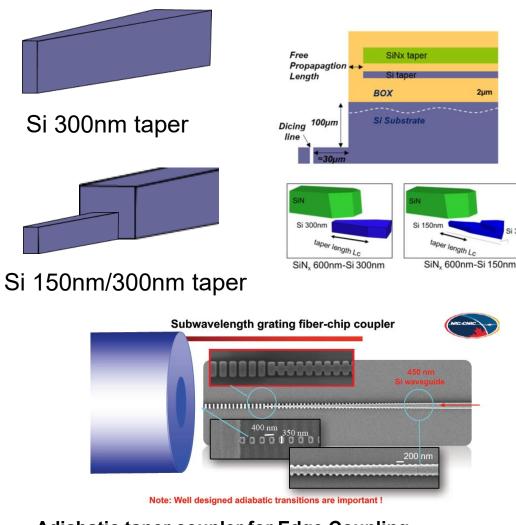

#### Adiabatic taper coupler for Edge Coupling

- Broadband

- Small mode size (3µm diameter)

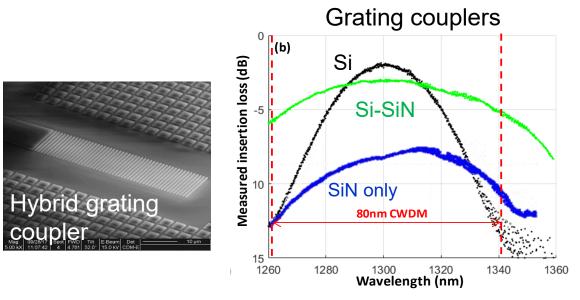

### Leti CALLECH ADVANCED COUPLING STRUCTURES

## SiN-Si hybrid grating coupler

- 2-layers grating SiN-Si

- 2.8 dB insertion loss

- -1dB BW ~ 50nm

$\rightarrow$  CWDM components wafer level testing (broadband)

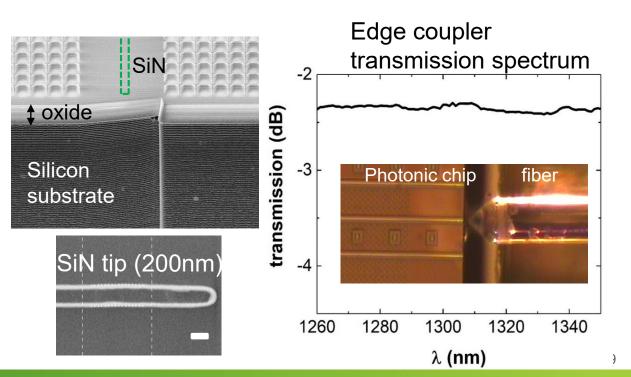

## Edge coupler with SiN taper

- Lensed fiber : MFD = 2.5µm

- SiN inverse taper

- Deep trench by dry etching

- Coupler insertion loss : < 2.4dB (O-band)</li>

- For CWDM modules

Q. Wilmart et al., Appl. Sci. (2019)

# leti

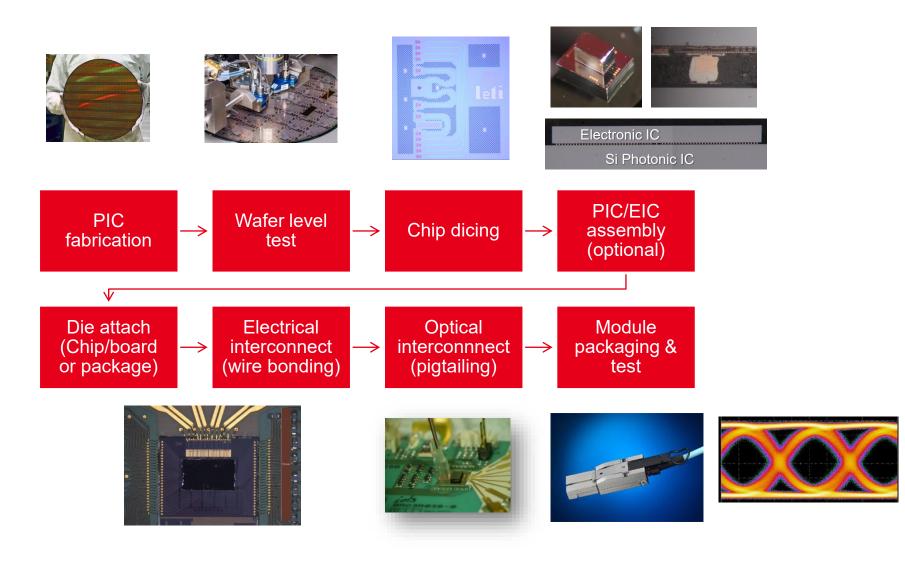

## SILICON PHOTONICS MODULE ASSEMBLY FLOW

# **SILICON PHOTONICS : ADVANTAGES**

- Small devices thanks to high index contrast between Silicon and oxide

- Integrated photonic device onto silicon, manufactured in a CMOS fab, enables low cost mass production

- Scalability to increase bit rate per channel : wavelength multiplexing, advanced modulation format

- Low-latency : architecture with unified switched photonic network

- High speed end-to-end network paths

- Wafer scale testing

leti

Ceatech

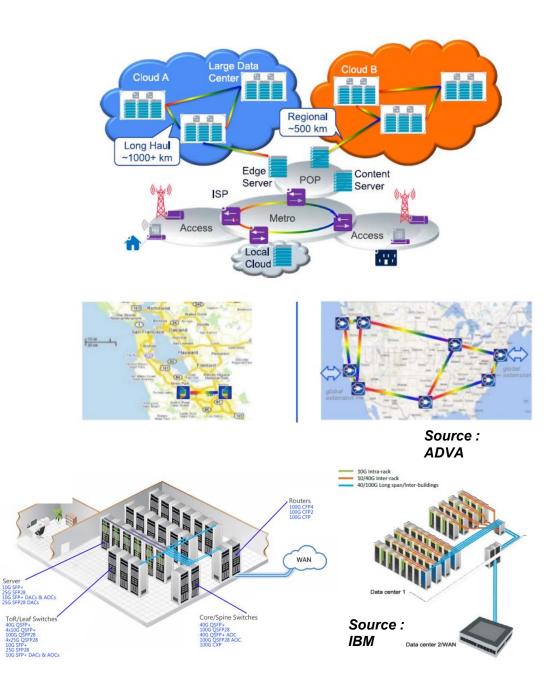

Solving electrical interconnect limits in Data centers, Supercomputers and ICs with higher capacity, lower cost optical interconnects

**Intel Transceiver**

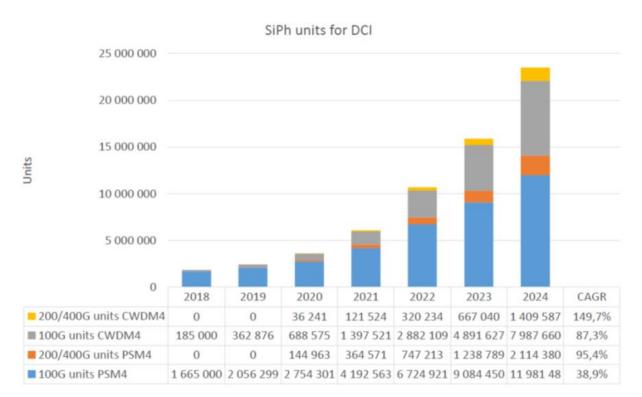

## **ROADMAP / MARKET TRENDS**

Source: Yole

leti

Ceatech

- 400G is widepreading

- Increasing size of DCs

- <1\$ / Gbps required

- Ethernet transceiver market Is expecting to reach 43Munits by 2025

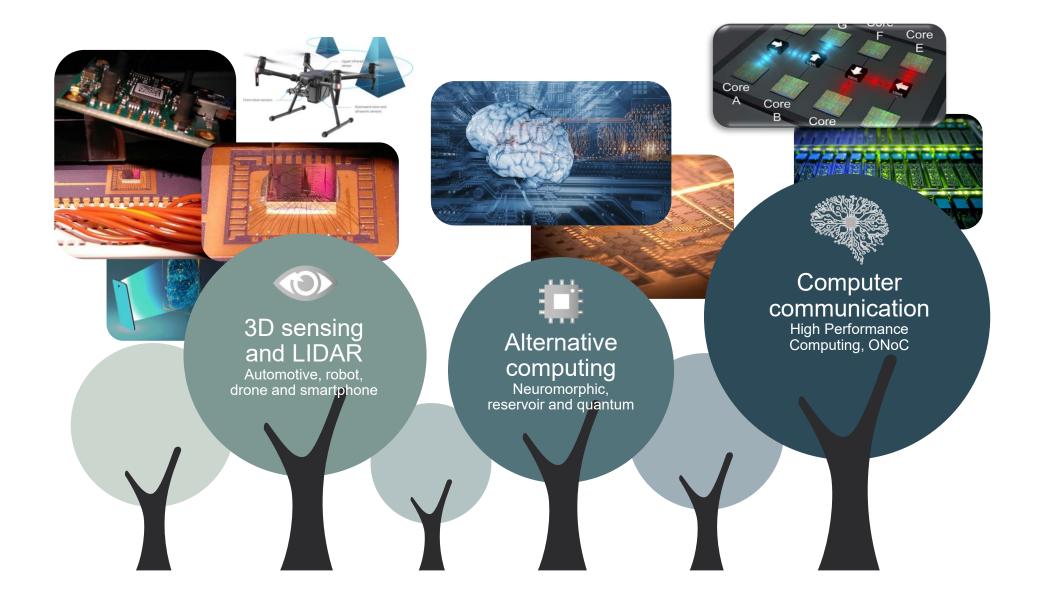

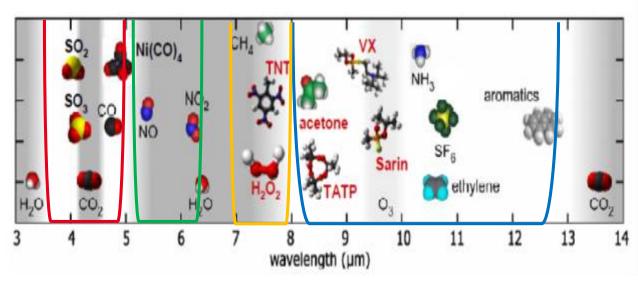

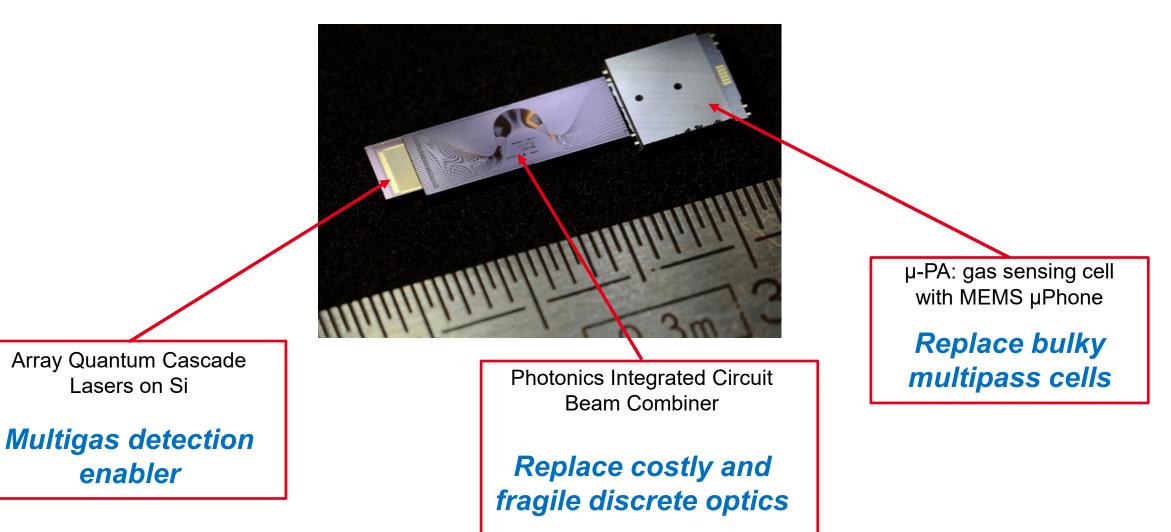

## **APPLICATIONS BEYOND TELECOM & DATACOM**

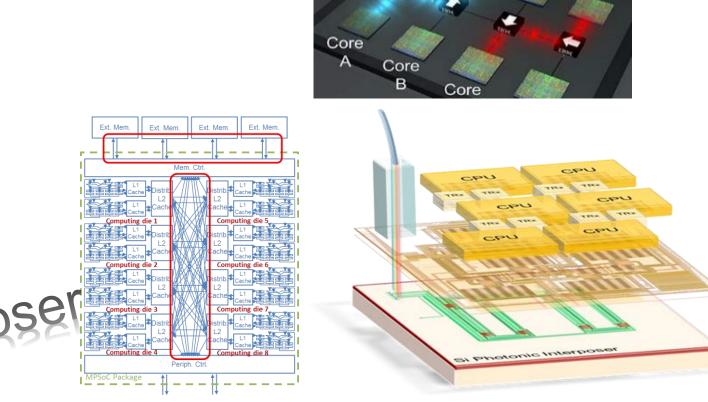

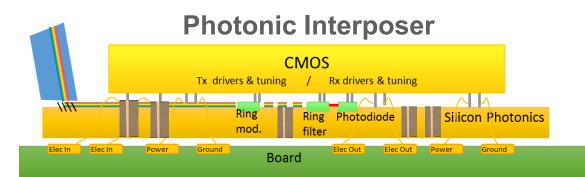

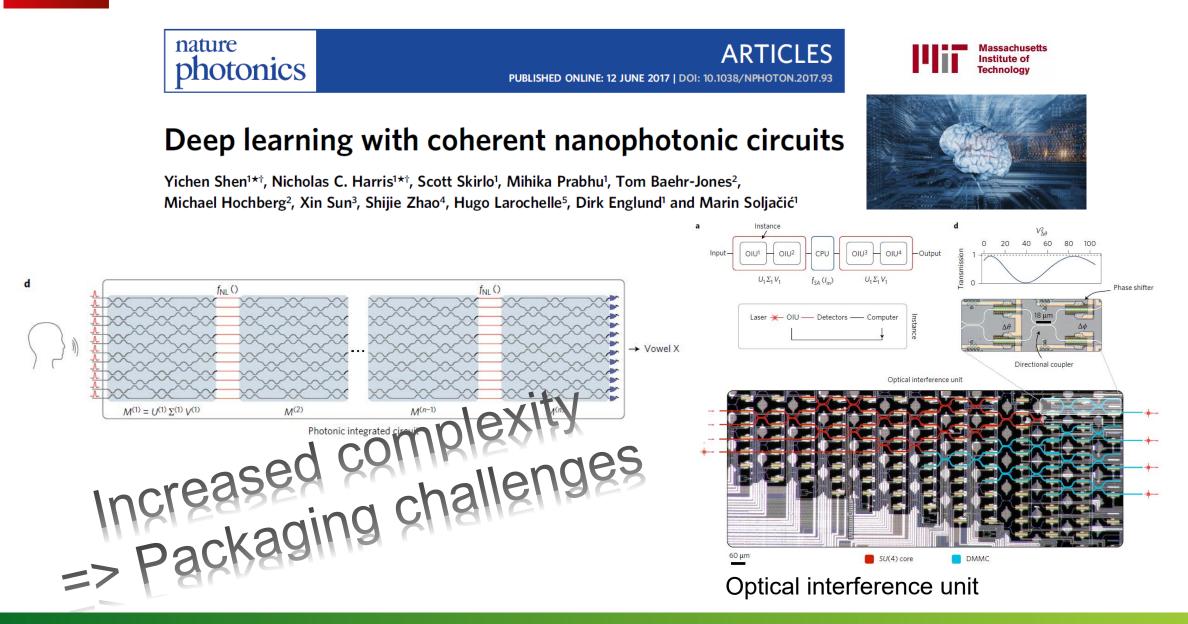

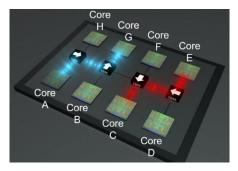

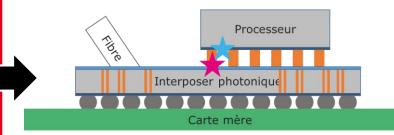

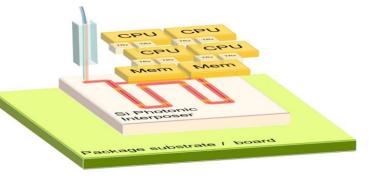

# **OPTICAL NETWORK ON CHIP**

### **Photonic assisted processor**

- Multi-cores bottlenecks

- Chiplet approach

- Manycore architectures

- Known Good Die sorting Photonic Interpose

with increasing maturity of silicon photonic platforms and compatibility with face-to-face die hybridization, it is now possible to consider the implementation **of optical network-on-chip (ONoC) topologies** on silicon photonic interposers to go beyond the scalability limitations of active CMOS interposers.

Y. Thonnart, ISSCC 2018

Core

d

## **NEUROMORPHIC COMPUTING**

## leti ceatech

## **OPTICAL PHASED ARRAY LIDARS**

Optical Beam steering for automotives

30

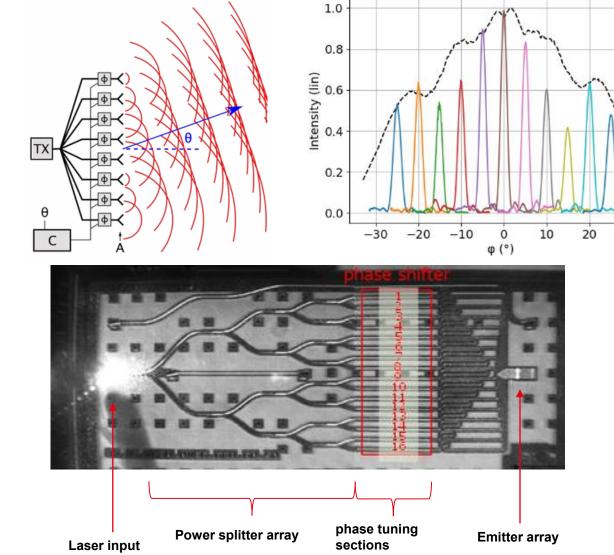

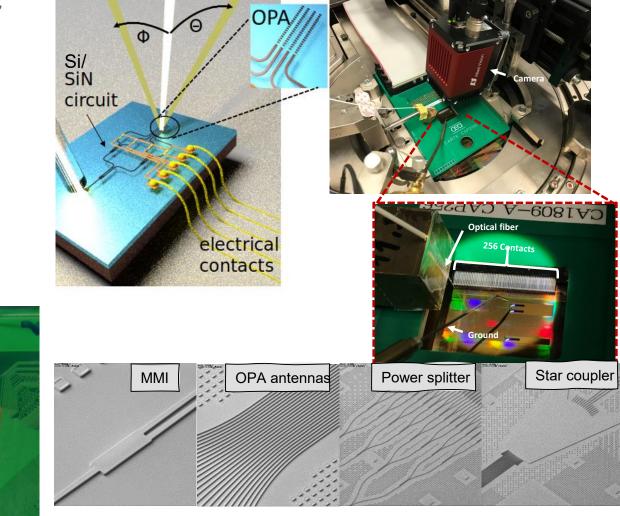

## **OPTICAL PHASED ARRAY LIDARS**

- Development of Optical Phased Arrays for LIDAR systems and other applications

- Application specific design of photonic components for 500-1000nm (SiN) or 1250-1600nm (Si or SiN).

- Relies on thermo optic effect applied to waveguides

- Co-design of photonic circuit and ASIC for hybrid integration of driver electronics.

- Packaging of demonstrators

Packaging challenges

N. A. Tyler *et al.*, "SiN integrated optical phased arrays for two-dimensional beam steering at a single near-infrared wavelength," *Optics Express*, 2019 S. Guerber *et al.*, "Development, calibration and characterization of silicon photonics based optical phased arrays," *Smart Photonic and Optoelectronic Integrated Circuits XXIII* 2021.

Coupe X

100 000

Coupe Y

-6.00 -5.00 -4.00 -3.00 -2.00 -1.00 0.00 1.00 2.00 3.00 4.00 5.00 6.00

1.0-

0.8-

0.6-0.4-0.2-

0.0-

1.0-

0.8-

0.6-

0.4-

0.2-

-7.00 -6.00 -5.00

.

4.00 5.00 6.00 7.00

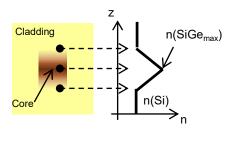

- Single Mode waveguide:

- Core: Ge (section: 2.5 x 2.5 μm<sup>2</sup>)

- Cladding: SiGe

#### Characteristics FEM simulations:

- TM mode @ 8.7 μm

- Mode size at (1% of max intensity) = 5.4 µm horizontal, 5.6 µm vertical

- Minimum cladding of 6 µm SiGe around the Ge core

LI O WOINSHOP ОТЕрнане Бегнаде́ | 21.10.21 | 28

## Challenge: Combine source optics and detection on the same chip

## **INTEGRATION CHALLENGES**

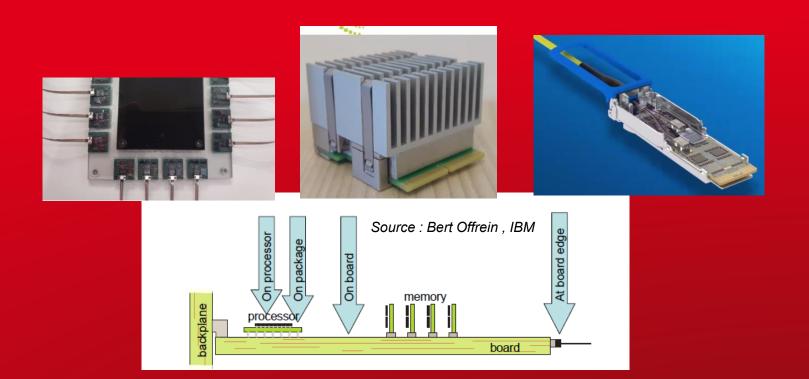

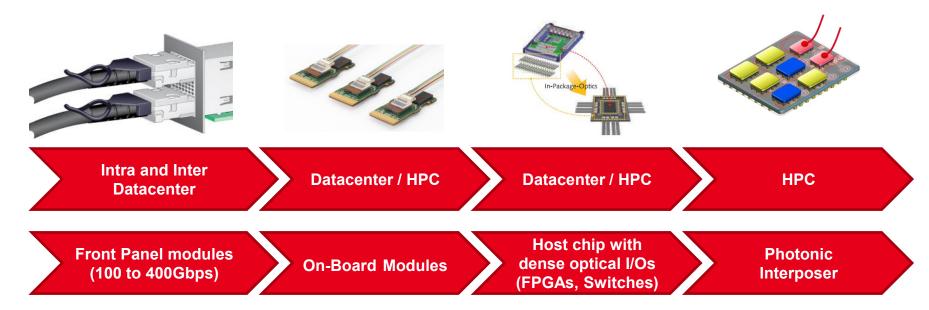

## **ROADMAP : FROM RACK INTERCONNECTS TO NETWORK ON CHIPS**

leti

Ceatech

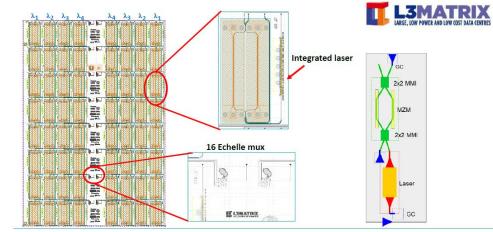

#### Review

Silicon photonics for terabit/s communication in data centers and exascale computers

S. Bernabé <sup>a</sup>, Q. Wilmart <sup>a</sup>, K. Hasharoni <sup>b</sup>, K. Hassan <sup>a, e</sup>, Y. Thonnart <sup>a</sup>, P. Tissier <sup>d</sup>, Y. Désières <sup>a</sup>, S. Olivier <sup>a</sup>, T. Tekin <sup>c</sup>, B. Szelag <sup>a</sup>

- <sup>a</sup> Univ. Grenoble Alpes, CEA LETI, Minatec Campus, F38054 Grenoble, France

- <sup>b</sup> DustPhotonics, 11 Tzela Hahar, Modiin, Israel <sup>c</sup> Fraunhofer IZM, Gustav-Meyer-Allee 25, 13355 Berlin, Germany

- <sup>d</sup> ST Microelectronics, Crolles, France

\* III-V Lab, Joint Lab of Nokia, Thales & CEA, 1 A. Fresnel, 91767 Palaiseau, France

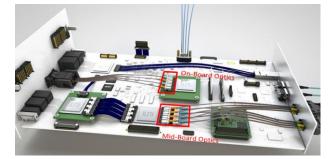

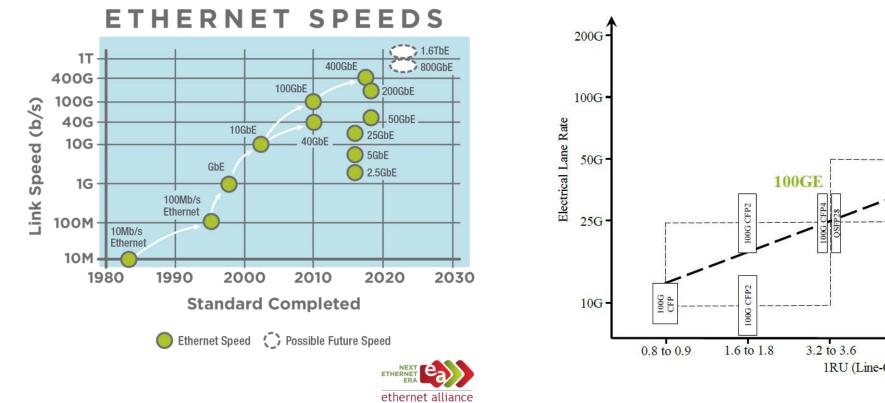

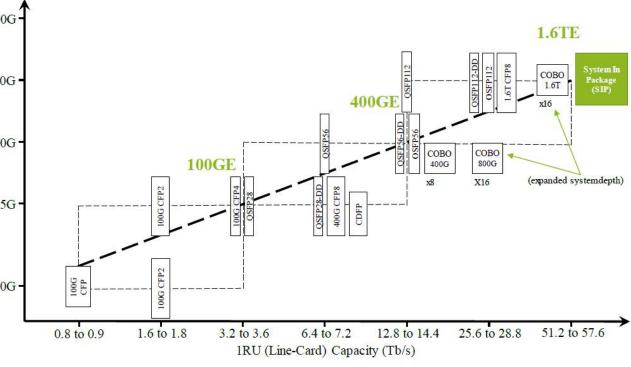

- 100G proliferating

- 400G ramping up

- Next stop, 800G and 1.6T

- Road >400G includes COBO and co-packaging

- Enable 2D use of the board (no more front panel limitation)

- >100Gpbs data rate

- Can be used for intra-rack or intra-board applications

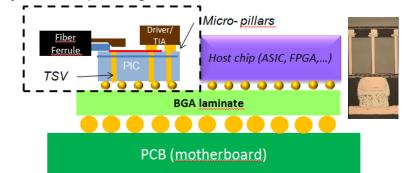

- Optical modules integrated on PCB or on BGA package, near the host chip (processors or FPGA)

- RF lines are shorter and the whole motherboard surface can be used to provide host chips with E/O transceivers

- Already available with VCSEL embedded (e.g. Avago, TE...)

• **COBO** Initiative defining the RF interface

EPS Workshop| Stéphane Bernabé | 21.10.21 | 33

Тусо, 2012

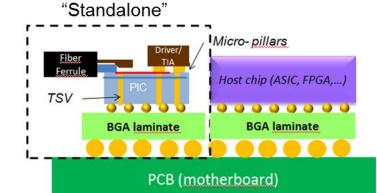

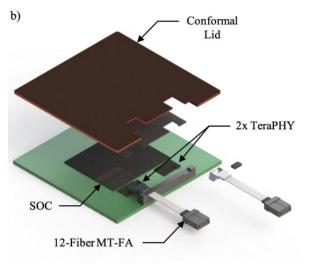

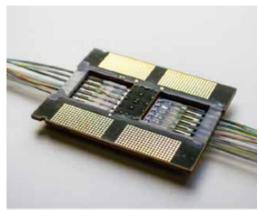

## **NEXT STEP : SYSTEM IN PACKAGE REQUIREMENTS**

Ayar Labs' TeraPHY

leti

Ceatech

**Rockley Photonics' OptoASIC**

- To provide 25 Tbps switches (and 50 Tbps) with Photonic Transceiver

- Low footprint, high density modulators needed

- TSV may improve integration

- Reflow compatible connectors

needed

- Laser integration management

- Many new module architectures from Start ups & RTOs

#### "System-in-package"

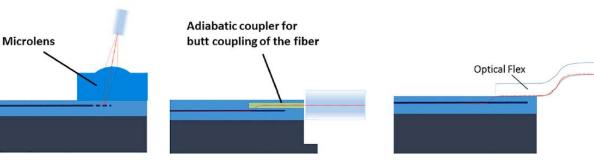

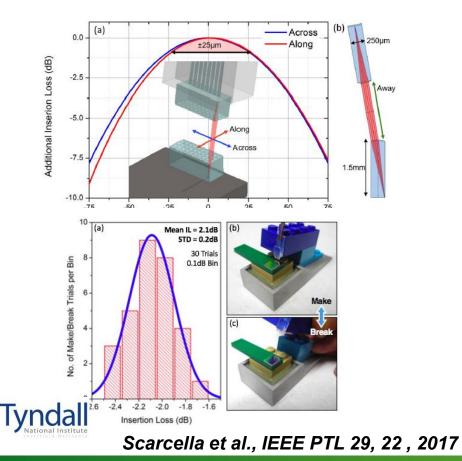

## FIBER COUPLING

- Not pluggable

- Not broadband

*O. Castany, ESTC 2016 ; Jun Su Lee, IEEE JSTQE 22,6, 2016*

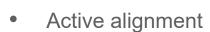

Fig. 2. (a) Cross-section schematic of an SMF28 fiber, showing the 8.2  $\mu$ m fiber core centered in the cladding layer, wave-guiding the 10.4  $\mu$ m MFD 1.55  $\mu$ m mode. Side view schematics of (b) planar polished, (c) angle polished, and (d) lensed SMF28. (e) Schematic of UHNA-to-SMF28 splicing, showing the thermally expanded adiabatic taper. The (b), (d), and (e) geometries are commonly used for edge coupling, while the (c) geometry is preferred for grating coupling.

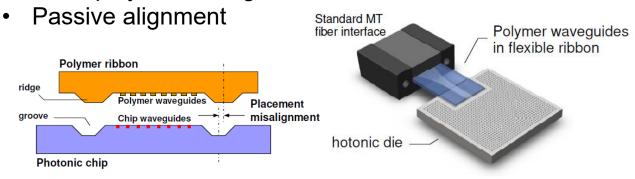

# Passive alignment Easy to package Broadband Small Form Factor

# WANTER !

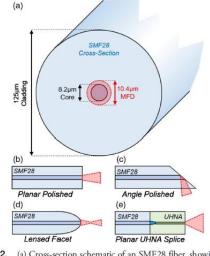

Fig. 22. Alternative techniques for fiber attach to PIC.

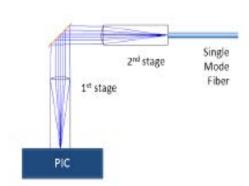

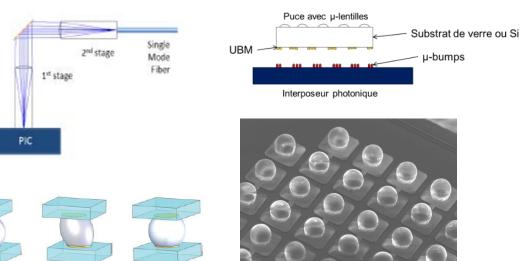

### **Microlens coupling**

- Relaxed lateral tolerance

- Two stage optical train

- Enable pigtail free module

0,5 µm misalignment demonstrated

D. Zonou et al. , ECTC 2017

### **Evanescent coupling approach** (IBM)

Evanescent coupling between • PIC and polymer waveguide

MT fiber ferrule

Polymer ribbon (end view)

#### P. Fortier et al., C2Mi workshop, 2015

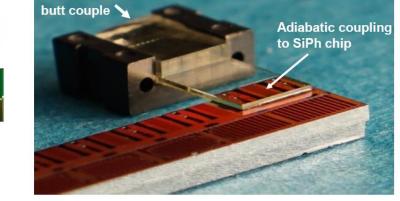

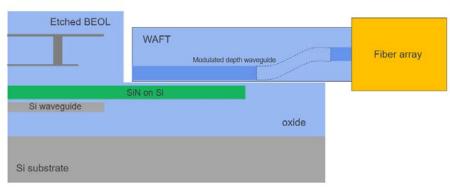

**Evanescent coupling** to SiN-on-Si waveguide layer (ST / Teem Photonics):

- Broadband and single-mode in O-band and C-band

- Low loss (< 1.5 dB from fiber to SiN) •

- Low PDL (< 0.2 dB) •

- Alignment tolerant

Fig 15 Glass interposer assembled Silicon Photonics Device with Cavity Etched BEOL

#### From Binda et al, EMPC 2019

### leti <sup>Ceatech</sup>

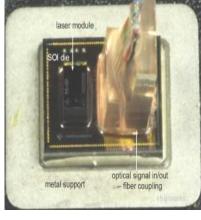

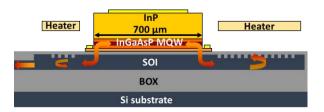

### LASER INTEGRATION STRATEGIES

De Dobbelaere, OFC 2014

#### Micropackaging

Luxtera, Tyndall

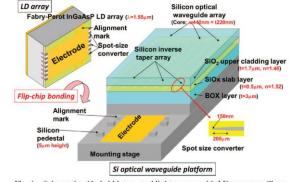

Fig. 1 Schematic of hybrid integrated light source with LD array on silicon platform made using SSC with  $SiO_x$  slab layer.

#### Shimizu et al., Trans. Jap. Inst. Of Elec. Pkg., 2014

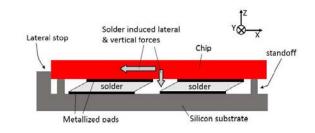

Self aligned flip-chip (Hybrid)

B. Szelag, IEDM 2017

#### **Direct bonding**

Intel, UCSB, LETI

EPS Workshop| Stéphane Bernabé | 21.10.21 | 38

Petra, IBM, IZM

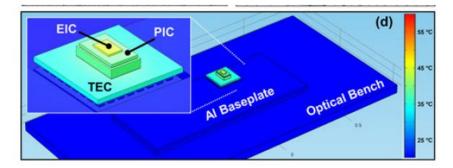

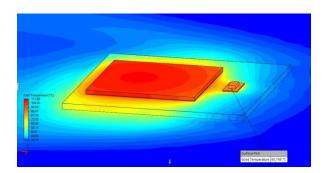

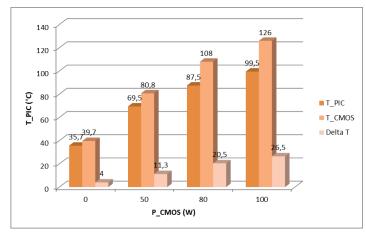

- Photonic devices are temperature sensitive

- In co-packaging approach, proximity to the host chip could be a problem

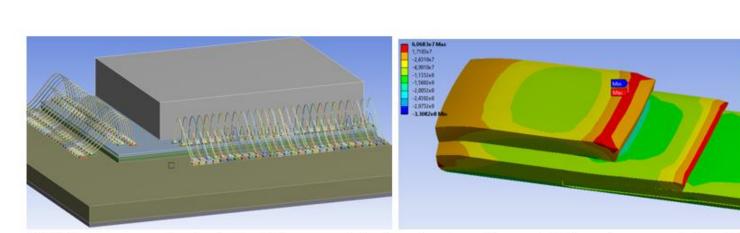

Fig. 8. (a)–(c) COMSOL model of the ONU, spanning the macroscopic dimensions of the TEC and Al baseplate to the microscopic dimensions of the CPB interconnects between the electronic-IC and PIC. (d) An example of the temperature map of the thermal stack and Al base-plate used to extract the temperature profiles in Fig. 9(a).

J. S. Lee et al., « Meeting the Electrical, Optical, and Thermal Design Challenges of Photonic-Packaging », *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 22 nº 6, p. 409-417, nov. 2016

FEM thermo-mechanical simulation model of a wire-bond based PIC package module with the typical material deformation maps due to mechanical stress and/or heat within the package. Source: B. Sirbu / Fraunhofer IZM

• **RF S-parameters**

25 Gbits/s 50 Gbits/s 75 Gbits/s

## A STRATEGY FOR ELECTRONIC/PHOTONIC CONVERGENCE

#### **THROUGH SOME EUROPEAN R&D INITIATIVES**

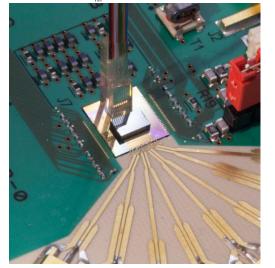

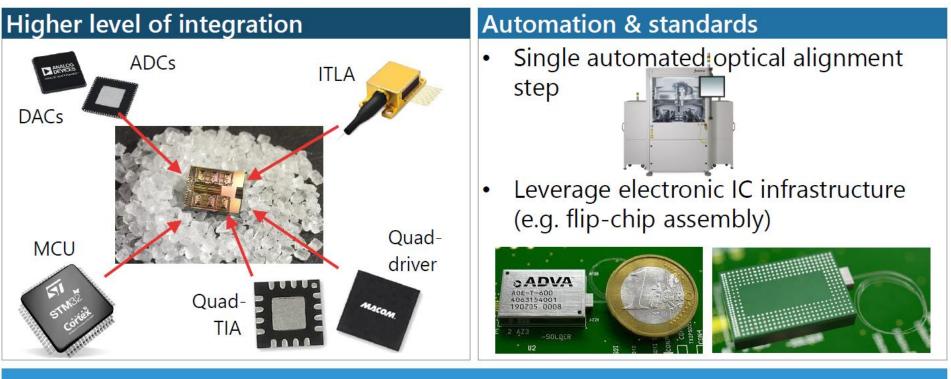

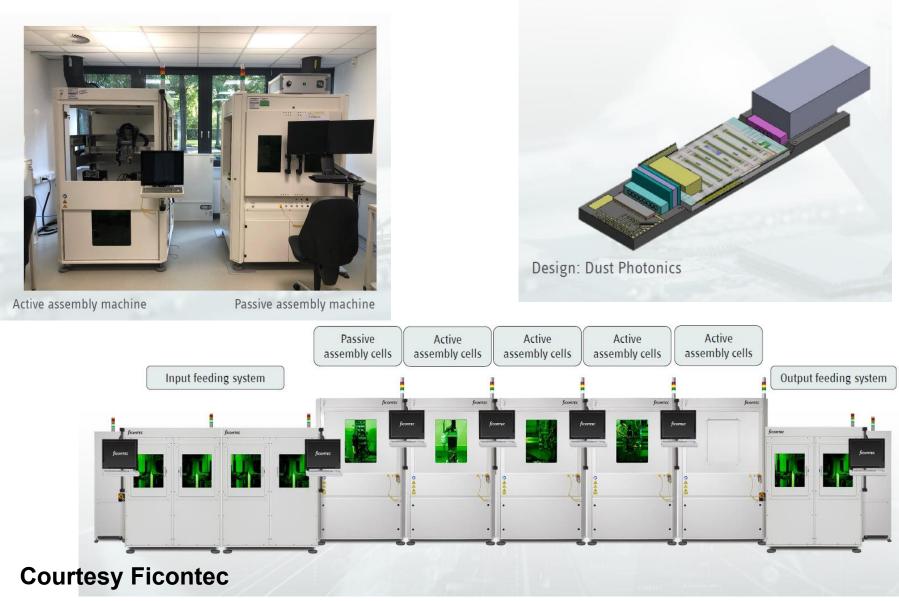

## **STEP1 : MASSIVE AUTOMATION**

## Cost

~80% of cost is in packaging

Integration, automation & volume

#### Courtesy of B. Wolfheil, ADVA

### **STEP1 : MASSIVE AUTOMATION**

MASSTART

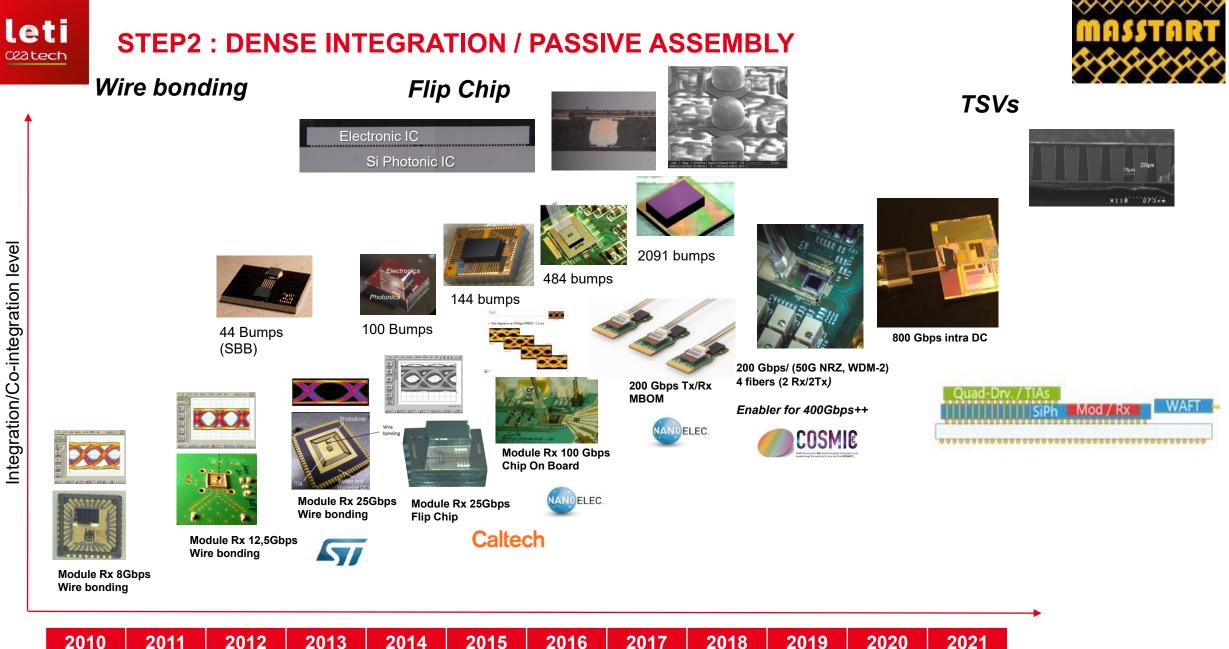

## **STEP2 : DENSE INTEGRATION / PASSIVE ASSEMBLY**

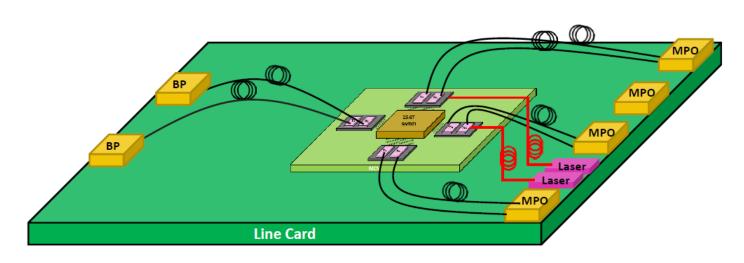

- · All fibers are routed to the passive front panel or backplane fiber connectors

- Module can be connected to the line card either using:

leti

Ceatech

- · Socket bad thermal connectivity, fibers may be glued in place during assembly

- BGA good thermal performance, fibers cannot go through reflow

- · Air flow through the line card is improved due to the elimination of the pluggables on the front panel

Figure 20: High speed microring with 45GHz BW, demonstrated by Intel [17].

Integration/Co-integration level

EPS Workshop| Stéphane Bernabé | 21.10.21 | 45

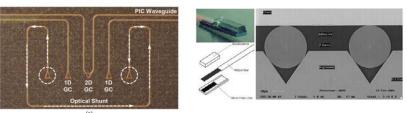

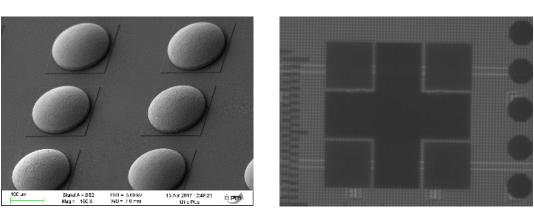

## SELF ALIGNMENT OF MICROLENSES

- Use of copper pillars to align first stage

- Through substrate IR observation of verniers

- <0,5 µm misalignment obtained

- Robust process (7µm offset is realigned)

- Compatible with High throughput bonding machine

EHT = 15.00 kV

WD = 9.3 mm

Signal A = SE2 Grand. = 1.12 K X Date :13 Nov 2012 Heure :14:48:34

leti

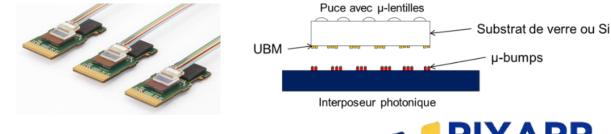

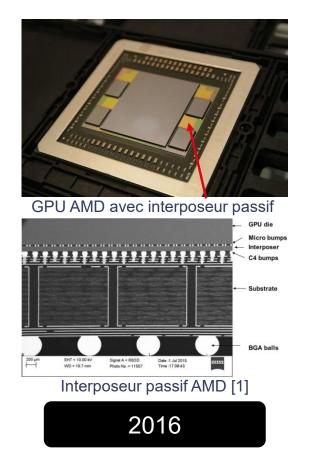

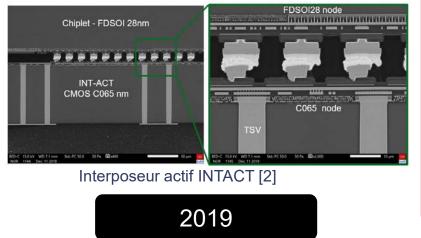

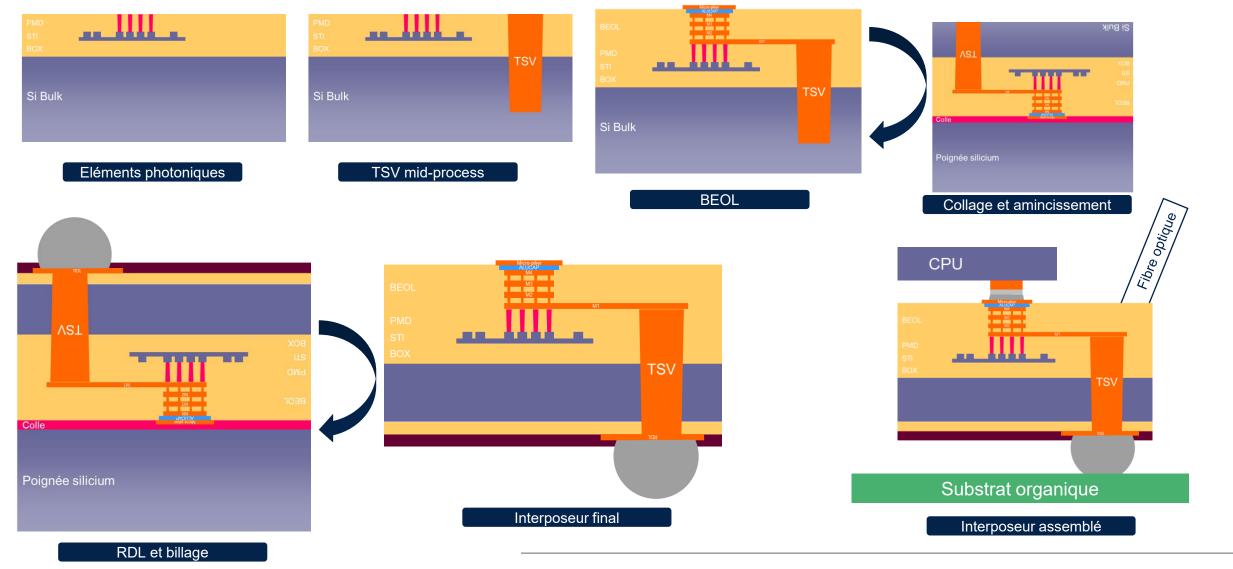

## **STEP 3 : THE ROAD TO PHOTONICS INTERPOSERS**

#### Passive Interposer

#### Only electrical Routing

#### Active Interposer

Electrical Routing DC-DC conversion Electrical Network On Chip

#### Photonic Interposer

Electrical Routing Optical Network On Chip OE conversion

202x?

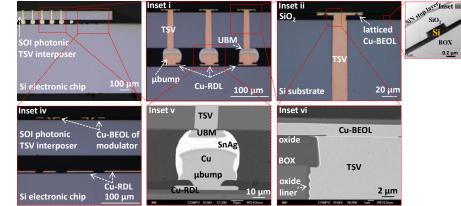

[1] C.-C. Lee et al., 2016 IEEE 66th Electronic Components and Technology Conference (ECTC) [2] P. Coudrain et al., 2019 IEEE 69th Electronic Components and Technology Conference (ECTC)

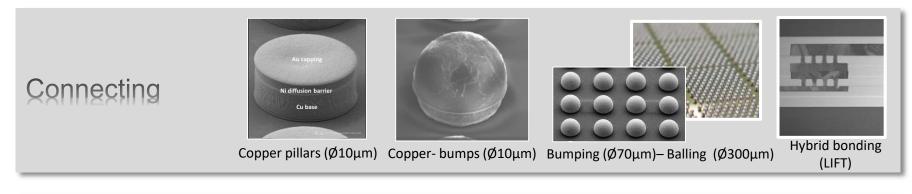

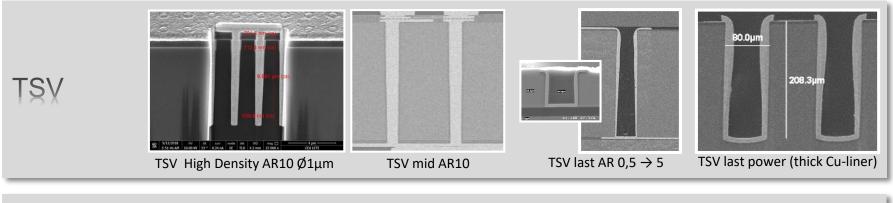

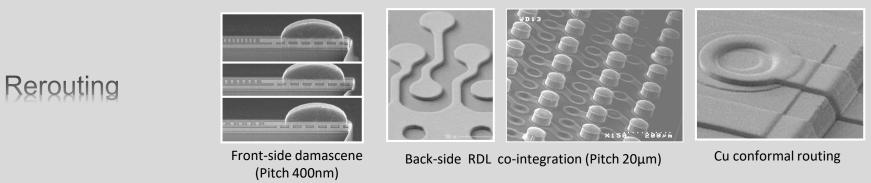

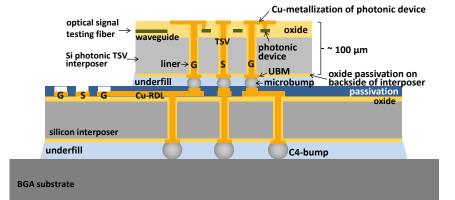

## **3D TECHNOLOGIES - LAB STATE OF THE ART**

Courtesy of J. Charbonnier

## FIRST PHOTONIC INTERPOSER (IME/ASTAR, 2016)

Yang, ECTC 2016

leti

Ceatech

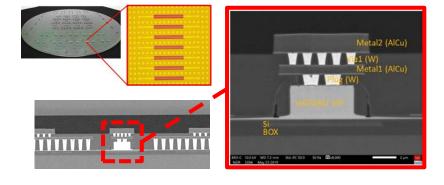

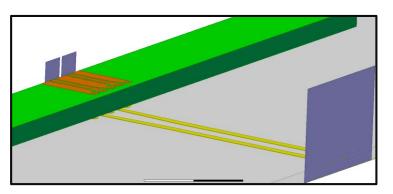

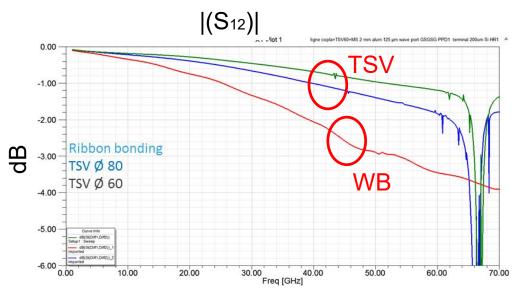

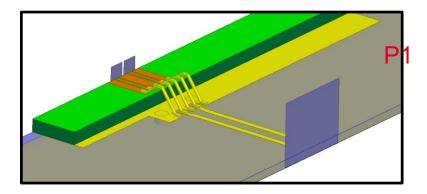

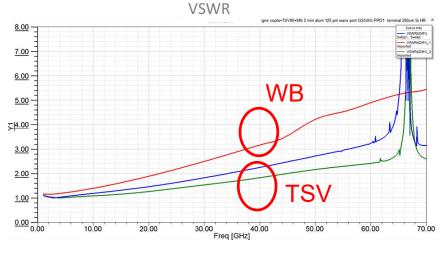

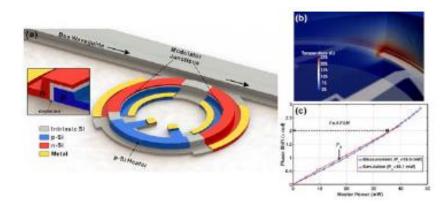

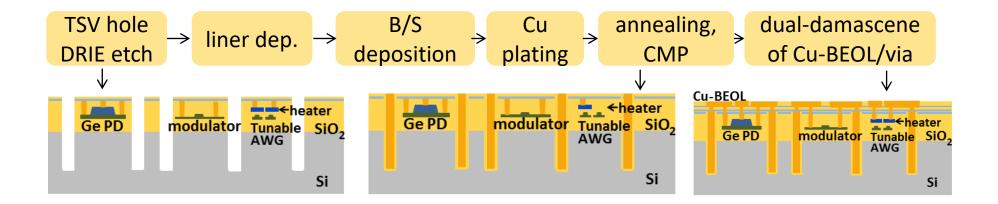

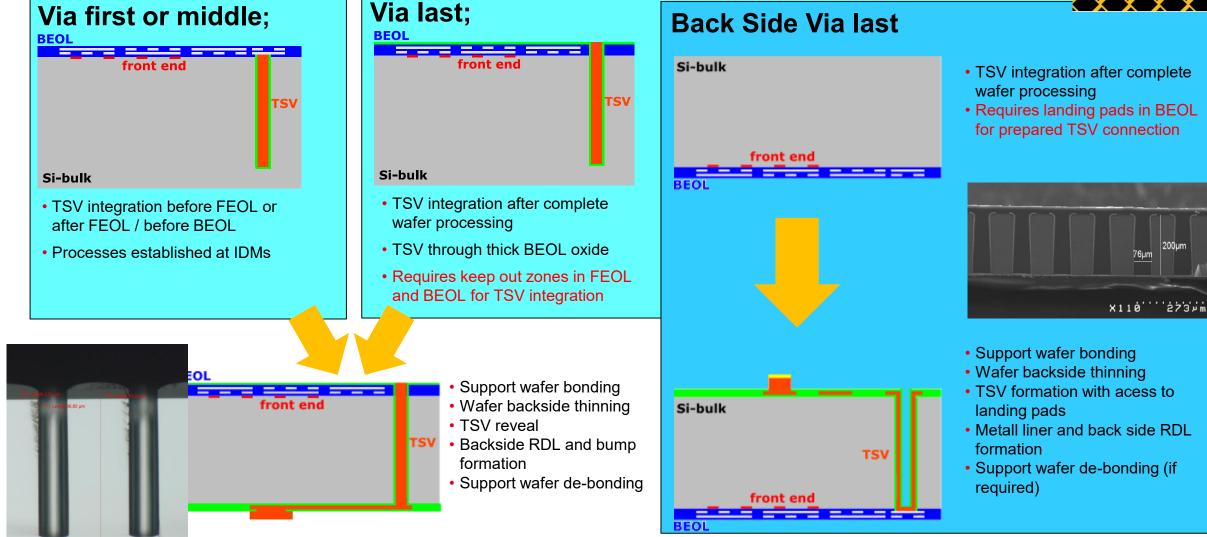

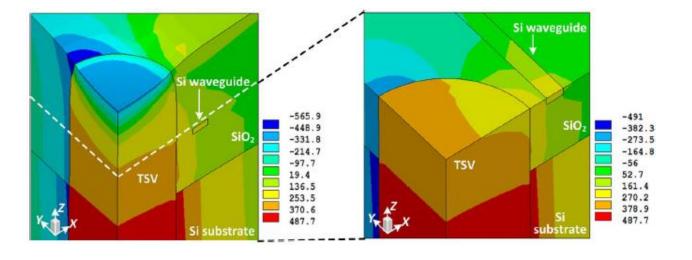

## **TSV DEVELOPMENT**

Courtesy of B. Sirbu, Fraunhofer IZM.

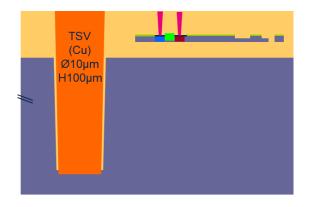

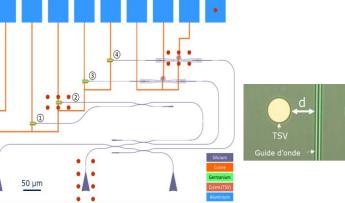

## **PHOTONIC INTERPOSER AT CEA LETi**

Dia. 10~12  $\mu m,$  height 100  $\mu m$  TSV mid process

Does TSV interfere with photonics structures? CTE differential Thick BOX (can lead to warpage then stress) Optomechanical effect Keep Out Zone for Designers ?

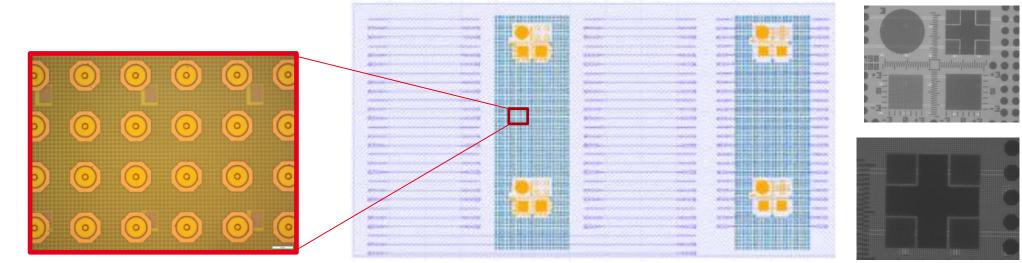

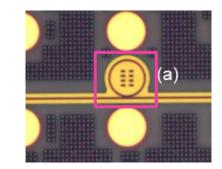

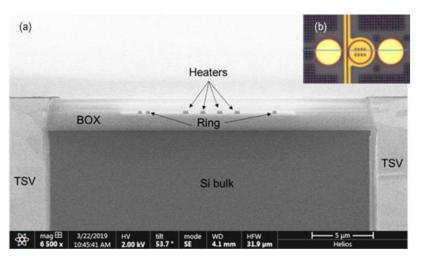

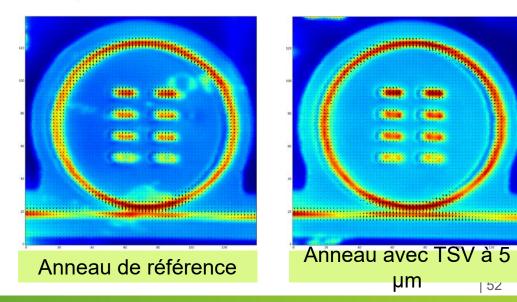

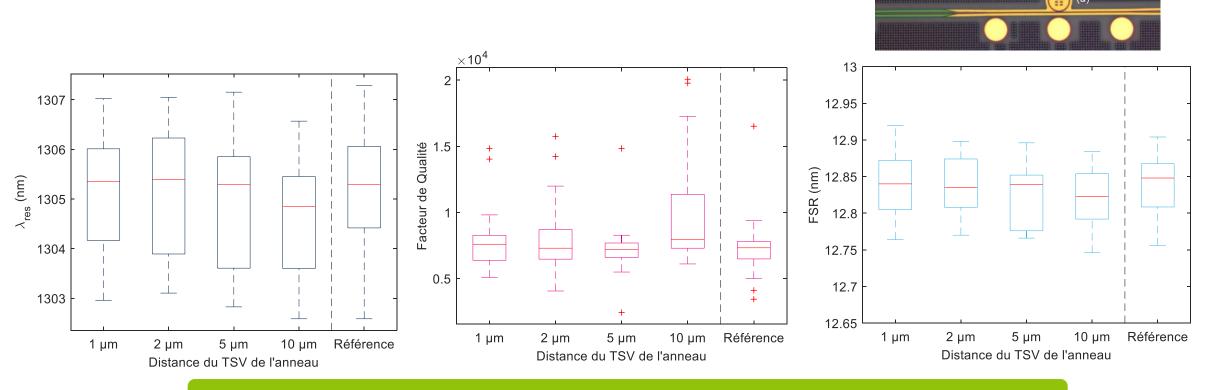

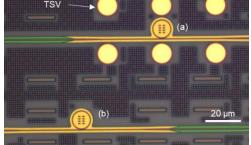

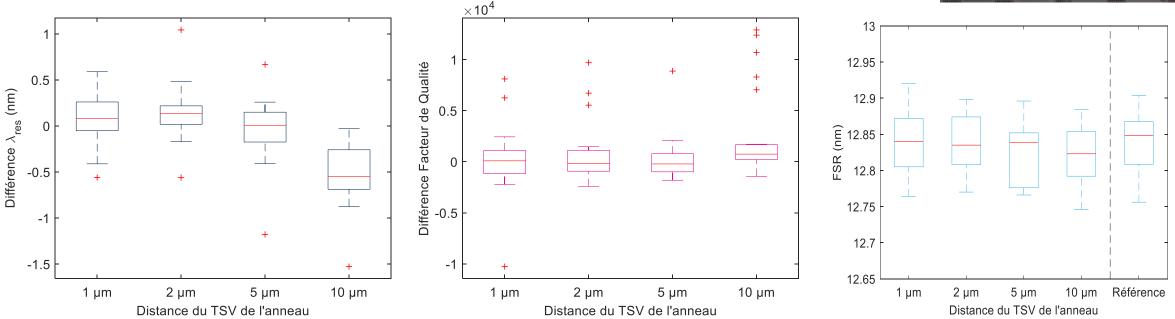

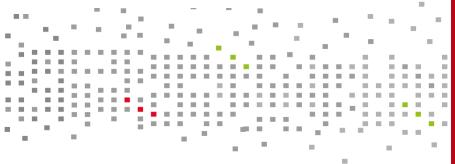

## PHOTONIC INTERPOSER AT CEA LETI

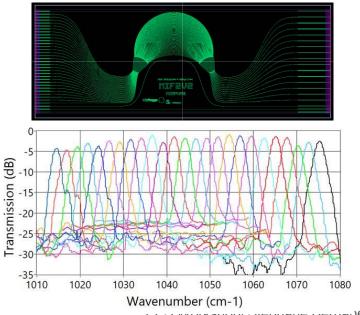

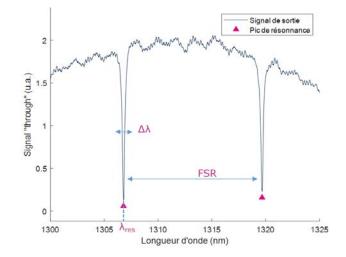

- Fabrication of Ring filters with TSV –last, on ST + LETi 300mm platform

- Measurement of X-Ray diffraction (Synchrotron) No evidence of high stress due to the TSV above 5µm distance

Confirmed by mixing simulated field of stress with FDTD optical simulations (Lumerical)

$\Delta n_{eff}=~5,8\cdot10^{-4}$

Experimental O/E measurements of Ring Filters

Fig. 4. a) SEM cross section of the TSV-surrounded ring before BEOL, b) optical top view of the ring and its TSVs and corresponding cross section plane

TSV

• Ring features as a function of TSV-Ring distance

TSV effect is below process dispersion

P. Tissier, PhD Thesis defense

## **PHOTONIC INTERPOSER AT CEA LETi**

#### No measured impact of TSV, KOZ > $1\mu m$ is safe

P. Tissier, PhD Thesis defense

Silicon Photonics has widespread at every stage of the Internet Network, now targeting emerging applications

#### This lead to a new paradigm in terms of packaging & assembly

- Mass manufacturing is needed

- Advanced packaging technologies will be applied

- The main driver will always be the Cost !

### SiPho packagers have to face some **challenges**:

- Laser integration

- Thermal constrains

- Fiber connector

- 3D integration

#### CEA LETI with ST microelectronics achieve a Photonics Interposer using Via Mid TSV

=> Keep Out Zone >1µm is OK for designers

#### Acknowledgements :

Karim Hassan Jean Charbonnier Pierre Tissier Quentin Wilmart Sergio Nicoletti Daivid Fowler

Bogdan Sirbu (IZM) Tolga Tekin (IZM) Paraskevas Bakopoulos (nVIDIA)

Leti Photonics team Leti Packaging team MASSTART project partners

# **Q & A**

Leti, technology research institute Commissariat à l'énergie atomique et aux énergies alternatives Minatec Campus | 17 avenue des Martyrs | 38054 Grenoble Cedex | France www.leti-cea.com

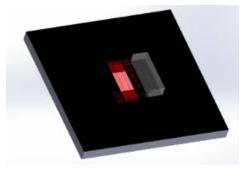

# Procédés de fabrication de l'interposeur photonique

06/10/2021