# On-Shoring the Next Generation of Advanced Packaging

February 17, 2022

Charles Woychik, Ross Miller, Bradley Ferguson and Clifford Sandstrom\*

SkyWater Technology Kissimmee, FL 3473 \*Deca Technologies Tempe, AZ 85284

## Agenda

- SkyWater History & Background

- Chiplets 3D Heterogeneous Integration

- SkyWater AP Offerings

- Si-Interposers

- Hybrid Bonding Interconnect

- Wafer Level and Fan-Out Packaging

- Solder bumping & Assembly

- Roadmap

- Summary

## Agenda

- SkyWater History & Background

- Chiplets 3D Heterogeneous Integration

- SkyWater AP Offerings

- Si-Interposers

- Hybrid Bonding Interconnect

- Wafer Level and Fan-Out Packaging

- Solder bumping & Assembly

- Roadmap

- Summary

# We streamline the concept to market journey for micro- and nanotechnologists.

**Technology as a Service (TaaS)**

**Innovation as a Service**

Manufacturing as a Service

## We are the only **U.S.-owned** pure-play foundry.

Extending a legacy of manufacturing excellence to meet the industry's needs in a post-Moore's Law reality

2005

Cypress

2008

SkyWater received DMEA Cat 1A Trusted Accreditation

2017

SkyWater

SkyWater and MIT selected for DARPA 3DSoC program

2018

\$170 M rad-hard technology and building expansion announced

2019

3-year anniversary of SkyWater completion of Cypress ToP contract

#### **OPERATION**

200 mm equipment 91,000 ft<sup>2</sup> Cleanroom Class 10 + SMIF 10,000 30 ML CMOS wafers or 50,000 MOSFET wafers per month 90 nm+ feature geometries

#### CERTIFIED

ISO9001 / IATF16949 Automotive Certified

ISO13485 Medical Certified

ISO14001 Environmental Certified

DMEA Cat 1A Trusted

ITAR and Secure Processing Supported

#### **OPERATION**

200 mm equipment Size: 109,000 ft<sup>2</sup> total 26,000 ft<sup>2</sup> of class 1000 9,400 ft<sup>2</sup> of class 10,000

#### **NOTES**

Site added to operation Feb 2021 DMEA Cat 1A Trusted – pending, planned late 2021 Facility will enable custom advanced packaging solutions

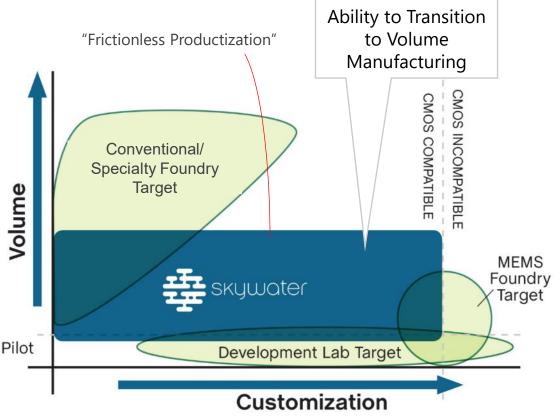

## SkyWater is Defining a New Category

#### Partnership Pathways: Prototype to Production

#### Research

#### **Commercialization**

**Primary Activity**

**Technology Readiness & Manufacturing Readiness**

Operating & Business Model

**Example Start Points**

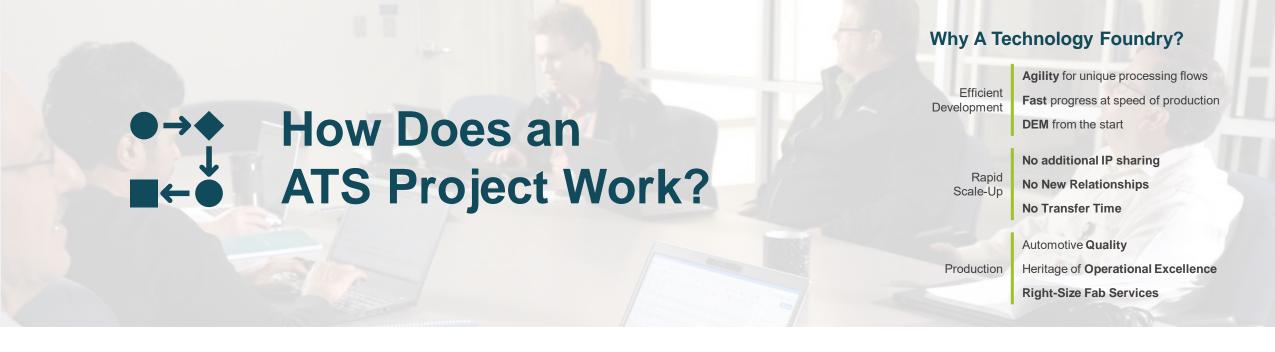

Advanced Technology Services (ATS)

#### R&d:

Proof of Concept Tech Demonstration Process Development

TRL / MRL: 3~6

- NRE

- Tooling

Qualification

#### r&D:

Maturing & Qualifying Capabilities, Process Flows, and Products for Scale

TRL / MRL: 6~8

- MPW

- NRE

- Tooling

- Early Access Program

- Flow Transfer

Photonics

Wafer Services

<del>r&</del>d:

Mfg. Volume Production

TRL / MRL: 8~9

- 1x Setup

- Per Wafer

Mixed-Signal

**Power Discrete**

**YOUR Idea**

- Understand the device performance objective

- Review device architecture concepts

- Jointly brainstorm possibilities

- · Identify end goal

#### Detailed Project Scoping & Setup

- Align on project objectives

- Align team resources with timeline requirements

- Establish interface requirements

- · Establish business terms

- Choose fixed-price or consumption model

- · Identify tool hosting needs

#### **Co-Create Your Ideas**

- Customer and SkyWater team execute development work

- Continuous learning and idea generation

- Data exchange per customer requirements

- Quarterly reviews

- Customer defined milestones

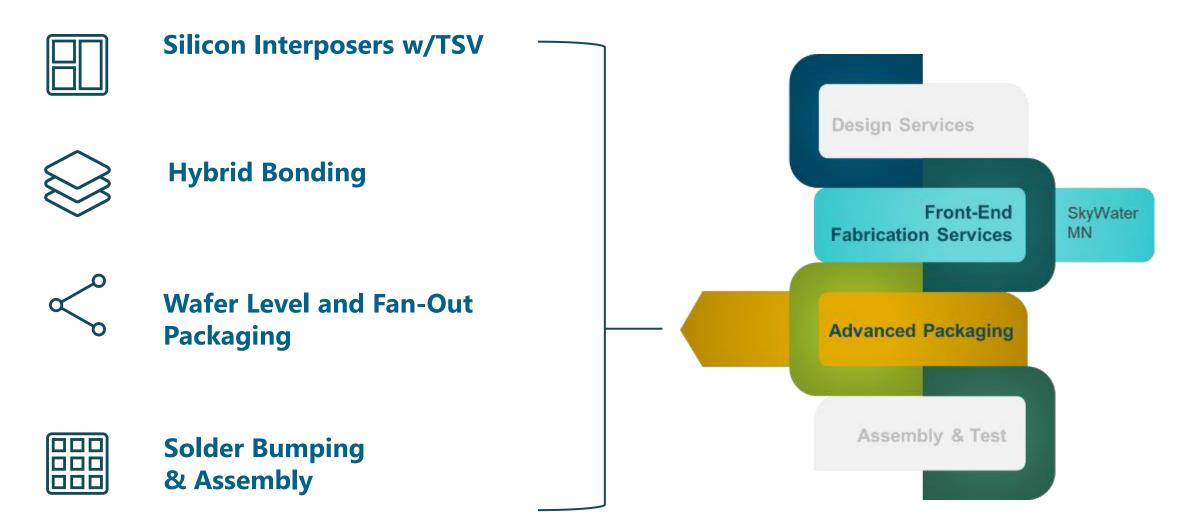

## Capabilities for Advanced Integrations

## Agenda

- SkyWater History & Background

- Chiplets 3D Heterogeneous Integration

- SkyWater AP Offerings

- Si-Interposers

- Hybrid Bonding Interconnect

- Wafer Level and Fan-Out Packaging

- Solder bumping & Assembly

- Roadmap

- Summary

#### **Drivers for Chiplet Integration**

SOC

End of Cost Advantage of Moore's Law

#### Shared Package

- Difficult

- Very Costly

- Low Initial Die Yield

#### **Pros**

- SWAP

- Flexibility

- Optimized Performance

- Lower Power

- Shorten Time-to-Market

- Gordon Moore predicted that eventually one would go to packaging individual chips

Original paper.

- Thermal optimization

- Spin multiple products faster

#### Cons

- Create System Integration Ecosystem (Supply Chain and Business).

- KGD Known Good Die

- Establish a pull by customers

- Standards

- Software Design Tools

- Yield Loss Ownership

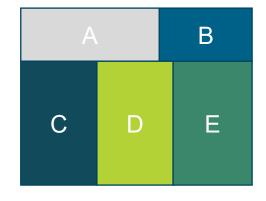

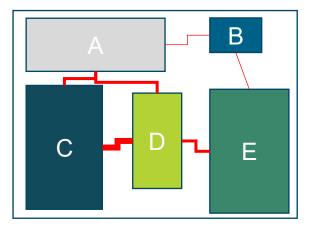

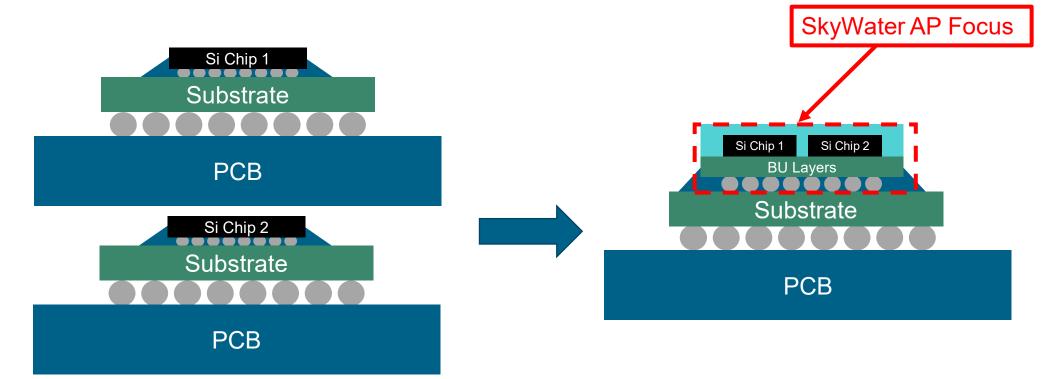

#### Pathway to 3D Integration (Fan-Out)

Conventional Flip Chip Attach

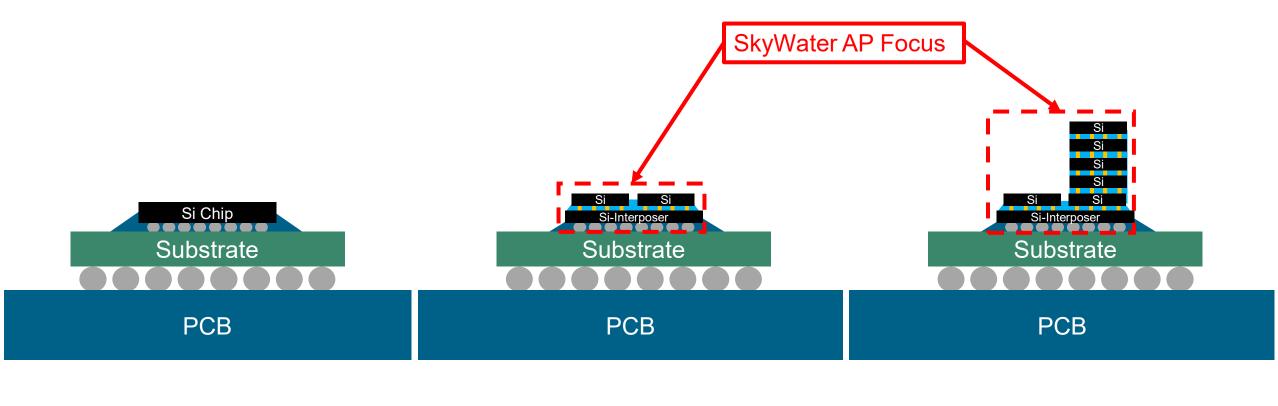

## Pathway to 3D Integration (Interposer)

Conventional Flip Chip Attach

2D Interposer Integration

3D IC Integration

## Agenda

- SkyWater History & Background

- Chiplets 3D Heterogeneous Integration

- SkyWater AP Offerings

- Si-Interposers

- Hybrid Bonding Interconnect

- Wafer Level and Fan-Out Packaging

- Solder bumping & Assembly

- Roadmap

- Summary

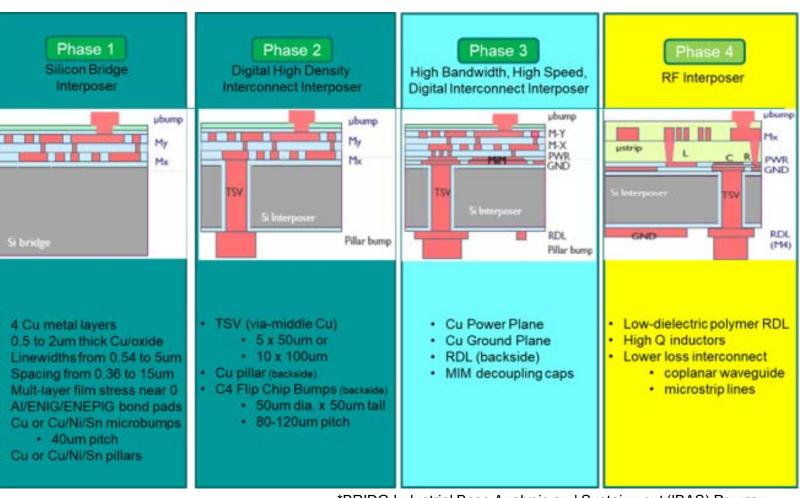

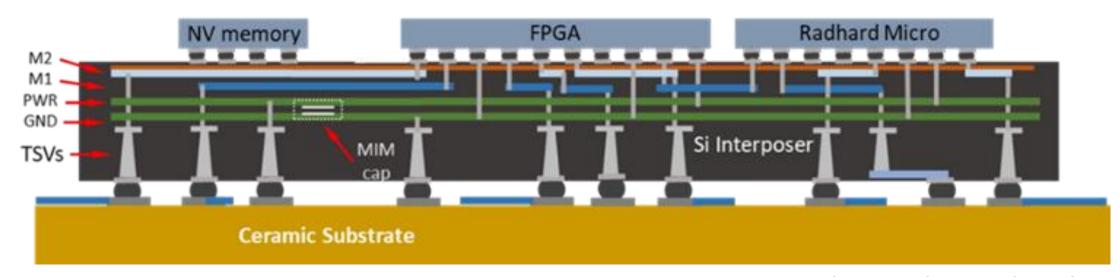

## Partnership with BRIDG to Develop Si-Interposers

Heterogeneous Integration & Advanced Packaging

Establishes a domestic silicon interposer capability for the industrial base

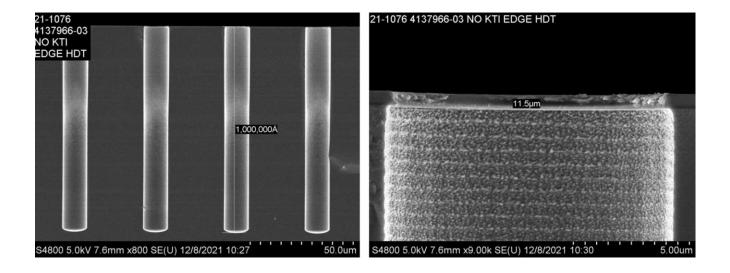

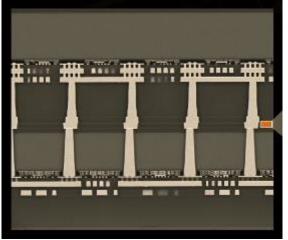

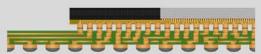

## SkyWater Si-Interposer

Phase I: Metallization buildup layers.

Phase 2: Via formation

#### Si-Interposer Assembly – BRIDG & SWFL

Schematic Courtesy of BRIDG

- Build Si-Interposer at SWFL.

- BRIDG and SWFL work with domestic supplier on first phase of assembly development. Goal is to have capability at SWFL.

- Generate reliability test data with Navy Crane.

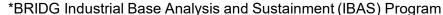

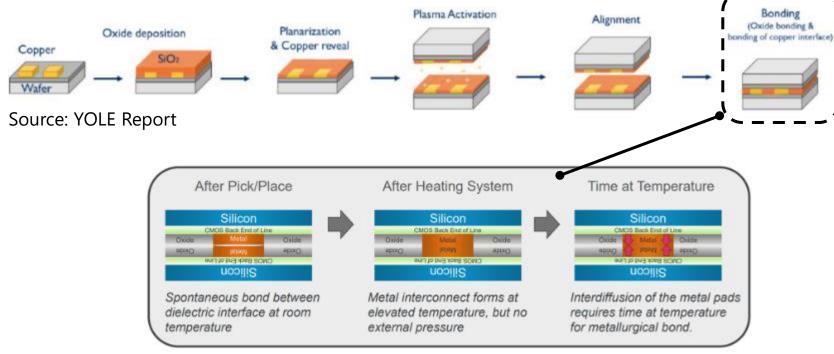

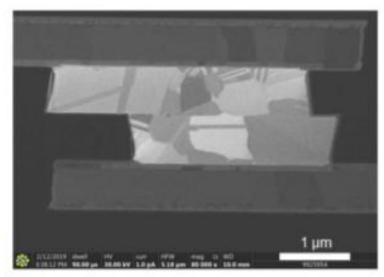

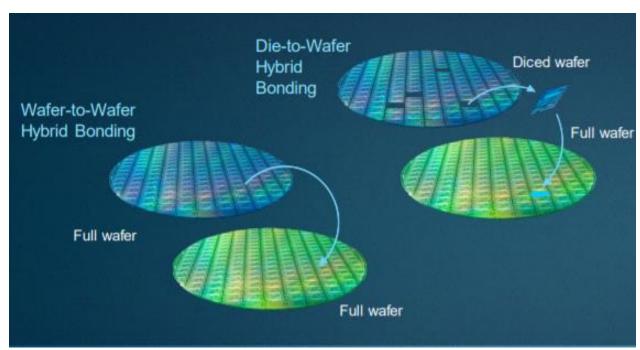

#### Hybrid Bonding Interconnect Formation

- Dielectric bonding at room temperature

- Metal interconnect formation at elevated temperature

- Thermal annealing of metal pads

Source: Xperi

Source: J Mudrick, et.al., MESA, Sandia National Laboratories

FIB-SEM images of metal pads after thermal annealing

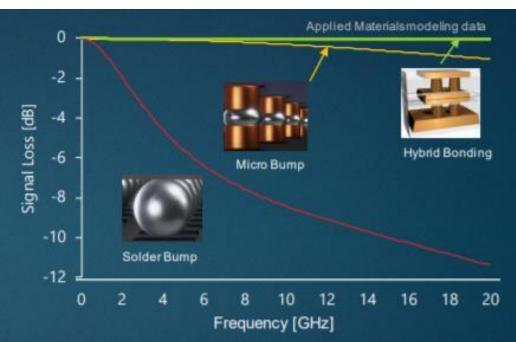

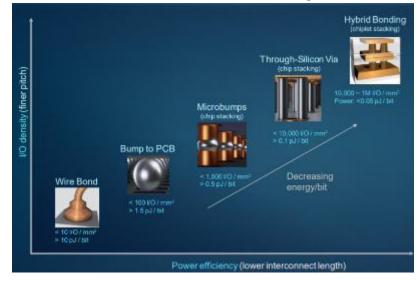

## Hybrid Bonding Interconnect

- Shortest connections with face-to-face chip bonding

- Outstanding performance compared to solder and micro-bumps

Source: Applied Materials, 2021 ICAPS and Packaging Master Class

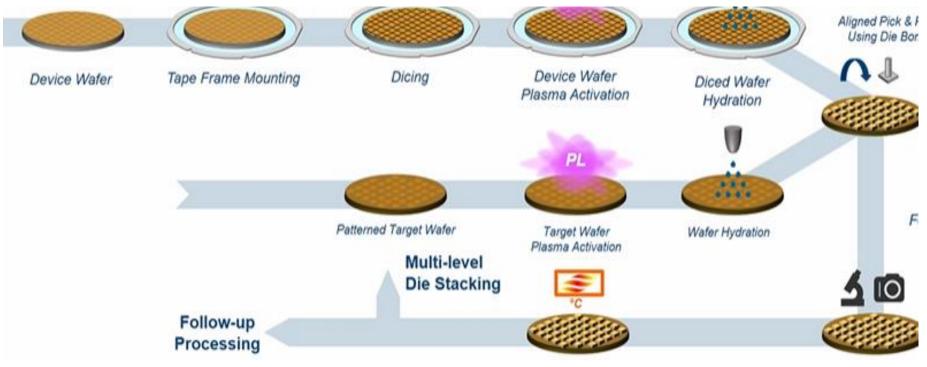

## Hybrid Bonding Die to Wafer (D2W) process flow and equipment

Source: SUSS

## Hybrid Bonding Die to Wafer (D2W)

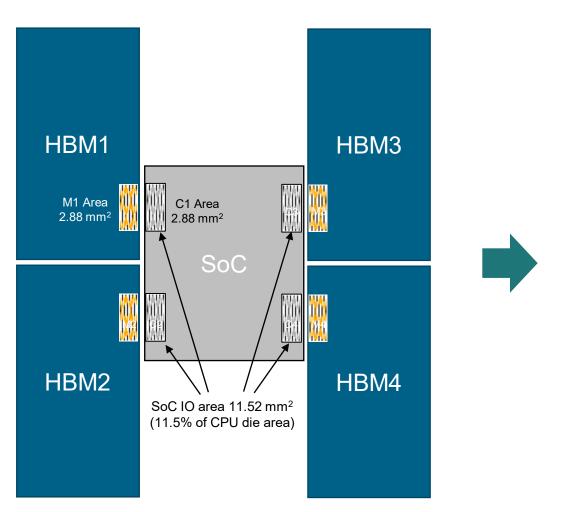

Packaging System Interconnect Scaling Roadmap

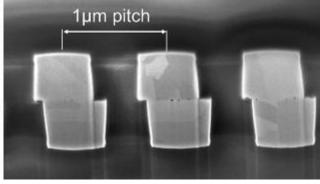

- Advanced micro bumps and pillars are structures with a 40-um pitch (25 um pillar). Going forward, the industry can scale bump pitch to 20 um

- The industry needs a new interconnect solution beyond bumps and pillars

- Enabling Cu/Cu Hybrid bonding to stack memory on memory or memory on logic. This process is challenging and involves complex fab-level processes

- Hybrid bonding enables 250K to 1M interconnects per square millimeter

- 40 um pitch micro-bumps enables ~600 interconnects per square millimeter

Source: Applied Materials, 2021 ICAPS and Packaging Master Class

Source: AMD, Hot CHIPS

conference 2021

## **Evolution of Bonding Methods**

| Bonding Method                           | C4 FC (Contolled<br>Collapse Chip<br>Connect) | C2 FC<br>(Chip Connect) | TC/LR (Local<br>Reflow) FC | TC FC   |

|------------------------------------------|-----------------------------------------------|-------------------------|----------------------------|---------|

| Schematic Diagram                        |                                               | 13                      | I                          | I       |

| Major Bump Pitch Range at<br>Application | > 130 um                                      | 140 um ~ 60 um          | 80 um ~ 20 um              | < 30 um |

Source: SUSS

*Hybrid Bonding Interconnect* with 1 μm pitch

Source: AMD, Hot CHIPS conference 2021

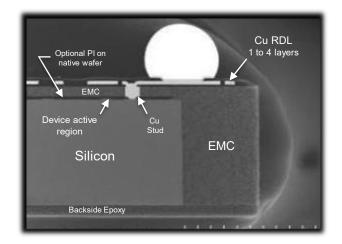

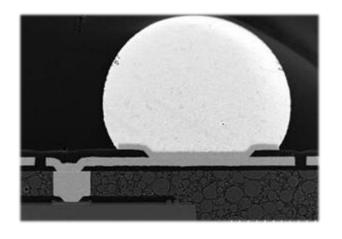

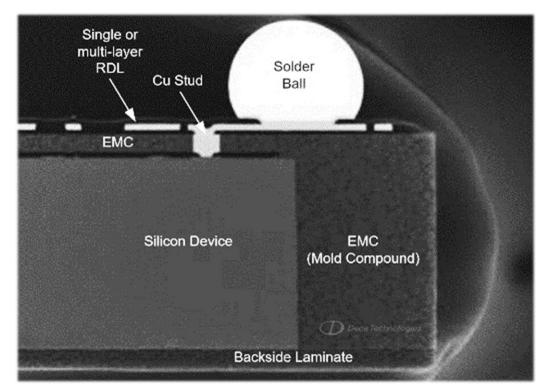

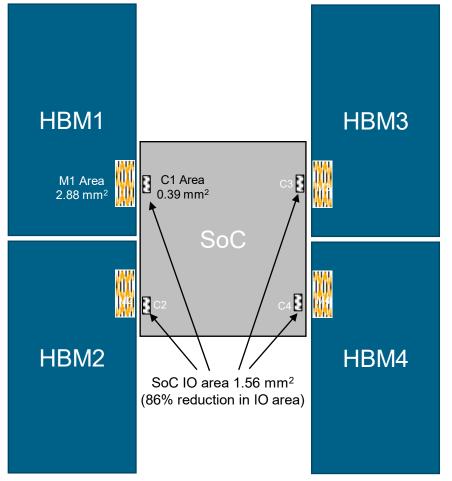

#### Deca's M-Series™ Fan-Out Basics

- Chips-first, chips-up fan-out technology

- Fully encapsulated active device region (key differentiator)

- Production yields > 99.85%+ on over 3 million shipping per day

- Planar surface enables scaling to fine CDs

- 5µm line & space in Gen 1.5

- 2µm in Gen 2

- Adaptive Patterning® for high yield & high interface density

- 45µm bond pad pitch in Gen 1

- 20µm in Gen 2

- Next closest competitors: TSMC InFO at 55μm & Intel EMIB at 45μm

- 300mm wafer format in high volume production for Gen 1

- 600mm square panel starting production in 2021 for Gen 1

## M-Series Structure – Planarity key to 3DHI

Cycles to Fail

Basic Package Construction of M-Series

BLR Comparison of M-Series versus WLP

- Lowering of e-CBI (chip board interaction) stresses applied to device due to molded stress buffer layer between the device surface and the PCB

- Typical 200% BLR performance improvement over traditional fan-in wafer level packaging (WLP)

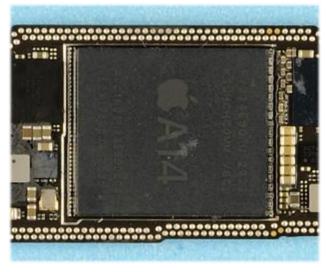

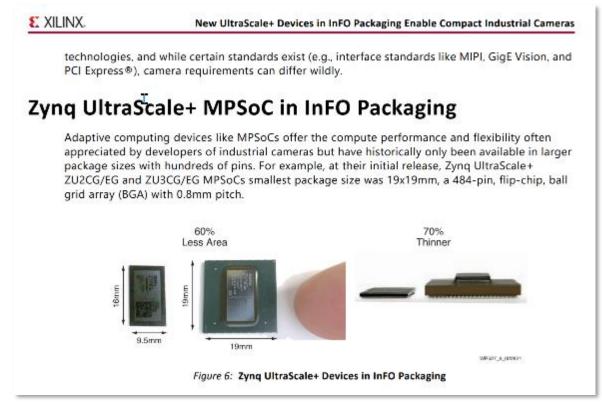

## Customer Adoption Examples of Fan-out

#### Apple Applications Processor Device in InFO PoP iPhone 12 Pro Max 5G

Prismark, CUSTOM TEARDOWN ANALYSIS: APPLE A14 Report No. 6771 - January 2021

https://www.xilinx.com/support/documentation/white papers/wp527-info-cameras.pdf

Significant electrical signal integrity benefits of fan-out vs. Si interposer or flip chip on substrate

#### FEOL Silicon Area Reduction From Pitch Reduction

> 10% reduction in advanced silicon die size

#### Competitive Device Interface Pitch Density Comparison

Cu Pillar Flip Chip (flip chip on substrate)

TSMC InFO (Chips first fan-out) M-Series Gen 1 (Chips first fan-out)

**EMIB** (Hybrid chips in substrate)

Higher density bond pad pitch

M-Series Gen 2 (Chips first fan-out)

Flip Chip Cu Pillar

Die pad pitch: 100 µm IO per mm<sup>2</sup>: 105

**TSMC InFO**

Die pad pitch: <u>55 μ</u>m IO per mm2: 314

**Deca M-Series Gen 1** Die pad pitch: 45 µm

492

IO per mm2:

Intel EMIB

Die pad pitch: 45 µm (36 µm\*) IO per mm2: (806)

Deca M-Series Gen 2.1

Die pad pitch: 20 µm IO per mm2: 2,518

> #1 in high density

\*https://www.anandtech.com/Show/Index/15980?cPage =2&all=False&sort=0&page=1&slug=intel-next-gen-10micron-stacking-going-3d-beyond-foveros

M-Series Gen 2 delivers order-of-magnitude density increase

#### Deca's M-Series Technology Roadmap

Gen 1 2018 →

Codec

RF

**PMIC**

Single-die

- · Protected fan-in

- Fan-out

**IoT Device**

**Dual PMIC**

- Integrated PMICs

Gen 1.5 2021 →

3D PoP - Mobile Applications Processor

Fan-out SoC - Advanced node silicon

Embedded Bridge Die Interposer - HBM intg

#### Passive & Active Interposers - CPU, GPU, AI

- Existing lithography & AOI equipment

- · Optimized direct & indirect materials

- · Enhanced process flows for 3D integration

- New design rules supporting 3D

#### Gen 2 (SkyWater Fl.)

2022 →

20 µm bond pad pitch 2 µm lines & spaces Up to 5 layers of RDL Full frontside & backside routing

- 3D PoP

- Fan-out SoC

- Embedded Bridge Die Interposer

- · Passive & Active Interposers

Ultra-High Density (UHD) Integration

- New lithography & AOI equipment

- Further material optimization for 5 µm vias

- New design rules supporting 2 μm RDL

- · Adaptive metal fill for up to 5 layers of RDL

## Agenda

- SkyWater History & Background

- Chiplets 3D Heterogeneous Integration

- SkyWater AP Offerings

- Si-Interposers

- Hybrid Bonding Interconnect

- Wafer Level and Fan-Out Packaging

- Solder bumping & Assembly

- Roadmap

- Summary

## Capabilities for Advanced Integrations

Wafer to Wafer

Hybrid Bonding

Full wafer

#### **Silicon Interposers** w/TSV

Die to Wafer

**Hybrid Bonding**

Diced wafer

#### **Hybrid Bonding**

**Wafer Level and Fan-Out Deca's M-Series Gen 2**

2024

## Agenda

- SkyWater History & Background

- Chiplets 3D Heterogeneous Integration

- SkyWater AP Offerings

- Si-Interposers

- Hybrid Bonding Interconnect

- Wafer Level and Fan-Out Packaging

- Solder bumping & Assembly

- Roadmap

- Summary

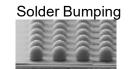

## Summary

- SW AP Roadmap consists of the following core technologies:

- Fan-Out Packaging (Initially wafers, migrating to panels)

- Si-Interposers

- Glass Interposers

- Hybrid Bonding Interconnect

- Maintain technical leadership for all AP areas to ensure our customers have access to a domestic state-of-the-art AP facility.

- Provide solder bumping services (Sn-Pb and Pb-free) and solder assembly services.

- SW is working with our partners to enable a domestic Ecosystem for AP.

Charles Woychik, Sr. Director Advanced Packaging Platforms

Chuck.Woychik@skywatertechnology.com

Are you working on an idea? Let's talk. Get in touch today!

For more information: www.skywatertechnology.com

Contact SkyWater: swfoundry@skywatertechnology.com

**SKYWater**