# Electrical Design of Advanced Packaging in Computing Systems

W. Dale Becker, Ph.D. IBM, Poughkeepsie, NY USA For presentation on 15 June 2022 IEEE EPS Distinguished Lecture

# Computer System Packaging Design

- Fundamentals of Electrical Design of Computer Systems

- The <u>challenges</u> that provide <u>opportunity</u> for engineering ingenuity

- Example: Processor socket challenge Bandwidth, Frequency

- Heterogeneous Integration addressing today's challenges

- Heterogeneous Integration Roadmap (HIR)

- Opportunity to learn more and contribute to the community

# Challenges: Drivers for advancing systems

- Historic Drivers

- Moore's Law

- Dennard Scaling

- Current Reality enabled by

- 3D Devices

- 3D Packaging

- Advanced interconnect

- Heterogeneous Integration

#### **Dennard Scaling**

TABLE I

SCALING RESULTS FOR CIRCUIT PERFORMANCE

| Device or Circuit Parameter      | Scaling Factor       |

|----------------------------------|----------------------|

| Device dimension $t_{ox}$ , L, W | 1/κ                  |

| Doping concentration $N_a$       | κ                    |

| Voltage V                        | $1/\kappa$           |

| Current I                        | $1/\kappa$           |

| Capacitance $\epsilon A/t$       | 1/κ                  |

| Delay time/circuit VC/I          | $\frac{1}{\kappa}$   |

| Power dissipation/circuit VI     | $\frac{1}{\kappa^2}$ |

| Power density $VI/A$             | 1                    |

R. H. Dennard, F. H. Gaensslen, H. -N. Yu, V. L. Rideout, E. Bassous and A. R. LeBlanc, "Design of ion-implanted MOSFET's with very small physical dimensions," in IEEE Journal of Solid-State Circuits, vol. 9, no. 5, pp. 256-268, Oct. 1974, doi: 10.1109/JSSC.1974.1050511.

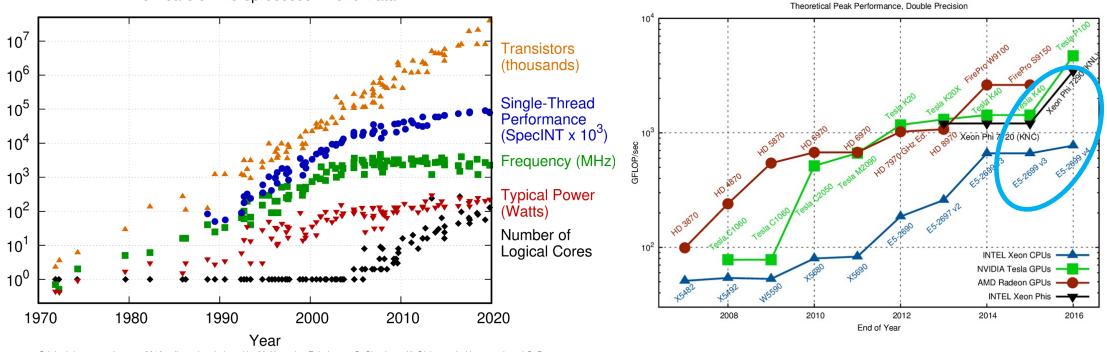

# Scaling Trends

48 Years of Microprocessor Trend Data

From <u>HIR Chapter 2</u> Kanad Ghose, Dale Becker, Co-Chairs

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten New plot and data collected for 2010-2019 by K. Rupp

#### Hardware Trends:

- Everything is getting intrinsically power and memory constrained; new applications are exacerbating the dependence on memory

- Accelerators are more energy-efficient than general-purpose designs, new memory technologies

- Heterogeneously integrated solutions have been making their mark for the past few years!

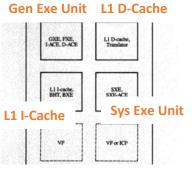

#### IBM Processor Packaging Integration – 50+ years

#### Courtesy: John Dux, IBM Ret'd

#### 1964 to 1990's Silicon & Pkg Integ. Silicon Complexity Î 1<sup>st</sup> Level Pkg

PCB

S/360 - 1964

Complexity

S/370 - 1970

S/3080 - 1980

S/ES9000 - 1990 Glass Ceramic/TF 4-6 TCMs/CPU

Opt. Vector Unit Vector or Crypto

| Figure   | 1              |             |          |             |

|----------|----------------|-------------|----------|-------------|

| Physical | layout of ES/9 | 000 Model 5 | 20-based | processors. |

|          |                | ALC: NO.    |          |             |

Complexity PCB

Today

Courtesy, John Dux, IBM, Ret'd.

S/390 - 1997 CMOS 10 single core PU Chips / MCM

zSeries 990 – 2003 2 PUs/chip System in Package

z13 - 2015 8 PUs/chip System on Chip

512MB cache

Heterogeneous Pkg Int.

Silicon 1 1<sup>st</sup> Level Pkg ↑ PCB

June 15, 2022

IEEE EPS

### Ongoing Challenges for system packaging To deliver the value propositions – Performance and Function

- Cost development and product cost

- Physical form factor Incremental changes

- Signal bandwidth density Increasing quickly

- Voltage regulation (Power In) Integrate closer to load

- Cooling (Power out) Constant power density

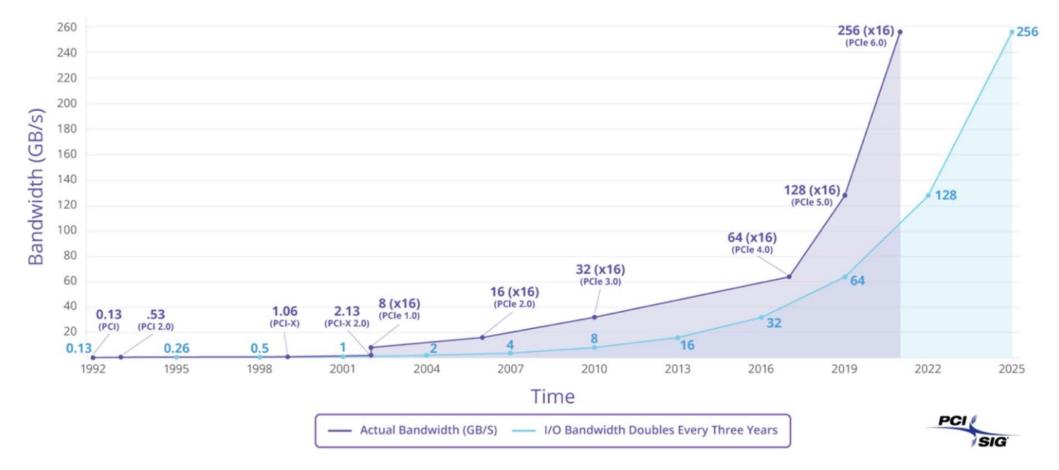

A very visible measure of success in system packaging is the bandwidth achievable and the growth of bandwidth and bandwidth density with new generations of systems.

# Example of signaling data rate growth - PCIe

From <u>HIR Chapter 2, Fig. 22, 2021</u> – Adapted from <u>U. Pirzada, 2017 Hot Chips</u>

# **Physical Metrics**

Linear Interconnect Density,

i.e. Wires (IO)/mm/Layer

Die 1

**EEE** June 15, 2022

photonics

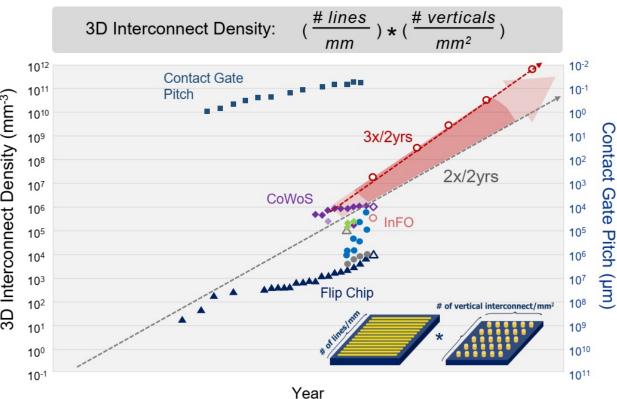

#### HIR Chapter 22: Ravi Mahajan, Chair

10<sup>12</sup> 1011 Pitch 3D Interconnect Density (mm<sup>-3</sup>) 1010 10<sup>9</sup> 108 107 Areal Interconnect Density, 106 i.e. Bumps (IO)/mm<sup>2</sup> 105 104 10<sup>3</sup> **Bump Pad** 10<sup>2</sup> 10<sup>1</sup> 100 10-1 Die 2 Package

#### System Scaling – 3DID Roadmap

D. Yu, 2019 Dec. IEDM Panel, San Francisco, Ca, USA

D. Yu, 2020 May IEEE ECTC Keynote. 2020 Aug. TSMC Technology Symposium,

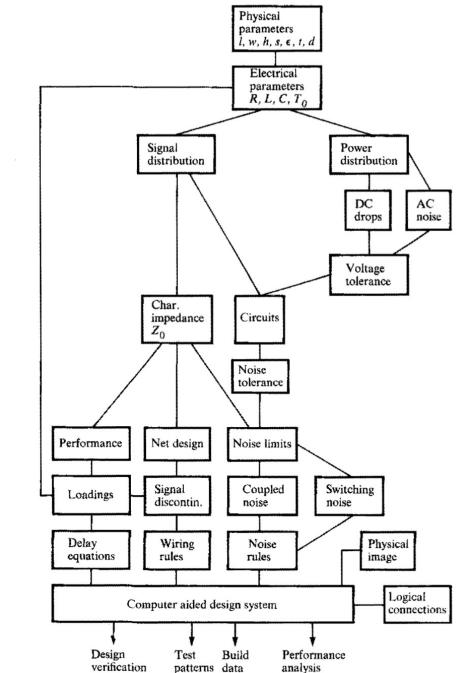

# Fundamentals

- Methodology Input

- Physical Parameters -> Electrical Parameters

- Signal Distribution and Power Distribution

- Design

- Circuits

- Net interconnections

- To

- Achieve performance

- With robust net design

- Ensuring meeting the noise limits in the presence of non-ideal interconnects

- By creating

- Design rules to meet wiring performance and noise criteria

- Methodology Output

- Verified design, build data, performance analysis and test patterns

### Increasing Bandwidth by Generation IBM Example

|                                |                      | POV                              | VER8 high-end p             | package          |                      | POWER9 high-end package       |                              |                  |  |

|--------------------------------|----------------------|----------------------------------|-----------------------------|------------------|----------------------|-------------------------------|------------------------------|------------------|--|

| Bus                            | No. of<br>interfaces | Byte                             | Data rate<br>per lane       | Raw<br>bandwidth | No. of<br>interfaces | Byte                          | Data rate per<br>lane        | Raw<br>bandwidth |  |

| X-bus.<br>chip-to-chip<br>link | 3                    | 3x 8B<br>drive/<br>8B<br>receive | 4.8 Gb/s<br>single-ended    | 230 GB/s         | 3                    | 3x 4B<br>drive/<br>4B receive | 16 Gb/s<br>differential      | 384 GB/s         |  |

| DMI<br>memory<br>link          | 8                    | 8x 1B<br>drive/<br>2B<br>receive | 9.6 Gb/s<br>differential    | 230 GB/s         | 8                    | 8x 1B<br>drive/<br>2B receive | 9.6 Gb/s<br>differential     | 230 GB/s         |  |

| A-bus<br>SMP link              | 3                    | 3x 2B<br>drive/<br>2B<br>receive | 6.4 Gb/s<br>differential    | 76 GB/s          | 4                    | 4x 2B<br>drive/<br>2B receive | 25 Gb/s<br>differential      | 400 GB/s         |  |

| PCIe                           | 2<br>Gen3            | 2x 2B<br>drive/<br>2B<br>receive | Gen3 8 Gb/s<br>differential | 64 GB/s          | 3<br>Gen4            | 3x 2B<br>drive/<br>2B receive | Gen4 16 Gb/s<br>differential | 192 GB/s         |  |

| Total<br>bandwidth             | 600GB/s              |                                  |                             |                  |                      | 1,2                           | 06 GB/s                      |                  |  |

S. Chun et al., "IBM POWER9 package technology and design," in IBM Journal of Research and Development, vol. 62, no. 4/5, pp. 12:1-12:10, 1 July-Sept. 2018, doi: 10.1147/JRD.2018.2847178.

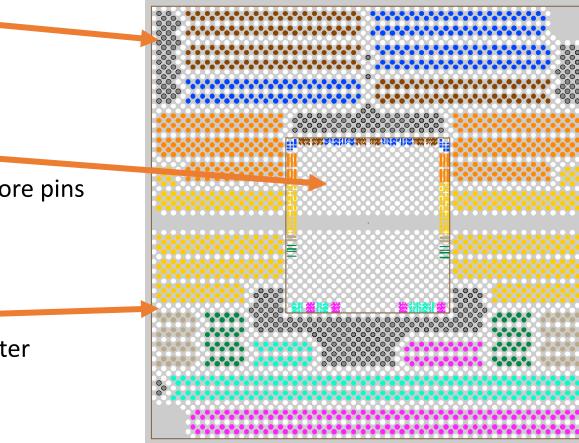

# Socket Pin Assignment

- Signal Pins

- More pins = more bandwidth

- Power Pins

- Lower voltage levels require more pins due to higher current

- Reference Pins

- Higher frequencies require better isolation between signal pins

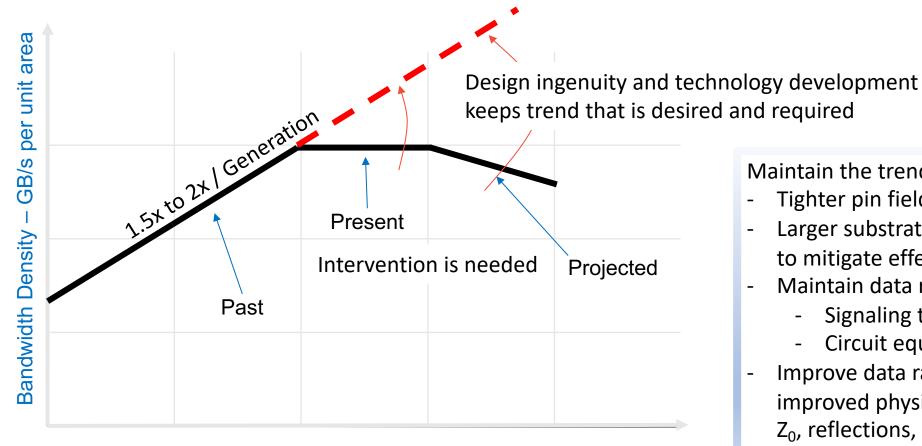

#### Reaching a bandwidth breakpoint at the socket level

#### Date of Introduction

Maintain the trend

- Tighter pin field pitch more contacts

- Larger substrates more contacts to mitigate effect

- Maintain data rate growth with -

- Signaling technology

- Circuit equalization

- Improve data rate capability with improved physical structures for Z<sub>0</sub>, reflections, and crosstalk

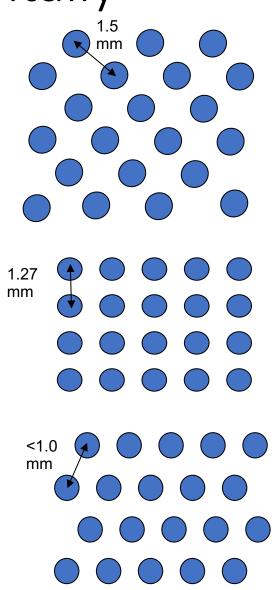

### Pin Density Increases Incrementally

- Over 20 years

- 1.5 mm min pitch interstitial

- 50 mil (1.27 mm) square

- 1 mm square

- 1 mm min pitch hexagonal

- <1.0 mm min pitch hexagonal

- Sockets are pin limited

- Crosstalk needs to be managed

- Reflections need to be minimized

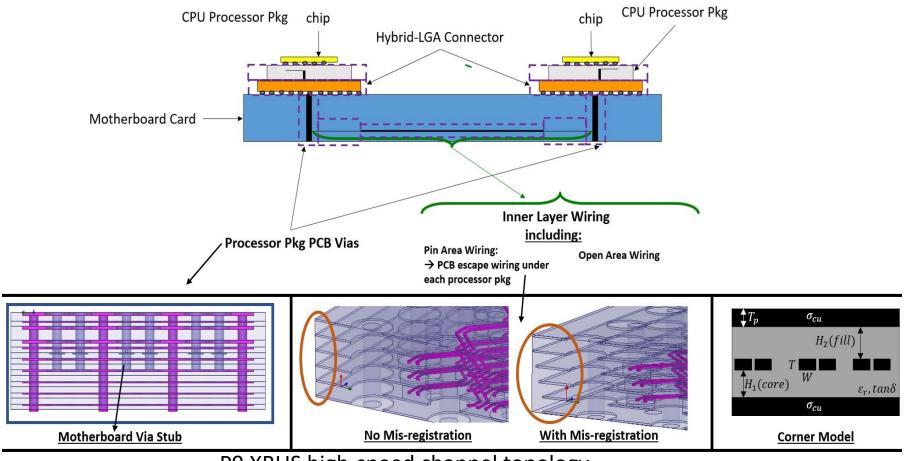

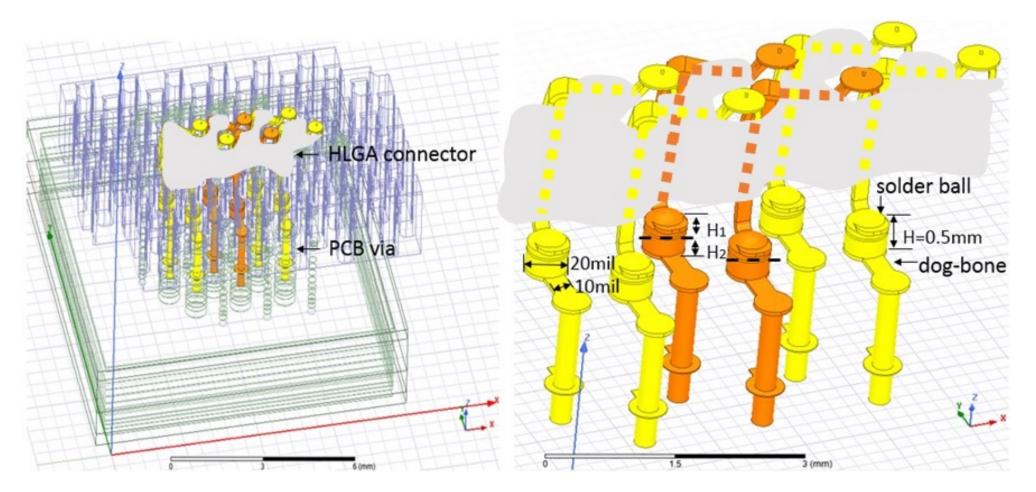

## Components of a channel with hLGA

P9 XBUS high-speed channel topology

M. Swaminathan, H. M. Torun, H. Yu, J. A. Hejase and W. D. Becker, "Demystifying Machine Learning for Signal and Power Integrity Problems in Packaging," in IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 10, no. 8, pp. 1276-1

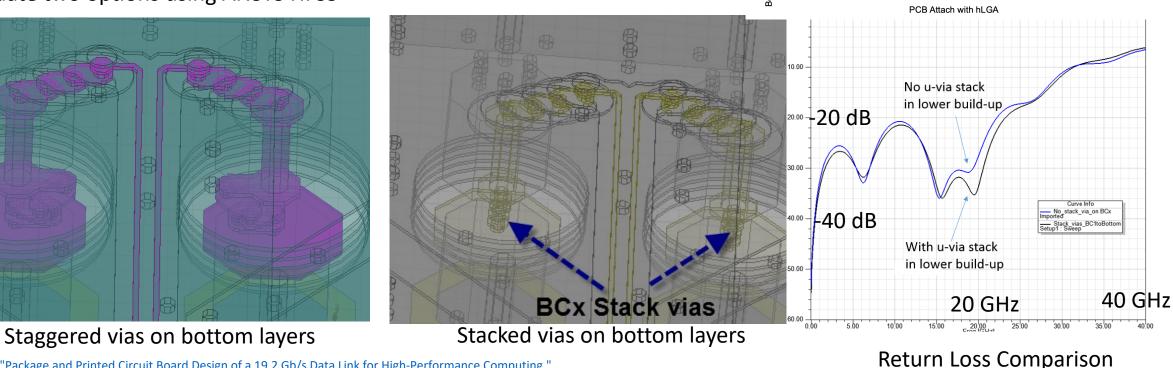

### Package Design for Signal Integrity – PTH to BGA/LGA Pads

- Maximize signal bandwidth while meeting mechanical reliability requirements (Benefit of Stacked Vias on Bandwidth)

- Evaluate two options using ANSYS HFSS

S. Chun et al., "Package and Printed Circuit Board Design of a 19.2 Gb/s Data Link for High-Performance Computing," 2017 IEEE 67th Electronic Components and Technology Conference (ECTC), 2017, pp. 1701-1707, doi: 10.1109/ECTC.2017.170. RFP

200 µm

Substrate - 2000 µm

Chip Attach with C4s

Core 200 μπ

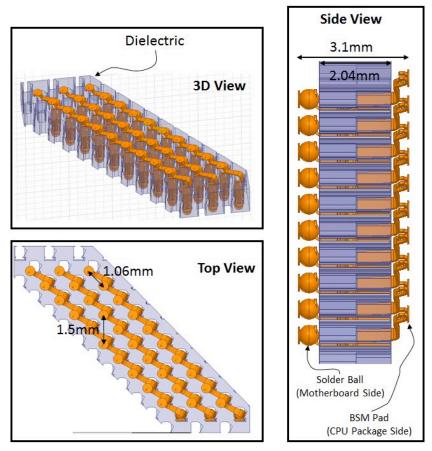

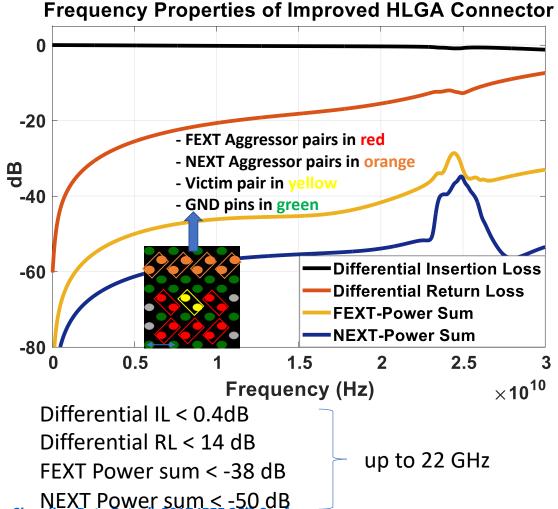

### HLGA Socket Connector Design and Performance

Views of a sample HLGA connector section\* (for illustrative purposes only):

- J.A. Hejase et al., "A Hybrid Land Grid Array Socket Connector Design for Achieving Higher Signaling Data Rates", 2017 IEEE 26<sup>th</sup> Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), San Jose, CA, 2017, pp. 1-3.

- P. R. Paladhi et al., "SI Model to Hardware Correlation on a 44 Gb/s HLGA Socket Connector," 2020 IEEE 29th Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), 2020, pp. 1-3, doi: 10.1109/EPEPS48591.2020.9231393.

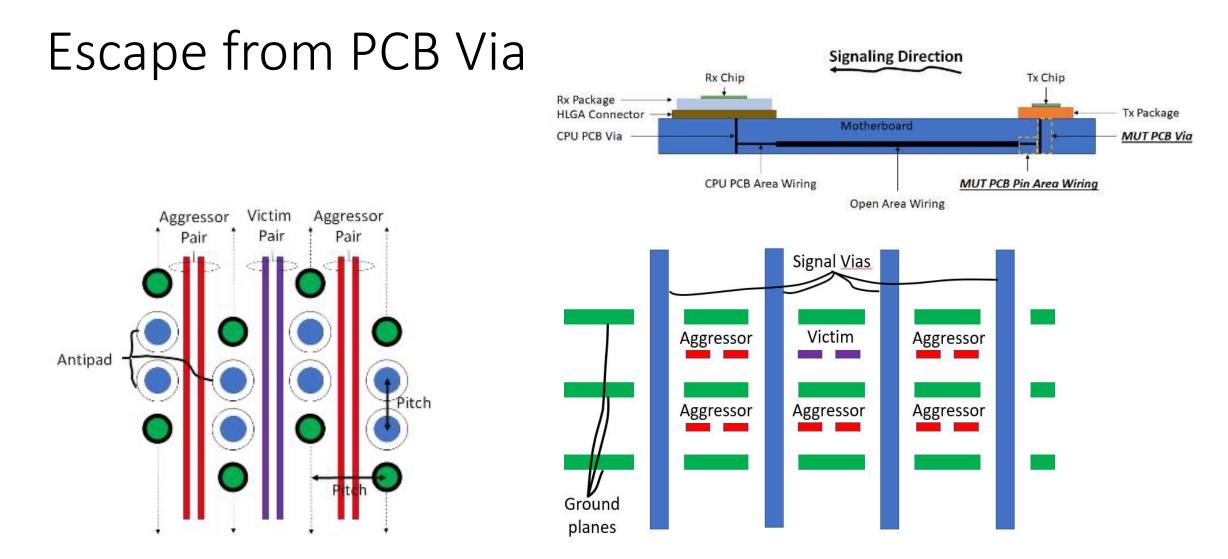

### Socket Connector Routing to PCB Via

Y. Zhang, J. A. Hejase, J. C. Myers, J. J. Audet, W. D. Becker and D. M. Dreps, "3D Electromagnetic Modelling of Connector to PCB Via Transitions," 2018 IEEE 27th Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), 2018, pp. 99-101, doi: 10.1109/EPEPS.2018.8534304.

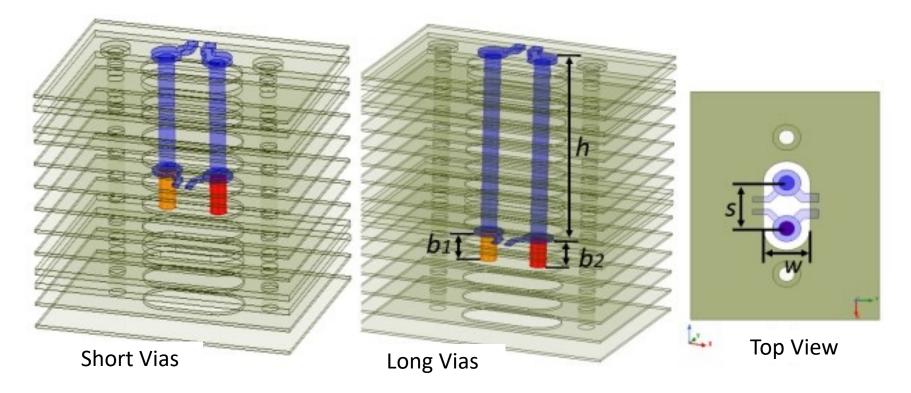

### PCB Via Stub Control

Y. Zhang, M. Bohra, N. Pham, P. R. Paladhi, W. D. Becker and D. M. Dreps, "Signal Integrity Characterization of Channels With Asymmetric Via Stubs," 2020 IEEE 29th Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), 2020, pp. 1-3, doi: 10.1109/EPEPS48591.2020.9231479.

J. C. Myers, J. A. Hejase, J. Tang, S. Chun, W. D. Becker and D. M. Dreps, "Signal Integrity Considerations of PCB Wiring in Tightly Pitched Module Pin Fields of High Speed Channels," 2019 IEEE 28th Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), 2019, pp. 1-3, doi: 10.1109/EPEPS47316.2019.193216.

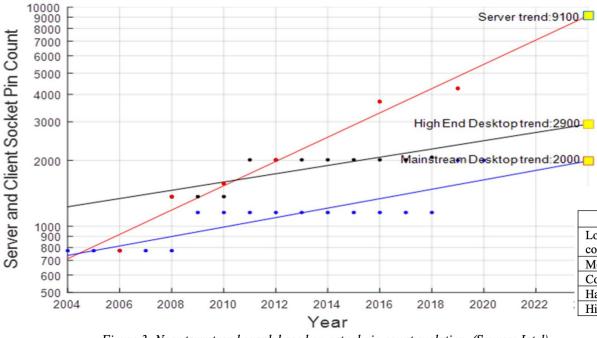

# Socket Pin Projections

Figure 3: Near term trend graph based on actual pin count evolution. (Source: Intel)

#### Link to Chapter 22:

https://eps.ieee.org/images/files/HIR 2021/ch22 2D-3D.pdf

- My Observations

- Projected number of socket pins have grown dramatically in the last 5 years

- Highlight 2025 projection below

- Opportunity

- top of substrate escape

- co-packaged optics

- Socket size will increase

- Adds to cooling challenge

Table 2a: Socket pin count projections from 2015 ITRS. [21]

|   |                               | 2019 | 2020 | 2021 | 2022 | 2023 | 2024 | 2025 | 2026 | 2027 | 2028   | 2029 | 2030 |

|---|-------------------------------|------|------|------|------|------|------|------|------|------|--------|------|------|

|   | Low-end, Low-<br>cost package | 550  | 550  | 550  | 600  | 600  | 600  | 600  | 600  | 650  | 650    | 650  | 650  |

|   | Memory (MCP)                  | 260  | 280  | 280  | 280  | 280  | 280  | 280  | 280  | 280  | 280    | 280  | 280  |

|   | Cost-performance              | 3200 | 3300 | 3400 | 3500 | 3600 | 3700 | 3800 | 3900 | 4000 | 4100   | 4200 | 4300 |

| _ | Harsh                         | 693  | 728  | 764  | 803  | 843  | 860  | 0//  | 894  | 911  | 928    | 945  | 962  |

| 1 | High performance              | 5394 | 5651 | 5934 | 6231 | 6543 | 6855 | 7167 | 479  | 7791 | 8103 □ | 8415 | 8727 |

Table 2b: Updated projections for socket pin count in the Cost-Performance and High-Performance segments.

|                  | 2019 | 2020 | 2021 | 2022 | 2025 | 2028  | 2031  | 2034  |

|------------------|------|------|------|------|------|-------|-------|-------|

| Cost performance | 3200 | 3300 | 3400 | 3500 | 3800 | 4100  | 4400  | 4700  |

| High performance | 5125 | 5694 | 6302 | 6946 | 9105 | 11601 | 14434 | 17604 |

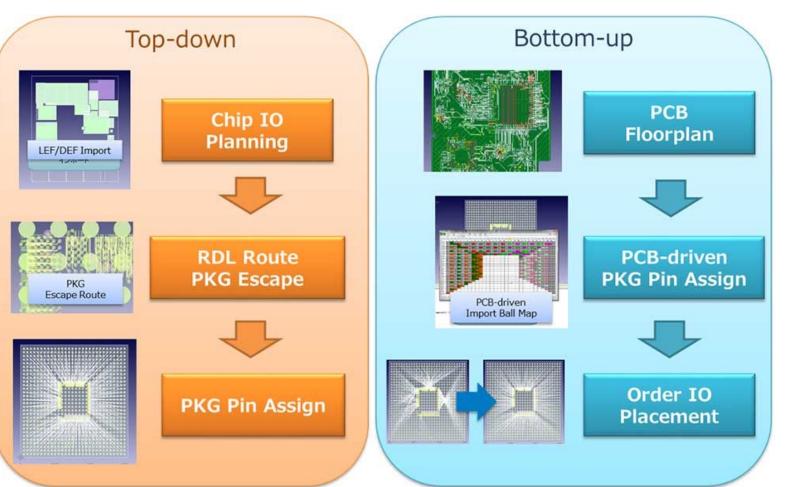

# **Co-Design Flow**

#### VERTICAL

Bridge IC, Package, Board Bridge System, Architecture, Layout Bridge Synthesis, Analysis, Verification Bridge Hardware, Software, Firmware

#### HORIZONTAL

Energy aware Signal/power integrity aware Stress/thermal aware

Security aware

Testing aware

Link to chapter 13:

https://eps.ieee.org/images/files/HIR\_2021/ch13\_co-d.pdf

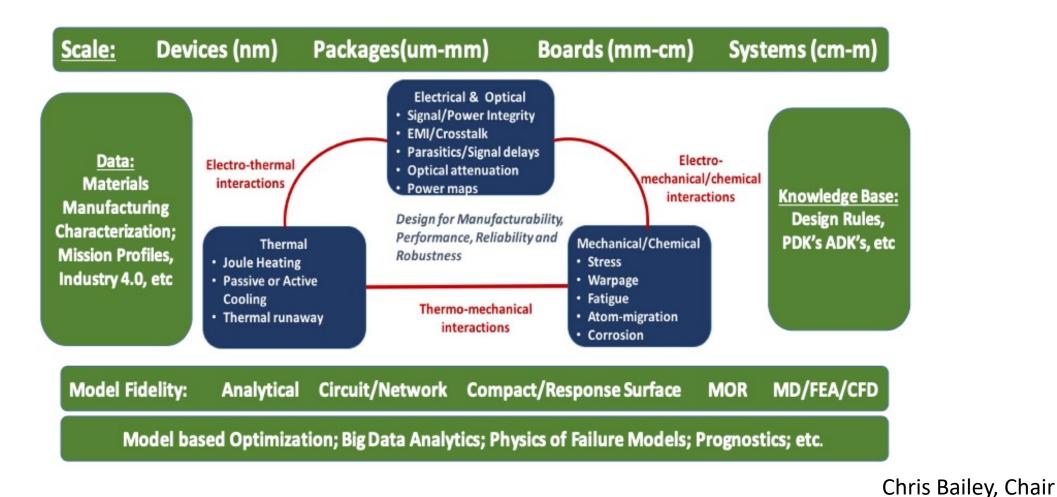

# Modeling and Simulation

Link to chapter: <u>https://eps.ieee.org/images/files/HIR\_2021/ch14\_ms.pdf</u>

CENTER PROPRIETARY

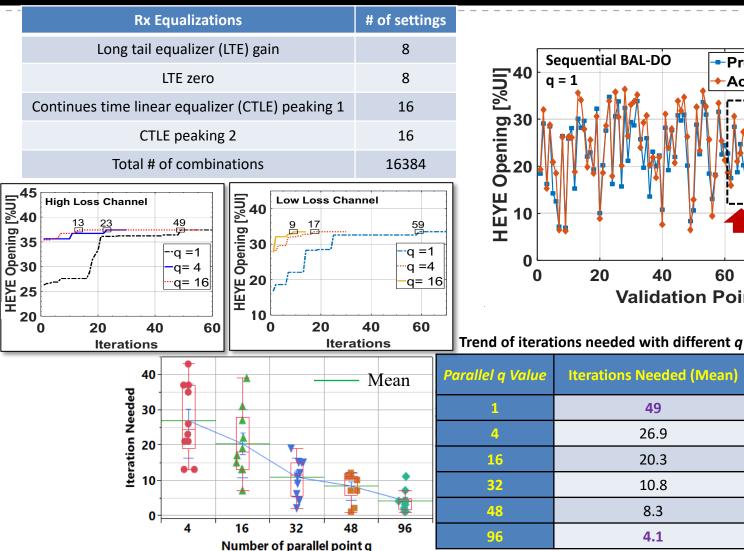

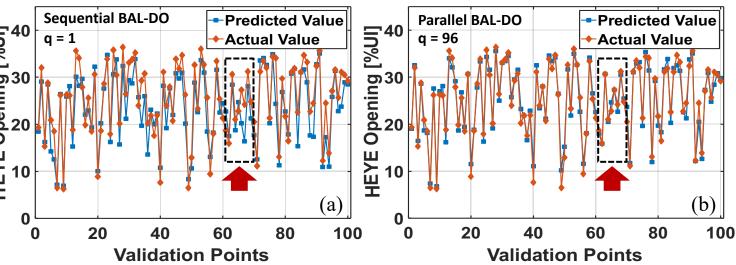

#### **Parallel BAL-DO for RX Equalization**

Optimization-Results "Parallel Bayesian Active Learning using Dropout for Optimizing High-Speed Channel Equalization," 2021 IEEE 30th Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), 2021, pp. 1-3, doi: 10.1109/EPEPS51341.2021.9609205.

**Uncertainty Prediction**

|                           | <i>q</i> =1 | <i>q</i> =16 | <b>q</b> =96 |

|---------------------------|-------------|--------------|--------------|

| Data from iteration       | 52          | 16           | 7            |

| Mean of absolute error    | 2.92 %UI    | 1.83 %UI     | 1.10 %UI     |

| Std dev of absolute error | 2.39 %UI    | 1.55 %UI     | 0.94 %UI     |

go.illinois.edu/caeml

# Opportunity for you - The HIR Chapters

| Chapter 1 Overview                  | Chapter 2 High Performance<br>Computing | Chapter 4 Medical          | Chapter 5 Automotive     |

|-------------------------------------|-----------------------------------------|----------------------------|--------------------------|

| Chapter 6 Aerospace &<br>Defense    | Chapter 7 Mobile                        | Chapter 8 Single & Multi C | hip Chapter 9 Photonics  |

| Chapter 11 MEMS                     | Chapter 12 5G                           | Chapter 13 Co Design       | Chapter 14 Simulation    |

| Chapter 15 Materials                | Chapter 16 Emerging Devices             | Chapter 17 Test            | Chapter 18 Supply Chain  |

| Chapter 19 Security                 | Chapter 20 Thermal                      | Chapter 21 SiP and Module  | Chapter 22 Interconnects |

| Chapter 23 Wafer Level<br>Packaging | <u>https://</u>                         | eps.ieee.org/hir           |                          |

### Participate - IEEE Technical Committee on EDMS

EDMS = Electrical Design, Modeling, and Simulation https://cmte.ieee.org/eps-edms/

- To join the Technical Committee

- Send email to EDMS-Chair@ieee.org

- Annual Conferences

- SPI Europe, May

- EPEPS North America, October

- EDAPS Asia, December

- DTMES Africa It's great to see this started

- Benchmark Subcommittee

- Provide benchmark designs for methodology development

- Distinguished Lecturers available

- See web site for more details

### Summary

- Fundamentals of Electrical Design

- <u>Input</u>: Physical parameters -> electrical models

- Signal Distribution and Power Distribution are inter-related and inter-dependent

- Advances in semiconductor technology drive system advances

- Engineering ingenuity to minimize noise and reflections creates differentiated systems

- <u>Output</u>: Verified design, build data, performance analysis, test patterns

- Engineering ingenuity

- Cost-efficient design and trade-offs levering and driving technology development

- Example Processor Socket with hybrid Land Grid Array (hLGA)

- Bandwidth density increase of 1.5x to 2x per processor generation drives innovation

- Heterogeneous Integration of Packaging and the HIR Roadmap

- Opportunity to apply design ingenuity to technology advances

- How you can get involved, learn, and give back to the community

- HIR Heterogeneous Integration Roadmap

- IEEE EPS Society and the Technical Committee on Design, Modeling, and Simulation (EDMS)