# "Optimization of Electrical Package Design and PCB Design for CSP Age"

Atsushi Nakamura

Assembly Technology Development Dept., SIC, Hitachi, Ltd., JAPAN

Oct. 2002

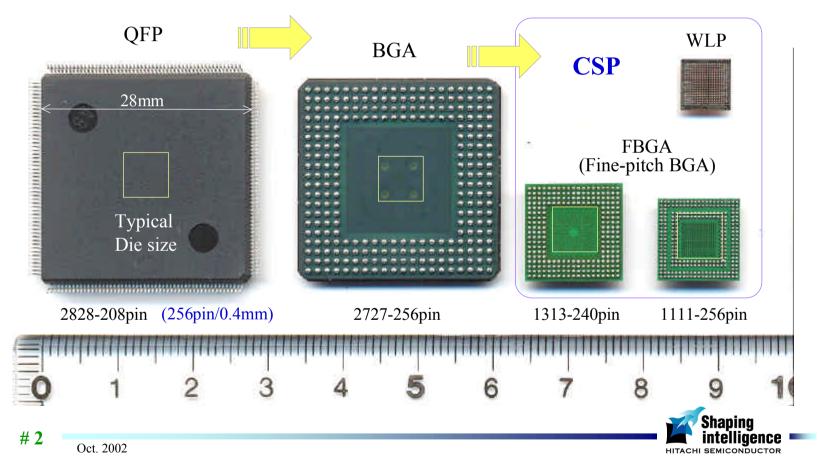

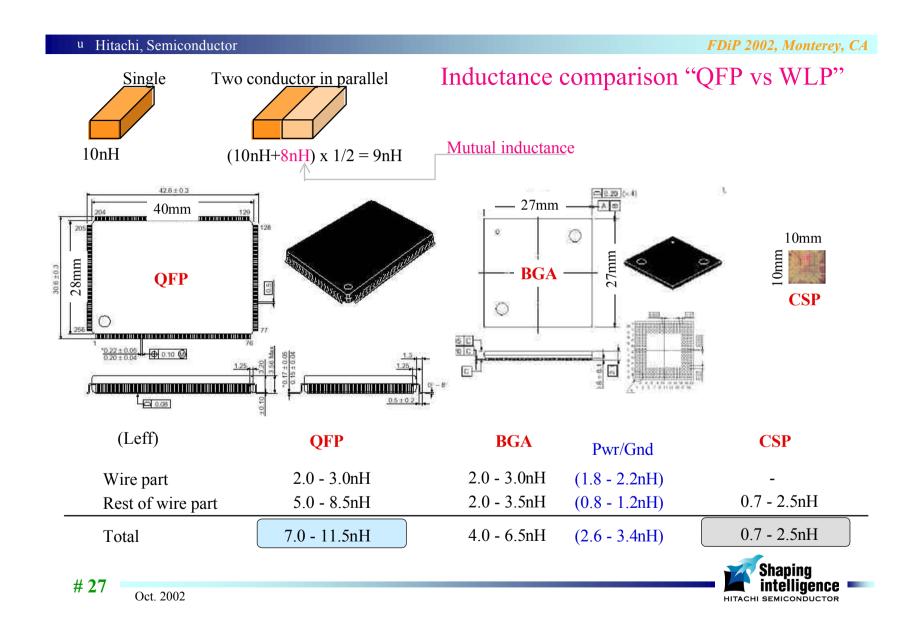

## Package Miniaturization (QFP > BGA > CSP)

MPU for consumer products has been shaping up his body smaller and smaller

HITACHI SEMICONDUCTOR

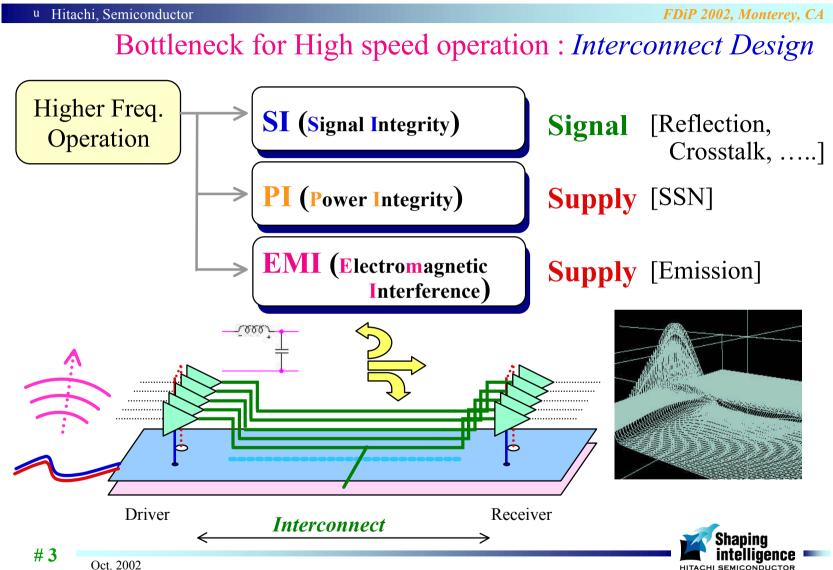

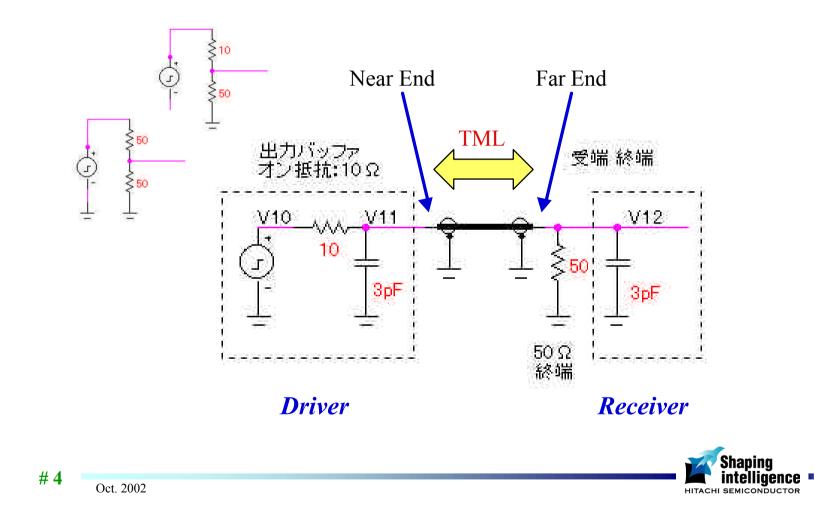

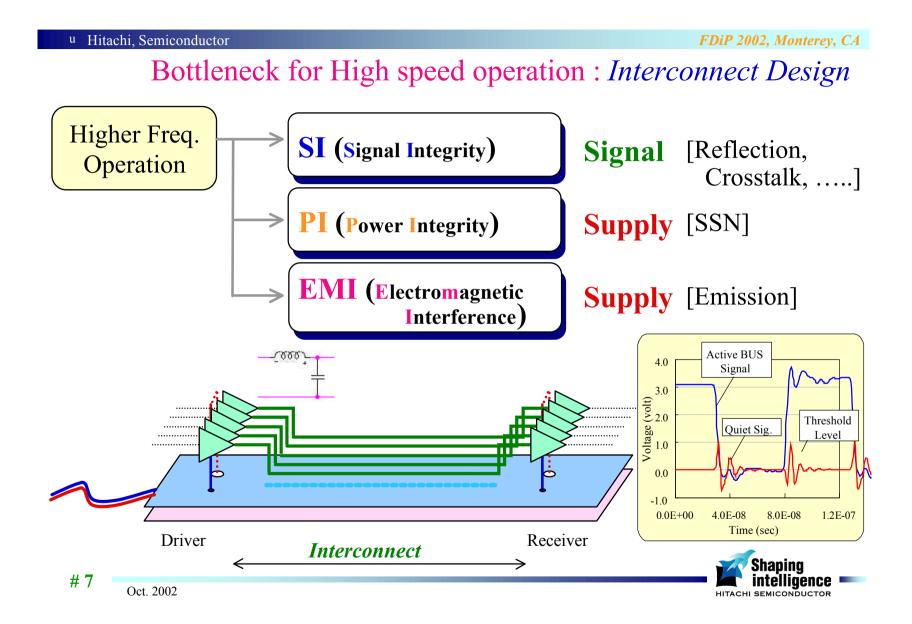

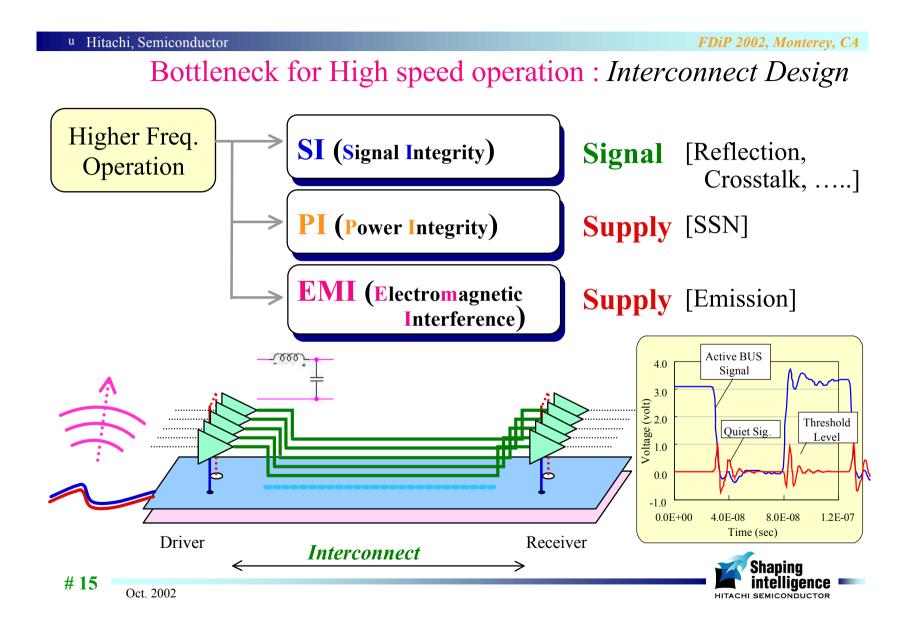

Impedance matching at Driver/TML and TML/Receiver

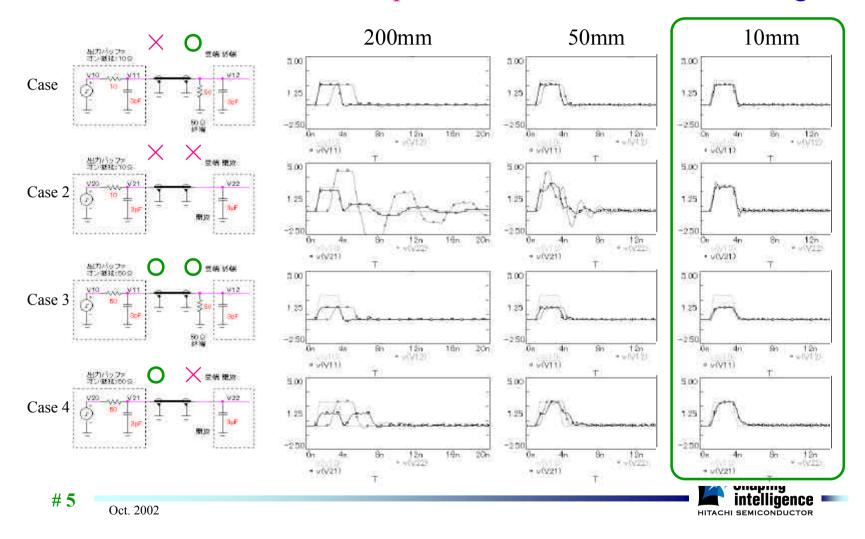

Waveform comparison on Termination, TML length

#### The FDiP 2002, Monterey, CA Miniaturization in Digital Consumer Products

# 6 Oct. 2002

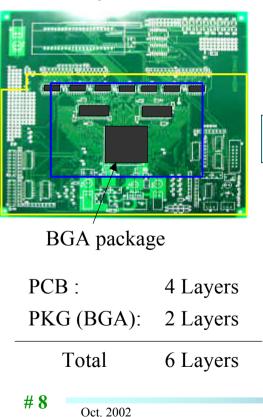

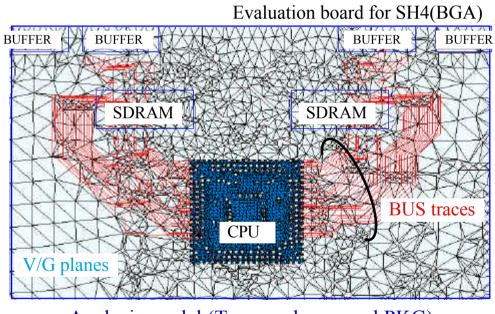

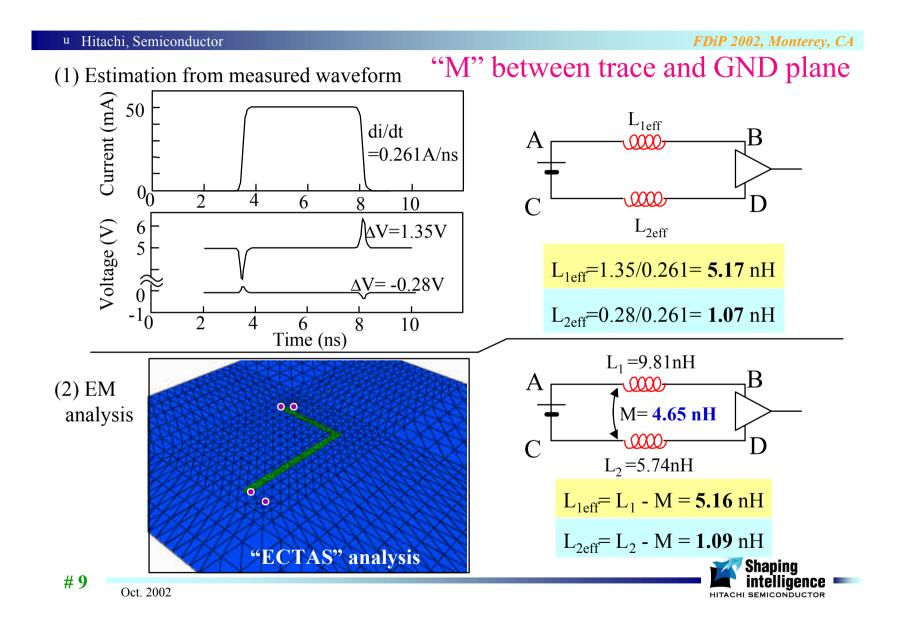

### PCB Modeling for Power Integrity Analysis

Analysis Vehicle

LSI Package, BUS traces and V/G plane conductors in PCB should be analyzed in a single model for field solver.

Analysis model (Traces, planes, and PKG)

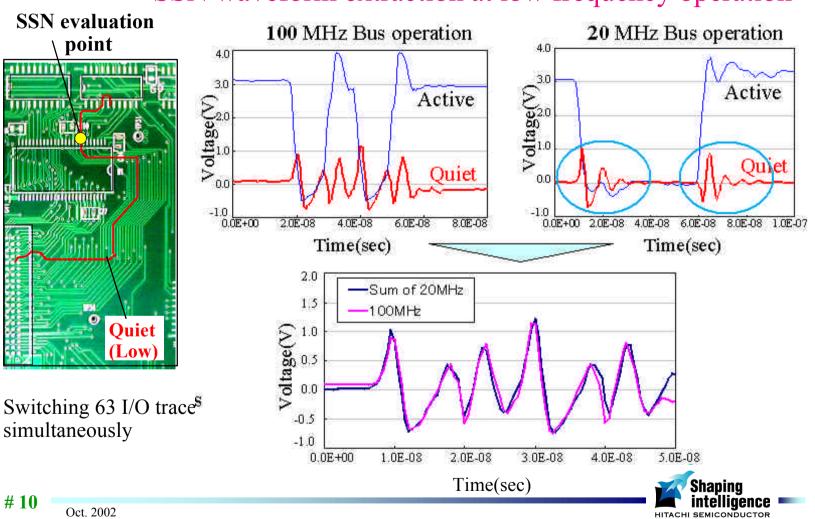

SSN waveform extraction at low frequency operation

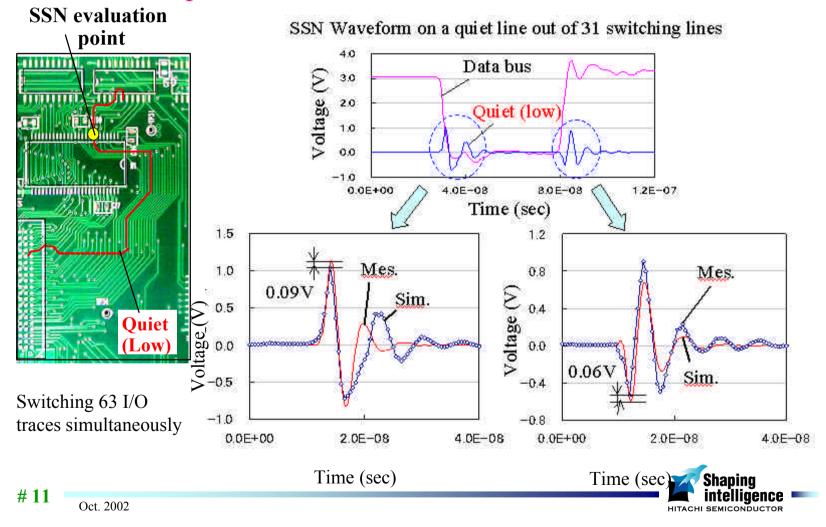

#### Comparison between measured and simulated waveform

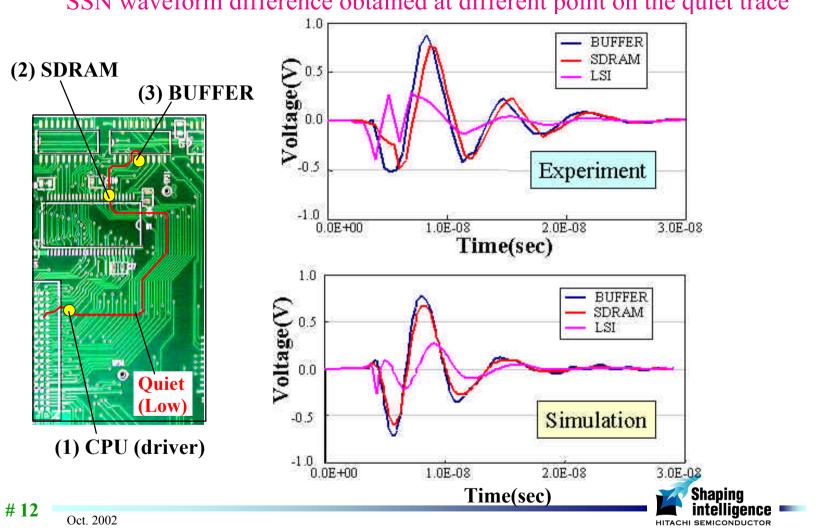

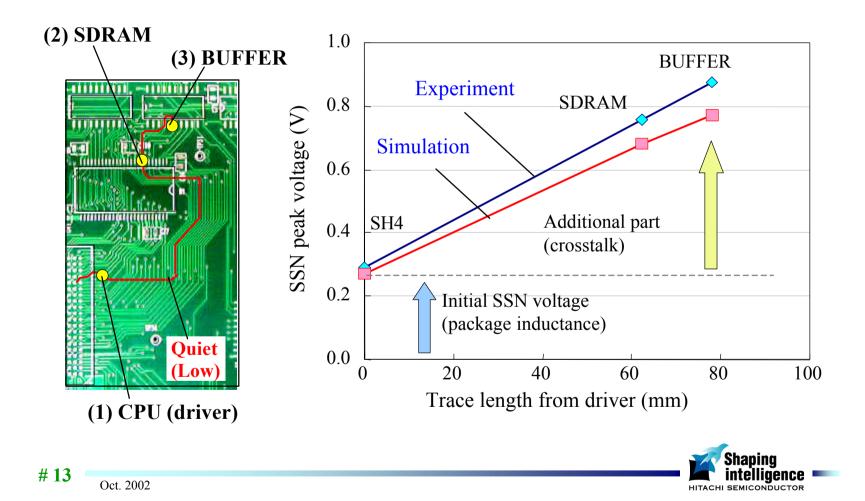

SSN waveform difference obtained at different point on the quiet trace

### Peak voltage increase proportional to trace length

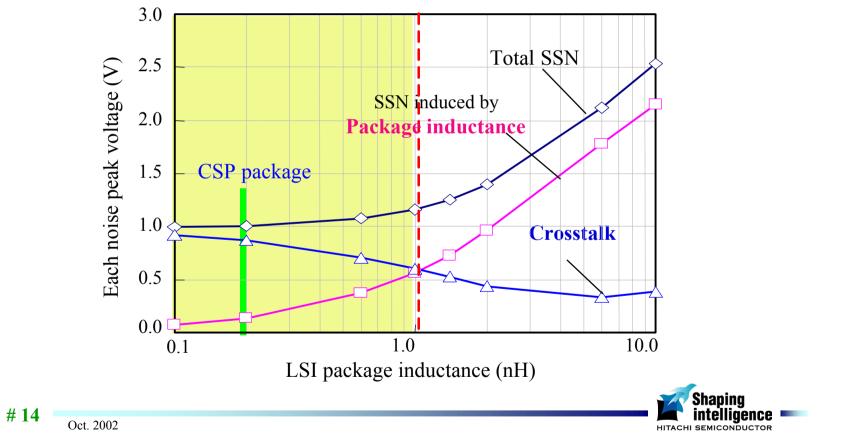

### Package dominant and PCB dominant region

Cross talk part is dominant on BUS system using low inductance packages (Less than 1nH)

FDiP 2002, Monterey, CA

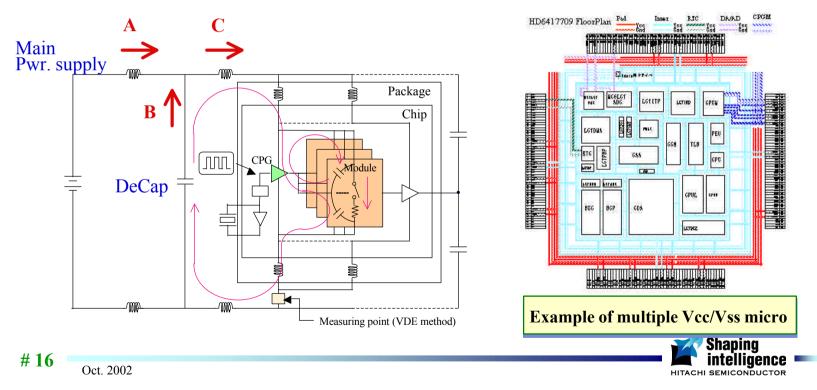

### Low noise assembly Basics

- ☐ Minimize voltage fluctuation around CPU by Supply decoupling

- □ Increase current supply from DeCap (B) and decrease current from main Power supply (A)

- Current ratio A/C represents effectiveness of DeCaps

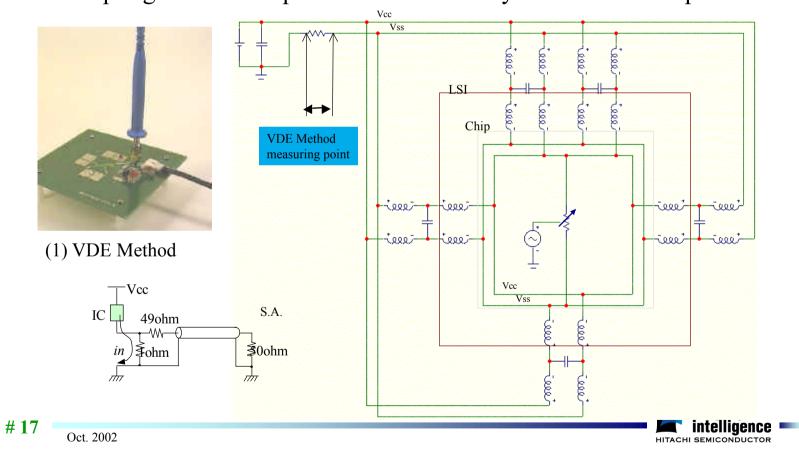

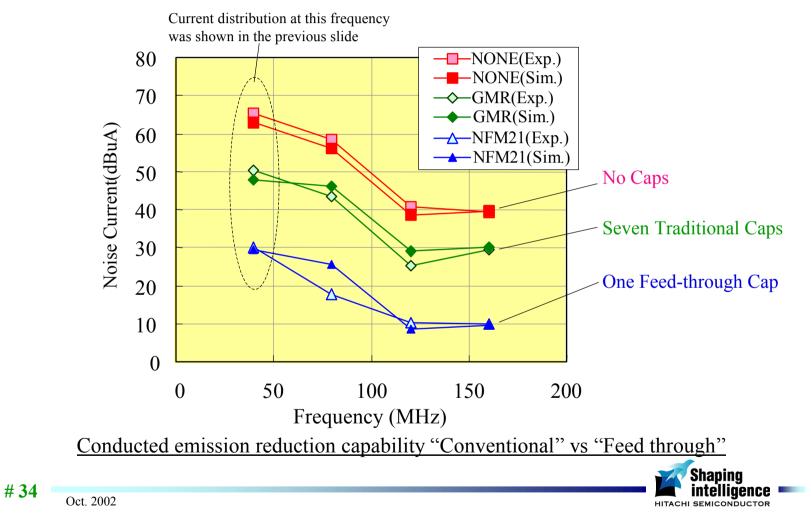

#### Noise current measurement

Noise current can be measured by 1 ohm (VDE) probe

Decoupling effect of Caps can be evaluated by w/ and w/o comparison

FDiP 2002, Monterey, CA

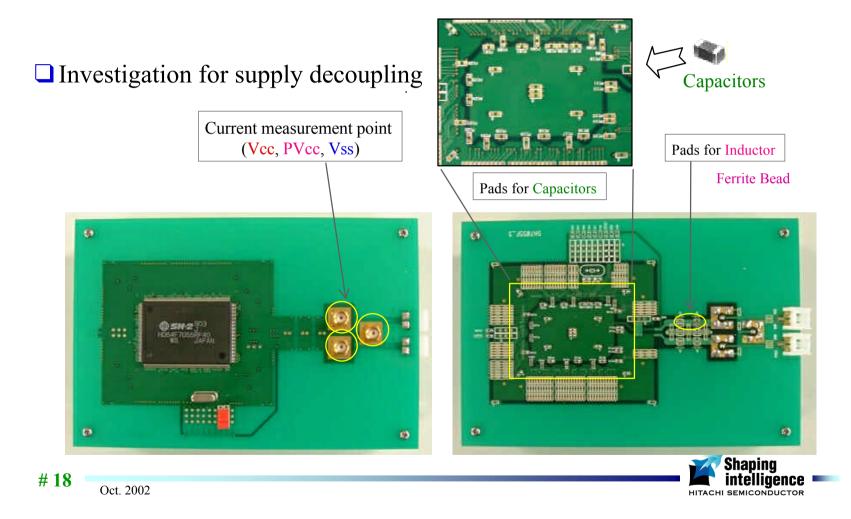

## Decoupling evaluation board

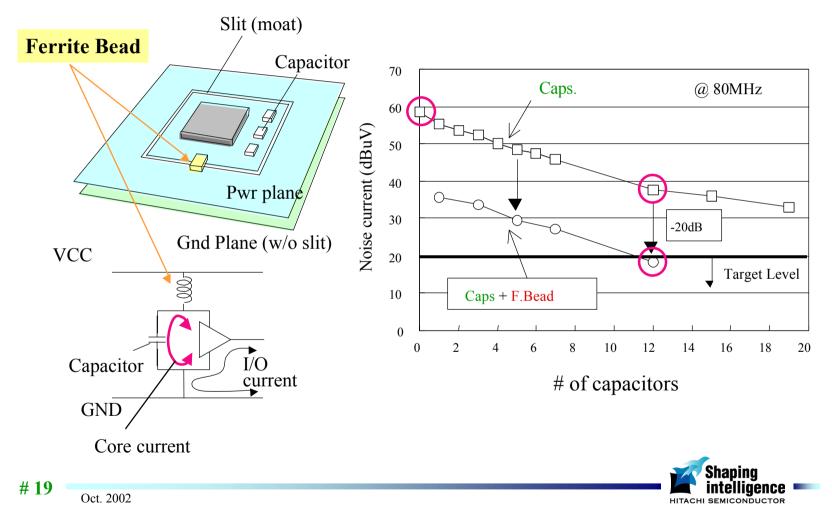

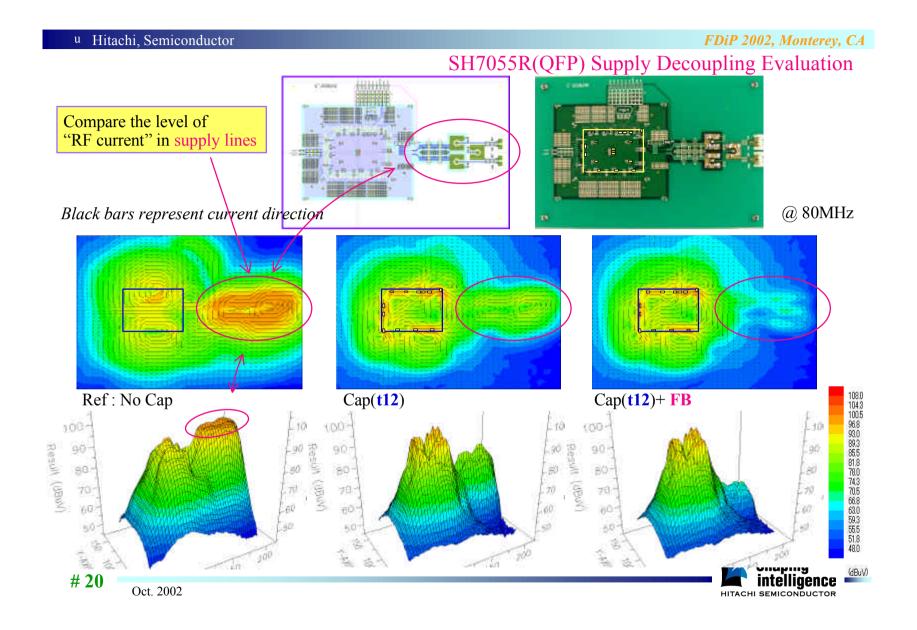

## Supply Decoupling using Ferrite-Bead

FDiP 2002, Monterey, CA

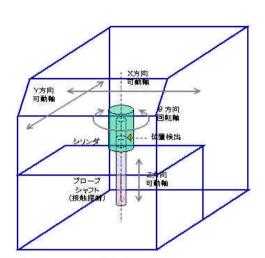

Four-axis Near Field Scanner

EMV-200

NF-probe Scanner system

□ Scan area : 300x300mm

http://www.hitachi.co.jp/HDEV/products/production/emi2/

- 3

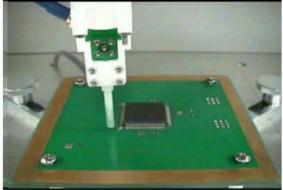

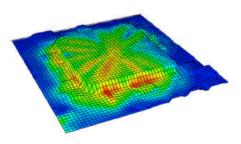

Example of "Surface scanning

# 21 Oct. 2002

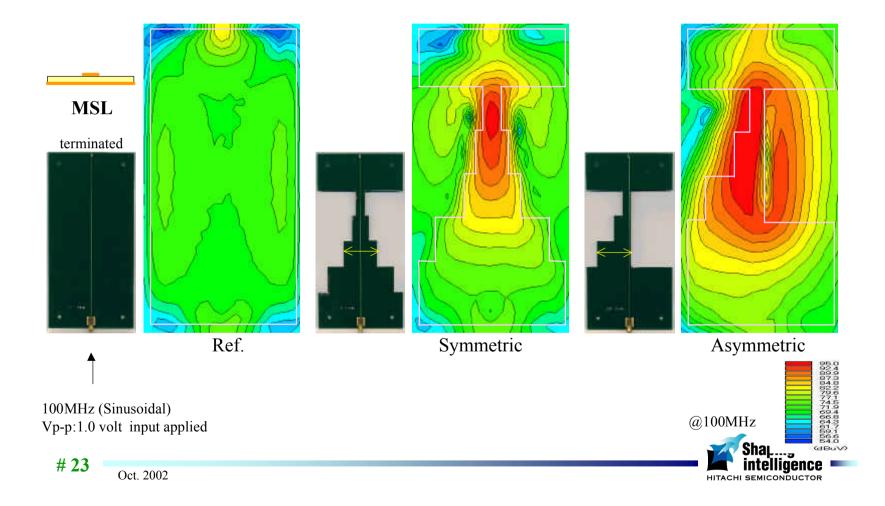

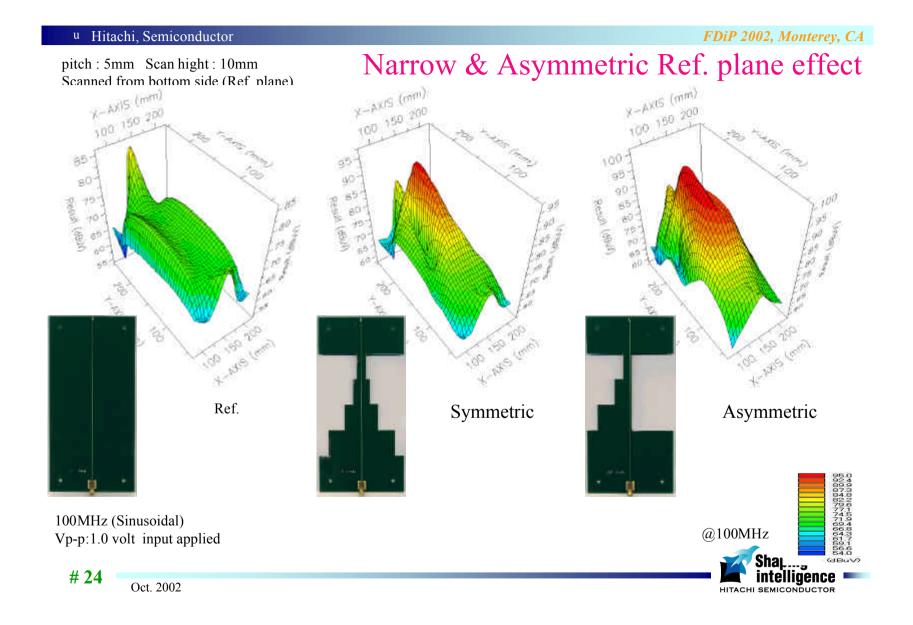

### Narrow & Asymmetric Ref. plane effect

FDiP 2002, Monterey, CA

pitch : 5mm Scan hight : 10mm Scanned from bottom side (Ref. plane)

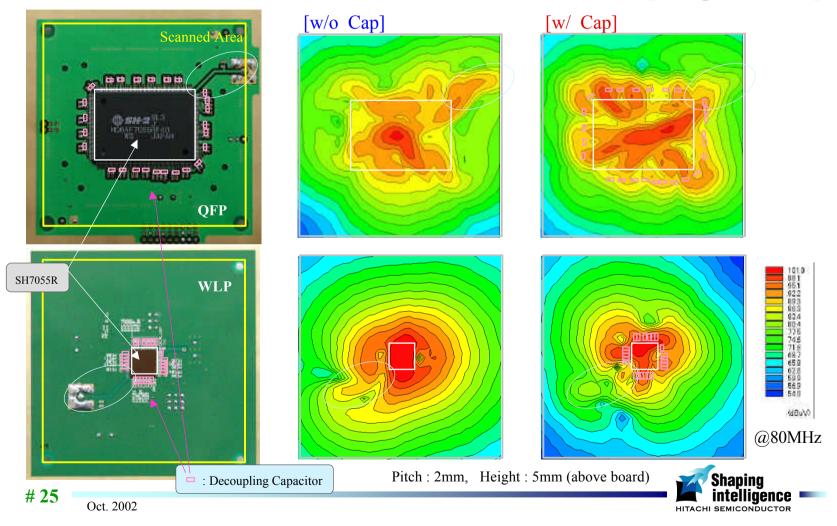

"QFP vs WLP" Current distribution [ NF-probe scan]

SH7055R

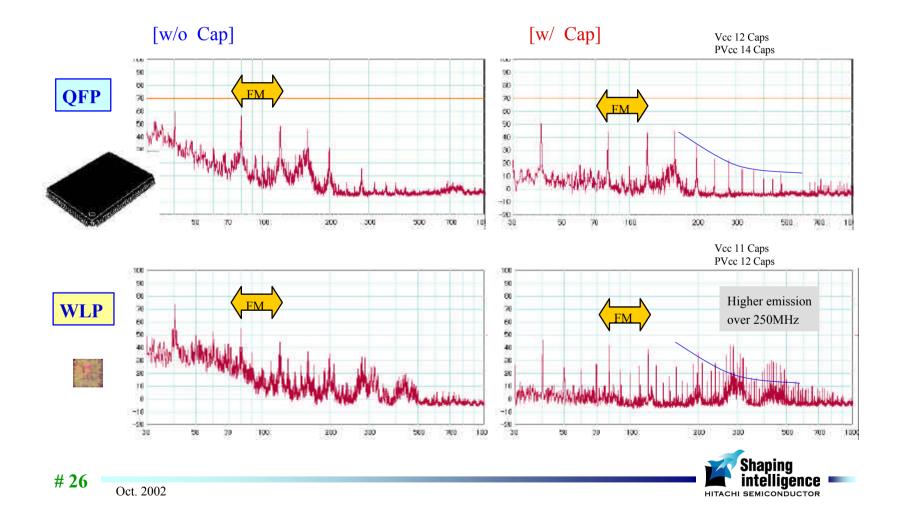

Conducted emission "QFP vs WLP" [VDE method]

FDiP 2002, Monterey, CA

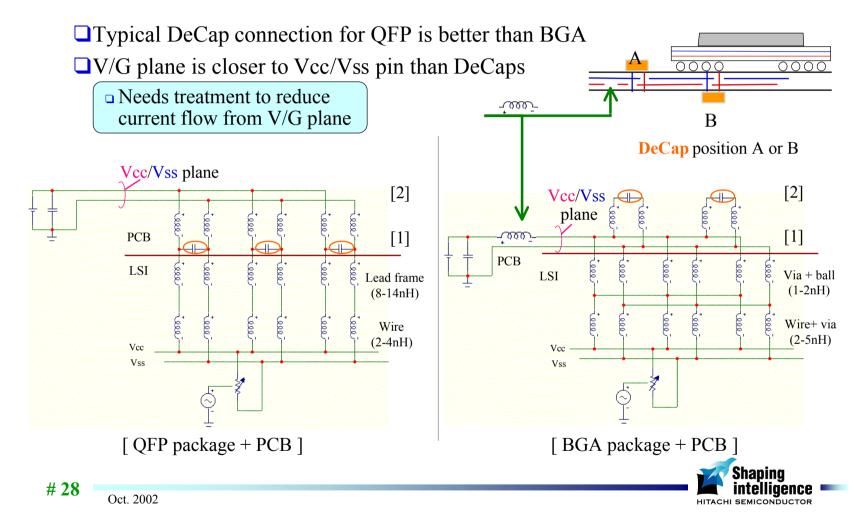

### Decoupling Capacitor connection [QFP vs BGA]

#### FDiP 2002, Monterey, CA

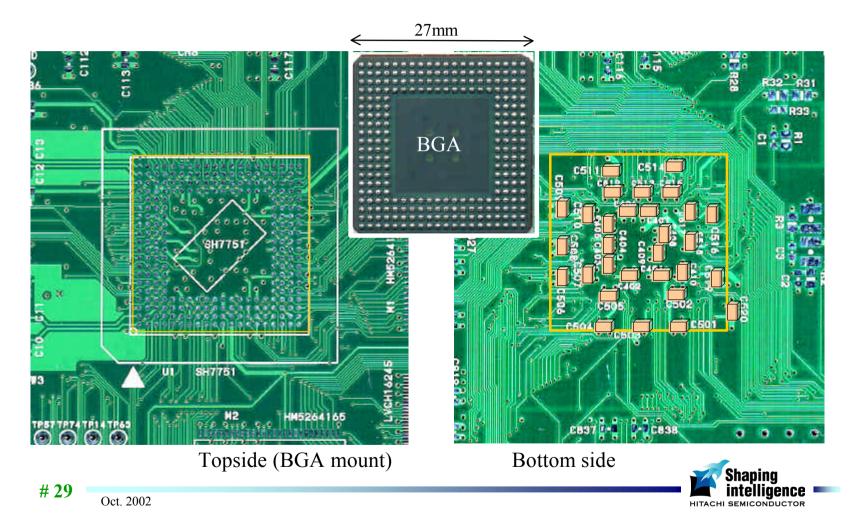

### Decoupling capacitors for BGA

#### FDiP 2002, Monterey, CA

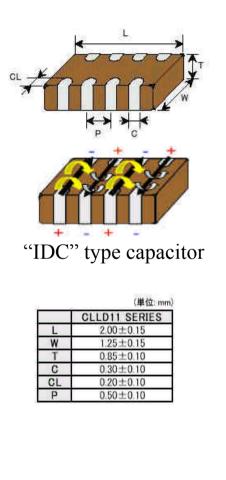

### Cost effective Low ESL Capacitors

-20%

80%

2A

16Vdc

500M ohm min.

0.03ohm

-40°C

85°C

2.0mm

1.25mm

0.85mm

Lower Tolerance

Upper Tolerance

Insulation Resistance

Max. of DC resistance

Min. of Operating Temp.

Max. of Operating Temp.

Withstand Voltage

Rated Current

Rated Voltage

Length

Width

Thickness

100% supply must be fed through

Oct. 2002

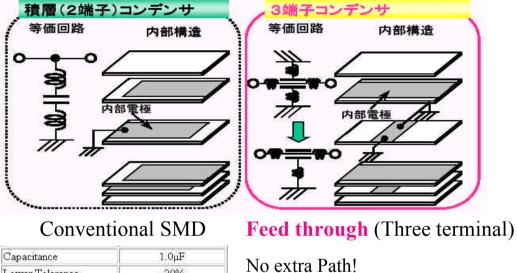

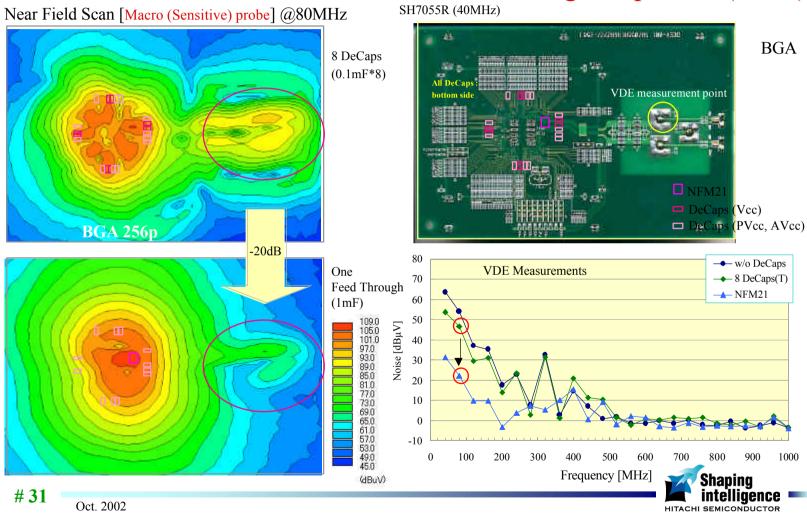

### Feed through Capacitor (BGA)

FDiP 2002, Monterey, CA

#### <sup>u</sup> Hitachi, Semiconductor FDiP 2002, Monterey, CA Feed through Capacitor (QFP) SH7055R (40MHz) Near Field Scan [Macro (Sensitive) probe] @80MHz STUSSOUNS 10 **OFP** 12 DeCaps (0.1mF\*12) VDE measurement point □ NFM21 DeCaps (Vcc) DeCaps (PVcc, AVcc) **QFP 256p** -20dB 80 **VDE** Measurements One → 12 DeCaps 70 Feed Through → NFM21 (1mF) 60 50 Noise [dBµV] Noise [dBµV] Noise 20 20 10 0 -10 100 200 400 500 900 1000 300 600 800 0 700 Frequency [MHz] Shaping intelligence (dBuV) # 32 Oct. 2002

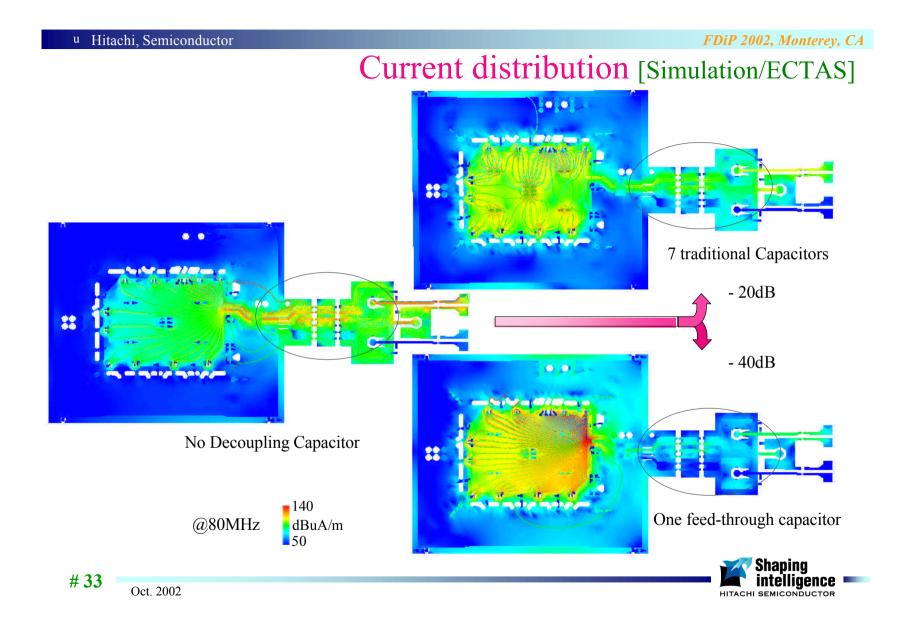

### Effectiveness of Feed-through capacitor [Exp. vs Sim.]

#### Radiation from External BUS

FDiP 2002, Monterey, CA

## Summary

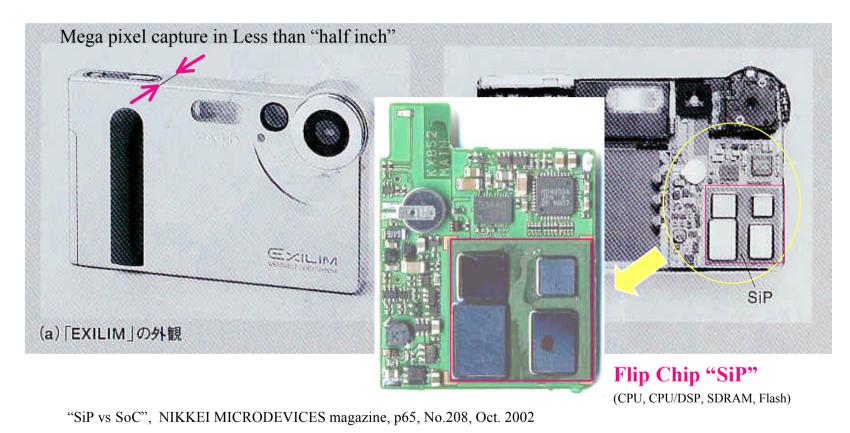

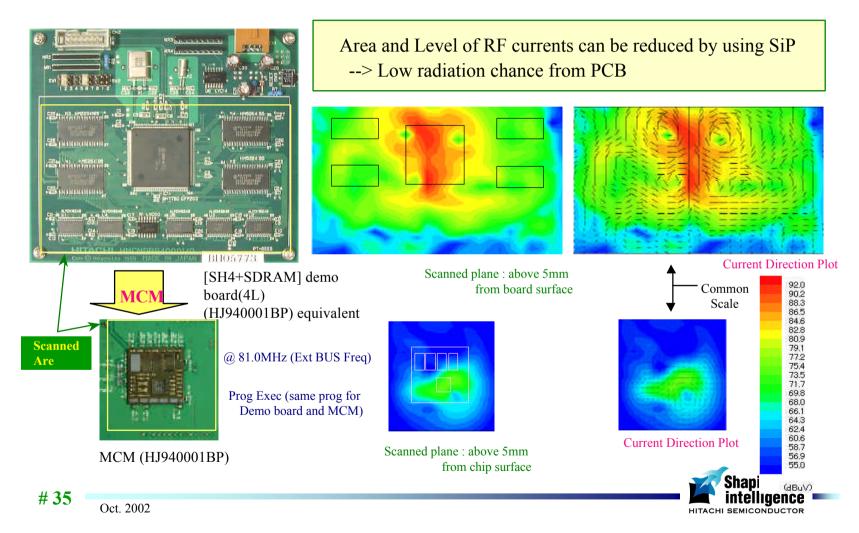

- Short trace interconnection (in SiP) solves most of the SI concern

- □ V/G plane analysis takes more important role for CSP age system

- Reduced EMI design is base on "Supply decoupling." (for Single chip MPU)

- □ NF-Scanner shows us locations generating "Common mode" current

- Direct connection to V/G plane for CSP (BGA) is not recommended

- □ Feed-through Capacitor is a good solution for CSP's decoupling saving space, great decoupling capability, making sense (cents)

- ❑ PCB design locating RF current trace adjacent to Gnd (return) path reduces emission. (ex. FC-SiP)