# **Full Chip Analysis**

Chung-Kuan Cheng Computer Science and Engineering Department University of California, San Diego La Jolla, CA 92093-0114 Kuan@cs.ucsd.edu

# **Outlines**

- I. Introduction

- **II. Circuit Level Analysis**

- III. Logic Level Analysis

- I. Timing Analysis

- **II. Functional Analysis**

- **IV. Mixed Signal Analysis**

- v. Research Directions

- vi. Conclusion

# I. Introduction

- 1. Trends of On-Chip Technologies

- 2. Statistics About Design Flaws

- 3. Spectrum of Analysis

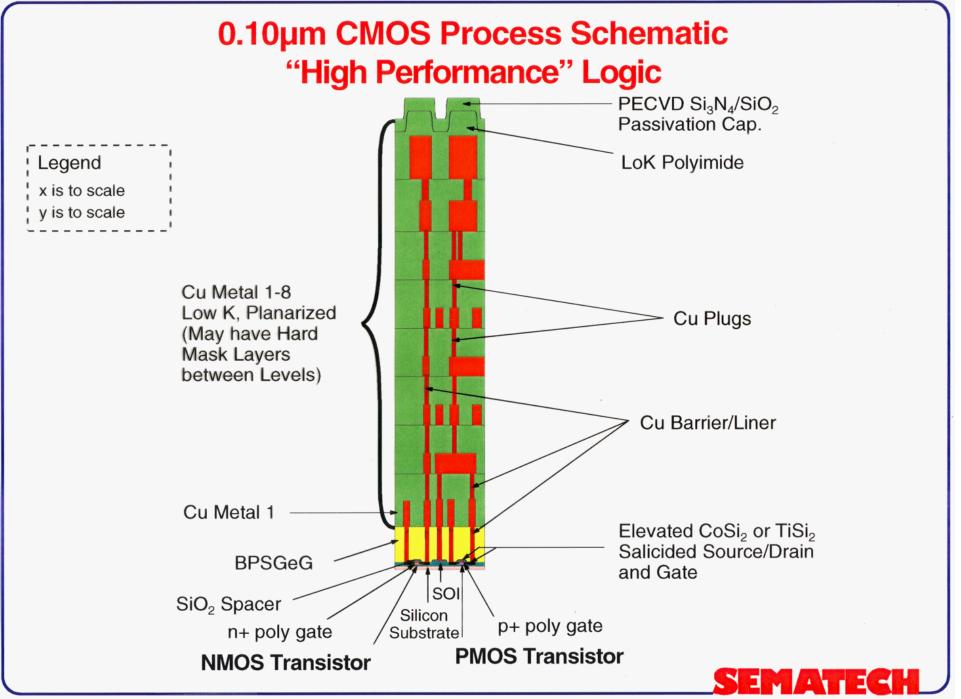

# **I.1 Trends of On-Chip Technologies**

System: Huge Numbers of Devices and Wires Power/Ground Distribution: Low Voltage, High Current Wires: Lateral Coupling, Fragmented Parasitics Devices: Modeling, Noise Mixed Signal Design: RF+Analog+Digital JRSDAY, JUNE 13, 2002 · USA TODAY

#### intel.com

# Will Moore's Law stand forever?

In 1965, Intel's Gordon Moore reated a "law" that became shortha for the rapid, unprecedented growth of technology. He predicted that the number of transistors on a chip would grow exponentiall

# to fulfill Moore's Law, year after year, companies everywhere can do more at lower cost. And that's not just a good law. It's very good business.

# **Power/Ground Distribution (ITRS)**

Lower V margin: Higher I & Inductance x Freq.

|                       | 2002  | 2003  | 2004  | 2005  |

|-----------------------|-------|-------|-------|-------|

| Supply<br>Voltage(V)  | 1.5   | 1.5   | 1.2   | 1.2   |

| Max<br>Power          | 130   | 140   | 150   | 160   |

| On-Chip<br>Freq(MHz)  | 1,600 | 1,724 | 1,857 | 2,000 |

| Off-Chip<br>Freq(MHz) | 885   | 932   | 982   | 1,035 |

# Flip Chip Dynamic Effects

| F:MHz   | Vdd | Static     | Dynamic    |            | Dynamic    | Static vs.     |

|---------|-----|------------|------------|------------|------------|----------------|

| Γ.ΙΥΠΤΖ | vaa | IR         | Ri(t)      | Ldi/dt     | Total      | Dynamic        |

| 250     | 1.8 | 9.9<br>mV  | 17.3<br>mV | 1.2<br>mV  | 18.5<br>mV | 0.5%<br>1.02%  |

| 500     | 1.5 | 16.2<br>mV | 29.3<br>mV | 12.3<br>mV | 41.6<br>mV | 1.08%<br>2.77% |

| 750     | 1.2 | 19.3<br>mV | 36<br>mV   | 28.5<br>mV | 64.5<br>mV | 1.6%<br>5.37%  |

| 1,000   | 1.0 | 22<br>mV   | 38.8<br>mV | 41.6<br>mV | 80.4<br>mV | 2.2%<br>8.0%   |

#### Courtesy of Apache

# **Wire-bond Dynamic Effects**

|       |      | Static    | Dynamic       |          | Dynamic   | Static vs.                  |

|-------|------|-----------|---------------|----------|-----------|-----------------------------|

| F:MHz | Volt | IR        | <i>R i(t)</i> | Ldi/dt   | Total     | Dynamic                     |

| 133   | 1.8  | 103<br>mV | 147<br>mV     | 3 mV     | 150<br>mV | 5.7%<br><mark>8.3%</mark>   |

| 250   | 1.5  | 181<br>mV | 275<br>mV     | 13 mV    | 288<br>mV | 12%<br>19.2%                |

| 400   | 1.2  | 200<br>mV | 276<br>mV     | 75<br>mV | 351<br>mV | 16.6%<br><mark>29.2%</mark> |

Courtesy of Apache

5/30/96 oce\j\_owens\logic - 2

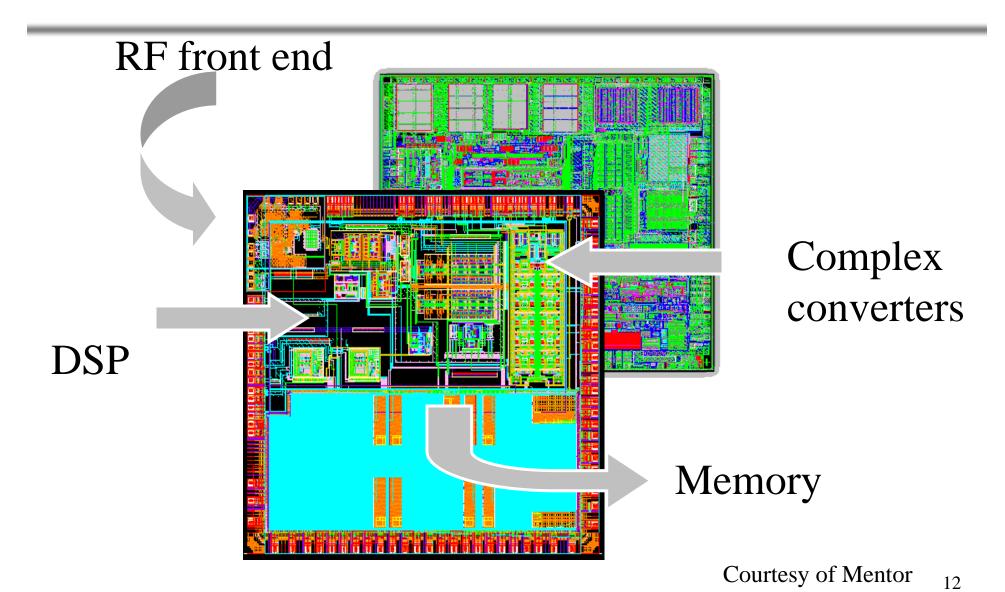

# **Increasing System Complexity**

# **I.2 Statistics about Design Flaws**

Percent of Total Flaws Fixed in IC/ASIC Designs Having Two or More Silicon Spins

| Collett Intl. 2000 Survey                                                                         | <ul> <li>Logical or Functional</li> </ul>                                                                                                   |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Logical or Functional<br>Slow Path<br>Noise<br>Yield<br>Clocking<br>Race Condition<br>Power<br>4% | <ul> <li>Analog</li> <li>Noise</li> <li>Slow Path</li> <li>Mixed-signal interface</li> <li>Clock, Power/Ground</li> <li>Firmware</li> </ul> |

| Mixed-Signal Interface 4%<br>IR Drops 3%<br>Other flaws 2%<br>0% 10% 20% 30%                      | Logical or Functional<br>Analog Circuit<br>Noise<br>Slow Path<br>28%                                                                        |

| Logical or Functional<br>Slow Path<br>Noise                                                       | Clocking<br>Yield<br>Yield<br>IR Drops<br>Race Condition<br>Firmware<br>0% 10% 20% 30% 40% 50% 60% 70% 80%                                  |

Collett Intl. 2001 Survey

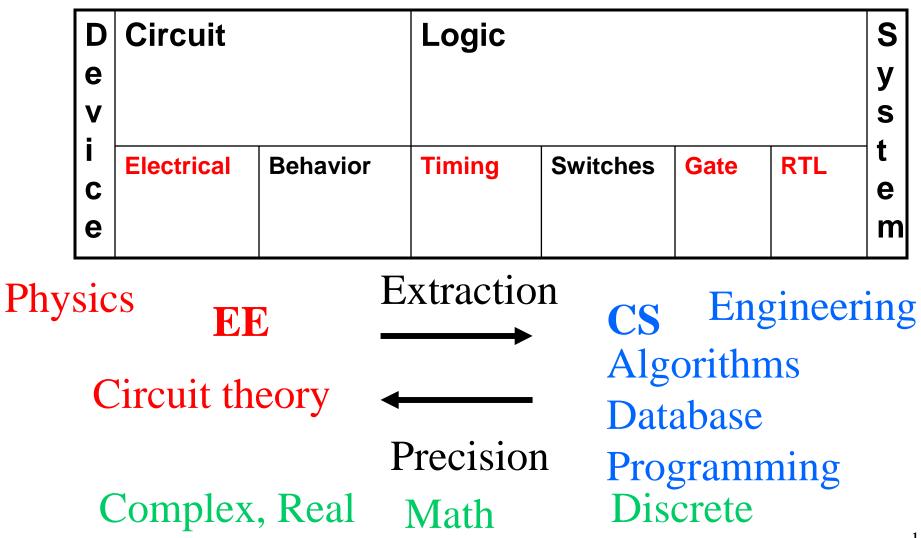

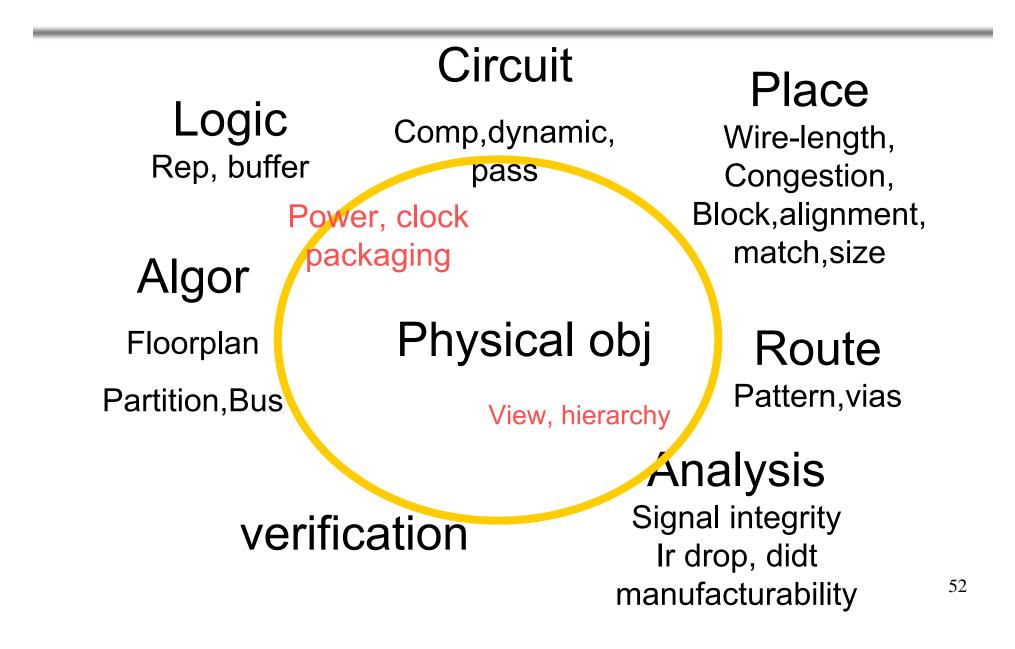

# **I.3 Spectrum of Analysis**

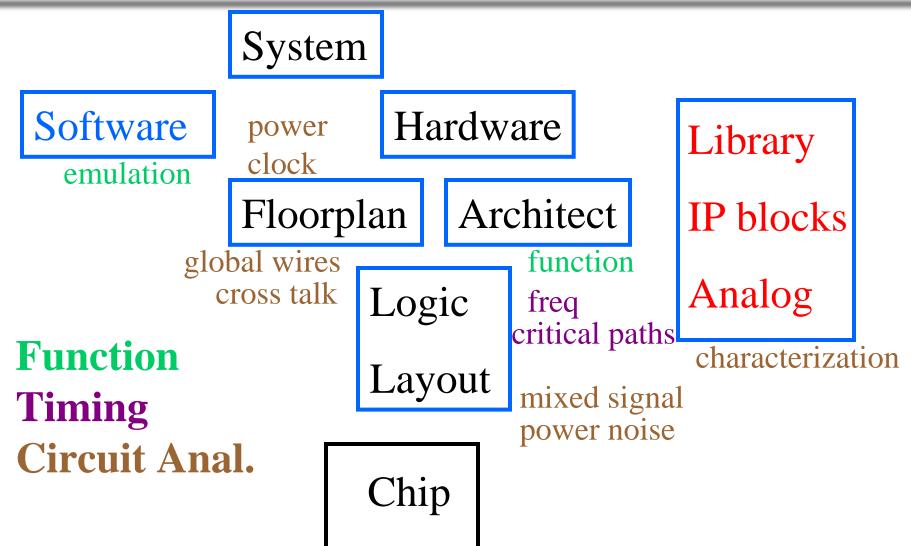

# I.3 Spectrum of Analysis(flow)

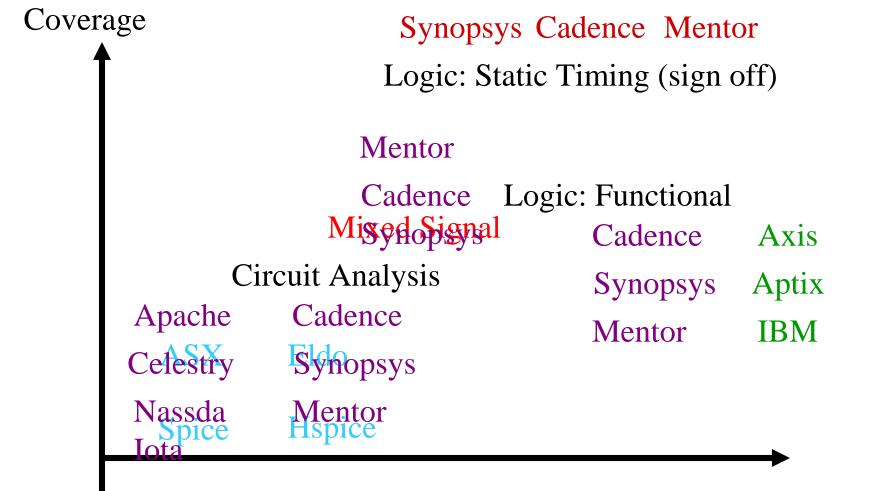

# I.3 Spectrum of Analysis(coverage)

Circuit Size

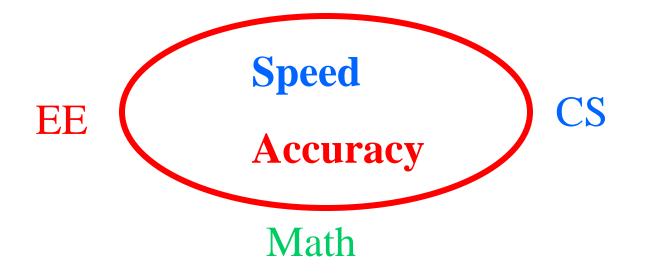

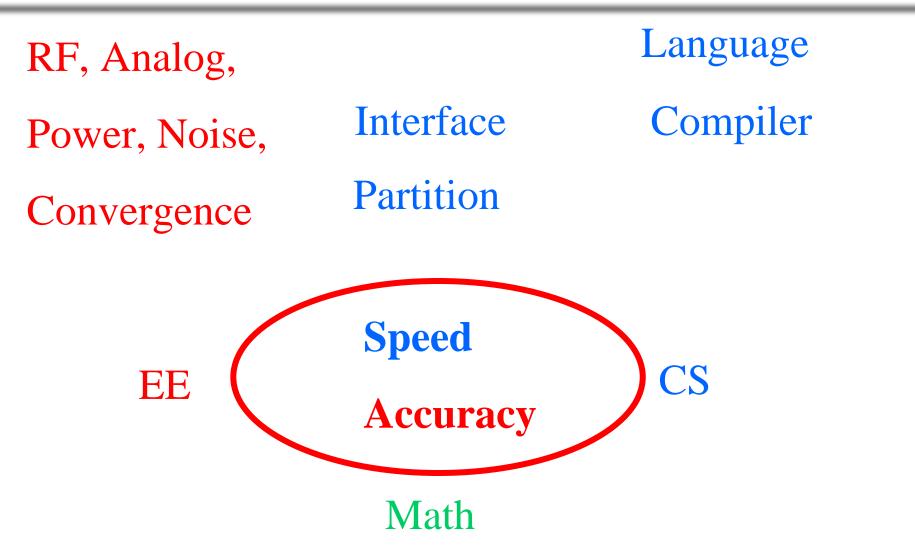

# I.3 Spectrum of Analysis(trend)

- Layout Dominated Analysis

- Power/Ground, Clock

- Wires

- Pre-layout, Post-layout

- Layout Oriented Analysis

- EE + CS

- EE=> CS High Complexity

- CS=>EE Deep Submicron Effect

- Accuracy and Efficiency

# **II. Circuit Level Analysis**

- 1. Circuit Analysis Advancement

- 2. Circuit Analysis Techniques

- 3. Examples

- 4. Tasks

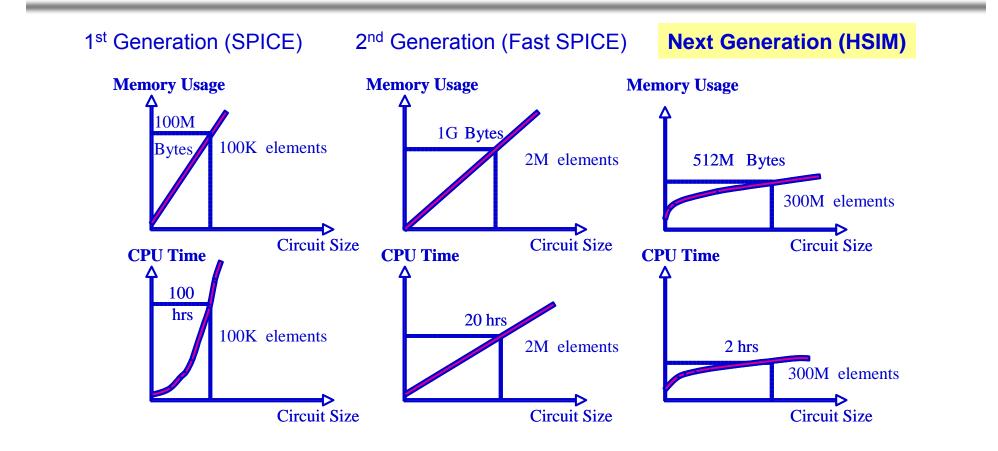

# II.1 Circuit Analysis Advancement

Courtesy of Nassda <sub>19</sub>

# **II.2 Circuit Analysis Techniques**

- Memory: Hierarchical Database

- Circuit Size: Parasitic Reduction

- Device Complexity: Table Model

- Simulation:

- Backward Euler, Trapezoidal Integration

- Hierarchical Flow

- Event Driven (ignoring miller effect)

- Mixed Rate, Multiple step sizes (partition)

# **II.3 Examples (HSIM)**

| Circuit Type           | Total       | Memory                | CPU        |

|------------------------|-------------|-----------------------|------------|

| (#MOS, #R,#C,#L)       | Elements    | Usage                 | Time (hrs) |

| Memory A               | <b>473M</b> | 775MB                 | 1.65       |

| (159M, 159M, 155M,0)   |             |                       |            |

| Memory B               | <b>13M</b>  | 195MB                 | 0.69       |

| (3.1M, 5.4M, 4.5M, 88) |             |                       |            |

| D/A                    | 121K        | <b>42MB</b>           | 1.11       |

| (9K,65K,47K,0)         |             |                       |            |

| PLL                    | <b>51K</b>  | 15MB                  | 0.21       |

| (2K, 8K, 23K, 0)       |             |                       |            |

| Analog                 | 525K        | 111MB                 | 0.37       |

| (119K, 175K, 232K,0)   |             | Courtesy of Nassda 21 |            |

# II.4. Tasks

# Device Mod.ConvergenceInput PatternsCircuit Red.Event DrivenHierarchy DatabaseMatrix Solver Hierarchical FlowIntegration Partition

# **III. Logic Level Analysis**

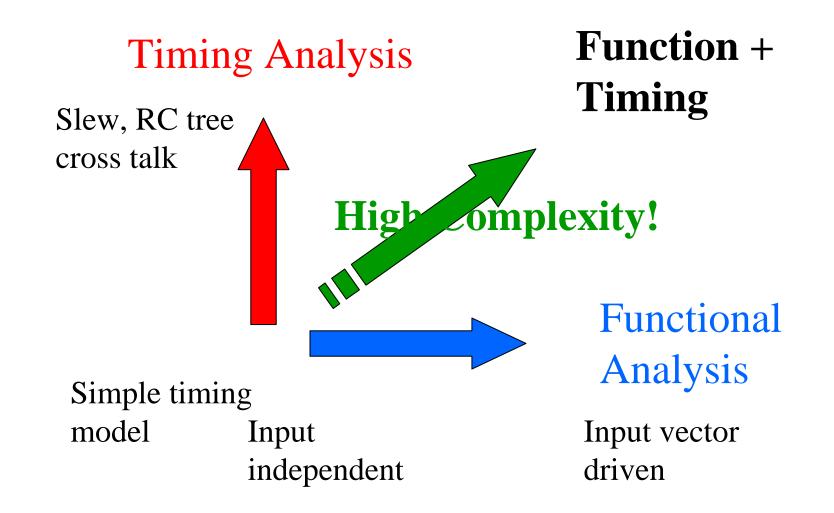

**1.Separation of Timing and Function 2.Static Timing Analysis Algorithms, Gate Models, Path, Cross Talks 3. Functional Analysis** Event Driven, Cycle Based 4.Tasks

# **III.1 Separation of Timing and Function**

# **III.2 Static Timing Analysis**

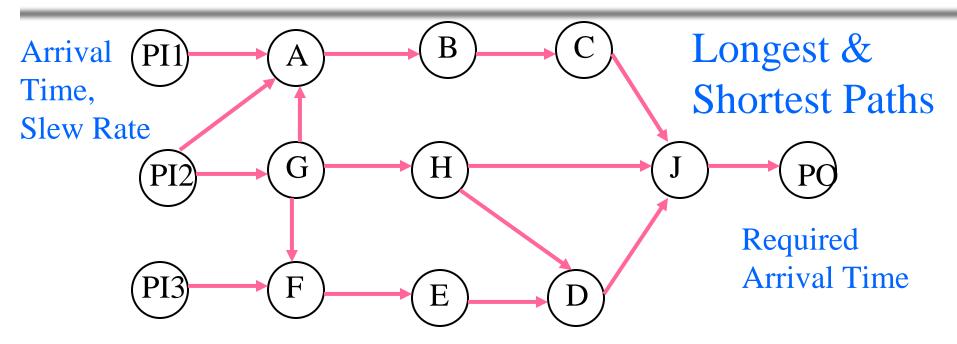

- i. Algor.: Shortest and Longest Paths Search

- ii. Gate Model:

- Logic: Unate, Binate Signal Propagations

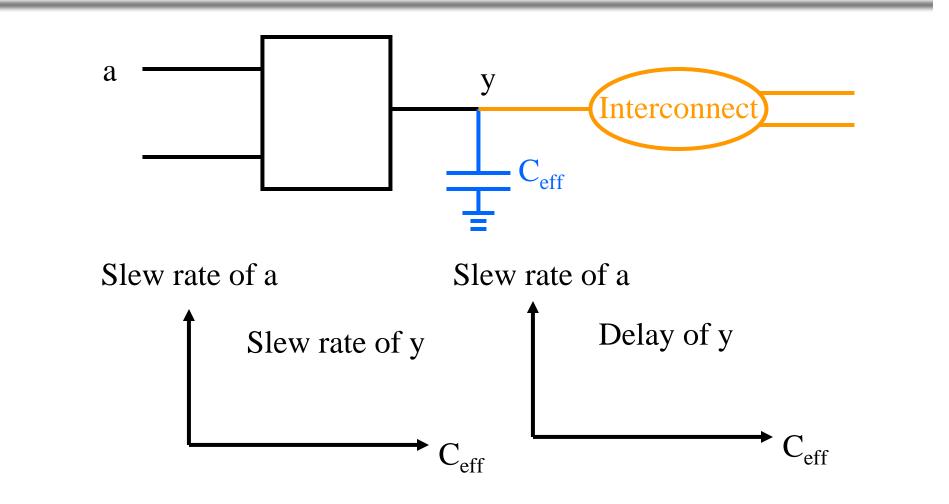

- Timing: functions of Input Slope and Output Load

- iii. Path Model:

- Logic: False Path, Multiple Cycle Path, Cycles of Combinational Logic, Multiple Clock Frequencies

- Timing: RC Tree

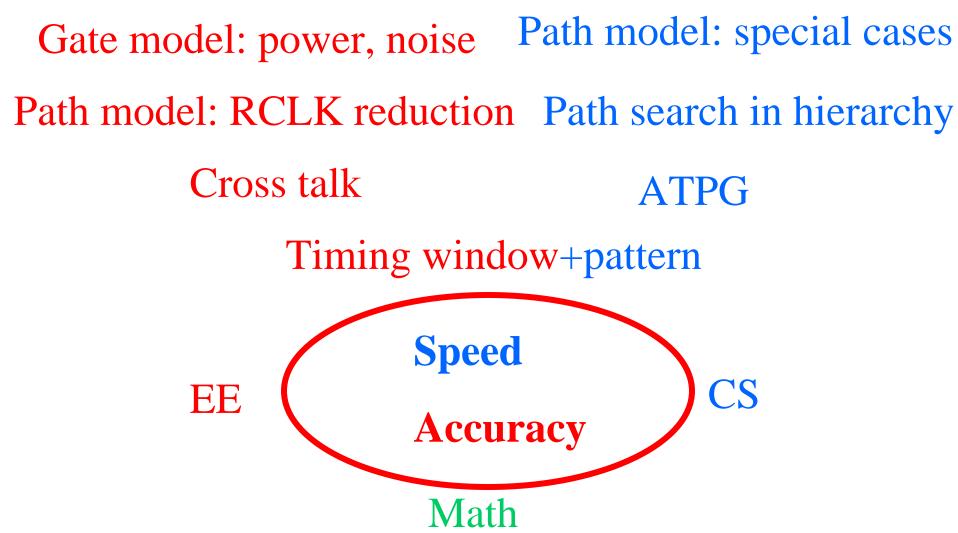

- iv. Cross Talks: Timing Window, ATPG

- v. Tasks

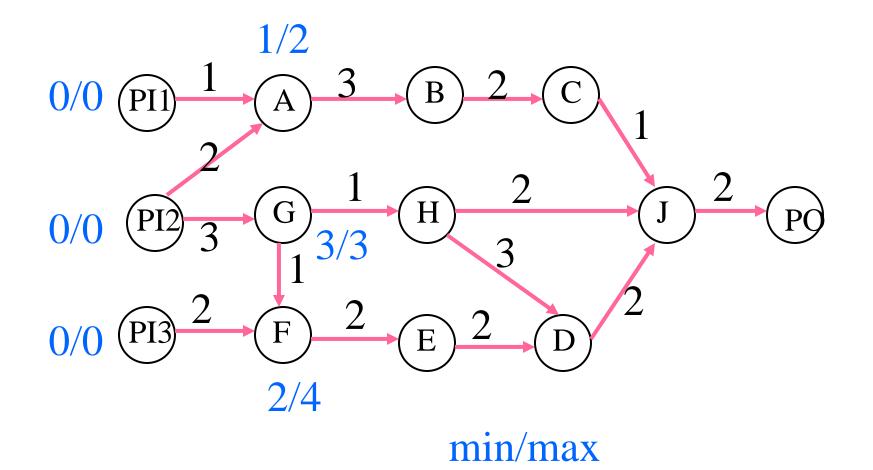

# III.2.i Algor.: Path Search

0->1 slew rate window 0->1 arrival time window 1->0 slew rate window 1->0 arrival time window

Static Timing Analysis: Worst Case Analysis, Independent of Input Patterns

# III.2.I Algor: Path Search(cont)

# III.2.I Algor: Path Search(cont)

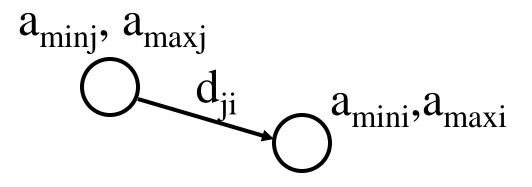

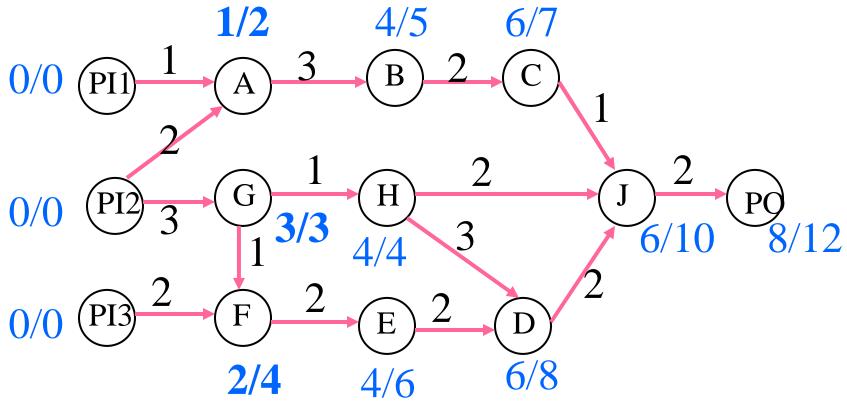

$$a_{\min} = \min_{j} a_{\min j} + d_{ji}$$

$$a_{\max} = \max_{j} a_{\max j} + d_{ji}$$

## III.2i Algor.: Path Search

min/max

Longest: PI2,G,F,E,D,J,PO Shortest: PI2,G,H,J,PO

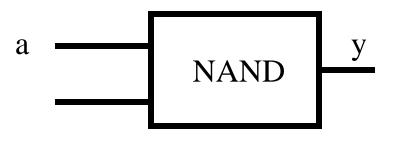

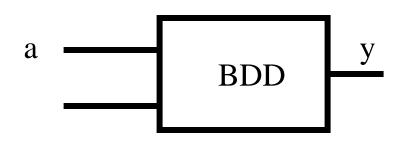

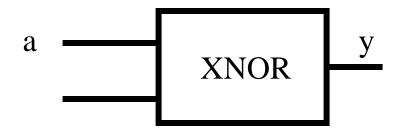

### III.2.ii Gate Logic Model: Unate & Binate Signals

Unateness: a 0->1 => y 1->0

Check unateness based on BDD

Binateness: a 0->1 => y 0->1 & 1->0

# III.2.ii Gate Timing Model

# III.2.iii Path Logic Model: False Path

# III.2.iii Path Logic Model: False Path

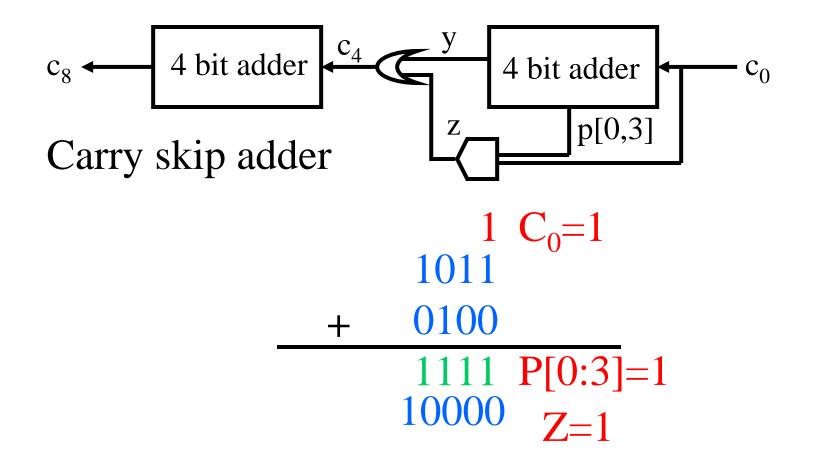

False path:  $c_0 \rightarrow y \rightarrow c_4 \rightarrow c_8$ Assumption:  $z \rightarrow c_4 \rightarrow c_8$  derives results faster

If we erase all false paths, we can identify the true critical paths and the corresponding input patterns

# III.2.iii Path Logic Model: False Path

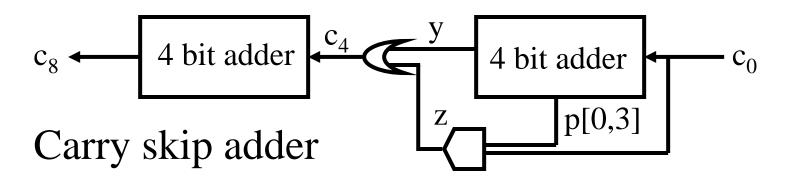

False path b->c->d->e

red+red=>red red+blue=>blue blue +blue=>blue

# III.2.iv Cross Talk

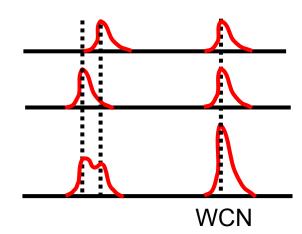

- WCN: worst-case noise: Delay & Glitch Noise with maximum pulse height

- Fixed circuit structure and parameters

- Fixed transition time of input signals

- Variable arrival time of input signals

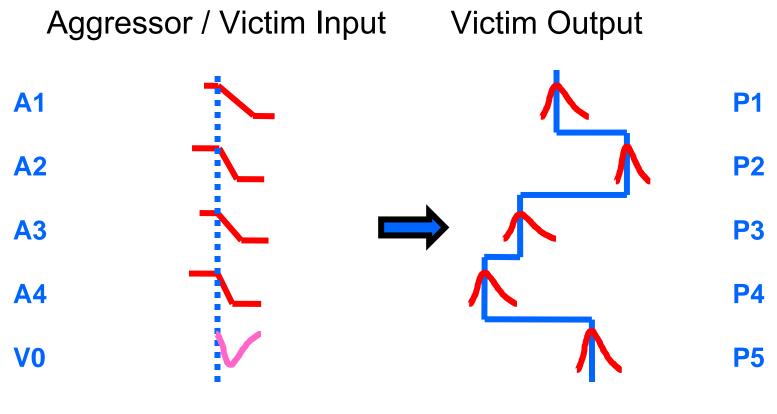

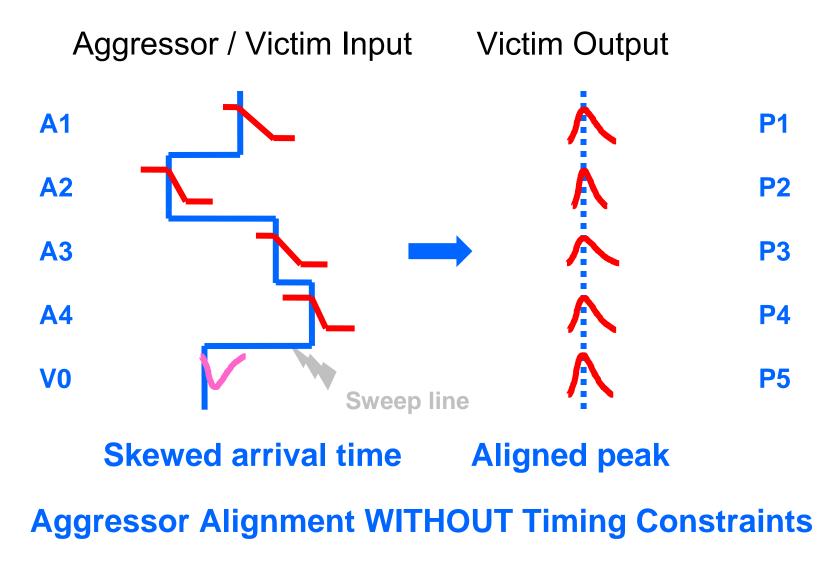

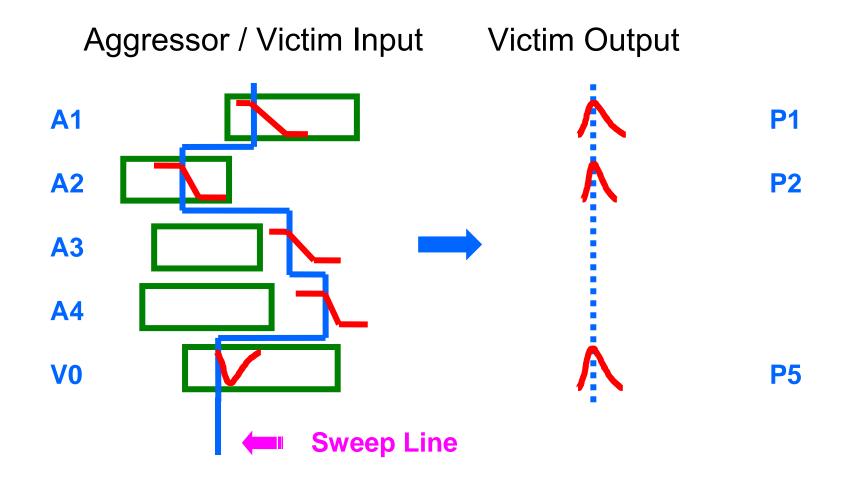

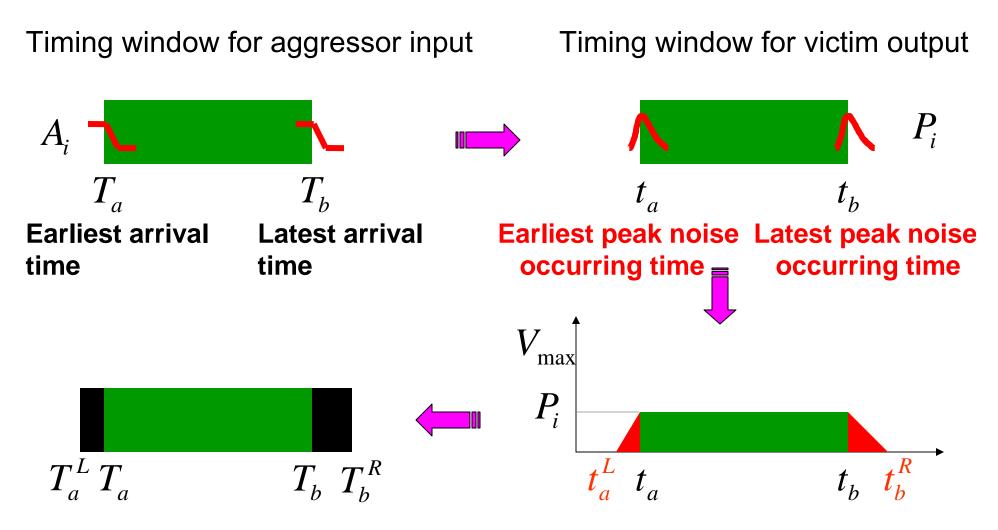

# **III.2.iv Cross Talk: Timing Window**

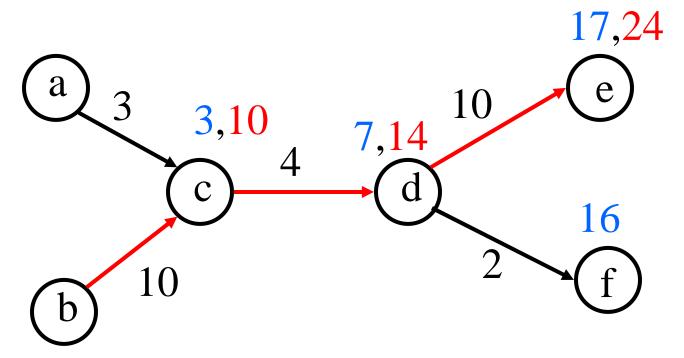

Aligned arrival time Skewed peak noise

## **III.2.iv Cross Talk: Timing Window**

# III.2.iv Cross Talk: Timing Window

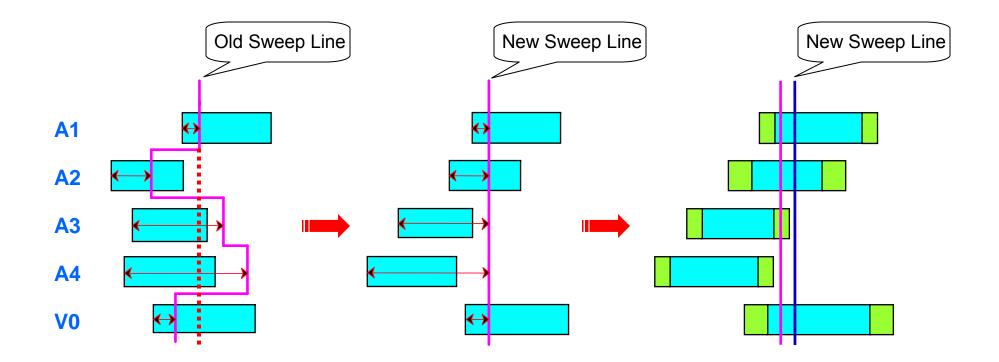

**Aggressor Alignment WITH Timing Constraints**

#### **III.2.iv Cross Talk: Effective Timing Window**

## Aggressor Alignment with Timing Constraints -- Reformulation

(a) Original timing window (b) Shifted timing window (c) Expanded timing window

#### III.2.v Tasks

## **III.3 Logic Level: Functional Analysis**

- i. Functional Analysis Techniques

- ii. Event Driven Analysis

- iii. Cycle Based Analysis

- iv. Tasks

## **III.3.i Functional Analysis Techniques**

Event Driven Simulation

VCS, Verilog-XL, VSS, ModelSim

Cycle Based Simulation

Frontline, Speedsim, Cyclone

Domain Specific Simulation

SPW, COSSAP

#### **III.3.ii Event Driven Analysis**

#### Event Wheel

- Maintains schedules of events

- Enables sub-cycle timing

- Advantages

- Timing accuracy

- Good Debug Capability

- Handles asynchronous

- Disadvantages

- Performance

#### **III.3.iii Cycle Based Analysis**

- RTL Description

- All gates evaluated every cycle

- Schedule is determined at compile time

- No timing

- No asynchronous feedback, latches

- Regression Phase

- High Performance

- High Capacity

## III.3.iv Tasks

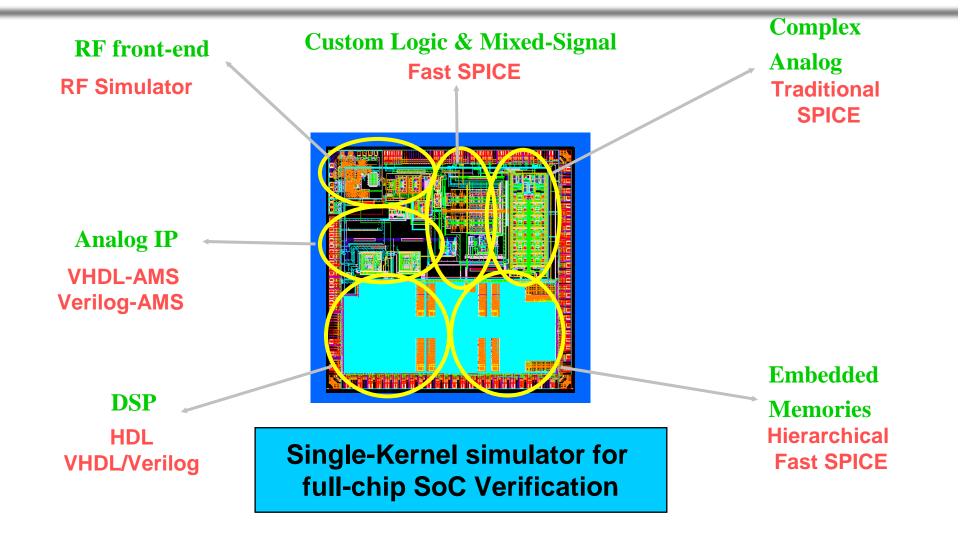

#### **IV. Mixed Signal Analysis**

Courtesy of Mentor

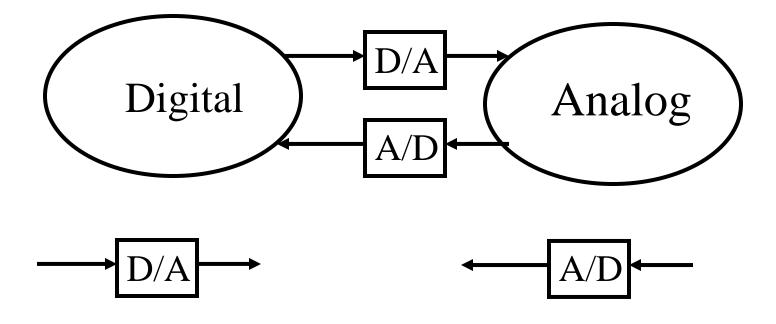

## **IV. Mixed Signal Analysis: Interface**

Analog Threshold Signal Detector 0, 1, X Rise, Fall Time Rise, Fall Resistance

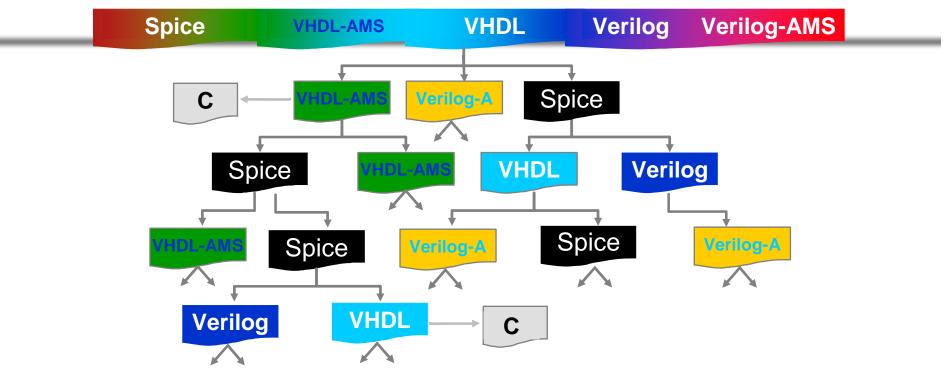

# **Mixed Signal: Mixed Languages**

Single Kernel Architecture

Single Netlist Hierarchy

Automatic D/A and A/D converter insertion

#### **IV. Tasks**

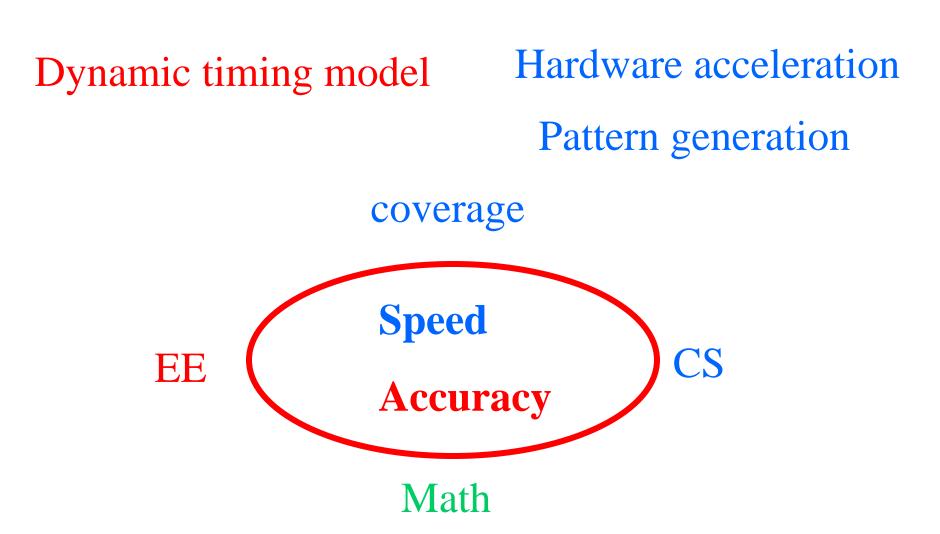

#### **IV. Research Directions**

- Hierarchy Management

- Analysis + Optimization

- Layout Oriented Analysis

- Circuit Reduction

- Spice

#### Hierarchy Management

## **Hierarchy management**

# **Hierarchy Management (cont.)**

Hierarchy Tree Construction

Hierarchy Tree Transformation

Incremental Changes

Graph Process on Tree Structure

## **Analysis and Optimization**

- i. Circuit Reduction

- ii. Transient Analysis

- iii. Optimization of

- power/ground: pads, decoup caps, network

- clock networks: topology, shield, decoup caps

- Buses: shield, topology

## **Layout Oriented Analysis**

Huge Circuitry Millions of nodes Whole Chip Analysis Power/Ground, Substrate, Analog Guaranteed Accuracy Accuracy vs Execution Time Construction or Incremental Changes

### **Layout Based Signal Analysis**

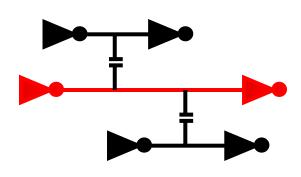

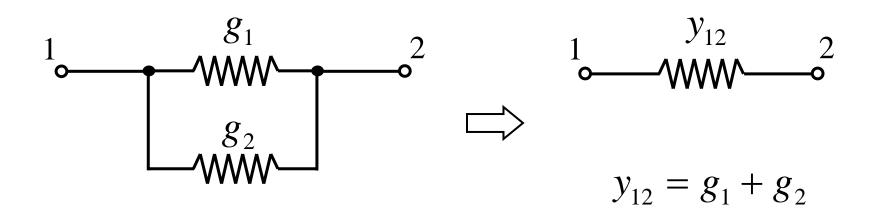

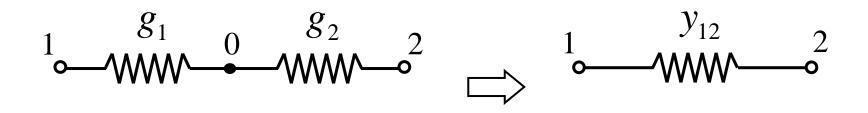

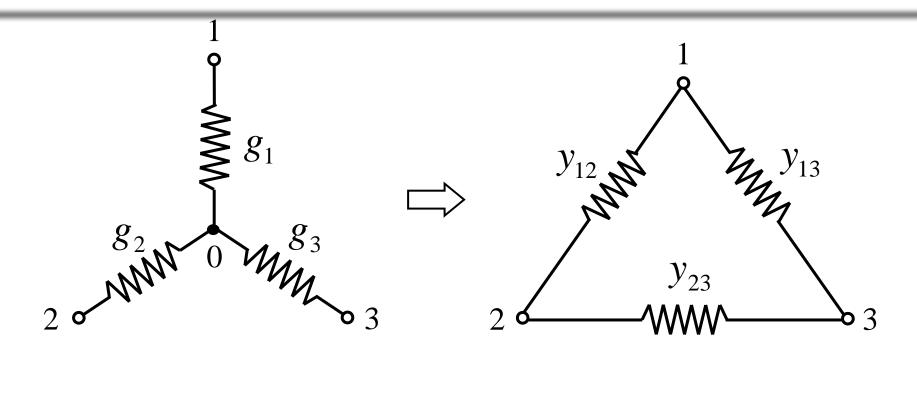

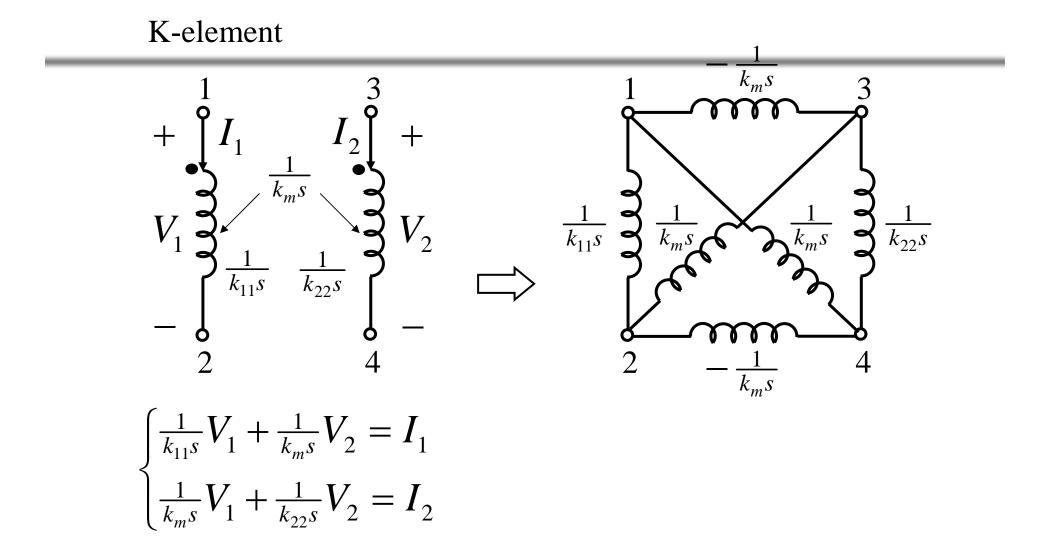

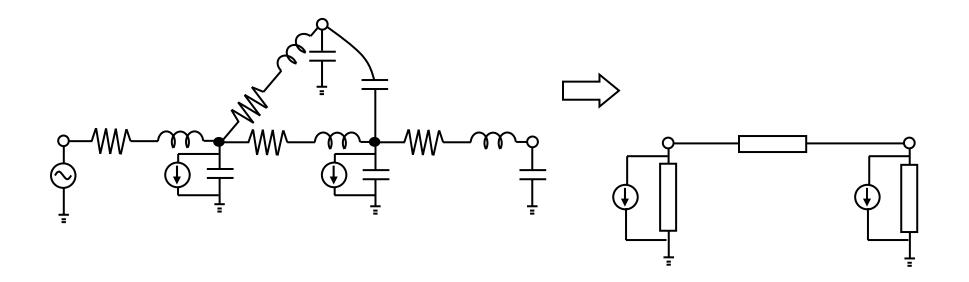

Generalized Y-Delta Transformation

R,C,L,Coupling, Sources

Natural Frequency

Realizability

Hierarchical Circuit Analysis

Conductance in parallel

Conductance in series

$$y_{12} = \frac{g_1 \cdot g_2}{g_1 + g_2}$$

Conductance in Y-structure

$$y_{ij} = \frac{g_i \cdot g_j}{g_1 + g_2 + g_3}$$

60

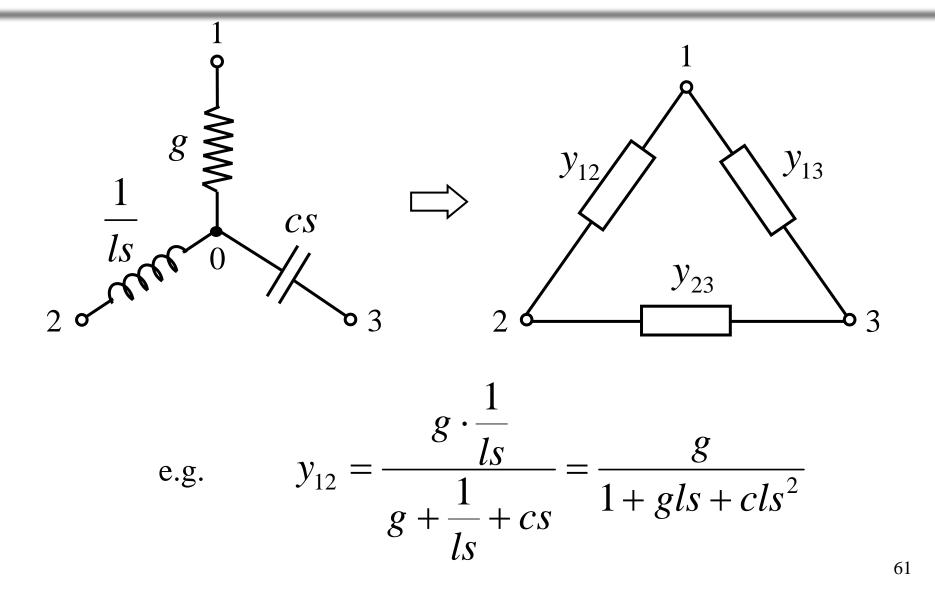

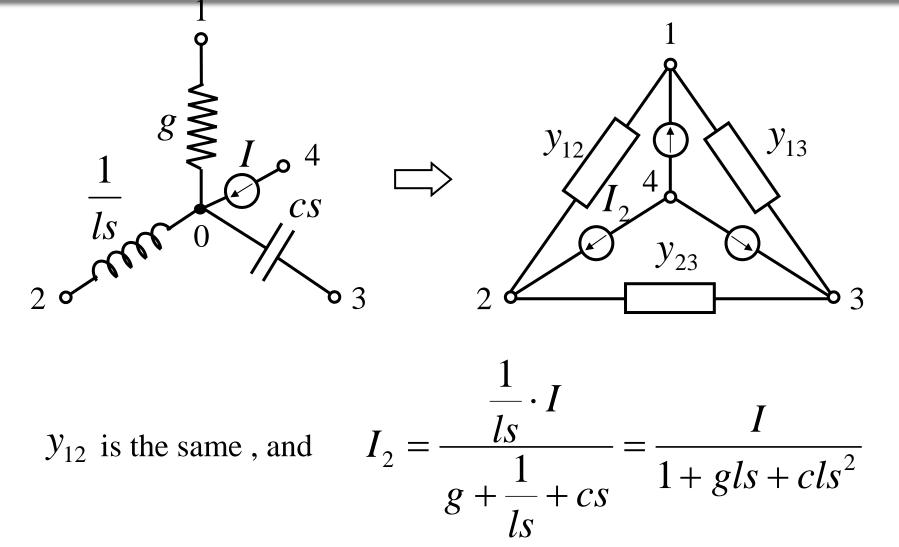

Admittance in Y-structure

Admittance in Y-structure, with current source

#### Reduction example

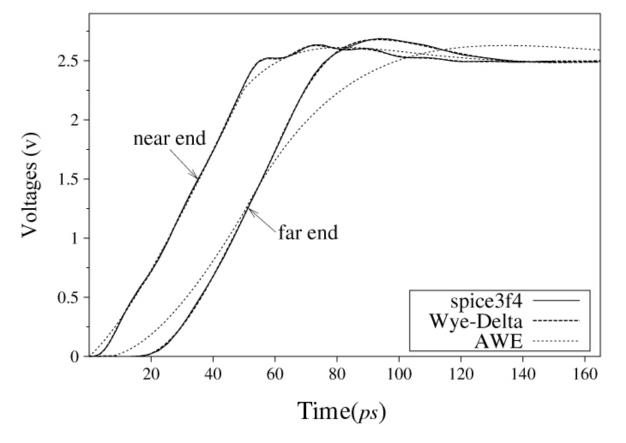

#### **Waveform Estimation**

Transient response evaluated using  $Y-\Delta$  transformation with Hurwitz polynomial approximation.

$8^{th}$  order stabilized Y-  $\Delta$  models are used for near-end and farend node waveform evaluation.

Only a 3<sup>rd</sup> order AWE model is obtained.

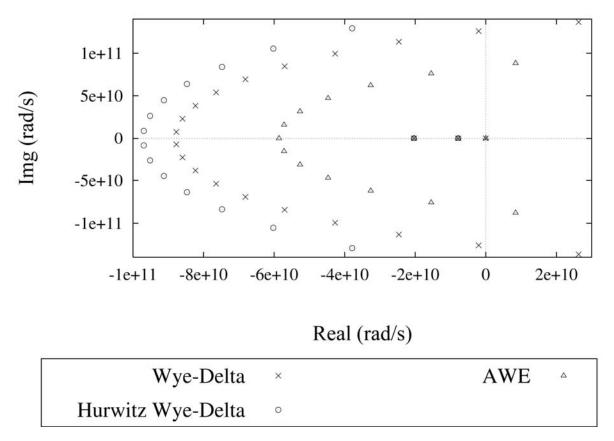

## **Pole Analysis**

Both AWE and Y- $\Delta$  transformation have artificial *positive* poles;

High order AWE tends to collapse approximate poles, hiding other less dominant ones.

Y- $\Delta$  transformation with model stabilization yields no positive poles, and has broader band in pole estimation.

# V. Conclusion

- Layout Oriented Analysis

- Unified tools combining EE and CS with Math as foundation

- New Methodologies

- Larger Circuits, Shorter Product Turnaround

## References

- M. Marek-Sadowska, UCSB

- L.T. Pileggi, CMU

- CK Cheng, et al, Interconnect Analysis and Synthesis, John Wiley

- ACM/IEEE Design Automation Conf.

- IEEE/ACM Int. Conf. On CAD

- Apache, Nassda, Mentor, Synopsys, Cadence, Celestry, IBM, and etc.