### Characterizing and Managing Variability in Microprocessor Chips

#### Manjul Bhushan IBM, Systems & Technology Group

### **Acknowledgements**

- Mark Ketchen

- Anne Gattiker

- IBM Systems & Technology Group Members

References:

- 1. Manjul Bhushan, Anne Gattiker, Mark B. Ketchen, and K.K. Das IEEE Transactions on Semiconductor Manufacturing, <u>19</u>, pp10-18, 2006.

- 2. Manjul Bhushan, Mark B. Ketchen, Stas Polonsky and Anne Gattiker Proceedings of 2006 ICMTS

- 3. Mark B. Ketchen and Manjul Bhushan IBM Journal of Research and Development, Vol 4/5, 2006

- 4. Anne Gattker, Manjul Bhushan and Mark B. Ketchen, ITC -2006.

## <u>Outline</u>

- Source of Variability and Impact

- Measuring Variability

- Process Induced

- Design Induced

- Managing Variability

- Summary

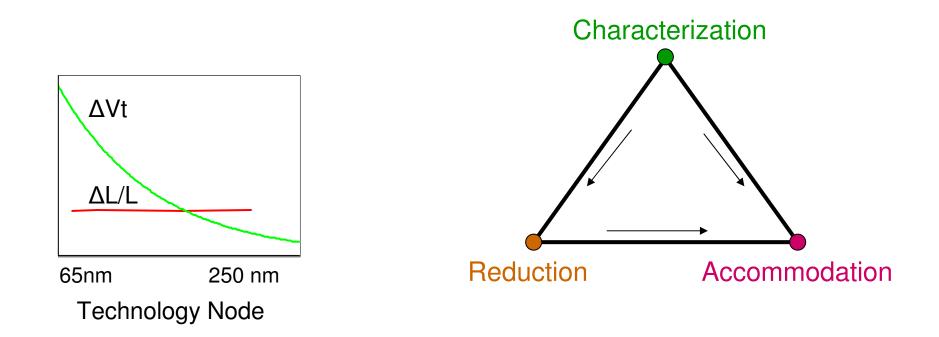

#### Variability - Challenges

Characterization Goal: Reduce impact of variability on microprocessor performance, power and yield

### Sources of Variability (CMOS Technology)

- Fundamental Random Variations

- Dopant fluctuations induced Vt variations

- Line edge roughness

- Systematic CMOS process induced variations

- Across chip, across reticle, across wafer, wafer-to-wafer and lot-to-lot

- Across circuit topology & metal wire R & C

- Time dependent variations, short term (10<sup>-9</sup> s 10<sup>-3</sup> s)

- SOI Floating body induced variations

- Power supply transients

- Time dependent variations, long term (10<sup>8</sup> s)

NBTI, hot-electron, electromigration

#### Sources of Variability (Package/ Design)

- Chip integration induced variation

- Power supply distribution

- Hotspots

- Package/module induced variations

- IR Drops

- Temperature gradients

- Design tool induced variations

- Hardware to parasitic and wire models

- Hardware to BSIM model

- BSIM model to piecewise linear model

### Is Variability an Issue?

- Reduced yield for high performance parts

- SRAM yield read/write fails

- Analog circuits functionality, out of specifications

### Characterizing Variability

- Product representative test structures

- on chip placement for ongoing evaluation

- design tools based target parameters

- experimental designs to minimize ambiguity

- Ease of data collection, development and manufacturing

- Techniques for effective data analysis

- Rapid feedback to CMOS process and design teams

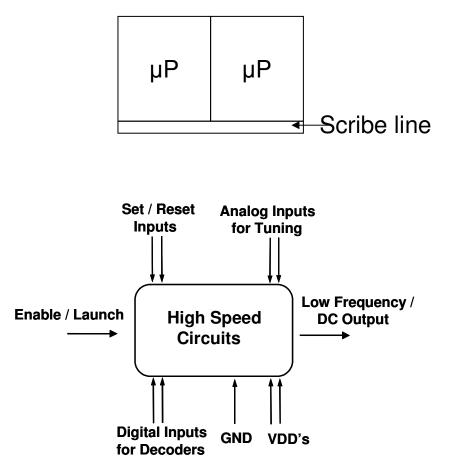

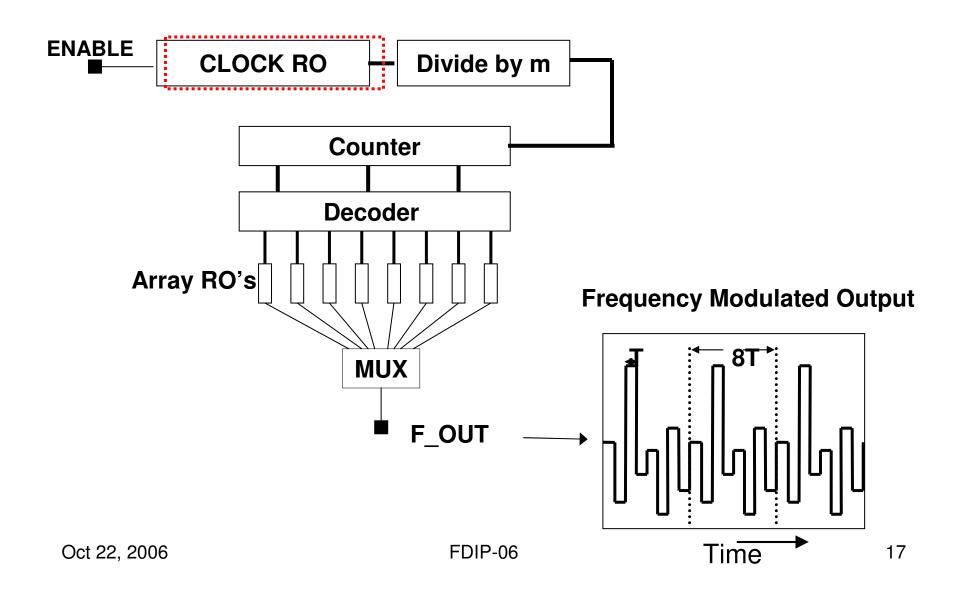

#### "At Speed" Test Structures

- Strategic placement

- Ring oscillator and pulse based

- Differential measurements/analysis

- DC I/O's for ease of measurement

- Circuit delays directly relate to process/device parameters

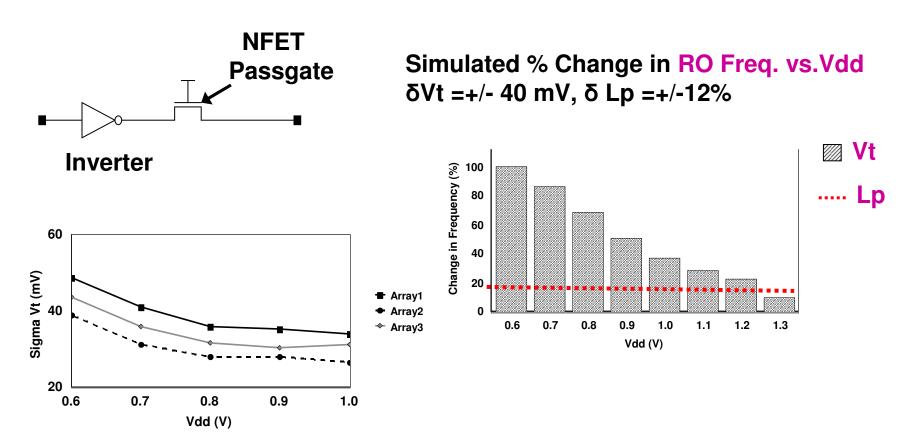

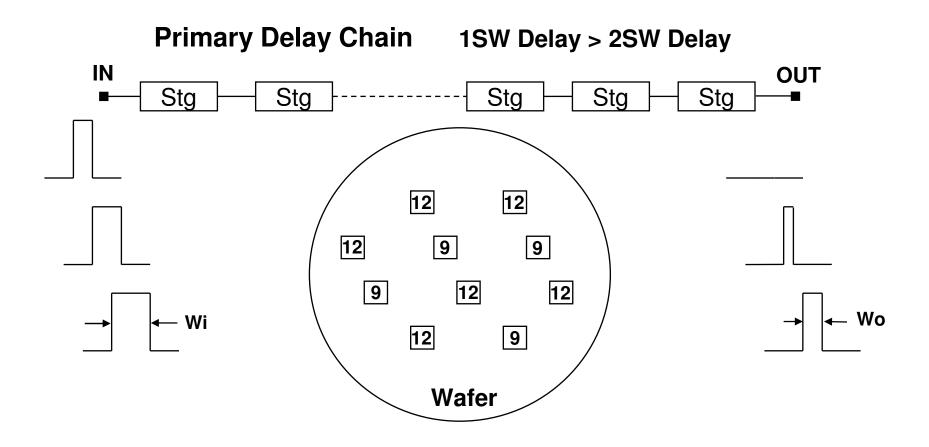

### Variability in Circuit Performance

- Process induced systematic variations

Across chip

- Across circuit toplogies / layout Styles

- Random variations in closely spaced identical circuits, arising from variations in Vt, Line width (Lpoly), Tox ..

Test Structures for rapid measurements of product representative identical ckt. delays to obtain underlying parametric variations

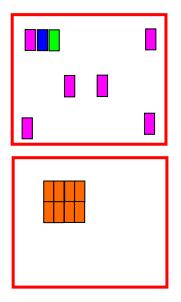

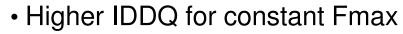

### <u>Across Chip Variation</u> <u>Multiple Identical Ring Oscillators</u>

- Placement of identical ring oscillators on a grid

- > 50 stages/ring to remove impact of random variations in MOSFET parameters

- Measurement (w & w/o clock) for CMOS performance variations vs. power supply and temperature variations

- Correlation of ring and chip frequency by location

#### Microprocessor Chip

#### **Delay Variation Across Chip**

• Fmax variation across wafer

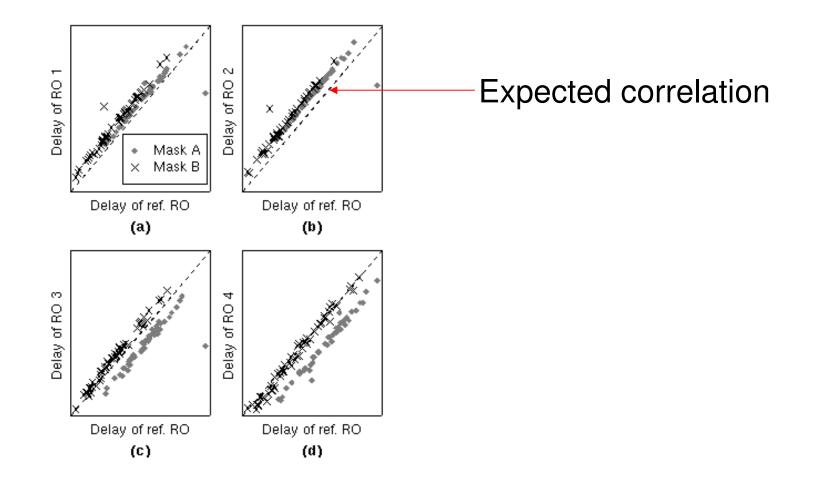

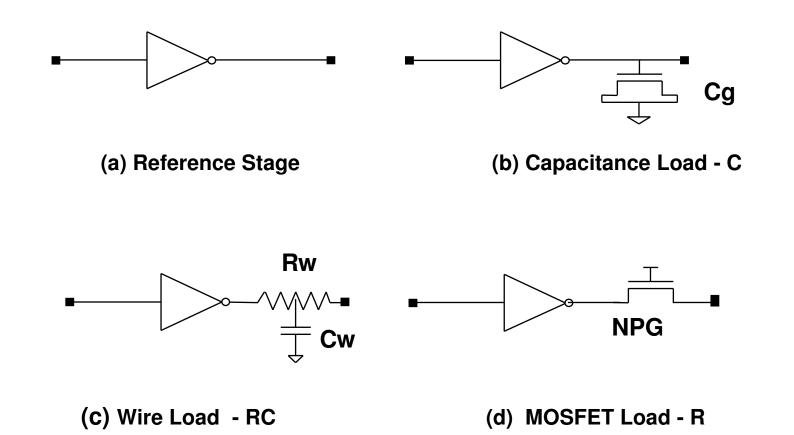

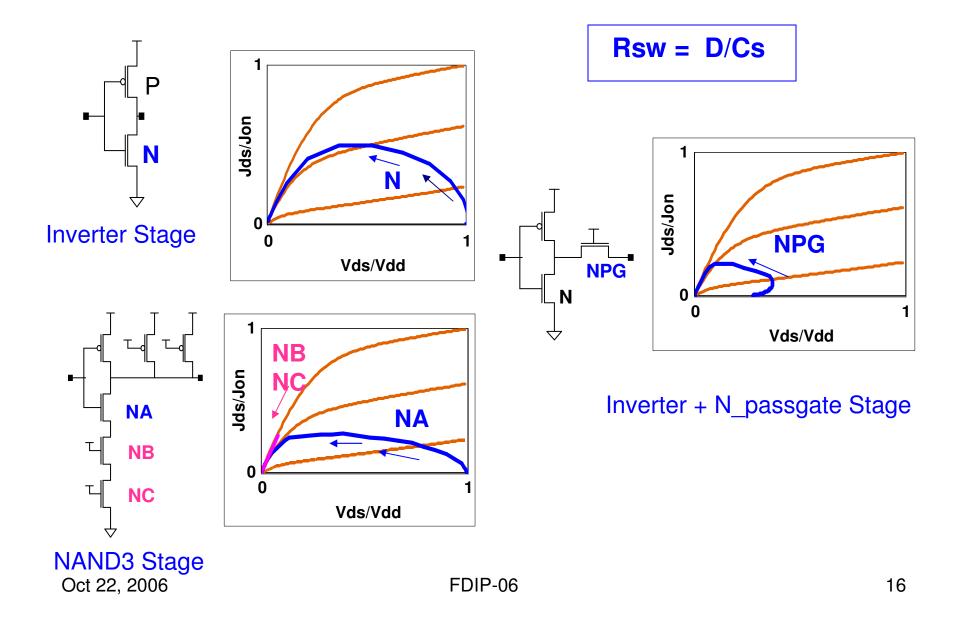

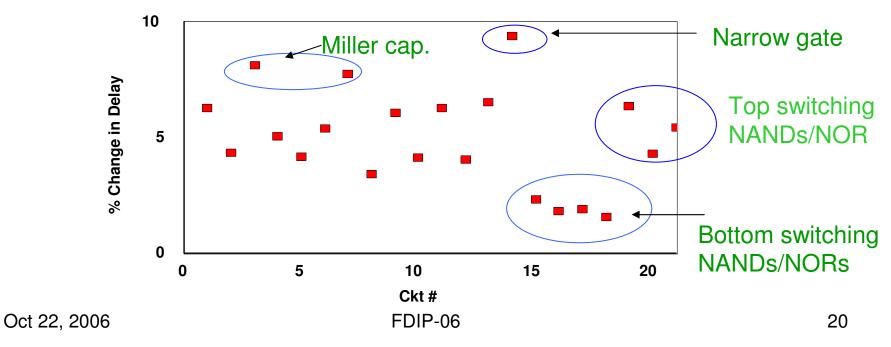

#### Across Circuit Type/Process Variability

Oct 22, 2006

Ring Oscillator Stage Designs Differencing Schemes

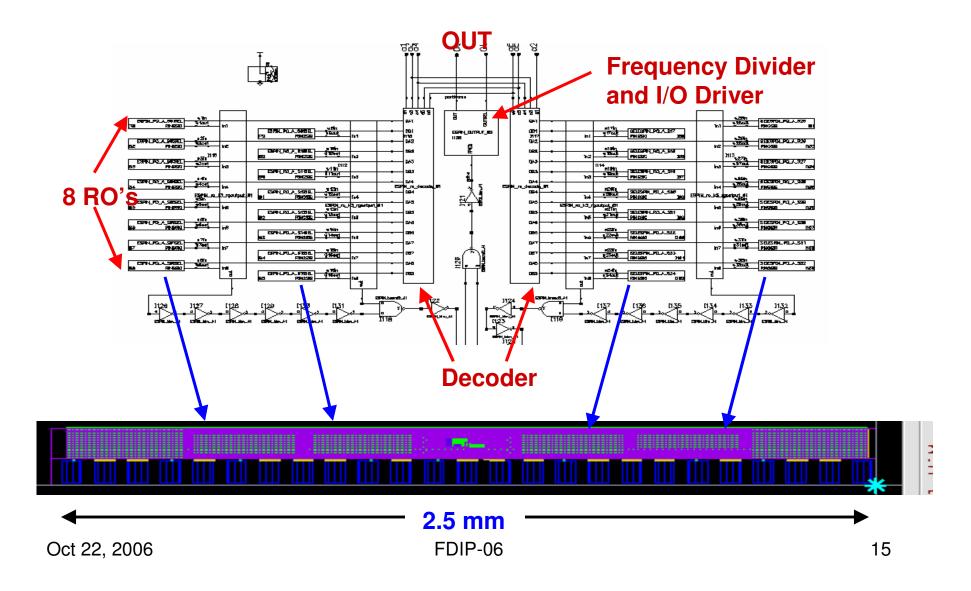

#### **Design of a 32 Ring Oscillator Macro**

#### Average Current from RO Delay/Stage

#### "At Speed" Test Structure for Vt Variations

#### Extraction of Vt Variations from Circuit Delays

Oct 22, 2006

#### Temporal Variability – SOI History Effect

#### Variability introduced by Chip Timing Tools

- Simulated circuit delays vary with parasitic models

- Model assumptions to reduce simulation time add to inaccuracies in timing

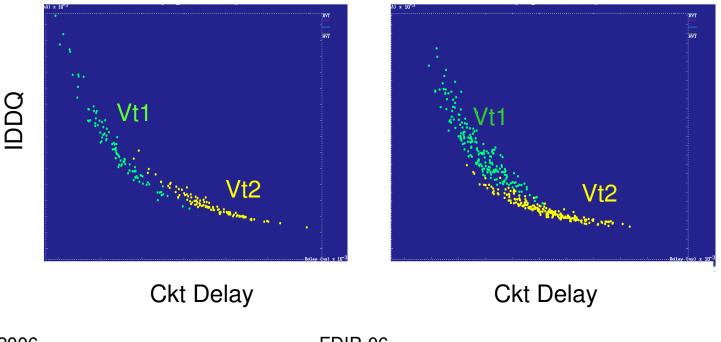

#### <u>Multiple Vt MOSFETs – Inverter FO3</u>

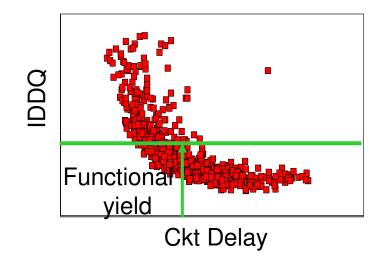

- IDDQ vs. Delay for two different Vt's

- Shifts in relative Vt centering in the hardware may merge the distributions

Vdd=0.8V

Vdd = 1.0V

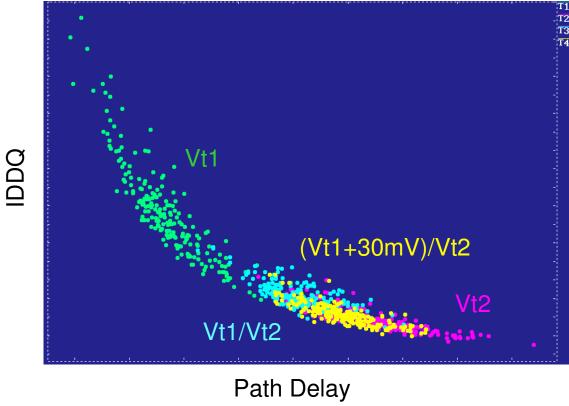

#### Multiple Vt's, Critical Path Example

Leakage Power (IDDQ) /Performance Trade-off varies with mixed Vt gates and Vt centering in the Hardware

Path composition All Gates Vt1 All Gates Vt2 Mixed Gates Vt1/Vt2 Mixed Gates (Vt1+30mV)/Vt2

Oct 22, 2006

FDIP-06

# <u>Summary</u>

- Characterization of variability on an on-going basis is key to its minimization and accommodation in design

- "At Speed" test structures for variability characterization aid in technology development and manufacturing

- Judicious composition of device menu and restrictive designs reduce the impact of variability