Future Directions in IC and Package Design Workshop

# Signal Bandwidth for High-Performance Computing

Dale Becker, Ph.D. IBM Corporation wbecker@us.ibm.com Poughkeepsie, NY, USA October, 2007

## Packaging solutions to system performance growth

- Industry targets through the eyes of the IEEE FDIP Workshop.

- Future Directions in IC and Package Design Workshop

- Observations that impact server packaging technology

- System and package electrical design considerations

- What does this bandwidth cost?

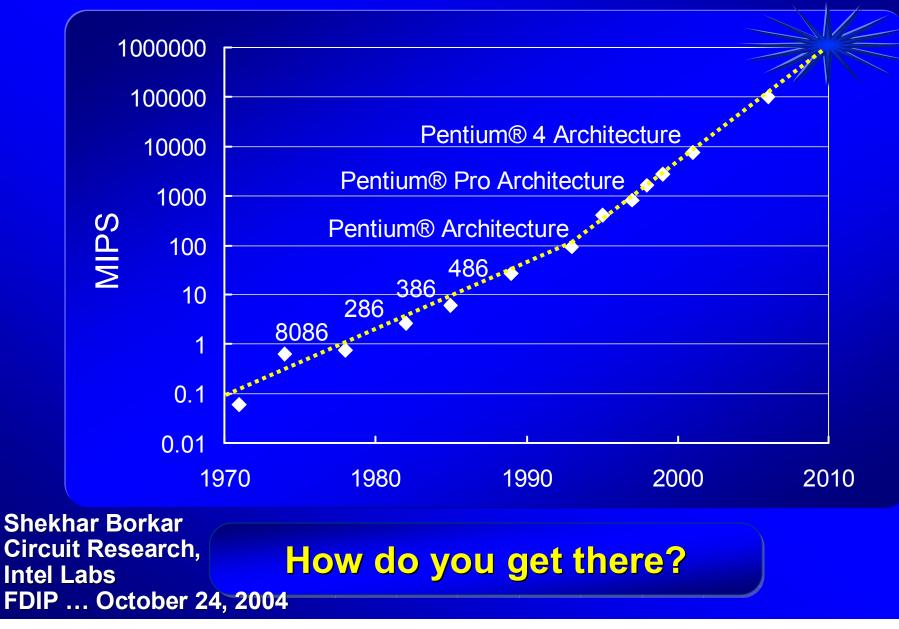

## Goal: 1TIPS by 2010

## **Chip Performance Trends**

Carl Anderson IBM FDIP – Oct. 2005

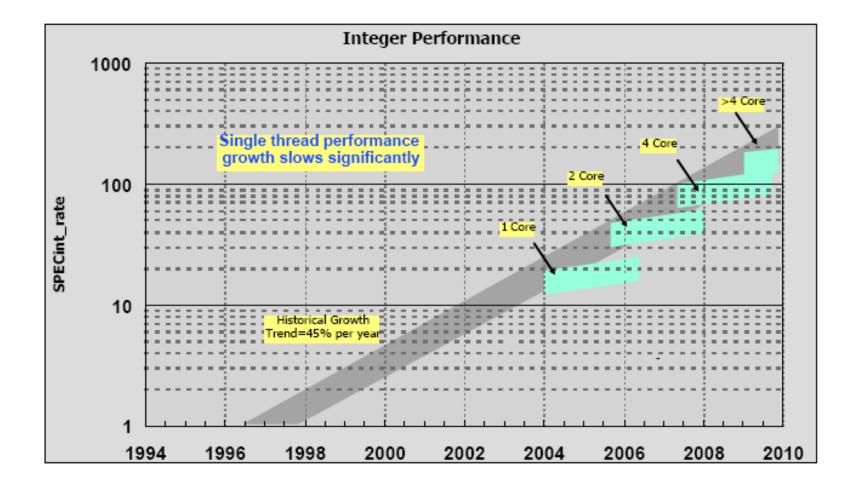

## Multi Cores

Carl Anderson IBM FDIP – Oct. 2005b

# 2-4 Cores per Socket Available Now 8+ Cores By 2010

Power 4 1st Dual Core 2001

Dual Core Opteron 1st Desktop Dual Core

Power 5 Quad Core per Socket

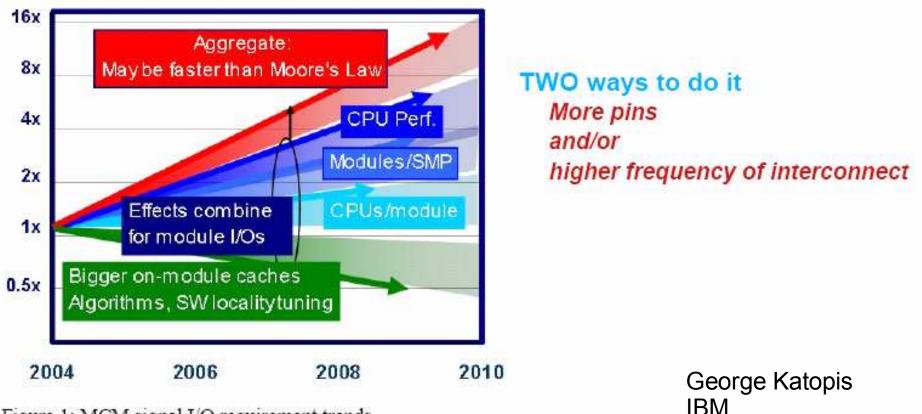

#### The CEC bandwidth component and requirements

Figure 1: MCM signal I/O requirement trends

FDIP October 23, 2005

G. A. Katopis @ 2005 IBM Corporation

FDIP – Oct. 2005

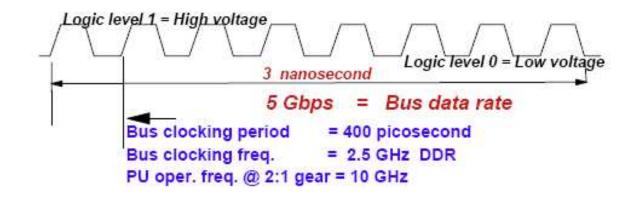

## The EM modeling challenge

| Eq. PU<br>Freq. of<br>Oper GHz | Time      | Data rate for<br>2:1 bus gear<br>Single Ended | Data rate for<br>1:1 bus gear<br>Differential | Bus freq. in<br>GHz | Interc. Model<br>freq. GHz |

|--------------------------------|-----------|-----------------------------------------------|-----------------------------------------------|---------------------|----------------------------|

| 2                              | Now       | 1 Gbps                                        | 2 Gbps                                        | 0.5-1               | 5-10                       |

| 5                              | Next Gen. | 2.5 Gbps                                      | 5 Gbps                                        | 1.25-2.5            | 12.5-25                    |

| 10                             | 2010      | 5 Gbps                                        | 10 Gbps                                       | 2.5-5               | 25-50                      |

The tools and verification measurements must be acurate for up to 50GHz in 2 years

FDIP October 23, 2005

G. A. Katopis @ 2005 IBM Corporation

FDIP05IOkatopisfoils.prz - 10

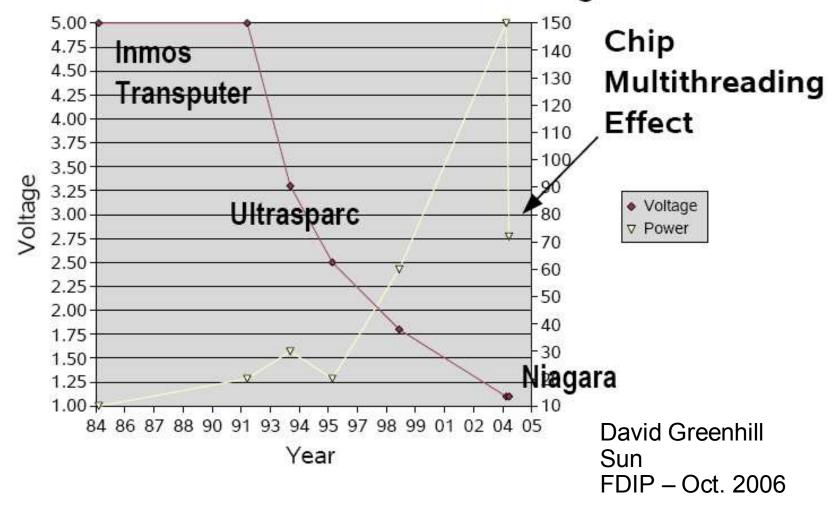

#### Personal View of Processor Designs

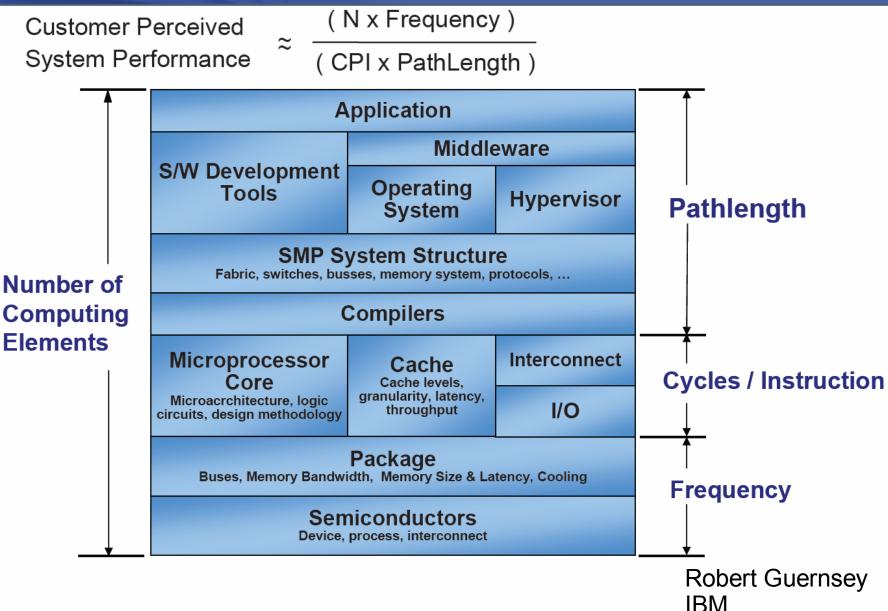

#### **System Performance Stack**

ESPW– Jan. 2007

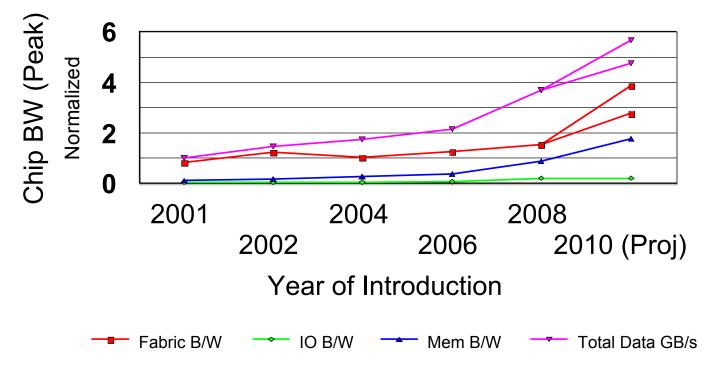

#### "Peak bandwidth" – My experience

#### Processor Peak Bandwidth Summary Simply Data Bits x Gb/sec signalling rate

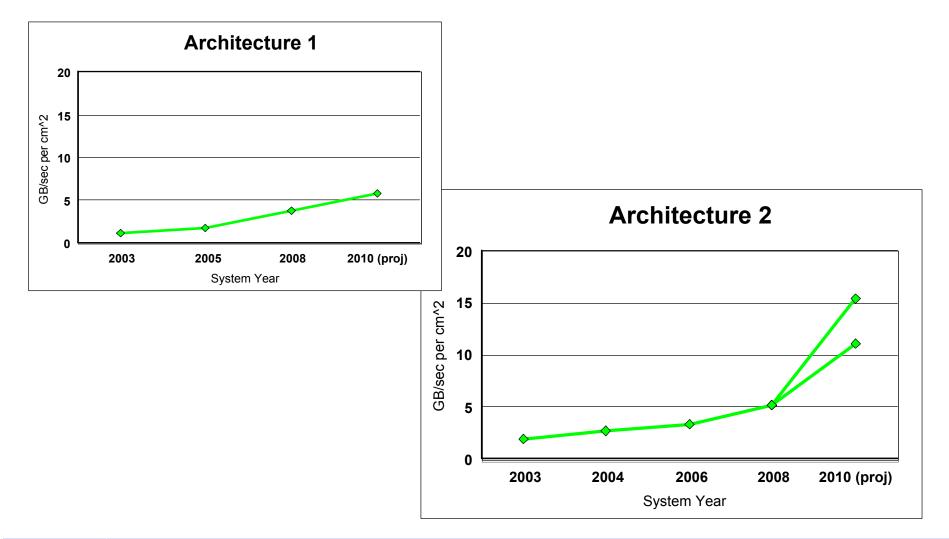

## Trend of package I/O bandwidth density.

## Key Observations for Server Systems

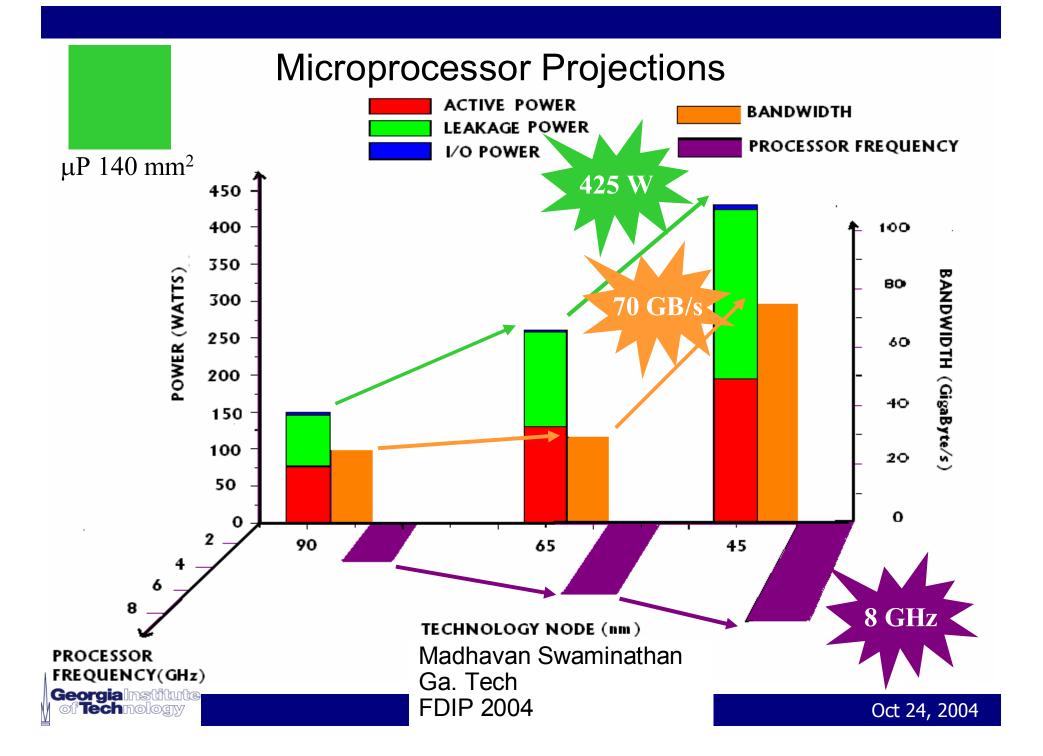

- System performance growth rate is maintained for the foreseeable future

- Innovative ways to maintain growth rate while minimizing growth in power and thermal

- Processor frequency growth rate is leveling off to help reduce power growth

- Off-processor signal frequency is increasing rapidly to maintain performance growth

- Memory bandwidth is a key part of maintaining performance.

- Also note that ASIC (Bridge chip) frequencies are increasing to keep up with off-chip bandwidth

#### IBM

## System Packaging Design Key Challenges

#### Manage Processor Power Growth

- Multiple voltage domains with similar voltage levels

- Tune voltage levels to logic frequency sort points

- Enable more aggressive power saving modes

- Multiple cores

- More cores per system

### Enable High-Bandwidth Signaling

- High number of connections

- Low-loss interconnections

- Minimize jitter

- Clocks, Switching Noise, Crosstalk, Reflections

#### Tends to lead to more on-chip integration of function

## **Electrical Considerations**

- Low Loss Signal Traces

- Minimize stubs and boards with low resistance and low tan  $\delta$

#### Low Noise Interfaces

- Low crosstalk in connectors

#### Reference Current Returns

- Splits induced by connector vias

## Power Distribution

- DC analysis becomes more system level

- Number of chip pins impacted by electromigration limits

- Number of package pins impacted by thermal limits

- Decoupling is challenged by multiple voltage domains

#### SI - A historical perspective

| Year | Bit Rate                    | Evolving<br>Constraints                | Evolving Design<br>Verification at tape-out              |  |

|------|-----------------------------|----------------------------------------|----------------------------------------------------------|--|

| 1996 | 0.166 Gb/s                  | Bound Timing Limits<br>AC Noise Budget | Spreadsheet timing<br>SSN determine VDDmin               |  |

| 1998 | 0.250 Gb/s                  | ISI In Noise Budget                    | Multi-pkg level Crosstalk<br>Core Noise included in SSN  |  |

| 2000 | 0.450 Gb/s                  | Clock-Data Timing                      | Noise feedback to timing<br>Spatial Vdd variance spec'ed |  |

| 2003 | 0.650 Gb/s                  | Freq. Dependent Loss                   | Fast simulation of each Net<br>IR Analysis Required      |  |

| 2005 | 1.9 Gb/s<br>on-MCM          | Transmitter Equalization               | Timing and Noise Combined<br>SSN induced jitter          |  |

| 2007 | 2.5 Gb/s<br>off-MCM         | Tx and Rx Equalization                 | Scattering Parameters/BER<br>Statistical Random Jitter   |  |

| 2010 | 6.4-10 Gb/s<br>Differential | Include Physical Layer                 | Channel Analysis<br>Full System Considerations           |  |

#### IBM

## What does this mean for electrical design tools?

#### Extraction – 3D Full-wave tools

- High-frequency operation

- Fully 3D effects of via stubs and discontinuous return paths

- The discontinuous return paths are a big challenge

#### Power Distribution Analysis

- Electromigration limits

- Impact of switching noise on signal interfaces

#### Signal Distribution Analysis

- Frequency-Domain Analysis

- Consortium defined interfaces and meeting compliance

#### Increasing use of commercial tools

- Tools are maturing

- Standardize design process when sharing design work among design teams

- Manage tool development cost

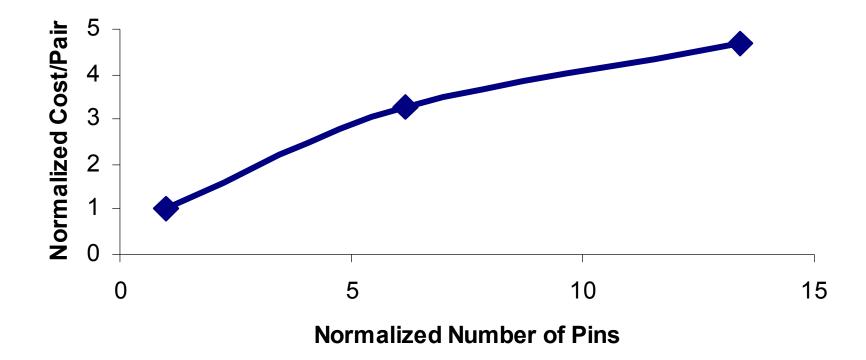

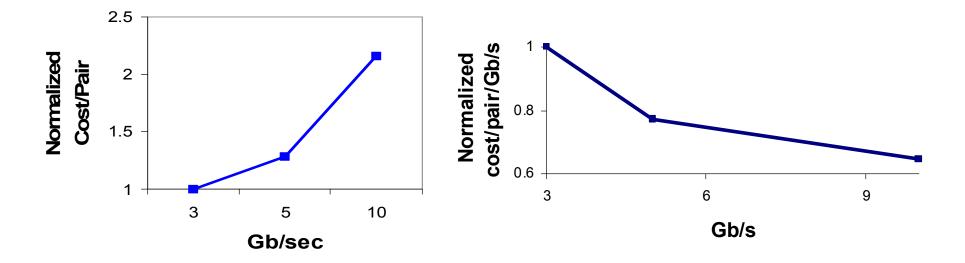

#### **Bandwidth Cost Pressures**

- Need to either increase number of pins or frequency to meet bandwidth growth

- Frequency increase requires more expensive technology

- High Frequency Connectors

- Removing Via Stubs

- Low Loss Laminates

- More pins ... cost is not linearly proportional to number

- More expensive connectors

- More card real estate for wiring and connector

- More card area is committed to provide proper plane and via signal shielding.

#### The cost of dense interconnection – Server comparisons

#### 2007 Future Directions in IC and Package Design Workshop

#### Cost Requirements for high-performance Assuming maintaining the same system structure

My Assumptions assuming high number of pins, 1 meter connection, 2 connectors3 Gb/s ... 1x PCB,1x connector cost5 Gb/s ... 1.4x PCB,2x connector cost10 Gb/s ... 3x PCB,4x connector cost

Higher frequencies create significant design and characterization effort. Higher frequencies also significantly increase chip area and power for I/O circuits.

## Conclusions

Multi-core sockets are needed to maintain performance growth.

- Meet 2010 targets for system performance

#### This trend stresses packaging

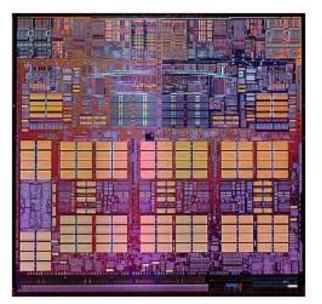

- Packaging larger chips or multiple processor chips in a socket.

- More cores demand more signal bandwidth, memory bandwidth

#### Electrical package design needs development

- Power distribution network impact on signal distribution

- Chip Package co-design ... system level design tools

- Cost optimization to meet competitive pressures